基于无掩模光刻的扇出封装系统、方法及重布线方法

文献发布时间:2023-06-19 11:57:35

技术领域

本发明涉及芯片技术领域,尤其涉及一种基于无掩模光刻的扇出封装系统、 方法及重布线方法。

背景技术

扇出型封装在集成电路封装中受到越来越多的关注。其在封装体积、产品 性能、封装成本和封装效率上都具有明显优势,并在近年来取得了长足进步。 然而在应用扇出型晶圆级封装时存在许多问题需要解决。其中之一便是芯片位 置准确度的问题。在重新构建晶圆时,必须要保证芯片从拾取及放置于载板上 的位置的精确度控制在5微米,同时塑封过程中,每一层的热膨胀系数不同也 可能导致芯片的偏移。由于后续再布线层(RDL)技术中,光学光刻技术要求掩模 版和晶圆严格对准。若芯片的位置发生偏移,则会导致后续光刻出来的线路失 效。

针对芯片偏移问题,现有技术都把目光聚焦于塑封步骤中,忽略了拾取及 放置于载板上的位置的精确度问题。同时,若在使用这些方法时还是出现了芯 片偏移现象,下一步就只能把这个芯片来去掉重新制作和封装,并不能进行一 定程度的补救,仍不能很好地解决芯片偏移问题。

发明内容

本发明的目的在于提出一种芯片扇出封装的无掩模光刻方法,其基于数字 微镜(DMD)的无掩模光刻技术,通过改变输入DMD中的电路图来改变光刻线路来 配合偏移的芯片进行光刻,它不需要直接使用掩模版就能实现在芯片上进行加 工,削减了封装成本,且激光成像可以解决扇出型封装中的芯片偏移问题。

本发明还提出一种芯片扇出封装的布线方法,其使用了上述的无掩模光刻 方法,能在芯片表面形成多层导电层。

本发明还提出一种芯片扇出封装的方法,其使用了上述的布线方法,使芯 片扇出封装完成。

本发明还提出一种芯片扇出封装的系统,包括:激光发生器、工业相机、 数据处理装置、光刻光源和数字微镜阵列DMD。

为达此目的,本发明采用以下技术方案:

一种芯片扇出封装的无掩模光刻方法,包括以下步骤:

步骤(1):基于已装贴于载板且已完成塑封的至少一个芯片,激光发生器 对载板和芯片扫描;工业相机拍摄芯片在载板形成的芯片阵列图,并传到数据 处理装置;数据处理装置对芯片阵列图的芯片进行识别并计算各个芯片的位置 和角度,获得芯片偏移信息;

若芯片的位置和/或角度有偏移,则从步骤(2)开始执行;若芯片的位置 和/或角度无偏移,则从步骤(3)开始执行,数字微镜阵列DMD依预设的电路 图工作;

步骤(2):根据芯片阵列图中非偏移芯片的端口特征及位置,结合芯片偏 移信息,数据处理装置计算并设计出新的电路图;

步骤(3):在塑封后的芯片表面涂光刻胶,并对光刻胶版进行光刻处理; 将光刻光源反射至数字微镜阵列DMD,数字微镜阵列DMD根据电路图调整每个微 镜的偏移角度,将光束照射于光刻胶上,依电路图的形状在光刻胶的表面刻蚀 出电路光刻道。

优选地,所述步骤(1)中,使用预先设定的芯片阵列标准图对芯片阵列图 的全局图像进行模板匹配,对芯片阵列图中所有芯片所在位置进行遍历,由芯 片阵列图与芯片阵列标准图进行相减,得出两者的像素差值,利用差值推算出 偏移芯片的位移量(X,Y)与角度θ。

优选地,所述步骤(3),以数字微镜阵列DMD作为数字图形发生器,其控 制系统通过对微镜的底层的一对存储状态始终互补的双CMOS型存储器进行控 制,把逻辑状态提前加载到微镜的存储元上,然后通过一个微镜定时脉冲批量 改变微镜的偏转,光路照射到数字微镜阵列DMD上生成一个虚拟的掩模,通过 光学仪器使光束透过此虚拟掩模照射在涂油光刻胶板上,完成光刻的过程。

优选地,所述步骤(1)中,将芯片放置于载板后,芯片经可塑材料塑成、 研磨和保护层沉积后,对芯片的载体拆除,使每个芯片经物理气相沉积或化学 气相沉积固封在保护层。

更优地,在晶圆上将芯片切割后,对芯片进行表面处理,使用机械手将芯 片逐一放置在已经进行胶带层压的载板。

一种芯片扇出封装的布线方法,包括以下步骤;

步骤(S1):将多个芯片装贴于载板后,对芯片进行塑封,使每个芯片固封 在保护层;

步骤(S2):通过上述的无掩模光刻方法,形成电路光刻道;在光刻胶的表 面及电路光刻道覆上导电层;

重复所述步骤(S2),直至在芯片表面形成多层导电层。

一种芯片扇出封装的方法,包括如上述的布线方法,以及以下步骤:

步骤(S3):在导电层表面涂光刻胶;

步骤(S4):在步骤(S3)的涂光刻胶设置导电座,导电座接触导电层;

步骤(S5):曝光显影,露出各个导电层和导电座;

步骤(S6):为导电层和导电座涂覆保护层;

步骤(S7):在导电座的表面植球。

一种芯片扇出封装的系统,包括:激光发生器、工业相机、数据处理装置、 光刻光源和数字微镜阵列DMD;

所述激光发生器,用于对载板和芯片扫描;

所述工业相机,用于拍摄芯片在载板形成的芯片阵列图,并传到数据处理 装置;

所述数据处理装置,用于对芯片阵列图的芯片进行识别并计算各个芯片的 位置和角度,获得芯片偏移信息;并根据芯片阵列图中非偏移芯片的端口特征 及位置,结合芯片偏移信息,数据处理装置计算并设计出新的电路图;

所述光刻光源,用于对光刻胶版进行光刻处理;

所述数字微镜阵列DMD,用于根据所述数据处理装置的电路图调整每个微镜 的偏移角度,将所述光刻光源的光束照射于光刻胶上,依电路图的形状在光刻 胶的表面刻蚀出电路光刻道。

优选地,所述数据处理装置,使用预先设定的芯片阵列标准图对芯片阵列 图的全局图像进行模板匹配,对芯片阵列图中所有芯片所在位置进行遍历,让 芯片阵列图与芯片阵列标准图进行相减,得出两者的像素差值,利用差值推算 出偏移芯片的位移量(X,Y)与角度θ。

更优地,还包括:机械手;

所述机械手用于将芯片逐一放置在已经进行胶带层压的载板。

本发明的有益效果:

1、本方案的无掩模光刻方法采用数字微镜阵列作为数字掩模,只需要电子 形式的掩模图形设计就可以进行光刻曝光,极大地节省了掩模板制作的时间金 钱成本;同时得益于数字微镜阵列具有空间光的灰度调制功能,本方案的无掩 模光刻方法制作出的图形精度更高,极大的提高了加工效率。

2、基于数据处理装置视觉的算法处理,本无掩模光刻方法根据偏移量与角 度生成一个新的掩模图像,即该方法可以解决扇出型封装中的芯片偏移问题, 极大地提高了封装的灵活性。

附图说明

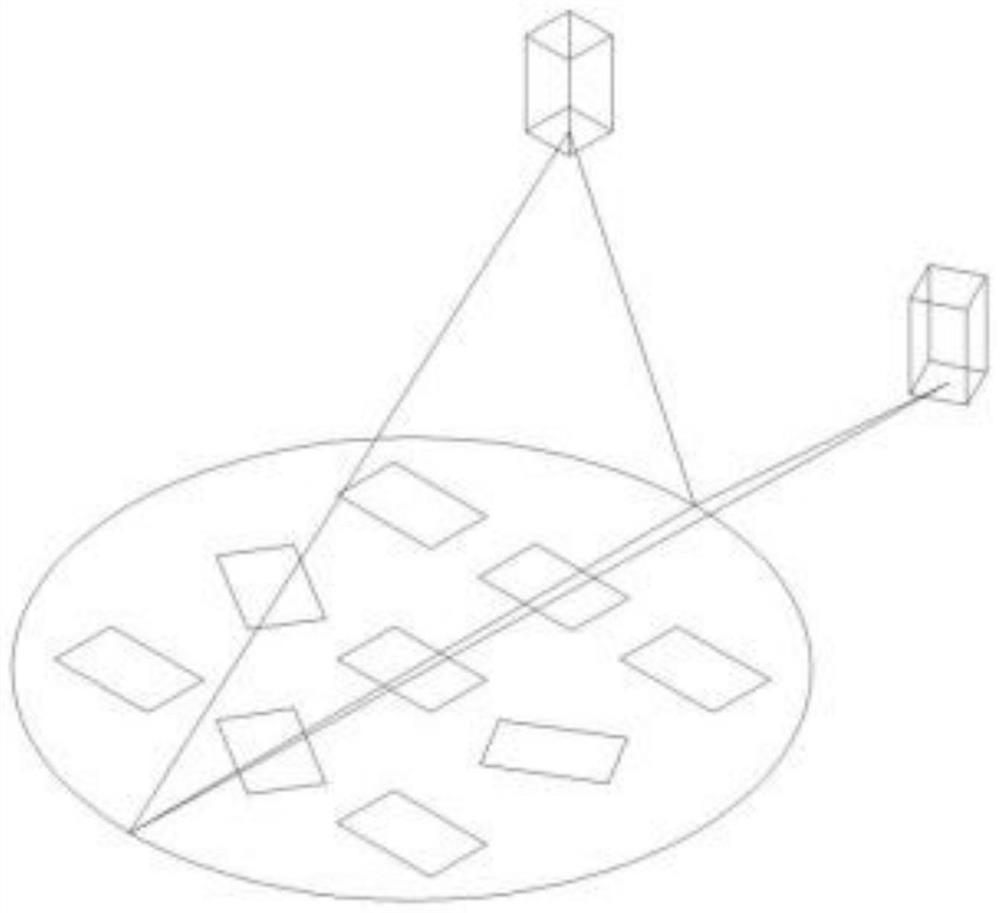

图1是激光发生器和工业相机识别出偏移芯片时的示意图;

图2是芯片放置在载板上并经过塑封后的示意图;

图3是芯片扇出封装中的重布线时的示意图;

图4是DMD的基本结构结构示意图;

图5是芯片扇出封装的过程示意图;

图6是无掩模光刻流程示意图。

具体实施方式

下面结合附图通过具体实施方式来进一步说明本发明的技术方案。

一种芯片扇出封装的无掩模光刻方法,包括以下步骤:

步骤(1):基于已装贴于载板且已完成塑封的至少一个芯片,激光发生器 对载板和芯片扫描;工业相机拍摄芯片在载板形成的芯片阵列图,并传到数据 处理装置;数据处理装置对芯片阵列图的芯片进行识别并计算各个芯片的位置 和角度,获得芯片偏移信息;

如图1,激光发射器和工业相机之间呈一定的夹角放置。激光发生器对载板 进行扫描,工业相机拍摄图像并传到数据处理装置上。数据处理装置对载板上 的芯片进行识别并计算芯片的位置和角度,找出偏移了的芯片;数据处理装置 为常规具有处理数据和计算数据的装置,如计算机或手机等数据处理端;

若芯片的位置和/或角度有偏移,则从步骤(2)开始执行;若芯片的位置 和/或角度无偏移,则从步骤(3)开始执行,数字微镜阵列DMD依预设的电路 图工作;

如图2中,a)为正常情况下,芯片经过PNP放置在载板上并经过塑封后的 效果,b)为芯片经过PNP放置在载板上并经过塑封后,发生了偏移。

对于图2中的a),由于芯片的位置和/或角度无偏移,则从步骤(3)开始 执行,数字微镜阵列DMD依预设的电路图工作;对于图2中的b),则先执行步 骤(2),再执行步骤(3)。

步骤(2):根据芯片阵列图中非偏移芯片的端口特征及位置,结合芯片偏 移信息,数据处理装置计算并设计出新的电路图;

步骤(3):在塑封后的芯片表面涂光刻胶,并对光刻胶版进行光刻处理; 将光刻光源反射至数字微镜阵列DMD,数字微镜阵列DMD根据电路图调整每个微 镜的偏移角度,将光束照射于光刻胶上,依电路图的形状在光刻胶的表面刻蚀 出电路光刻道。

本方案的无掩模光刻方法采用数字微镜阵列作为数字掩模,只需要电子形 式的掩模图形设计就可以进行光刻曝光,极大地节省了掩模板制作的时间金钱 成本;同时得益于数字微镜阵列具有空间光的灰度调制功能,本方案的无掩模 光刻方法制作出的图形精度更高,极大的提高了加工效率。

同时基于数据处理装置视觉的算法处理,本无掩模光刻方法根据偏移量与 角度生成一个新的掩模图像,即该方法可以解决扇出型封装中的芯片偏移问题, 极大地提高了封装的灵活性。

在重新构建晶圆时,必须要保证芯片从拾取及放置于载板上的位置的精确 度控制在5微米,同时塑封过程中,每一层的热膨胀系数不同也可能导致芯片 的偏移。由于后续再布线层(RDL)技术中,光学光刻技术要求掩模版和晶圆严格 对准。若芯片的位置发生偏移,则会导致后续光刻出来的线路失效。

如图3中a)为芯片扇出封装中的重布线示意图,芯片处于正常位置,芯片 及其端口和RDL层端口与预设的电路图接近或一样;预设的电路图如图3中b) 所示;当数字微镜阵列DMD根据电路图刻蚀出电路光刻道时,其在需要的布置 电路的位置形成电路光刻道,以在后续布置导电层时,导电层能沿电路光刻道 分布,实现了导电层能沿电路图分布,如图3中c)。

而如图3中的d)为芯片扇出封装中的重布线示意图,芯片处于偏移位置, 因此芯片及其端口和RDL层端口与图3中的a)不同,需要数据处理装置根据芯 片阵列图中非偏移芯片的端口特征、位置和芯片偏移信息等计算并设计出新的 电路图,设计出新的电路图如图3的e);图3中的e)为芯片处于偏移位置时, 应该输入DMD中的电路图;当数字微镜阵列DMD根据新设计的电路图刻蚀出电 路光刻道时,其在需要的布置电路的位置形成电路光刻道,该电路光刻道是根 据芯片实际偏移的位置和/或角度计算出来的,以在后续布置导电层时,导电层 能沿电路光刻道分布,如图3f),实现了导电层能沿电路图分布,解决了芯片的位置发生偏移时导致后续光刻出来的线路失效的问题。

其中,光刻光源经过电子快门、扩束准直反射至数字微镜阵列DMD。DMD可 作为一种数字图形发生器,相当于传统光刻系统的掩模版。它与输入电路图的 像素点一一对应;其中电路图可以为常见的文件格式,例如CAD位图的DWG格 式。例如,如图4,DMD由微米尺寸的微镜阵列组成。DMD微镜结构中,每个DMD 微镜的偏转状态由该微镜下面的SRAM单元中存储的二进制数据决定。比如,偏 转+12°定义为“on”状态,偏转-12°定义为“off”状态。当电路图对应的像 素点为白色时,对应的微镜输入二进制控制信号为1,处于on状态,微镜偏转+12°。相反,若电路图对应像素点为黑色时,对应微镜输入二进制控制信号为0,处于off状态,微镜偏转-12°。因此,只需用绘图软件绘制相应的电路图, 并将其输入到DMD的控制芯片,在DMD表面就会生成相应的掩模结构图形。光 源经过光学系统再通过生成掩模结构图形的DMD达到涂有光刻胶的载板上,便 能在载板上光刻出相应的电路。

优选地,所述步骤(1)中,使用预先设定的芯片阵列标准图对芯片阵列图 的全局图像进行模板匹配,对芯片阵列图中所有芯片所在位置进行遍历,由芯 片阵列图与芯片阵列标准图进行相减,得出两者的像素差值,利用差值推算出 偏移芯片的位移量(X,Y)与角度θ。

预先设定的芯片阵列标准图中,由于芯片可近似为四边形矩形或其他规则 的形状,可使用数据处理装置视觉中模板匹配的算法,识别出偏移芯片的位移 量(X,Y)与角度θ,并将位移量(X,Y)与角度θ反馈给系统数据处理装置, 由数据处理装置计算,再针对偏移的情况设计出新的电路图,解决扇出型封装 中的芯片偏移问题,极大地提高了封装的灵活性。例如,使用opencv的 matchtemplat的相关函数,利用一个模板芯片图对全局图像进行模板匹配,对 所有芯片所在位置进行遍历,让原始图像与模板图进行相减,得出两者的像素 差值,可利用差值推算出偏移芯片的位移量和角度。

优选地,所述步骤(3),以数字微镜阵列DMD作为数字图形发生器,其控 制系统通过对微镜的底层的一对存储状态始终互补的双CMOS型存储器进行控 制,把逻辑状态提前加载到微镜的存储元上,然后通过一个微镜定时脉冲批量 改变微镜的偏转,光路照射到数字微镜阵列DMD上生成一个虚拟的掩模,通过 光学仪器使光束透过此虚拟掩模照射在涂油光刻胶板上,完成光刻的过程。

优选地,所述步骤(1)中,将芯片放置于载板后,芯片经可塑材料塑成、 研磨和保护层沉积后,对芯片的载体拆除,使每个芯片经物理气相沉积或化学 气相沉积固封在保护层。

更优地,在晶圆上将芯片切割后,对芯片进行表面处理,使用机械手将芯 片逐一放置在已经进行胶带层压的载板。

对晶圆上将芯片切割后,进行芯片清洗等公知的表面工艺后,使用PNP(pick andplace)装置将其逐一放置在已经进行胶带层压的载板上;完成放置后,进 行了Molding(可塑材料塑成)、研磨、保护层沉积最后进行载体拆除,然后使 每个芯片经过PVD或CVD沉积工艺固封在保护层上。

一种芯片扇出封装的布线方法,包括以下步骤;

步骤(S1):将多个芯片装贴于载板后,对芯片进行塑封,使每个芯片固封 在保护层;

步骤(S2):通过上述任意实施例的无掩模光刻方法,形成电路光刻道;在 光刻胶的表面及电路光刻道覆上导电层;

重复所述步骤(S2),直至在芯片表面形成多层导电层。

本方案的使用的芯片扇出封装布线方法,其能应芯片扇出封装,为芯片进 行多层重布线时提供一种新型的布线方法,基于DMD的无掩模光刻技术应用到 扇出型晶圆级封装的重布线层,有效地根据芯片偏移与否以及偏移的角度和位 置,对DMD输入不同的电路图来进行光刻,解决了芯片封装中产生的芯片偏移 问题;且本布线方法通过采用数字微镜生成的一个虚拟掩模板,极大的节省了 掩模板制作的成本。

其中,导电层可为常规具有导电功能的金属形成,如银、铜、金等,优选 使用铜。

一种芯片扇出封装的方法,包括上述任意实施例的布线方法,以及以下步 骤:

步骤(S3):在导电层表面涂光刻胶;

步骤(S4):在步骤(S3)的涂光刻胶设置导电座,导电座接触导电层;

步骤(S5):曝光显影,露出各个导电层和导电座;

步骤(S6):为导电层和导电座涂覆保护层;

步骤(S7):在导电座的表面植球。

一种芯片扇出封装的系统,包括:激光发生器、工业相机、数据处理装置、 光刻光源和数字微镜阵列DMD;

所述激光发生器,用于对载板和芯片扫描;

所述工业相机,用于拍摄芯片在载板形成的芯片阵列图,并传到数据处理 装置;

所述数据处理装置,用于对芯片阵列图的芯片进行识别并计算各个芯片的 位置和角度,获得芯片偏移信息;并根据芯片阵列图中非偏移芯片的端口特征 及位置,结合芯片偏移信息,数据处理装置计算并设计出新的电路图;

所述光刻光源,用于对光刻胶版进行光刻处理;

所述数字微镜阵列DMD,用于根据所述数据处理装置的电路图调整每个微镜 的偏移角度,将所述光刻光源的光束照射于光刻胶上,依电路图的形状在光刻 胶的表面刻蚀出电路光刻道。

优选地,所述数据处理装置,使用预先设定的芯片阵列标准图对芯片阵列 图的全局图像进行模板匹配,对芯片阵列图中所有芯片所在位置进行遍历,让 芯片阵列图与芯片阵列标准图进行相减,得出两者的像素差值,利用差值推算 出偏移芯片的位移量(X,Y)与角度θ。

优选地,还包括:机械手;所述机械手用于将芯片逐一放置在已经进行胶 带层压的载板。

实施例1:

1)晶圆重布;将原来的晶圆进行磨划、切割等工艺,获取单颗芯片。随后 如图1,将芯片重新阵列贴装在贴有双面胶膜的载板上。

2)塑封;如图2,对装贴在载板上的芯片进行塑封,如图2a)或图2b), 芯片可能会在这步骤后发生偏移。

3)AOI检测;如图1,激光发射器和工业相机之间呈一定的夹角放置。激 光发生器对载板进行扫描,工业相机拍摄图像并传到数据处理装置上。数据处 理装置对载板上的芯片进行识别并计算芯片的位置和角度,找出偏移了的芯片, 获得芯片偏移信息。

若芯片的位置和/或角度无偏移,则从5)开始执行,数字微镜阵列DMD依 预设的电路图工作;若芯片的位置和/或角度偏移,则从4)开始执行;

4)设计CAD位图;如图3a)–c),根据正常芯片的端口以及电路端口的 位置;数据处理装置设计电路图,或根据预设的电路图工作。

数据处理装置找出偏移芯片的端口位置,如图3d)-f),根据偏移芯片的 端口以及电路端口的位置,数据处理装置设计电路图。

5)芯片扇出封装布线方法;如图5b),为塑封后的芯片表面涂上一层光刻 胶。随后,如图5c),对光刻胶版进行光刻。光刻流程如图6,光源经过电子 快门、扩束准直反射后打到光路照射到数字微镜阵列DMD上,同时光路照射到 数字微镜阵列DMD根据数据处理装置输入的CAD位图,调整每个微镜的偏移角 度,将反应CAD位图的光束打在光刻胶版上,刻蚀出CAD位图的形状,在光刻 胶的表面刻蚀出电路光刻道。随后如图5d),对光刻胶版覆上一层铜,铜可盖 于电路光刻道,清洗表面,便能在光刻中的线路中覆上铜。

6)芯片扇出封装根据芯片扇出封装布线方法再次重布线;如图5e)–g), 在第一层重布线层上进行第二次重布线。

7)芯片植球;如图5的h)–l),在第二个布线层上布上一层光刻胶, 在上面进行凸点下金属(UBM)沉积,随后进行显影来将光刻胶去掉,最后进行植 球完成芯片扇出封装。

以上结合具体实施例描述了本发明的技术原理。这些描述只是为了解释本 发明的原理,而不能以任何方式解释为对本发明保护范围的限制。基于此处的 解释,本领域的技术人员不需要付出创造性的劳动即可联想到本发明的其它具 体实施方式,这些方式都将落入本发明的保护范围之内。

- 基于无掩模光刻的扇出封装系统、方法及重布线方法

- 基于无掩模光刻的扇出封装系统、方法及重布线方法