开关控制装置、驱动装置、绝缘型DC/DC转换器、AC/DC转换器、电源适配器

文献发布时间:2024-01-17 01:24:51

本申请是申请日2019年09月30日,申请号2019109437524,发明名称“开关控制装置、驱动装置、绝缘型DC/DC转换器、AC/DC转换器、电源适配器”的分案申请。

技术领域

本发明涉及一种开关控制装置、驱动装置、绝缘型DC/DC转换器、AC/DC转换器、电源适配器及电气设备。

背景技术

开关控制装置有时用于对与线圈串联连接的开关元件进行开关驱动(参照下述专利文献1)。在这种情况下,有采用一种利用检测电阻(センス抵抗)来检测流经开关元件的电流的结构,使用在使开关元件导通后基于检测电阻的产生电压来决定开关元件的断开定时的电流控制方式。

作为典型例,例如有将开关元件串联连接于变压器的一次侧绕组(线圈),并对该开关元件适用电流控制方式的利用方式。

当采用如上所述的电流控制方式时,假设检测电阻短路,则检测电阻的产生电压不表示流经开关元件的电流,因而有可能丧失开关元件的断开的机会而引发开关元件的破损等。保护开关元件免遭破损等极为重要。

一方面,图21中示出现有技术中具备高侧晶体管901和低侧晶体管902的驱动装置900。在图21中,互相串联连接的晶体管901与晶体管902之间的连接节点与驱动装置900的输出端子903连接,在驱动装置900的外部,开关晶体管910的栅极与输出端子903连接。驱动装置900可以通过将晶体管901和晶体管902交替地设为导通、断开来对开关晶体管910进行开关驱动。

在驱动装置中,存在输出端子发生电源故障(天絡)或接地故障(地絡)等异常的可能性。例如,在图21的驱动装置900中,若当输出端子903发生电源故障时低侧晶体管902为导通状态,则过大的电流通过低侧晶体管902流动,若当输出端子903发生接地故障时高侧晶体管901为导通状态,则过大的电流通过高侧晶体管901流动。过大的电流可能导致驱动装置900的破损或劣化。

现有技术文献

专利文献1:日本特开2009-240067号公报;

专利文献2:日本特开2013-070530号公报。

发明内容

本发明的目的在于,提供一种具备与检测电阻的短路等相关的保护功能的开关控制装置、以及利用该开关控制装置的绝缘型DC/DC转换器、AC/DC转换器、电源适配器及电气设备。

或者,本发明的目的在于,提供一种具备针对电源故障等异常的发生的保护功能的驱动装置、以及利用该驱动装置的绝缘型DC/DC转换器、AC/DC转换器、电源适配器及电气设备。

本发明的一方面的开关控制装置是如下一种结构,即,该开关控制装置具备:输出端子,其与开关元件的控制电极连接;电压输入端子,其将应与所述开关元件串联连接的检测电阻的产生电压作为检测电压(センス電圧)来接受;控制电路,其生成驱动控制信号;以及驱动电路,其基于所述驱动控制信号,通过所述输出端子使所述开关元件导通或断开,所述控制电路被构成为能够在使所述开关元件导通后,执行基于所述检测电压来决定所述开关元件的断开定时的电流控制,在所述电流控制的执行过程中,当从使所述开关元件导通后经过预定时间,所述检测电压仍未达到预定的判定电压时,所述控制电路使所述开关元件断开(第一结构)。

在上述第一结构的开关控制装置中,可以是如下一种结构,即,对所述开关元件、所述检测电阻与线圈的串联电路施加预定的直流电压,在所述开关元件的导通区间,随着从所述开关元件导通后的经过时间的增加,流经所述开关元件的电流增加(第二结构)。

在上述第一结构或第二结构的开关控制装置中,可以是如下一种结构,即,在所述电流控制中,所述控制电路在使所述开关元件导通后,响应于所述检测电压达到预定的断开基准电压,使所述开关元件断开,所述判定电压低于所述断开基准电压(第三结构)。

在上述第一结构或第二结构的开关控制装置中,可以是如下一种结构,即,在所述电流控制中,所述控制电路在使所述开关元件导通后,响应于所述检测电压达到预定的断开基准电压,使所述开关元件断开,所述判定电压具有与所述断开基准电压相同的电压值(第四结构)。

在上述第一结构至第四结构中的任一结构的开关控制装置中,可以是如下结构,即,该开关控制装置由半导体集成电路形成(第五结构)。

本发明的一方面的绝缘型DC/DC转换器是如下一种结构,即,该绝缘型DC/DC转换器具备具有一次侧绕组和二次侧绕组的变压器、作为与所述一次侧绕组连接的开关元件的开关晶体管、与所述开关晶体管串联连接的检测电阻以及控制所述开关晶体管的导通、断开的一次侧控制电路,根据施加于所述一次侧绕组的输入电压在所述变压器的二次侧生成输出电压,作为所述一次侧控制电路,所述绝缘型DC/DC转换器使用上述第一结构至第五结构中的任一结构的开关控制装置,所述开关晶体管的控制电极与所述开关控制装置的输出端子连接,且由所述开关控制装置对所述开关晶体管进行开关驱动(第六结构)。

本发明的一方面的AC/DC转换器是如下一种结构,即,具备:整流电路,其对交流电压进行全波整流;平滑电容器,其通过对全波整流后的电压进行平滑化来生成直流电压;以及上述第六结构的绝缘型DC/DC转换器,其根据作为所述直流电压的输入电压生成直流的输出电压(第七结构)。

本发明的一方面的电源适配器是如下一种结构,即,具备:插头,其接受交流电压;上述第七结构的AC/DC转换器;以及壳体,其容纳所述AC/DC转换器(第八结构)。

本发明的一方面的电气设备是如下一种结构,即,具备:上述第七结构的AC/DC转换器;以及基于所述AC/DC转换器的输出电压来驱动的负载(第九结构)。

本发明的一方面的驱动装置是如下一种结构,即,该驱动装置具备输出端子、与所述输出端子连接,用于调整所述输出端子的电压电平的驱动电路以及控制所述驱动电路的状态的状态控制部,所述驱动电路取用于将输出端子的电压电平设为预定的第一电平的第一状态、用于将所述输出端子的电压电平设为高于所述第一电平的预定的第二电平的第二状态以及第三状态中的任一状态,从所述输出端子观察到的所述驱动电路的阻抗在所述第三状态比在所述第一状态和所述第二状态高,当从所述驱动电路的状态被设为所述第一状态后经过预定时间,所述输出端子的电压仍未成为高于所述第一电平的电压的预定的判定电压以下时,所述状态控制部将所述驱动电路的状态设为所述第三状态(第十结构)。

本发明的另一方面的驱动装置是如下一种结构,即,该驱动装置具备输出端子、与所述输出端子连接,用于调整所述输出端子的电压电平的驱动电路以及控制所述驱动电路的状态的状态控制部,所述驱动电路取用于将输出端子的电压电平设为预定的第一电平的第一状态、用于将所述输出端子的电压电平设为高于所述第一电平的预定的第二电平的第二状态以及第三状态中的任一状态,从所述输出端子观察到的所述驱动电路的阻抗在所述第三状态比在所述第一状态和所述第二状态高,当从所述驱动电路的状态被设为所述第二状态后经过预定时间,所述输出端子的电压仍未成为低于所述第二电平的电压的预定的判定电压以上时,所述状态控制部将所述驱动电路的状态设为所述第三状态(第十一结构)。

在上述第十结构的驱动装置中,可以是如下一种结构,即,所述驱动电路具有互相串联连接的第一晶体管和第二晶体管,对所述第一晶体管和所述第二晶体管的串联电路施加预定的驱动用电压,所述第一晶体管配置在所述第二晶体管的高电位侧,所述第一晶体管与所述第二晶体管之间的连接节点与所述输出端子连接,在所述第一状态下,所述第一晶体管和所述第二晶体管分别被设为断开、导通,在所述第二状态下,所述第一晶体管和所述第二晶体管分别被设为导通、断开,在所述第三状态下,所述第一晶体管和所述第二晶体管均被设为断开(第十二结构)。

在上述第十一结构的驱动装置中,可以是如下一种结构,即,所述驱动电路具有互相串联连接的第一晶体管和第二晶体管,对所述第一晶体管和所述第二晶体管的串联电路施加预定的驱动用电压,所述第一晶体管配置在所述第二晶体管的高电位侧,所述第一晶体管与所述第二晶体管之间的连接节点与所述输出端子连接,在所述第一状态下,所述第一晶体管和所述第二晶体管分别被设为断开、导通,在所述第二状态下,所述第一晶体管和所述第二晶体管分别被设为导通、断开,在所述第三状态下,所述第一晶体管和所述第二晶体管均被设为断开(第十三结构)。

本发明的另一方面的驱动装置是如下一种结构,即,该驱动装置具备输出端子、与所述输出端子连接,用于调整所述输出端子的电压电平的驱动电路以及控制所述驱动电路的状态的状态控制部,所述驱动电路取用于将所述输出端子的电压电平设为预定的第一电平的第一状态和用于将所述输出端子的电压电平设为高于所述第一电平的预定的第二电平的第二状态中的任一状态,从所述输出端子观察到的所述驱动电路的阻抗在所述第二状态笔在所述第一状态高,当从所述驱动电路的状态被设为所述第一状态后经过预定时间,所述输出端子的电压仍未成为高于所述第一电平的电压的预定的判定电压以下时,所述状态控制部将所述驱动电路的状态设为所述第二状态(第十四结构)。

在上述第十四结构的驱动装置中,可以是如下一种结构,即,所述驱动电路具有互相串联连接的上拉电阻和晶体管,对所述上拉电阻和所述晶体管的串联电路施加预定的驱动用电压,所述上拉电阻配置在所述晶体管的高电位侧,所述上拉电阻与所述晶体管之间的连接节点与所述输出端子连接,在所述第一状态、所述第二状态下,所述晶体管分别被设为导通、断开(第十五结构)。

本发明的又一方面的驱动装置是如下一种结构,即,该驱动装置具备输出端子、与所述输出端子连接,用于调整所述输出端子的电压电平的驱动电路以及控制所述驱动电路的状态的状态控制部,所述驱动电路取用于将所述输出端子的电压电平设为预定的第一电平的第一状态和用于将所述输出端子的电压电平设为高于所述第一电平的预定的第二电平的第二状态中的任一状态,从所述输出端子观察到的所述驱动电路的阻抗在所述第一状态比在所述第二状态高,当从所述驱动电路的状态被设为所述第二状态后经过预定时间,所述输出端子的电压仍未成为低于所述第二电平的电压的预定的判定电压以上时,所述状态控制部将所述驱动电路的状态设为所述第一状态(第十六结构)。

在上述第十六结构的驱动装置中,可以是如下一种结构,即,所述驱动电路具有互相串联连接的晶体管和下拉电阻,对所述晶体管和所述下拉电阻的串联电路施加预定的驱动用电压,所述晶体管配置在所述下拉电阻的高电位侧,所述晶体管与所述下拉电阻之间的连接节点与所述输出端子连接,在所述第一状态、所述第二状态下,所述晶体管分别被设为断开、导通(第十七结构)。

在上述第十结构至第十七结构中的任一结构的驱动装置中,可以是如下结构,即,该驱动装置由半导体集成电路形成(第十八结构)。

本发明的一方面的绝缘型DC/DC转换器是如下一种结构,即,该绝缘型DC/DC转换器具备具有一次侧绕组和二次侧绕组的变压器、与所述一次侧绕组连接的开关晶体管以及控制所述开关晶体管的导通、断开的一次侧控制电路,根据施加于所述一次侧绕组的输入电压在所述变压器的二次侧生成输出电压,作为所述一次侧控制电路,所述绝缘型DC/DC转换器采用上述第十结构至第十八结构中的任一结构的驱动装置,所述开关晶体管的栅极与所述驱动装置的输出端子连接,由所述驱动装置对所述开关晶体管进行开关驱动(第十九结构)。

本发明的一方面的AC/DC转换器是如下一种结构,即,具备:整流电路,其对交流电压进行全波整流;平滑电容器,其通过对全波整流后的电压进行平滑化来生成直流电压;以及上述第十九结构的绝缘型DC/DC转换器,其根据作为所述直流电压的输入电压生成直流的输出电压(第二十结构)。

本发明的一方面的电源适配器是如下一种结构,即,具备:插头,其接受交流电压;上述第二十结构的AC/DC转换器;以及壳体,其容纳所述AC/DC转换器(第二十一结构)。

本发明的一方面的电气设备是如下一种结构,即,具备:上述第二十结构的AC/DC转换器;以及基于所述AC/DC转换器的输出电压来驱动的负载(第二十二结构)。

根据本发明,能够提供一种具备与检测电阻的短路等相关的的保护功能的开关控制装置、以及利用该开关控制装置的绝缘型DC/DC转换器、AC/DC转换器、电源适配器及电气设备。

或者,根据本发明,能够提供一种具备针对电源故障等异常的发生的保护功能的驱动装置、以及利用该驱动装置的绝缘型DC/DC转换器、AC/DC转换器、电源适配器及电气设备。

附图说明

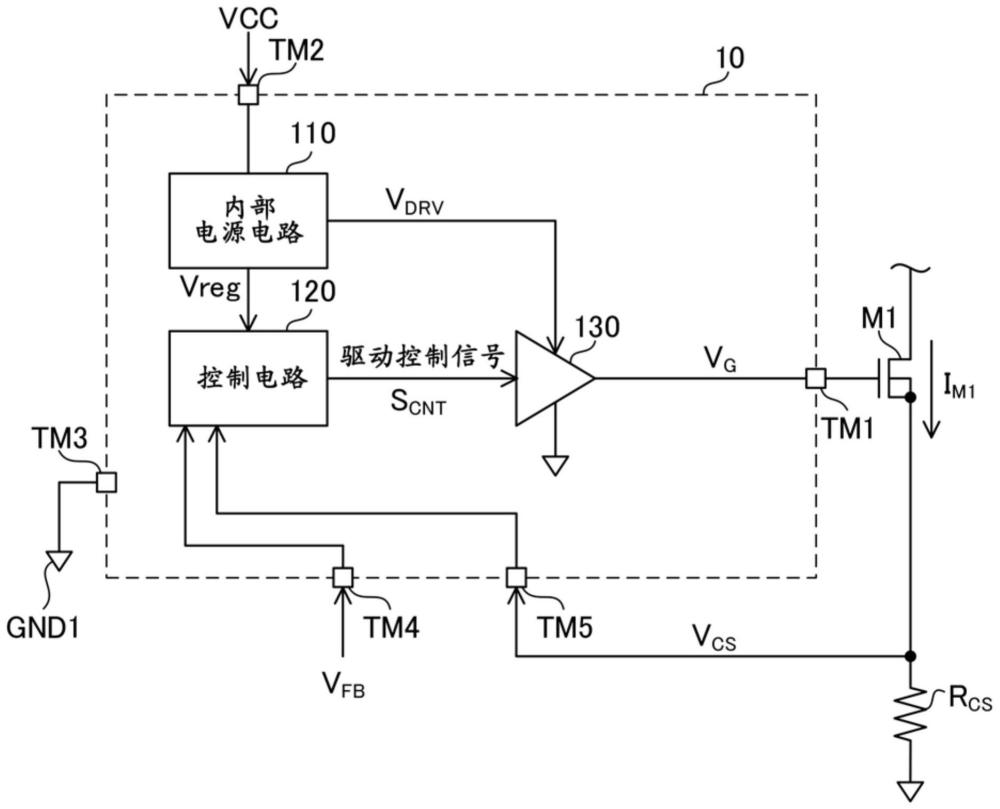

图1是本发明的第一实施方式的DC/DC转换器的整体结构图。

图2是图1所示的一次侧控制IC的外观立体图。

图3是图1所示的一次侧控制IC的示意性框图。

图4是图3所示的驱动电路的内部结构图。

图5是示出一次侧控制IC的启动时周边的开关晶体管的状态及输出电压的情形的图。

图6是本发明的第一实施方式的电流控制的说明图。

图7是本发明的第一实施方式的示出检测电阻短路时的电压及电流的波形等的图。

图8是本发明的第一实施方式的检测电阻短路时的保护动作的说明图。

图9是示出本发明的第三实施方式的AC/DC转换器的结构的图。

图10是示出本发明的第三实施方式的电源适配器的结构的图。

图11A和图11B是示出本发明的第三实施方式的电气设备的结构的图。

图12是本发明的第五实施方式的驱动装置的示意性框图。

图13是图12所示的驱动装置的外观立体图。

图14A和图14B是本发明的第五实施方式的驱动装置相关的电源故障和接地故障的说明图。

图15是示出本发明的第五实施方式的驱动电路和保护电路的结构例(EX5_1)的图。

图16是示出本发明的第五实施方式的输出端子电压的高电平及低电平与两个判定电压之间的关系的图。

图17是示出本发明的第五实施方式的驱动电路和保护电路的另一结构例(EX5_2)的图。

图18是示出本发明的第五实施方式的驱动电路和保护电路的又一结构例(EX5_3)的图。

图19是示出本发明的第九实施方式的负载驱动装置的结构的图。

图20是示出本发明的第九实施方式的非绝缘升压型DC/DC转换器的结构的图。

图21是示出现有技术中的通常的驱动装置的结构例的图。

具体实施方式

下面参照附图对本发明的实施方式的例子进行具体说明。在所参照的各图中,对相同的部分赋予相同的符号,并以省略关于相同部分的重复的说明为原则进行省略。此外,在本说明书中,为简化描述,有时通过标记来表示信息、信号、物理量或部件等的记号或符号来省略或略写与该记号或符号对应的信息、信号、物理量或部件等的名称。例如,后述的以“M1”表示的开关晶体管(参照图1)、有时用开关晶体管M1表记,有时也可能略写为晶体管M1,但其所指均相同。

首先,对本实施方式的描述中使用的一些术语进行说明。电平指电位的水平,对于任意的信号或电压,高电平具有高于低电平的电位。对于电平周期性地在低电平与高电平之间切换的任意的信号或电压,将该信号或电压的电平为高电平的区间的长度相对于该信号或电压的一个周期的区间的长度的比例称为占空比。

对于被构成为FET(场效应晶体管)的任意的晶体管(开关元件),导通状态指该晶体管的漏极与源极之间成为导通状态,断开状态指该晶体管的漏极与源极之间成为非导通状态(断开状态)。以下,对于任意的晶体管,有时将导通状态、断开状态仅表述为导通、断开。另外,对于任意的晶体管,将由断开状态向导通状态的切换表述为导通,将由导通状态向断开状态的切换表述为断开。

《第一实施方式》

下面对本发明的第一实施方式进行说明。图1是本发明的第一实施方式的绝缘同步整流型DC/DC转换器1(以下,可略写为DC/DC转换器1)的整体结构图。DC/DC转换器1是回扫方式的DC/DC转换器,其根据施加于输入端子P1的直流的输入电压V

DC/DC转换器1由相互电绝缘的一次侧电路和二次侧电路构成,一次侧电路中的接地端以“GND1”表示,二次侧电路中的接地端以“GND2”表示。在一次侧电路和二次侧电路的各个电路中,接地端指具有0V(零伏)的基准电位的导电部,或指基准电位本身。但是,由于接地端GND1与接地端GND2相互绝缘,因而可能具有彼此不同的电位。

DC/DC转换器1中的一对输出端子P2和P3中,输出端子P3与接地端GND2连接,从输出端子P3的电位(即,接地端GND2的电位)观察,向输出端子P2施加输出电压V

DC/DC转换器1具备变压器TR,变压器TR具有一次侧绕组W1和二次侧绕组W2。在变压器TR中,一次侧绕组W1与二次侧绕组W2相互电绝缘且相互以反极性磁耦合。

在DC/DC转换器1的一次侧电路中,除了一次侧绕组W1外,还设有作为一次侧控制电路的一次侧控制IC10、一次侧电源电路11、输入电容器C

在DC/DC转换器1的二次侧电路中,除了二次侧绕组W2外,还设有作为二次侧控制电路的二次侧控制IC20、反馈电路30、同步整流晶体管M2、二极管D2、分压电阻R1至R4、输出电容器C

二次侧绕组W2的一端与输出端子P2连接,因而向二次侧绕组W2的一端施加输出电压V

SR晶体管M2的源极与接地端GND2连接。另外,在输出端子P2与P3之间设有输出电容器C

二次侧控制IC20将输出电压V

在DC/DC转换器1中,光耦合器31跨设于一次侧电路和二次侧电路。光耦合器31具有配置于二次侧电路的发光元件和配置于一次侧电路的受光元件。光耦合器31的发光元件由输出电压V

一次侧控制IC10与光耦合器31的受光元件连接,且与流经光耦合器31的受光元件的反馈电流I

一次侧控制IC10与开关晶体管M1的栅极连接,且通过向开关晶体管M1的栅极供给脉冲信号来对开关晶体管M1进行开关驱动。脉冲信号是信号电平在低电平与高电平之间切换的矩形波状的信号。当向晶体管M1的栅极供给低电平、高电平的信号时,晶体管M1分别成为断开状态、导通状态。对一次侧控制IC10的结构及控制方式不做特殊限定。例如,一次侧控制IC10既可以利用PWM调制(脉冲宽度调制)将具有与反馈信号V

图2中示出一次侧控制IC10的外观的例子。一次侧控制IC10是通过将半导体集成电路封入由树脂构成的壳体(封装(パッケージ))内而形成的电子器件(半导体装置),构成一次侧控制IC10的各电路由半导体集成化。在作为一次侧控制IC10的电子器件的壳体中设有相暴露于IC10的外部的多个外部端子。此外,图2所示的外部端子的数量只不过是例示。二次侧控制IC20也具有与图2的一次侧控制IC10相同的结构。

作为设于一次侧控制IC10的多个外部端子的一部分,图1中示出了外部端子TM1至TM5。外部端子TM1是输出端子,与开关晶体管M1的栅极连接。外部端子TM2是电源端子,接受来自一次侧电源电路11的电源电压VCC的输入。外部端子TM3是接地端子,与接地端GND1连接。外部端子TM4、TM5分别接受反馈信号V

下面关注一次侧电路,并进一步对一次侧电路的部分结构和动作进行说明。此外,在本实施方式中,下文中,未另设定基准而示出的电压为从接地端GND1的电位观察到的电压,除非另外说明,0V(零伏)指接地端GND1的电位。

图3中示出一次侧控制IC10的示意性内部结构。一次侧控制IC10具备内部电源电路110、控制电路120以及驱动电路130。

内部电源电路110通过对输入至电源端子TM2的电源电压VCC进行直流-直流转换来生成1个以上的其他直流电压。这里,认为由内部电源电路110生成的直流电压中包括内部电源电压Vreg和驱动用电压V

控制电路120基于内部电源电压Vreg来驱动。控制电路120由逻辑电路构成,或由模拟电路和逻辑电路构成。控制电路120基于反馈信号V

驱动电路130基于驱动用电压V

图4中示出驱动电路130的内部结构例。图4的驱动电路130具备互相串联连接的晶体管131和132、预驱动器133。晶体管131被构成为P沟道型MOSFET,晶体管132被构成为N沟道型MOSFET。但是,也可以是将晶体管131构成为N沟道型MOSFET的变形。对晶体管131和晶体管132的串联电路施加驱动用电压V

当驱动控制信号S

当驱动控制信号S

此外,就预驱动器133而言,为了防止晶体管131和晶体管132同时成为导通状态,可以适当插入使晶体管131和晶体管132同时为断开状态的死区时间。

控制电路120可以通过向驱动电路130供给使信号电平在高电平与低电平之间切换的驱动控制信号S

利用反馈电路30的上述动作是反馈控制的执行过程中的动作。反馈控制指仅限在二次侧电路中的输出电压V

如图5所示,假设以二次侧电路的输出电压V

参照图6,对电流控制(自运行控制)进行说明。此外,下文中,为便于说明,称由电流检测信号V

电流控制是在使开关晶体管M1导通后,基于与电流I

在电流控制中,断开时间T

或者,在电流控制中,可以使开关晶体管M1的开关周期恒定。在电流控制中,当开关晶体管M1的开关周期被设为恒定时,按周期地根据开关晶体管M1的导通时间T

由于对一次侧绕组W1、开关晶体管M1、检测电阻R

如上述,本应向外部端子TM5输入与电流I

控制电路120具备与检测电阻R

当判断为发生了短路异常时,此后,控制电路120将驱动控制信号S

通过这样的动作,即使发生检测电阻R

短路判定电压V

当使短路判定电压V

另一方面,若将短路判定电压V

例如,假设在断开基准电压V

对此,当将断开基准电压V

此外,在从图5的定时t2起的反馈控制中,也可以利用电流控制。在这种情况下,如下进行动作即可。

即,例如,将反馈电路30构成为,仅限在输出电压V

《第二实施方式》

下面对本发明的第二实施方式进行说明。第二实施方式以及后述的第三、第四实施方式是以第一实施方式为基础的实施方式,关于在第二至第四实施方式中不另阐述的事项,只要不存在矛盾,第一实施方式的记载也适用于第二至第四实施方式。在第二实施方式中,对于在第一实施方式与第二实施方式之间矛盾的事项,可以是第二实施方式的记载优先(对于后述的第三、第四实施方式也同样)。只要不存在矛盾,可以组合第一至第四实施方式中的任意多个实施方式。进一步地,只要不存在矛盾,可以组合第一至第四实施方式和后述的第五至第九实施方式中的任意多个实施方式。

在第一实施方式中,虽然DC/DC转换器1是绝缘同步整流型DC/DC转换器,但就DC/DC转换器1而言,只要是根据施加于一次侧绕组W1的输入电压V

例如,虽然在图1所示的DC/DC转换器1中采用了所谓的低侧应用,但也可以采用高侧应用。在采用高侧应用的DC/DC转换器1中,SR晶体管M2设于输出端子P2侧,且SR晶体管M2被串联地插入于施加输出电压V

又例如,DC/DC转换器1也可以是使用整流二极管的DC/DC转换器(绝缘二极管整流型DC/DC转换器)。在这种情况下,在DC/DC转换器1中,代替图1的SR晶体管M2和寄生二极管D2地,将整流二极管设于二次侧电路。整流二极管被插入于二次侧绕组W2与输出电容器C

又例如,也可以将DC/DC转换器1构成为前馈式绝缘型DC/DC转换器,在这种情况下,也可以采用同步整流方式和整流二极管方式中的任一方式。

《第三实施方式》

下面对本发明的第三实施方式进行说明。在第三实施方式中,对本发明的绝缘型DC/DC转换器的用途进行说明。

如图9所示,可以构成使用本发明的绝缘型DC/DC转换器的AC/DC转换器300。AC/DC转换器300具备滤波器301、整流电路302、平滑电容器303以及绝缘型DC/DC转换器304。滤波器301去除被输入至AC/DC转换器300的交流电压V

也可以利用AC/DC转换器300来构成电源适配器。图10是示出具备AC/DC转换器300的电源适配器320的图。电源适配器320具备AC/DC转换器300、插头321、壳体322以及输出连接器323,在壳体322中容纳和配置AC/DC转换器300。插头321从未图示的插座接受工业用交流电压V

也可以构成具备AC/DC转换器300的电气设备。图11A和图11B是示出具备AC/DC转换器300的电气设备340的图。虽然图11A和图11B所示的电气设备340为显示装置,但对电气设备340的种类不做特殊限定,只要是内置AC/DC转换器的设备,则可以是任意设备,如音频设备、冰箱、洗衣机、吸尘器等。电气设备340具备AC/DC转换器300、插头341、壳体342以及负载343,且在壳体322中容纳和配置AC/DC转换器300和负载343。插头341从未图示的插座接受工业用交流电压V

《第四实施方式》

下面对本发明的第四实施方式进行说明。在第四实施方式中说明对第一至第三实施方式的一些变形技术等。

如上述,一次侧控制IC10的各电路元件以半导体集成电路的形式形成,通过将该半导体集成电路封入由树脂构成的壳体(封装)中来构成半导体装置。但是,也可以利用多个分立器件来构成与一次侧控制IC10中的电路等同的电路。作为在一次侧控制IC10中包括的电路元件,上述的任意的一些电路元件也可以设于一次侧控制IC10外而与一次侧控制IC10外接。反过来,也可以将作为设于一次侧控制IC10外的电路元件,将上述的一些电路元件设于一次侧控制IC10中。

关于任意的信号或电压,可以以无损于上述主旨的形式,使其高电平与低电平的关系颠倒过来。

也可以实施在N沟道型与P沟道型之间对FET的类型进行替换的变形。

图3所示的一次侧控制IC10作为控制对象开关元件的导通、断开的任意的开关控制装置发挥功能。但是,对象开关元件与对象线圈和检测电阻串联连接,且对对象开关元件和对象线圈与检测电阻的串联电路施加预定的直流电压。因此,在对象开关元件的导通区间,随着从对象开关元件导通后的经过时间的增加,流经对象开关元件的电流增加。虽然对图1的一次侧控制IC10而言的对象开关元件和对象线圈是开关晶体管M1和一次侧绕组W1,但在本发明中,对象开关元件和对象线圈不限于此,可以将本发明广泛适应于通过对象开关元件的开关驱动来控制流经对象线圈的电流的用途。

上述各晶体管可以是任意种类的晶体管。例如,也可以将作为MOSFET所上述的晶体管置换为结型FET、IGBT(Insulated Gate Bipolar Transistor,绝缘栅双极型晶体管)或双极型晶体管。任意的晶体管具有第一电极、第二电极以及控制电极。在FET中,第一电极和第二电极中的一方是漏极,另一方是源极,且控制电极是栅极。在IGBT中,第一电极和第二电极中的一方是集电极,另一方是发射极,且控制电极是栅极。在不属于IGBT的双极型晶体管中,第一电极和第二电极中的一方是集电极,另一方是发射极,且控制电极是基极。

作为成为本发明的开关控制装置的控制对象的开关元件(对象开关元件),主要设想是包括MOSFET的FET或IGBT等电压控制型晶体管(即,根据控制电极上的电压来控制流经第一电极与第二电极之间的电流的晶体管),但也可以将双极型晶体管用作该开关元件(对象开关元件)。

《第五实施方式》

下面对本发明的第五实施方式进行说明。图12是本发明的第五实施方式的驱动装置1100的示意性内部结构图。图13是驱动装置1100的外观图。

驱动装置1100是通过将半导体集成电路封入由树脂构成的壳体(封装)内而形成的电子器件(半导体装置),构成驱动装置1100的各电路由半导体集成化。在作为驱动装置1100的电子器件的壳体中设有暴露于IC10的外部的多个外部端子。此外,图13所示的外部端子的数量只不过是例示。

作为设于驱动装置1100的多个外部端子的一部分,图12中示出了外部端子TM1至TM3。外部端子TM1是输出端子,且由驱动装置1100驱动栅极的晶体管(图12中未图示)等与外部端子TM1外接。外部端子TM2是电源端子,从未图示的电源电路接受直流的电源电压VCC的输入。外部端子TM3是接地端子,与接地端GND连接。接地端指具有0V(零伏)的基准电位的导电部(预定电位点),或指基准电位本身。

驱动装置1100具备内部电源电路1110、控制电路1120、驱动电路1130以及保护电路1140。

内部电源电路1110通过对被输入至电源端子TM2的电源电压VCC进行直流-直流转换来生成1个以上的其他直流电压。这里,认为由内部电源电路1110生成的直流电压中包括内部电源电压Vreg和驱动用电压V

控制电路1120由逻辑电路构成,或由模拟电路和逻辑电路构成。控制电路1120生成驱动控制信号S

驱动电路1130通过输出线OL与输出端子TM1连接,并按照驱动控制信号S

输出端子电压V

输出端子电压V

无论如何,输出端子电压V

保护电路1140具有监视输出端子电压V

如图14A所示,电源故障指诸如以相当低的输出阻抗输出正的电压的电压源与输出端子TM1短路的情况。例如,电源端子TM2与输出端子TM1短路的情况属于电源故障。发生电源故障时,虽然取决于驱动电路1130的状态,但有可能过大的电流从输出端子TM1通过输出线OL继续朝向驱动电路1130流入。

如图14B所示,接地故障指诸如接地端GND与输出端子TM1短路的情况或以相当低的输出阻抗输出负的电压的电压源与输出端子TM1短路的情况。发生接地故障时,虽然取决于驱动电路1130的状态,但有可能过大的电流从驱动电路1130通过输出线OL朝向输出端子TM1继续流出。

因此,当判断为发生电源故障或接地故障时,保护电路1140进行不遵循驱动控制信号S

第五实施方式包括以下实施例EX5_1至EX5_3。在实施例EX5_1至EX5_3中,对驱动电路1130和保护电路1140的结构例和动作例进行说明。

[实施例EX5_1]

下面对实施例EX5_1进行说明。图15中示出实施例EX5_1的驱动电路

1130A和保护电路1140A的结构。在实施例EX5_1中,图15的驱动电路1130A和保护电路1140A被用作图12的驱动电路1130和保护电路1140。

图15的驱动电路1130A具备互相串联连接的晶体管1131、1132和预驱动器1133。晶体管1131被构成为P沟道型MOSFET,晶体管1132被构成为N沟道型MOSFET。但是,也可以实施将晶体管1131构成为N沟道型MOSFET的变形。对晶体管1131和晶体管1132的串联电路施加驱动用电压V

向预驱动器1133输入来自控制电路1120的驱动控制信号S

即,当异常判定信号Sc为低电平且驱动控制信号S

当异常判定信号Sc为低电平且驱动控制信号S

此外,就预驱动器1133而言,为了防止晶体管1131和晶体管1132同时成为导通状态,可以适当插入使晶体管1131和晶体管1132同时为断开状态的死区时间。

保护电路1140A具备比较器1141和1143、电压源1142和1144、判定部1145。电压源1142生成和输出预定的判定电压V

判定电压V

判定电压V

此外,虽然主要设想判定电压V

向比较器1141的非反相输入端子、反相输入端子分别输入输出端子电压V

向比较器1143的反相输入端子、非反相输入端子分别输入输出端子电压V

向判定部1145输入来自控制电路1120的驱动控制信号S

若在未发生电源故障时驱动电路1130A被设为输出低状态,则输出端子电压V

即,当从驱动控制信号S

另外,若在未发生接地故障时驱动电路1130A被设为输出高状态,则输出端子电压V

即,当从驱动控制信号S

异常判定信号Sc一旦被设为高电平,此后,维持异常判定信号Sc上的高电平,直到对包括驱动电路1130A和保护电路1140A的驱动装置1100输入预定的复位信号为止,或者,直到向该驱动装置1100的电源电压VCC的输入被切断为止。或者,也可以是,若异常判定信号Sc由低电平被切换为高电平后经过预定的冷却时间,则使异常判定信号Sc恢复为低电平。

驱动电路1130A在异常判定信号Sc为高电平时不遵循驱动控制信号S

当晶体管1131和晶体管1132中的任一方成为导通时,从输出端子TM1和输出线OL观察到的驱动电路1130A的阻抗非常低(例如,几百毫欧姆Ω)。对此,当晶体管1131和晶体管1132双方均成为断开时,从输出端子TM1和输出线OL观察到的驱动电路1130A的阻抗远高于晶体管1131和晶体管1132中的任一方成为导通时的阻抗(例如,几百兆欧姆)。因此,即使发生电源故障或接地故障,也能够抑制过大的电流的持续地输入输出,抑制包括驱动电路1130A的驱动装置1100的破损或劣化。

在图15中,可以说控制电路1120和保护电路1140A构成控制驱动电路1130A的状态的状态控制部,由状态控制部将驱动电路1130A的状态控制为输出低状态(第一状态)、输出高状态(第二状态)以及Hi-Z状态(第三状态)中的任一状态。当从驱动电路1130A的状态由输出高状态被切换为输出低状态后经过预定时间T

此外,在图15中,虽然采用了向预驱动器1133供给异常判定信号Sc的结构,但也可以将异常判定信号Sc输出至控制电路1120,而不是输出至预驱动器1133,并使控制电路1120成为主体来执行当异常判定信号Sc为高电平时将驱动电路1130A的状态设为Hi-Z状态的保护动作。

另外,在实施例EX5_1中,也可以是只进行电源故障保护和接地故障保护中的任一方。当只进行电源故障保护时,在保护电路1140A中,删除比较器1143和电压源1144,信号Sb始终被视为是低电平。相反地,当只进行接地故障保护时,在保护电路1140A中,删除比较器1141和电压源1142,信号Sa始终被视为是低电平。

[实施例EX5_2]

下面对实施例EX5_2进行说明。图17中示出实施例EX5_2的驱动电路1130B和保护电路1140B的结构。在实施例EX5_2中,图17的驱动电路1130B和保护电路1140B被用作图12的驱动电路1130和保护电路1140。

图17的驱动电路1130B具备互相串联连接的上拉电阻1134、晶体管1135、预驱动器1136。晶体管1135被构成为N沟道型MOSFET。上拉电阻1134的电阻值(例如,几百欧姆至几百千欧姆)远大于晶体管1135的导通电阻的电阻值(例如,几百毫欧姆)。对上拉电阻1134和晶体管1135的串联电路施加驱动用电压V

向预驱动器1136输入来自控制电路1120的驱动控制信号S

即,当异常判定信号Sc为低电平且驱动控制信号S

当异常判定信号Sc为低电平且驱动控制信号S

保护电路1140B具备比较器1141、电压源1142以及判定部1146。保护电路1140B中的比较器1141和电压源1142与保护电路1140A(参照图15)中的比较器1141和电压源1142相同,关于实施例EX5_1的比较器1141和电压源1142的说明也适用于实施例EX5_2。

因此,比较器1141在输出端子电压V

向判定部1146输入来自控制电路1120的驱动控制信号S

若在未发生电源故障时驱动电路1130B被设为输出低状态,则输出端子电压V

即,当从驱动控制信号S

异常判定信号Sc一旦被设为高电平,此后,维持异常判定信号Sc的高电平,直到对包括驱动电路1130B和保护电路1140B的驱动装置1100输入预定的复位信号为止,或者,直到向该驱动装置1100的电源电压VCC的输入被切断为止。或者,也可以是,若异常判定信号Sc由低电平被切换为高电平后经过预定的冷却时间,则使异常判定信号Sc恢复为低电平。

驱动电路1130B在异常判定信号Sc为高电平时不遵循驱动控制信号S

当晶体管1135为导通时,从输出端子TM1和输出线OL观察到的驱动电路1130B的阻抗非常低(例如,几百毫欧姆)。对此,当晶体管1135为断开时,从输出端子TM1和输出线OL观察到的驱动电路1130B的阻抗远高于晶体管1135为导通时的阻抗(与上拉电阻1134的电阻值一致)。因此,即使发生电源故障,也能够抑制过大的电流的持续性的输入,抑制包括驱动电路1130B的驱动装置1100的破损或劣化。

在图17中,可以说控制电路1120和保护电路1140B构成控制驱动电路1130B的状态的状态控制部,由状态控制部将驱动电路1130B的状态控制为输出低状态(第一状态)和输出高状态(第二状态)中的任一状态。当从驱动电路1130B的状态由输出高状态被切换为输出低状态后经过预定时间T

此外,在图17中,虽然采用了向预驱动器1136供给异常判定信号Sc的结构,但也可以将异常判定信号Sc输出至控制电路1120,而不是输出至预驱动器1136,并使控制电路1120成为主体来执行当异常判定信号Sc为高电平时将驱动电路1130B的状态设为输出高状态的保护动作。

[实施例EX5_3]

下面对实施例EX5_3进行说明。图18中示出实施例EX5_3的驱动电路1130C和保护电路1140C的结构。在实施例EX5_3中,图18的驱动电路1130C和保护电路1140C被用作图12的驱动电路1130和保护电路1140。

图18的驱动电路1130C具备互相串联连接的晶体管1137、下拉电阻1138、预驱动器1139。晶体管1137被构成为P沟道型MOSFET。但是,也可以实施将晶体管1137构成为N沟道型MOSFET的变形。下拉电阻1138的电阻值(例如,几百欧姆至几百千欧姆)远大于晶体管1137的导通电阻的电阻值(例如,几百毫欧姆)。对晶体管1137和下拉电阻1138的串联电路施加驱动用电压V

向预驱动器1139输入来自控制电路1120的驱动控制信号S

即,当异常判定信号Sc为低电平且驱动控制信号S

当异常判定信号Sc为低电平且驱动控制信号S

保护电路1140C具备比较器1143、电压源1144以及判定部1147。保护电路1140C中的比较器1143和电压源1144与保护电路1140A(参照图15)中的比较器1143和电压源1144相同,关于实施例EX5_1中的比较器1143和电压源1144的说明也适用于实施例EX5_3。

因此,比较器1143在输出端子电压V

向判定部1147输入来自控制电路1120的驱动控制信号S

若在未发生接地故障时驱动电路1130C被设为输出高状态,则输出端子电压V

即,当从驱动控制信号S

异常判定信号Sc一旦被设为高电平,此后,维持异常判定信号Sc的高电平,直到对包括驱动电路1130C和保护电路1140C的驱动装置1100输入预定的复位信号为止,或者,直到向该驱动装置1100的电源电压VCC的输入被切断为止。或者,也可以是,若异常判定信号Sc由低电平被切换为高电平后经过预定的冷却时间,则使异常判定信号Sc恢复为低电平。

驱动电路1130C在异常判定信号Sc为高电平时不遵循驱动控制信号S

当晶体管1137成为导通时,从输出端子TM1和输出线OL观察到的驱动电路1130C的阻抗非常低(例如,几百毫欧姆)。对此,当晶体管1137成为断开时,从输出端子TM1和输出线OL观察到的驱动电路1130C的阻抗远高于晶体管1137成为导通时的阻抗(与下拉电阻1138的电阻值一致)。因此,即使发生接地故障,也能够抑制过大的电流的持续性的输出,抑制包括驱动电路1130C的驱动装置1100的破损或劣化。

在图18中,可以说控制电路1120和保护电路1140C构成控制驱动电路1130C的状态的状态控制部,由状态控制部将驱动电路1130C的状态控制为输出低状态(第一状态)和输出高状态(第二状态)中的任一状态。当从驱动电路1130C的状态由输出低状态被切换为输出高状态后经过预定时间T

此外,在图18中,虽然采用了向预驱动器1139供给异常判定信号Sc的结构,但也可以将异常判定信号Sc输出至控制电路1120,而不是输出至预驱动器1139,并使控制电路1120成为主体来执行当异常判定信号Sc为高电平时将驱动电路1130C的状态设为输出低状态的保护动作。

《第六实施方式》

下面对本发明的第六实施方式进行说明。第六实施方式以及后述的第七至第九实施方式是以第五实施方式为基础的实施方式,关于在第六至第九实施方式中不另阐述的事项,只要不存在矛盾,第五实施方式的记载也适用于第六至第九实施方式。在第六实施方式中,对于在第五实施方式与第六实施方式之间矛盾的事项,可以是第六实施方式的记载优先(对于后述的第七至第九实施方式也同样)。只要不存在矛盾,可以组合第五至第九实施方式中的任意多个实施方式。进一步地,只要不存在矛盾,可以组合第一至第九实施方式中的任意多个实施方式。

在第六实施方式中,对第五实施方式所示的驱动装置1100的用途的例子进行说明。利用驱动装置1100可以构成绝缘同步整流型DC/DC转换器。第六实施方式的绝缘同步整流型DC/DC转换器与第一实施方式的绝缘同步整流型DC/DC转换器1(图1)相同,以下,将第六实施方式的绝缘同步整流型DC/DC转换器也称为绝缘同步整流型DC/DC转换器1或DC/DC转换器1。在第六实施方式中,DC/DC转换器1的结构和动作如第一实施方式所示,如图1所示,DC/DC转换器1中包括一次侧控制IC10。

可以将第五实施方式的驱动装置1100用作一次侧控制IC10,或者,可以在一次侧控制IC10的结构要素中包括第五实施方式的驱动装置1100。一次侧控制IC10是通过将半导体集成电路封入由树脂构成的壳体(封装)内而形成的电子器件(半导体装置),构成一次侧控制IC10的各电路由半导体集成化。在作为一次侧控制IC10的电子器件的壳体中设有暴露于IC10的外部的多个外部端子。二次侧控制IC20也具有与图2的一次侧控制IC10相同的结构。

作为设于一次侧控制IC10的多个外部端子的一部分,图1中示出了外部端子TM1至TM5。设于一次侧控制IC10的外部端子TM1至TM3相当于第五实施方式所示的外部端子TM1至TM3(参照图12)。外部端子TM1与开关晶体管M1的栅极连接。因此,图12的输出端子电压V

对包括驱动装置1100的一次侧控制IC10,适用实施例EX5_1的结构(图15)。但是,从原理而言,也可以对包括驱动装置1100的一次侧控制IC10采用实施例EX5_2或EX5_3的结构(图17或图18)。

第五实施方式的驱动装置1100与一次侧控制IC10的对应关系如下,即,基于反馈信号V

《第七实施方式》

下面对本发明的第七实施方式进行说明。在第六实施方式中,虽然DC/DC转换器1是绝缘同步整流型DC/DC转换器,但就DC/DC转换器1而言,只要是由施加于一次侧绕组W1的输入电压V

《第八实施方式》

下面对本发明的第八实施方式进行说明。在第八实施方式中,对本发明的绝缘型DC/DC转换器的用途进行说明。

如图9所示,可以构成利用本发明的绝缘型DC/DC转换器的AC/DC转换器300。AC/DC转换器300的结构和动作如第三实施方式所示。可以将第六或第七实施方式的DC/DC转换器1用作AC/DC转换器300中的绝缘型DC/DC转换器304。

进一步地,也可以利用包括第六或第七实施方式的DC/DC转换器1而构成的AC/DC转换器300来形成电源适配器320(参照图10)或电气设备340(参照图11A和图11B)。电源适配器320的结构、动作和电气设备340的结构、动作如上述第三实施方式中所示,第三实施方式的记载也适用于本实施方式。

《第九实施方式》

下面对本发明的第九实施方式进行说明。在第九实施方式中说明对第六至第八实施方式的一些变形技术等。

如上述,一次侧控制IC10の各电路元件以半导体集成电路的形式形成,通过将该半导体集成电路封入由树脂构成的壳体(封装)中来构成半导体装置。但是,也可以利用多个分立器件来构成与一次侧控制IC10中的电路等同的电路。对于驱动装置1100也同样。作为在一次侧控制IC10中包括的电路元件,上述的任意的一些电路元件也可以设于一次侧控制IC10外而与一次侧控制IC10外接。反过来,作为设于一次侧控制IC10外的电路元件,也可以将上述的一些电路元件设于一次侧控制IC10中。

关于任意的信号或电压,可以以无损于上述主旨的形式,使其高电平与低电平的关系颠倒过来。

也可以实施在N沟道型与P沟道型之间对FET的类型进行替换的变形。

驱动装置1100或一次侧控制IC10可以用于有必要在高电平与低电平之间切换输出端子TM1的电压电平的任意的用途。尤其,例如,驱动装置1100或一次侧控制IC10可以作为用于驱动对象晶体管的栅极的栅极驱动装置发挥功能。虽然图1的结构中的对象晶体管是设于绝缘型DC/DC转换器1的一次侧电路的开关晶体管M1,但在本发明中,对象晶体管不限于此。

例如,如图19所示,在通过控制串联地插入于施加预定的直流电源电压V1的线401与负载402之间的输出晶体管403来通过输出晶体管403向负载402供给电力的负载驱动装置400中,可以将输出晶体管403当作对象晶体管。在该负载驱动装置400中,使栅极驱动装置404具有与驱动装置1100或一次侧控制IC10等同的结构,并利用栅极驱动装置404来驱动输出晶体管403的栅极即可。栅极驱动装置404的输出端子TM1与输出晶体管403的栅极连接,栅极驱动装置404可以通过向输出晶体管403的栅极供给脉冲信号(电压V

在图19的结构中,对象晶体管403和负载402串联连接,当对象晶体管403为导通时,通过对象晶体管,基于直流电源电压V1的电流被供给至负载402。

或者,例如,也可以将非绝缘型的开关电源电路中的开关晶体管作为对象晶体管,并对该对象晶体管适用具有与驱动装置1100或一次侧控制IC10等同的结构的栅极驱动装置。

作为一例,图20中示出非绝缘升压型DC/DC转换器420。非绝缘升压型DC/DC转换器420具备以符号421至427表示的各部位。在非绝缘升压型DC/DC转换器420中,向电感器421的一端施加预定的直流输入电压V1,电感器421的另一端与被构成为N沟道型MOSFET的开关晶体管422的漏极连接,并与二极管423的阳极连接。二极管423的阴极与平滑电容器424的一端连接。平滑电容器424的另一端和开关晶体管422的源极与具有0V的基准电位的接地端连接。在二极管423的阴极与平滑电容器1424的连接节点出现直流的输出电压V2。利用分压电阻425、426向栅极驱动装置427供给与输出电压V2对应的反馈电压。栅极驱动装置427基于反馈电压向开关晶体管422的栅极供给脉冲信号来对开关晶体管422进行开关驱动,以使输出电压V2被稳定在高于电压V1的期望的目标电压。此时,将开关晶体管422当作对象晶体管,并将与驱动装置1100或一次侧控制IC10等同的结构适用于栅极驱动装置427。因此,栅极驱动装置427的输出端子TM1与晶体管422的栅极连接,以向晶体管422的栅极施加输出端子电压V

在图1的结构和图20的结构中,对象晶体管(M1或422)和线圈(W1或421)串联连接,当对象晶体管为导通时,通过对象晶体管和线圈,基于直流电压(V

另外,可以对本发明的驱动装置1100的输出端子TM1连接电机等负载。

上述各晶体管可以是任意种类的晶体管。例如,作为MOSFET,也可以将上述的晶体管置换为结型FET、IGBT(Insulated Gate Bipolar Transistor,绝缘栅双极型晶体管)或双极型晶体管。任意的晶体管具有第一电极、第二电极以及控制电极。在FET中,第一电极和第二电极中的一方是漏极,另一方是源极,且控制电极是栅极。在IGBT中,第一电极和第二电极中的一方是集电极,另一方是发射极,且控制电极是栅极。在不属于IGBT的双极型晶体管中,第一电极和第二电极中的一方是集电极,另一方是发射极,且控制电极是基极。

但是,作为上述对象晶体管,优选包括MOSFET的FET或IGBT等电压控制型的输出晶体管(即,根据控制电极的电压来控制流经第一电极与第二电极之间的电流的晶体管),但双极型晶体管也可以成为对象晶体管。

可以在专利请求范围所示的技术思想的范围内适当地对本发明的实施方式实施多种变更。以上实施方式归根结底只是本发明的实施方式的例子,本发明乃至各构成要件的术语的含义不限于在以上实施方式中记载的含义。上述说明书中示出的具体的数值仅仅是例示,显而易见地,可以将其变更为各种各样的数值。