一种嵌入式计算机开机身份认证方法

文献发布时间:2023-06-19 09:36:59

技术领域

本发明涉及但不限于嵌入式计算机信息安全技术领域,尤指一种嵌入式计算机开机身份认证方法。

背景技术

图像信息处理计算机是目标跟踪系统的核心,通常采用DSP+FPGA架构,FPGA实现图像预处理功能,DSP实现目标截获与跟踪。

图像信息处理计算机的软硬件具有较高的经济价值,需要具备信息安全防护措施,使得产品出厂后不被克隆和篡改,但当前的图像信息处理计算机在开机环节存在信息安全漏洞,一是主流的DSP器件没有信息安全防护措施,DSP上电后直接运行外部存放的引导程序,无法对引导程序时否被篡改进行识别,存在软件代码被非法篡改的风险;二是产品中固化的软件与硬件平台没有深度耦合,存在计算机被非法克隆的风险。

针对以上存在的技术风险,可以采用密码技术保障图像信息处理计算机开机环节的信息安全。一是在图像信息处理系统中大量使用了FPGA,部分新型的FPGA芯片内集成bit流解密逻辑,可提供高度的设计安全性;二是密码技术中的SM3和SM4算法可提供对软件代码的加密和防护措施;SM3杂凑(Hash)算法是一种单向密码体制,可以将任意长度的输入经过变化后得到固定长度的输出,具有唯一和不可逆的特性,SM4算法是一个分组对称密钥算法,加密和解密密钥相同,可对大量数据进行批量加密或解密。

因此,如何在图像信息处理计算机等嵌入式计算机中,基于现有硬件平台,引入密码技术,提高产品的信息安全防护非常具有经济效益。

发明内容

本发明的目的是:

本发明实施例提供一种嵌入式计算机开机身份认证方法,以解决现有嵌入式计算机软硬件的非法篡改、克隆等问题,从而达到保护计算机软硬件知识产权的目的。

本发明的技术方案是:本发明实施例提供一种嵌入式计算机开机身份认证方法,所述嵌入式计算机硬件组成至少包括:FPGA,通用处理器,FPGA上电配置存储器,所述FPGA分别与处理器和存储器互联,处理器与存储器之间通过FPGA隔离,其中,FPGA支持密钥存储和bit流加解密,所述存储器中存储有加密FPGA上电配置代码、处理器引导程序和开机授权信息;所述开机身份认证方法包括:

步骤1,计算机上电后,FPGA从存储器中加载加密FPGA上电配置代码;

步骤2,FPGA配置完成后,执行嵌入于加密FPGA上电配置代码中的开机身份认证程序;

步骤3,通过执行开机身份认证程序,将计算机的硬件信息和软件程序分别与开机授权信息进行对比,以对计算机进行开机身份认证。

可选地,如上所述的嵌入式计算机开机身份认证方法中,所述FPGA中运行的软件程序采用FPGA代码实现,开机授权信息的密钥[A]和开机身份认证程序嵌入在所述FPGA代码中。

可选地,如上所述的嵌入式计算机开机身份认证方法中,在执行所述开机身份认证方法之前,还包括:

将嵌入密钥[A]和开机身份认证程序的FPGA代码经FPGA加密软件加密,形成加密FPGA上电配置代码,并将加密FPGA上电配置代码存入FPGA上电配置存储器中。

可选地,如上所述的嵌入式计算机开机身份认证方法中,所述加密FPGA上电配置代码用的密钥[B]保存在FPGA内部的专用存储单元中。

可选地,如上所述的嵌入式计算机开机身份认证方法中,经对称加密算法加密后的开机授权信息存储在存储器的一次编程OTP区域内。

可选地,如上所述的嵌入式计算机开机身份认证方法中,在执行所述开机身份认证方法之前,还包括:

通过处理器执行开机授权程序,以形成开机授权信息,并存储于存储器的OTP区域中;其中,开机授权程序通过仿真器下载至处理器中执行,在计算机的存储器中不存留。

可选地,如上所述的嵌入式计算机开机身份认证方法中,所述处理器执行开机授权程序的步骤,包括:

步骤21,收集计算机中核心器件ID信息,器件至少包括处理器和FPGA;

步骤22,采用哈希加密算法,将收集到的所有器件的ID信息加上自定义信息A,生成签名DATA[A];

步骤23,采用对称密钥算法,使用密钥[A]将步骤23中生成的签名DATA[A]加密生成加密数据DATA[B];

步骤24,采用哈希加密算法,将存储器中存储的处理器引导程序形成签名DATA[C];

步骤25,采用对称密钥算法算法,使用密钥[A]将DATA[C]加密,生成加密数据DATA[D];

(6)通过FPGA将DATA[B]和DATA[D]写入FPGA上电配置FLASH的OTP区域,其中,DATA[B]和DATA[D]为所述开机授权信息。

可选地,如上所述的嵌入式计算机开机身份认证方法中,所述FPGA执行开机身份认证程序,并将计算机的硬件信息和软件程序分别与开机授权信息进行对比的步骤包括:

步骤31,FPGA从存储器的OTP区域中读取加密数据DATA[D],采用对称密钥算法,使用FPGA中嵌入的密钥[A],对DATA[D]进行解密,生产DATA[C];

步骤32,FPGA采用哈希加密算法,将存储器中存储的处理器引导程序形成签名DATA[C*];

步骤33,FPGA比较数据DATA[C]与DATA[C*]是否一致,如果两者均一致,则FPGA从存储器中读取处理器引导程序,并加载到处理器中运行。否则FPGA通过硬件措施将处理器置于复位状态,停止运行;

步骤34,FPGA从存储器的OTP区域中读取加密数据DATA[B],使用FPGA中嵌入的密钥[A],采用对称算法对加密DATA[B]进行解密,生成DATA[A];

步骤35,FPGA读取FPGA内部自身的ID信息,通过处理器引导程序获取处理器自身的ID信息;

步骤36,FPGA采用哈希加密算法,将在步骤35中收集到的ID信息加上自定义信息A,生成签名DATA[A*]。

步骤37,FPGA比较数据DATA[A]与DATA[A*]是否一致,如果两者不一致,FPGA通过处理器复位控制逻辑将处理器置于复位状态,停止处理器运行;如果两者均一致,则处理器继续执行引导程序。

本发明的有益效果是:

本发明实施例提供一种嵌入式计算机开机身份认证方法,基于现有硬件平台,主要功能采用软件和逻辑实现,以FPGA为中心,构建嵌入式计算机开机身份认证方案,非法用户无法获得开机授权程序和开机认证代码,无法通过复制硬件和软件达到克隆使用计算机的目的。主要有以下优点:

(1)开机认证信息保存于FLASH的OTP区域,不占用FLASH扇区地址空间,不影响用户正常使用,且OTP区域只能编程一次,防止非法用户篡改OTP区域写入的信息。

(2)开机认证信息中包含了产品硬件状态的唯一ID信息,每台产品中的开机认证信息不同,开机认证信息必须与计算机软硬件状态一致,每台计算机必须经过认证后才可以正常使用。

(3)非法用户无法获取开机授权程序。开机授权程序不公开,认证信息由生产厂家在产品出厂前加载运行,在产品中不存留。

(4)非法用户无法获取开机授权程序中使用的原始信息。在开机授权程序中使用的用户自定义信息不公开,开机授权程序采用SM3算法对认证信息进行了数字签名,并经过了SM4算法加密,因此,在FLASH中固化的开机认证信息为加密后的信息。

(5)非法用户无法直接获取开机认证代码。开机认证代码嵌入在FPGA代码中,FPGA代码经过加密后烧入FLASH中,非法用户同样无法获取开机认证代码信息。

附图说明

附图用来提供对本发明技术方案的进一步理解,并且构成说明书的一部分,与本申请的实施例一起用于解释本发明的技术方案,并不构成对本发明技术方案的限制。

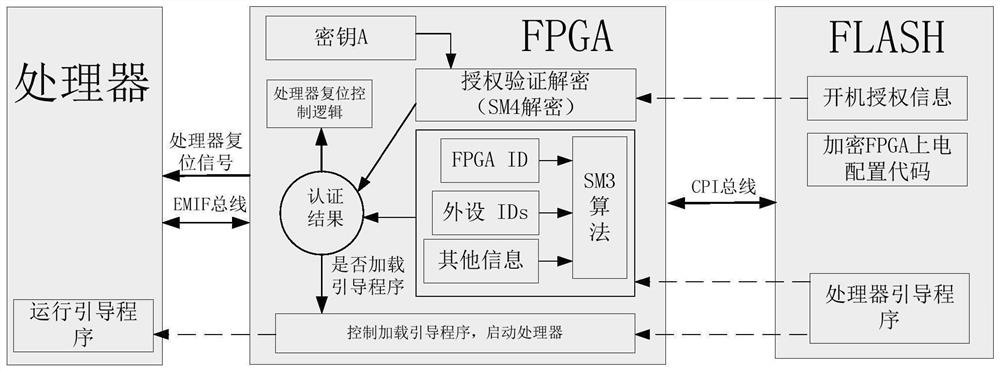

图1为本发明实施例提供的嵌入式计算机开机身份认证方法的原理示意图。

具体实施方式

为使本发明的目的、技术方案和优点更加清楚明白,下文中将结合附图对本发明的实施例进行详细说明。需要说明的是,在不冲突的情况下,本申请中的实施例及实施例中的特征可以相互任意组合。

在附图的流程图示出的步骤可以在诸如一组计算机可执行指令的计算机系统中执行。并且,虽然在流程图中示出了逻辑顺序,但是在某些情况下,可以以不同于此处的顺序执行所示出或描述的步骤。

本发明提供以下几个具体的实施例可以相互结合,对于相同或相似的概念或过程可能在某些实施例不再赘述。

图1为本发明实施例提供的嵌入式计算机开机身份认证方法的原理示意图。本发明实施例提供的嵌入式计算机开机身份认证方法中,嵌入式计算机硬件组成至少包括:FPGA,通用处理器,FPGA上电配置存储器,例如为一FLASH,其中FPGA与处理器互联,FPGA与FLASH互联,处理器与FLASH之间通过FPGA隔离;其中,FPGA支持密钥存储和bit流加解密,处理器引导程序存储在FLASH中,开机授权信息经SM4算法加密后存放在FLASH的一次编程(OTP)区域,加密密钥[A]嵌入在加密FPGA上电配置代码中,加密FPGA上电配置代码使用的密钥[B]保存在FPGA内部的专用存储单元中,例如SRAM或eFUSE中。

软件程序上主要包括两部分,分别为开机授权程序和开机身份认证程序。开机授权程序通过仿真器下载至处理器中执行,在计算机的FLASH中不存留。开机授权程序实现的主要步骤如下:

(1)收集计算机中核心器件ID信息(该ID信息可作为芯片的唯一识别信息,譬如处理器的网口的MAC地址等),器件至少包括处理器和FPGA。

(2)采用哈希加密算法(例如SM3算法),将收集到的所有器件的ID信息加上自定义信息A,生成签名DATA[A]。

(3)采用对称密钥算法(例如SM4算法),使用密钥[A]将步骤2中生成的签名DATA[A]生成加密数据DATA[B]。

(4)采用哈希加密算法(例如SM3算法),将FLASH中存储的处理器引导程序形成签名DATA[C]。

(5)采用对称密钥算法(例如SM4算法),使用密钥[A]将DATA[C]加密,生成加密数据DATA[D]。

(6)通过FPGA将DATA[B]和DATA[D]写入FPGA上电配置FLASH的OTP区域,其中,DATA[B]和DATA[D]为开机授权信息。

开机身份认证程序作为FPGA逻辑的一部分嵌入FPGA逻辑代码,该代码经FPGA加密软件加密后形成加密FPGA bit流(即加密FPGA上电配置代码),同样存入FPGA的上电配置FLSAH中。计算机上电后,FPGA从FLASH中加载加密的逻辑配置位流,FPGA配置完成后,FPGA执行开机身份认证程序。开机身份认证程序实现的主要步骤如下:

(1)FPGA从FLASH的OTP区域中读取加密数据DATA[D],采用SM4算法,使用FPGA中嵌入的密钥[A],对DATA[D]进行解密,生产DATA[C]。

(2)FPGA采用SM3算法,将FLASH中存储的处理器引导程序形成签名DATA[C*]。

(3)FPGA比较数据DATA[C]与DATA[C*]是否一致,如果两者均一致,则FPGA从FLASH中读取处理器引导程序,并加载到处理器中运行。否则FPGA通过硬件措施将处理器置于复位状态,停止运行。

(4)FPGA从FLASH的OTP区域中读取加密数据DATA[B],使用FPGA中嵌入的密钥[A],采用SM4算法对加密DATA[B]进行解密,生成DATA[A]。

(5)FPGA读取FPGA内部自身的ID信息,通过处理器的引导程序获取处理器自身的ID信息。

(6)FPGA采用SM3算法,将在步骤5中收集到的ID信息加上自定义信息A,生成签名DATA[A*]。

(7)FPGA比较数据DATA[A]与DATA[A*]是否一致,如果两者不一致,FPGA通过处理器复位控制逻辑将处理器置于复位状态,停止处理器运行;如果两者均一致,则处理器继续运行引导程序。

需要说明的是,开机授权的过程中,步骤(1)到(3)为计算机中硬件信息的对比和授权认证,(4)到(7)为计算机中软件程序的对比和授权认证。

本发明实施例提供的嵌入式计算机开机身份认证方法,基于现有硬件平台,主要功能采用软件和逻辑实现,以FPGA为中心,构建嵌入式计算机开机身份认证方案,非法用户无法获得开机授权程序和开机认证代码,无法通过复制硬件和软件达到克隆使用计算机的目的。主要有以下优点:

(1)开机认证信息保存于FLASH的OTP区域,不占用FLASH扇区地址空间,不影响用户正常使用,且OTP区域只能编程一次,防止非法用户篡改OTP区域写入的信息。

(2)开机认证信息中包含了产品硬件状态的唯一ID信息,每台产品中的开机认证信息不同,开机认证信息必须与计算机软硬件状态一致,每台计算机必须经过认证后才可以正常使用。

(3)非法用户无法获取开机授权程序。开机授权程序不公开,认证信息由生产厂家在产品出厂前加载运行,在产品中不存留。

(4)非法用户无法获取开机授权程序中使用的原始信息。在开机授权程序中使用的用户自定义信息不公开,开机授权程序采用SM3算法对认证信息进行了数字签名,并经过了SM4算法加密,因此,在FLASH中固化的开机认证信息为加密后的信息。

(5)非法用户无法直接获取开机认证代码。开机认证代码嵌入在FPGA代码中,FPGA代码经过加密后烧入FLASH中,非法用户同样无法获取开机认证代码信息。

以下通过一个具体实施例对本发明实施例提供的嵌入式计算机开机身份认证方法进行详细说明。该具体实施例包括以下内容:

嵌入式计算机的硬件电路组成包括:处理器为Ti公司生产的DSP TMS320C6678,FPGA为Xilinx公司生产的XC7K325T,FLASH为CYPRESS公司生产的S29GL01GT。FPGA与DSP通过EMIF总线互联,FPGA与FLASH通过CPI(Common Flash Interface)总线互联,处理器与FLASH之间通过FPGA隔离。如图1所示。处理器引导程序存储在FLASH中,开机授权信息经SM4算法加密后存放在FLASH的一次编程(OTP)区域,加密密钥[A]嵌入在加密FPGA上电配置代码中,加密FPGA上电配置代码使用的密钥[B]保存在FPGA内部的eFUSE中。

软件设计主要包括两部分,分别为开机授权程序和开机身份认证程序。开机授权程序通过仿真器下载至处理器中执行,在计算机的FLASH中不存留。开机授权程序实现的主要步骤如下:

(1)收集计算机中核心器件ID信息(该ID信息可作为芯片的唯一识别信息,譬如处理器的网口的MAC地址等),器件至少包括处理器和FPGA。

(2)采用SM3算法,将收集到的器件ID信息加上自定义信息A,生成签名DATA[A]。

(3)采用SM4算法,使用密钥[A]将步骤2中生成的签名DATA[A]生成加密数据DATA[B]。

(4)采用SM3算法,将FLASH中存储的有效程序代码形成签名DATA[C]。

(5)采用SM4算法,使用密钥[A]将DATA[C]加密,生成加密数据DATA[D]。

(6)通过FPGA将DATA[B]和DATA[D]写入FPGA上电配置FLASH的OTP区域,其中,DATA[B]和DATA[D]为所述开机授权信息。

开机身份认证程序作为FPGA逻辑的一部分嵌入FPGA逻辑代码,该代码经FPGA加密软件加密后形成加密bit流(即加密FPGA上电配置代码),同样存入FPGA的上电配置FLSAH中。计算机上电后,FPGA从FLASH中加载加密的逻辑配置位流,FPGA配置完成后,FPGA执行开机身份认证程序。开机身份认证程序实现的主要步骤如下:

(1)FPGA从FLASH的OTP区域中读取加密数据DATA[D],采用SM4算法,使用FPGA中嵌入的密钥[A],对DATA[D]进行解密,生产DATA[C]。

(2)FPGA采用SM3算法,将FLASH中存储的有效程序代码形成签名DATA[C*]。

(3)FPGA比较数据DATA[C]与DATA[C*]是否一致,如果两者均一致,则FPGA从FLASH中读取处理器引导程序,并加载到处理器中运行。否则FPGA通过硬件措施将处理器置于复位状态,停止运行。

(4)FPGA从FLASH的OTP区域中读取加密数据DATA[B],使用FPGA中嵌入的密钥[A],采用SM4算法对加密DATA[B]进行解密,生成DATA[A]。

(5)FPGA读取FPGA内部自身的ID信息,通过处理器的引导程序获取处理器自身的ID信息。

(6)FPGA采用SM3算法,将在步骤5中收集到的ID信息加上自定义信息A,生成签名DATA[A*]。

(7)FPGA比较数据DATA[A]与DATA[A*]是否一致,如果两者不一致,FPGA通过处理器复位控制逻辑将处理器置于复位状态,停止处理器运行;如果两者均一致,则处理器继续运行引导程序。

虽然本发明所揭露的实施方式如上,但所述的内容仅为便于理解本发明而采用的实施方式,并非用以限定本发明。任何本发明所属领域内的技术人员,在不脱离本发明所揭露的精神和范围的前提下,可以在实施的形式及细节上进行任何的修改与变化,但本发明的专利保护范围,仍须以所附的权利要求书所界定的范围为准。

- 一种嵌入式计算机开机身份认证方法

- 一种计算机开机身份认证系统及其认证方法