接口信号回环测试方法、装置、计算机设备和存储介质

文献发布时间:2023-06-19 09:41:38

技术领域

本申请涉及计算机技术领域,特别是涉及一种接口信号回环测试方法、装置、计算机设备和存储介质。

背景技术

随着计算机技术的发展,PCIE(peripheral component interconnect express)接口在硬件上的广泛使用,通信终端在人们的生活中越来越普遍,为了保证通信设备建网的完美运行,要求很多设备能够具有回环测试的功能以便能远程监测通信设备运行是否合格。终端设备的芯片或者模组在出厂前均需要进行硬件和接口功能通路测试,所以在通信设备出厂前测试通信设备的回环功能是否合格成为了重要的测试之一。

然而,目前的回环测试方法中,局限于只能测试数据信号,无法测试时钟信号以及参考时钟信号,PCIE接口通路测试时还需要接入主从设备才能进行接口的通路测试,或者需要示波器等辅助设备进行单独的测试,需要花费大量的人力、精力进行测试,容易导致生产芯片的测试效率较低。

发明内容

基于此,有必要针对上述技术问题,提供一种能够提高生产芯片测试效率的接口信号回环测试方法、装置、计算机设备和存储介质。

一种接口信号回环测试方法,所述方法包括:

发送查询指令至已上电的待测试芯片;所述待测试芯片处于低电平状态;

在接收所述待测试芯片返回状态参数的情况下,确定所述待测试芯片对应的信号通道连接成功;

在未接收到所述待测试芯片返回状态参数的情况下,确定所述待测试芯片对应的信号通道连接失败。

在其中一个实施例中,所述待测试芯片对应的信号通道包括数据信号通道和时钟信号通道。

在其中一个实施例中,所述发送查询指令至已上电的待测试芯片之后,所述方法还包括:

检测每个时钟信号对应的接地线路的状态参数;

在检测所述接地线路的状态参数为低电平状态的情况下,确定所述时钟信号对应的链路连接成功;

在检测所述接地线路的状态参数为高阻状态的情况下,则确定所述时钟信号对应的链路连接失败。

一种接口信号回环测试装置,所述装置包括:

发送模块,用于发送查询指令至已上电的待测试芯片;所述待测试芯片处于低电平状态;

确定模块,用于在接收所述待测试芯片返回状态参数的情况下,确定所述待测试芯片对应的信号通道连接成功;在未接收到所述待测试芯片返回状态参数的情况下,确定所述待测试芯片对应的信号通道连接失败。

一种计算机设备,包括存储器和处理器,所述存储器存储有计算机程序,所述处理器执行所述计算机程序时实现以下步骤:

发送查询指令至已上电的待测试芯片;所述待测试芯片处于低电平状态;

在接收所述待测试芯片返回状态参数的情况下,确定所述待测试芯片对应的信号通道连接成功;

在未接收到所述待测试芯片返回状态参数的情况下,确定所述待测试芯片对应的信号通道连接失败。

一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现以下步骤:

发送查询指令至已上电的待测试芯片;所述待测试芯片处于低电平状态;

在接收所述待测试芯片返回状态参数的情况下,确定所述待测试芯片对应的信号通道连接成功;

在未接收到所述待测试芯片返回状态参数的情况下,确定所述待测试芯片对应的信号通道连接失败。

一种接口信号回环测试方法,所述方法包括:

对待测试芯片的每个时钟信号通道对应的管脚进行低电平设置操作后,对所述待测试芯片进行上电操作;

发送查询指令至所述待测试芯片;

在接收所述待测试芯片返回状态参数的情况下,确定所述待测试芯片对应的信号通道连接成功;

在未接收到所述待测试芯片返回状态参数的情况下,确定所述待测试芯片对应的信号通道连接失败。

在其中一个实施例中,所述对待测试芯片的每个时钟信号通道的管脚进行低电平设置操作包括:

对每个时钟信号通道外接预设数值的电阻;

将每个所述时钟信号通道对应的管脚进行接地连接操作。

在其中一个实施例中,所述发送查询指令至所述待测试芯片之后,所述方法还包括:

检测每个时钟信号对应的接地线路的状态参数;

在检测所述接地线路的状态参数为低电平状态的情况下,确定所述时钟信号对应的链路连接成功;

在检测所述接地线路的状态参数为高阻状态的情况下,则确定所述时钟信号对应的链路连接失败。

一种接口信号回环测试装置,所述装置包括:

设置模块,用于对待测试芯片的每个时钟信号通道对应的管脚进行低电平设置操作后,对所述待测试芯片进行上电操作;

发送模块,用于发送查询指令至所述待测试芯片;

确定模块,用于在接收所述待测试芯片返回状态参数的情况下,确定所述待测试芯片对应的信号通道连接成功;在未接收到所述待测试芯片返回状态参数的情况下,确定所述待测试芯片对应的信号通道连接失败。

一种计算机设备,包括存储器和处理器,所述存储器存储有计算机程序,所述处理器执行所述计算机程序时实现以下步骤:

对待测试芯片的每个时钟信号通道对应的管脚进行低电平设置操作后,对所述待测试芯片进行上电操作;

发送查询指令至所述待测试芯片;

在接收所述待测试芯片返回状态参数的情况下,确定所述待测试芯片对应的信号通道连接成功;

在未接收到所述待测试芯片返回状态参数的情况下,确定所述待测试芯片对应的信号通道连接失败。

一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现以下步骤:

对待测试芯片的每个时钟信号通道对应的管脚进行低电平设置操作后,对所述待测试芯片进行上电操作;

发送查询指令至所述待测试芯片;

在接收所述待测试芯片返回状态参数的情况下,确定所述待测试芯片对应的信号通道连接成功;

在未接收到所述待测试芯片返回状态参数的情况下,确定所述待测试芯片对应的信号通道连接失败。

上述接口信号回环测试方法、装置、计算机设备和存储介质,通过发送查询指令至已上电的待测试芯片,待测试芯片处于低电平状态。在接收待测试芯片返回状态参数的情况下,确定待测试芯片对应的信号通道连接成功。在未接收到待测试芯片返回状态参数的情况下,确定待测试芯片对应的信号通道连接失败。由此使得,能够完整的测试生产芯片或者PCIE接口的所有信号,包括数据信号和时钟以及参考时钟信号,避免了需要示波器等辅助设备进行测试的繁琐流程,实现了快速的测试PCIE接口硬件以及内部模块是否通路,从而有效的提高了生产芯片的测试效率。

上述接口信号回环测试方法、装置、计算机设备和存储介质,通过对待测试芯片的每个时钟信号通道对应的管脚进行低电平设置操作后,对待测试芯片进行上电操作。发送查询指令至待测试芯片,在接收待测试芯片返回状态参数的情况下,确定待测试芯片对应的信号通道连接成功。在未接收到待测试芯片返回状态参数的情况下,确定待测试芯片对应的信号通道连接失败。由此使得,通过对PCIE接口的时钟类信号进行低电平设置操作后,能够实现信号硬件通路的验证,避免了需要示波器等辅助设备进行测试的繁琐流程,从而有效的提高了生产芯片的测试效率。

附图说明

图1为一个实施例中接口信号回环测试方法的应用环境图;

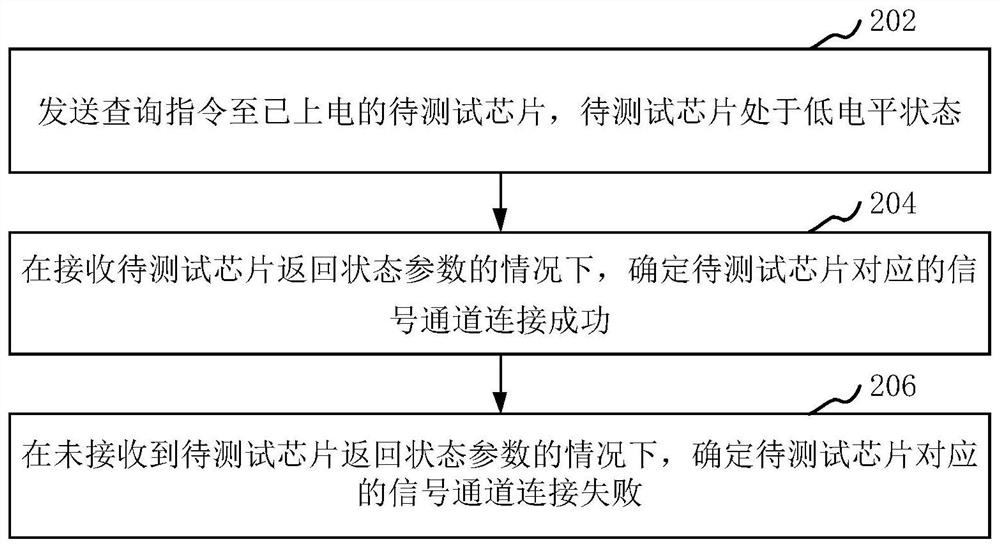

图2为一个实施例中接口信号回环测试方法的流程示意图;

图3A为一个实施例中对某个待测试芯片进行回环测试的示意图;

图3B为一个实施例中检测每个时钟信号对应的接地线路的状态参数步骤的流程示意图;

图4为另一个实施例中接口信号回环测试方法的流程示意图;

图5为一个实施例中对待测试芯片的每个时钟信号通道的管脚进行低电平设置操作步骤的流程示意图;

图6为一个实施例中接口信号回环测试装置的结构框图;

图7为另一个实施例中接口信号回环测试装置的结构框图;

图8为一个实施例中计算机设备的内部结构图。

具体实施方式

为了使本申请的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本申请进行进一步详细说明。应当理解,此处描述的具体实施例仅仅用以解释本申请,并不用于限定本申请。

本申请提供的接口信号回环测试方法,可以应用于如图1所示的应用环境中。其中,终端102通过网络与待测试芯片104通过网络进行通信。终端102发送查询指令至已上电的待测试芯片104,待测试芯片104处于低电平状态。终端102在接收待测试芯片104返回状态参数的情况下,确定待测试芯片104对应的信号通道连接成功。终端102在未接收到待测试芯片104返回状态参数的情况下,确定待测试芯片104对应的信号通道连接失败。其中,终端102可以但不限于是各种个人计算机、笔记本电脑、智能手机、平板电脑和便携式可穿戴设备。

在一个实施例中,如图2所示,提供了一种接口信号回环测试方法,以该方法应用于图1中的终端为例进行说明,包括以下步骤:

步骤202,发送查询指令至已上电的待测试芯片,待测试芯片处于低电平状态。

PCI-Express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准,它原来的名称为“3GIO”,是由英特尔在2001年提出的,旨在替代旧的PCI,PCI-X和AGP总线标准。PCIe属于高速串行点对点双通道高带宽传输,所连接的设备分配独享通道带宽,不共享总线带宽,主要支持主动电源管理,错误报告,端对端的可靠性传输,热插拔以及服务质量(QOS)等功能。

PCIe交由PCI-SIG(PCI特殊兴趣组织)认证发布后才改名为“PCI-Express”,简称“PCI-e”。它的主要优势就是数据传输速率高,而且还有相当大的发展潜力。PCI-e接口是一种高速通讯接口,可用于板集间通讯,也可用于板卡间通讯。随着PCI-e接口在硬件上广泛使用,芯片或者模组在出厂前均需要进行硬件和接口功能通路测试,所以在通信设备出厂前测试通信设备的回环功能是否合格成为了重要的测试之一。在芯片或者模组在出厂前,工作人员可以利用测试工具对生产的芯片进行通路测试,以确保出厂后的芯片能正常工作。

具体的,以终端作为测试设备举例说明。终端可以发送查询指令至已上电的待测试芯片,待测试芯片处于低电平状态。其中,已上电的待测试芯片是指对待测试芯片进行上电操作,即对待测试芯片进行正常电压范围的供电操作,使其能够正常启动工作。低电平状态是指对待测芯片的信号进行低电平设置的操作,使其处于低电平状态。例如,用户终端可以通过AT命令,即用户可以通过AT命令为AT+GTSET=“PCIEQU”,0手动发送查询命令即可。

步骤204,在接收待测试芯片返回状态参数的情况下,确定待测试芯片对应的信号通道连接成功。

当终端发送查询指令至已上电的待测试芯片之后,终端在接收到待测试芯片返回状态参数的情况下,确定待测试芯片对应的信号通道连接成功。具体的,终端发送查询指令至已上电的待测试芯片之后,当PCI-e回环测试成功时,会返回状态参数pcieloopback ok,即当用户终端接收到待测试芯片返回的状态参数值时,即可确定待测试芯片对应的信号通道连接成功,即当用户看到返回值之后,即可确认PCIE回环测试成功。

步骤206,在未接收到待测试芯片返回状态参数的情况下,确定待测试芯片对应的信号通道连接失败。

当终端发送查询指令至已上电的待测试芯片之后,终端在未接收到待测试芯片返回状态参数的情况下,确定待测试芯片对应的信号通道连接失败。具体的,终端发送查询指令至已上电的待测试芯片之后,当PCI-e回环测试成功时,会返回状态参数pcieloopbackok,即当用户终端接收到待测试芯片返回的状态参数值时,即可确定待测试芯片对应的信号通道连接成功,即当用户看到返回值之后,即可确认PCI-e回环测试成功,如果回环测试不成功,则不会返回该数据,即当用户终端没有接收到待测试芯片返回的状态参数值时,即可确定待测试芯片对应的信号通道连接失败,即当用户没有看到返回值时,即可确认PCI-e回环测试失败。本申请中通过对待测试芯片或模块内部的PCIE模块进行寄存器的配置,将模块内部的PCIE时序设置成RC模块,即实现PCIE通讯的目的,从而能够快速验证是否达到通路状态。其中,寄存器配置是指对待测试芯片内部的电路进行高低电平的配置。

传统的PCI-e接口回环测试方法中限制于只能测试数据信号,无法测试时钟信号以及参考时钟信号,产线上测试时钟信号和参考时钟信号时还需要代码逻辑或者示波器等辅助设备进行单独的测试,导致产线上对生产芯片测试的效率较低,对于模组或者芯片生产线上,使用者关心的是能否高效稳定的测试PCI-e接口的回环是否成功。本实施例中,通过发送查询指令至已上电的待测试芯片,待测试芯片处于低电平状态。在接收待测试芯片返回状态参数的情况下,确定待测试芯片对应的信号通道连接成功。在未接收到待测试芯片返回状态参数的情况下,确定待测试芯片对应的信号通道连接失败。由此使得,能够完整的测试生产芯片或者PCIE接口的所有信号,包括数据信号和时钟以及参考时钟信号,避免了需要示波器等辅助设备进行测试的繁琐流程,实现了快速高效的测试PCIE接口硬件以及内部模块是否通路,从而有效的提高了生产芯片的测试效率。

在一个实施例中,待测试芯片对应的信号通道包括数据信号通道和时钟信号通道。如图3A所示,为对某个待测试芯片进行回环测试的示意图。PCIE接口传输的信号属于差分信号,故RXO_P与RXO_M分别表示接收信号的正和负。TXO_P与TXO_M分别表示发送信号的正和负。R表示recvice,即接收信号。T表示send,即发送信息。PCIE协议进行通讯时,需要把接收信号和发送信号进行连接,使得测试设备可以对收发信号进行测试,发送信号和接收信号统称为数据信号。例如,回环测试时将RX类信号和TX类信号进行短接,利用终端测试出该数据信号的硬件通路是否正常,在进行回环测试时,ioctl会返回测试数据,该测试数据就是PCIE连接状态的相关信息。Data link是指PCIE接口数据已连接状态。同时,本申请实施例中还可以对时钟信号即CLK类的信号进行硬件通路的验证。例如,回环测试时将CLK类的信号和外部设备连接,并将CLK类的信号进行接地操作,利用测试终端对CLK类的信号的接地线路进行检测操作,避免了需要示波器等辅助设备进行测试的繁琐流程,从而实现了对CLK类信号的硬件通路的验证。本实施例中不仅对Rx和Tx类的信号进行短接,然后进行数据的收发操作,同时,通过对CLK信号类进行接地操作,终端也可以对CLK类信号的接地进行对应的检测操作,从而实现了快速高效的对信号的硬件通路进行验证。

在一个实施例中,如图3B所示,发送查询指令至已上电的待测试芯片之后,该方法还包括检测每个时钟信号对应的接地线路的状态参数的步骤,具体包括:

步骤302,检测每个时钟信号对应的接地线路的状态参数。

步骤304,在检测接地线路的状态参数为低电平状态的情况下,确定时钟信号对应的链路连接成功。

步骤306,在检测接地线路的状态参数为高阻状态的情况下,则确定时钟信号对应的链路连接失败。

当终端发送查询指令至已上电的待测试芯片之后,终端可以检测每个时钟信号对应的接地线路的状态参数。具体的,终端可以检测每个时钟信号对应的接地线路的状态参数。在终端检测到接地线路的状态参数为低电平状态的情况下,确定时钟信号对应的链路连接成功。在终端检测到接地线路的状态参数为高阻状态的情况下,则确定时钟信号对应的链路连接失败。其中,对待测试芯片进行上电操作之前,可以对硬件进行相应的调整。例如,如图3A所示,可在产线等夹具上给PCIE_CLK_REQ、REF_CLK_P以及REF_CLK_M信号分别外接50欧姆的电阻,并接地信号,接地信号是指将该管脚或者信号在电路板上进行接地连接操作,接地信号的作用就是对该信号进行拉低电平操作。对上述调整后的待测试芯片或者模块进行上电操作后,正常启动。进一步的,终端可以检测上述PCIE_CLK_REQ、REF_CLK_P以及REF_CLK_M每个时钟信号对应的接地线路的状态参数。在终端检测到PCIE_CLK_REQ信号对应的接地线路的状态参数为低电平状态的情况下,确定PCIE_CLK_REQ信号对应的链路连接成功。在终端检测到REF_CLK_M对应的接地线路的状态参数为高阻状态的情况下,则确定REF_CLK_M信号对应的链路连接失败。由此使得,通过使用寄存器配置以及对硬件的电阻值的调整,完整的模拟出PCIE网卡设备,能够完整的测试出芯片或者PCIE所有信号,包含数据信号和时钟以及参考时钟信号,实现了对所有信号的硬件通路的验证,从而有效的提高了生产芯片测试效率。

在一个实施例中,如图4所示,提供了一种接口信号回环测试方法,以该方法应用于图1中的终端为例进行说明,包括以下步骤:

步骤402,对待测试芯片的每个时钟信号通道对应的管脚进行低电平设置操作后,对待测试芯片进行上电操作。

步骤404,发送查询指令至待测试芯片。

步骤406,在接收待测试芯片返回状态参数的情况下,确定待测试芯片对应的信号通道连接成功。

步骤408,在未接收到待测试芯片返回状态参数的情况下,确定待测试芯片对应的信号通道连接失败。

终端可以对待测试芯片的每个时钟信号通道对应的管脚进行低电平设置操作后,对待测试芯片进行上电操作。其中,待测试芯片可以安装在终端设备中。终端发送查询指令至已上电的待测试芯片,在终端接收到待测试芯片返回状态参数的情况下,确定待测试芯片对应的信号通道连接成功。在终端未接收到待测试芯片返回状态参数的情况下,确定待测试芯片对应的信号通道连接失败。由此使得,通过对PCIE接口的时钟类信号进行低电平设置操作后,能够实现信号硬件通路的验证,避免了需要示波器等辅助设备进行测试的繁琐流程,从而有效的提高了生产芯片的测试效率。

在一个实施例中,如图5所示,对待测试芯片的每个时钟信号通道的管脚进行低电平设置操作的步骤包括:

步骤502,对每个时钟信号通道外接预设数值的电阻。

步骤504,将每个时钟信号通道对应的管脚进行接地连接操作。

终端可以对待测试芯片的每个时钟信号通道对应的管脚进行低电平设置操作后,对待测试芯片进行上电操作。具体的,终端可以对每个时钟信号通道外接预设数值的电阻,并将每个时钟信号通道对应的管脚进行接地连接操作。例如,预设数值的电阻可以设置为50欧姆的电阻,接地电阻的作用是为了防止电力或电子等设备遭雷击而采取的保护性措施。其中,接地操作是用于对每个时钟信号通道对应的管脚外部进行低电平设置的操作。例如,终端可以对产线等夹具上的时钟信号即CLK类的信号进行硬件通路的验证。例如,PCIE_CLK_REQ、REF_CLK_P以及REF_CLK_M信号分别表示参考时钟信号。可在产线等夹具上给PCIE_CLK_REQ、REF_CLK_P以及REF_CLK_M信号分别外接预设数值为50欧姆的电阻,并将PCIE_CLK_REQ、REF_CLK_P以及REF_CLK_M每个时钟信号通道对应的管脚进行接地连接操作,对上述进行接地连接操作的待测试芯片或者模块进行上电操作后,正常启动。进一步的,终端可以检测上述PCIE_CLK_REQ、REF_CLK_P以及REF_CLK_M每个时钟信号对应的接地线路的状态参数。由此使得,通过使用寄存器配置以及对硬件的电阻值的调整,完整的模拟出PCIE网卡设备,能够高效的测试出芯片或者PCIE所有信号,包含数据信号和时钟以及参考时钟信号,实现了对所有信号的硬件通路的验证,从而有效的提高了生产芯片测试效率。

在一个实施例中,发送查询指令至待测试芯片之后,该方法还包括检测每个时钟信号对应的接地线路的状态参数的步骤,具体包括:

检测每个时钟信号对应的接地线路的状态参数。

在检测接地线路的状态参数为低电平状态的情况下,确定时钟信号对应的链路连接成功。

在检测接地线路的状态参数为高阻状态的情况下,则确定时钟信号对应的链路连接失败。

终端发送查询指令至已上电的待测试芯片之后,终端可以检测每个时钟信号对应的接地线路的状态参数。具体的,终端可以检测每个时钟信号对应的接地线路的状态参数。在终端检测到接地线路的状态参数为低电平状态的情况下,确定时钟信号对应的链路连接成功。在终端检测到接地线路的状态参数为高阻状态的情况下,则确定时钟信号对应的链路连接失败。其中,对待测试芯片进行上电操作之前,可以对硬件进行相应的调整。例如,可在产线等夹具上给PCIE_CLK_REQ、REF_CLK_P以及REF_CLK_M信号分别外接50欧姆的电阻,并接地信号。对上述调整后的待测试芯片或者模块进行上电操作后,正常启动。进一步的,终端可以检测上述PCIE_CLK_REQ、REF_CLK_P以及REF_CLK_M每个时钟信号对应的接地线路的状态参数。在终端检测到PCIE_CLK_REQ信号对应的接地线路的状态参数为低电平状态的情况下,确定PCIE_CLK_REQ信号对应的链路连接成功。在终端检测到REF_CLK_M对应的接地线路的状态参数为高阻状态的情况下,则确定REF_CLK_M信号对应的链路连接失败。由此使得,通过使用寄存器配置以及对硬件的电阻值的调整,完整的模拟出PCIE网卡设备,能够完整的测试出芯片或者PCIE所有信号,包含数据信号和时钟以及参考时钟信号,实现了对所有信号的硬件通路的验证,从而有效的提高了生产芯片测试效率。

应该理解的是,虽然图1-5的流程图中的各个步骤按照箭头的指示依次显示,但是这些步骤并不是必然按照箭头指示的顺序依次执行。除非本文中有明确的说明,这些步骤的执行并没有严格的顺序限制,这些步骤可以以其它的顺序执行。而且,图1-5中的至少一部分步骤可以包括多个步骤或者多个阶段,这些步骤或者阶段并不必然是在同一时刻执行完成,而是可以在不同的时刻执行,这些步骤或者阶段的执行顺序也不必然是依次进行,而是可以与其它步骤或者其它步骤中的步骤或者阶段的至少一部分轮流或者交替地执行。

在一个实施例中,如图6所示,提供了一种接口信号回环测试装置,包括:发送模块602和确定模块604,其中:

发送模块602,用于发送查询指令至已上电的待测试芯片,待测试芯片处于低电平状态。

确定模块604,用于在接收待测试芯片返回状态参数的情况下,确定待测试芯片对应的信号通道连接成功;在未接收到待测试芯片返回状态参数的情况下,确定待测试芯片对应的信号通道连接失败。

在一个实施例中,该装置还包括:检测模块。

检测模块用于检测每个时钟信号对应的接地线路的状态参数;在检测接地线路的状态参数为低电平状态的情况下,确定时钟信号对应的链路连接成功;在检测接地线路的状态参数为高阻状态的情况下,则确定时钟信号对应的链路连接失败。

在一个实施例中,如图7所示,提供了一种接口信号回环测试装置,包括:设置模块702、发送模块704和确定模块706,其中:

设置模块702,用于对待测试芯片的每个时钟信号通道对应的管脚进行低电平设置操作后,对待测试芯片进行上电操作。

发送模块704,用于发送查询指令至待测试芯片。

确定模块706,用于在接收待测试芯片返回状态参数的情况下,确定待测试芯片对应的信号通道连接成功;在未接收到待测试芯片返回状态参数的情况下,确定待测试芯片对应的信号通道连接失败。

在一个实施例中,该装置还包括:连接模块。

连接模块用于对每个时钟信号通道外接预设数值的电阻,将每个时钟信号通道对应的管脚进行接地连接操作。

在一个实施例中,该装置还包括:检测模块。

检测模块用于检测每个时钟信号对应的接地线路的状态参数;在检测接地线路的状态参数为低电平状态的情况下,确定时钟信号对应的链路连接成功;在检测接地线路的状态参数为高阻状态的情况下,则确定时钟信号对应的链路连接失败。

关于接口信号回环测试装置的具体限定可以参见上文中对于接口信号回环测试方法的限定,在此不再赘述。上述接口信号回环测试装置中的各个模块可全部或部分通过软件、硬件及其组合来实现。上述各模块可以硬件形式内嵌于或独立于计算机设备中的处理器中,也可以以软件形式存储于计算机设备中的存储器中,以便于处理器调用执行以上各个模块对应的操作。

在一个实施例中,提供了一种计算机设备,该计算机设备可以是终端,其内部结构图可以如图8所示。该计算机设备包括通过系统总线连接的处理器、存储器、通信接口、显示屏和输入装置。其中,该计算机设备的处理器用于提供计算和控制能力。该计算机设备的存储器包括非易失性存储介质、内存储器。该非易失性存储介质存储有操作系统和计算机程序。该内存储器为非易失性存储介质中的操作系统和计算机程序的运行提供环境。该计算机设备的通信接口用于与外部的终端进行有线或无线方式的通信,无线方式可通过WIFI、运营商网络、NFC(近场通信)或其他技术实现。该计算机程序被处理器执行时以实现一种接口信号回环测试方法。该计算机设备的显示屏可以是液晶显示屏或者电子墨水显示屏,该计算机设备的输入装置可以是显示屏上覆盖的触摸层,也可以是计算机设备外壳上设置的按键、轨迹球或触控板,还可以是外接的键盘、触控板或鼠标等。

本领域技术人员可以理解,图8中示出的结构,仅仅是与本申请方案相关的部分结构的框图,并不构成对本申请方案所应用于其上的计算机设备的限定,具体的计算机设备可以包括比图中所示更多或更少的部件,或者组合某些部件,或者具有不同的部件布置。

在一个实施例中,提供了一种计算机设备,包括存储器、处理器及存储在存储器上并可在处理器上运行的计算机程序,处理器执行计算机程序时实现上述各个方法实施例的步骤。

本领域普通技术人员可以理解实现上述实施例方法中的全部或部分流程,是可以通过计算机程序来指令相关的硬件来完成,所述的计算机程序可存储于一非易失性计算机可读取存储介质中,该计算机程序在执行时,可包括如上述各方法的实施例的流程。其中,本申请所提供的各实施例中所使用的对存储器、存储、数据库或其它介质的任何引用,均可包括非易失性和易失性存储器中的至少一种。非易失性存储器可包括只读存储器(Read-Only Memory,ROM)、磁带、软盘、闪存或光存储器等。易失性存储器可包括随机存取存储器(Random Access Memory,RAM)或外部高速缓冲存储器。作为说明而非局限,RAM可以是多种形式,比如静态随机存取存储器(Static Random Access Memory,SRAM)或动态随机存取存储器(Dynamic Random Access Memory,DRAM)等。

以上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

以上所述实施例仅表达了本申请的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本申请构思的前提下,还可以做出若干变形和改进,这些都属于本申请的保护范围。因此,本申请专利的保护范围应以所附权利要求为准。

- 接口信号回环测试方法、装置、计算机设备和存储介质

- 芯片接口的测试方法、装置、计算机设备和存储介质