电路结构体及电气连接箱

文献发布时间:2023-06-19 10:32:14

技术领域

本发明涉及安装有半导体元件的电路结构体及具备该电路结构体的电气连接箱。

本申请主张基于在2018年9月3日提出申请的日本申请第2018-164663号的优先权,并援引所述日本申请记载的全部的记载内容。

背景技术

一直以来,在汽车搭载有从电源向前照灯、雨刷等负载分配电力的电气连接箱。电气连接箱具备连接于电源而构成电力电路的母排、具有控制所述电力电路的控制电路的电路基板。在电力电路具备进行电力的供给/切断的开关元件等。

专利文献1提出了一种将弯曲的电路导体利用注塑树脂覆盖而生成的注塑成型基板,所述电路导体的一部分从注塑树脂露出,且露出的这样的一部分与注塑树脂齐平,由此能够进行丝网印刷的注塑成型基板。

在先技术文献

专利文献

专利文献1:日本特开2015-138881号公报

发明内容

本公开的一形态涉及的电路结构体并列设置有多个半导体元件,所述半导体元件具备多个第一端子和与所述第一端子并列设置的至少一个第二端子,其中,所述电路结构体具备:第一导电片,与各半导体元件的所述第一端子连接;多个连接部,沿所述半导体元件的并列设置方向并列设置,将一端连接于各半导体元件的所述第一端子,将所述第一端子与所述第一导电片连接;绝缘部,设置在所述连接部彼此之间;及导电部,设置于所述绝缘部,与所述第二端子连接。

本公开的一形态的电气连接箱具备:上述的电路结构体;及控制电路基板,控制所述电路结构体的所述半导体元件。

附图说明

图1是表示本实施方式的电气连接箱的外观的立体图。

图2是本实施方式的电气连接箱的分解图。

图3是本实施方式的电路结构体的分解图。

图4是将图3的方形的虚线部放大后的放大图。

图5是图4的V-V线的纵向剖视图。

图6是图4的VI-VI线的纵向剖视图。

图7是说明本实施方式的电路结构体的制造方法的说明图。

图8是说明本实施方式的电路结构体的制造方法的说明图。

图9是说明本实施方式的电路结构体的制造方法的说明图。

图10是说明本实施方式的电路结构体的制造方法的说明图。

图11是说明本实施方式的电路结构体的制造方法的说明图。

图12是说明本实施方式的电路结构体的制造方法的说明图。

具体实施方式

[本公开要解决的课题]

另一方面,在使用MOSFET(Metal Oxide Semiconductor Field EffectTransistor:金属氧化物半导体场效应晶体管)等半导体开关元件的情况下,需要将漏极端子、源极端子、栅极端子分别连接在不同的母排上。

通常,开关元件的端子排列中,将源极端子与栅极端子直线状地并列设置,对应于端子间距而以规定间隙分别配置母排。而且,在与漏极端子有关的母排中,也与源极端子、栅极端子涉及的母排隔开规定间隙地配置。

然而,近年来,伴随着开关元件的小型化,端子间距不断变小,使母排彼此相邻的配置在物理上变得困难。而且,在并列设置多个开关元件的情况下,母排的配置更加困难。

然而,在专利文献1的电子元件搭载用基板中,也未考虑这样的问题,无法解决。

因此,目的在于提供一种在将具有狭小的端子间距的多个半导体元件并列设置的情况下能够进行高精度的配线的电路结构体及电气连接箱。

[本公开的效果]

根据本公开的一形态,能够提供一种在将具有狭小的端子间距的多个半导体元件并列设置的情况下可进行高精度的配线的电路结构体及电气连接箱。

[本发明的实施方式的说明]

首先列举本公开的实施形态进行说明。而且,也可以将以下记载的实施方式的至少一部分任意组合。

(1)本公开的一形态涉及的电路结构体并列设置有多个半导体元件,所述半导体元件具备多个第一端子和与所述第一端子并列设置的至少一个第二端子,其中,所述电路结构体具备:第一导电片,与各半导体元件的所述第一端子连接;多个连接部,沿所述半导体元件的并列设置方向并列设置,将一端连接于各半导体元件的所述第一端子,将所述第一端子与所述第一导电片连接;绝缘部,设置在所述连接部彼此之间;及导电部,设置于所述绝缘部,与所述第二端子连接。

在本形态中,使所述第一端子连接于所述连接部,使所述第二端子连接于所述导电部,所述导电部在设置于所述连接部彼此之间的所述绝缘部内设置。因此,即使将所述第一端子及所述第二端子间的间距狭小的多个半导体元件并列设置的情况下,也能够高精度地配线,能够防止在所述第一端子的配线及所述第二端子的配线间发生短路等的情况。

(2)本公开的一形态涉及的电路结构体中,各连接部为弯曲的矩形板状,所述绝缘部具有与各连接部的所述一端卡合的梳齿状部。

在本形态中,所述绝缘部的所述梳齿状部与各接合部的所述一端卡合,因此所述绝缘部存在于所述连接部彼此之间。因此,即使将所述第一端子及所述第二端子间的间距狭小的多个半导体元件并列设置的情况下,也能够高精度地配线,能够防止在所述第一端子的配线及所述第二端子的配线间发生短路等的情况。

(3)本公开的一形态涉及的电路结构体中,所述第一导电片及所述多个连接部形成为一体。

在本形态中,所述第一导电片及所述多个连接部形成为一体。因此,所述第一导电片及所述多个连接部之间的连接点消失,能够降低它们之间的电阻。

(4)本公开的一形态涉及的电路结构体中,各连接部的与所述第一端子连接的所述一端侧的端面与在所述绝缘部中形成有所述导电部的导电面齐平。

在本形态中,所述绝缘部中形成有所述导电部的所述导电面与所述连接部中与所述第一端子连接的所述一端侧的端面齐平。因此,在一个半导体元件中,并列设置的所述第一端子及所述第二端子能够容易地配线。

(5)本公开的一形态涉及的电路结构体中,所述电路结构体具备第二导电片,该第二导电片设置成与所述绝缘部的所述导电面齐平,在与所述连接部的并列设置方向交叉的方向上与所述连接部分离第一间隔地配置,各半导体元件的第三端子与所述第二导电片连接。

在本形态中,所述第二导电片与所述连接部分离第一间隔地配置,所述第三端子与所述第一端子及所述第二端子被绝缘。而且,所述第二导电片与所述绝缘部的所述导电面齐平,因此能够将一个半导体元件具备的所述第一端子、所述第二端子及所述第三端子配线在同一面上。

(6)本公开的一形态涉及的电路结构体中,所述绝缘部为矩形,所述绝缘部在一边部的除了两端之外的部分形成有所述梳齿状部,所述绝缘部在所述一边部的两端侧设置有间隔维持部,该间隔维持部维持所述第一导电片与所述第二导电片之间的所述第一间隔。

在本形态中,维持所述第一导电片与所述第二导电片之间的所述第一间隔的所述间隔维持部设置于所述绝缘部中未形成所述梳齿状部的所述一边部的两端侧,即所述一边部中未设置所述半导体元件的部位。因此,能够事先防止由于半导体元件的发热而以所述间隔维持部膨胀的情况为起因的问题。

(7)本公开的一形态涉及的电路结构体中,在与所述多个连接部的并列设置方向交叉的方向上,在所述连接部与所述绝缘部的所述梳齿状部之间形成第二间隔。

在本形态中,在所述连接部与所述绝缘部的所述梳齿状部之间,在与所述多个连接部的并列设置方向交叉的方向上形成所述第二间隔。因此,例如,在半导体元件发热的情况下,所述连接部能够向与所述多个连接部的并列设置方向交叉的方向变形,能够缓和应力。

(8)本公开的一形态涉及的电气连接箱具备:上述中的任一个电路结构体;及控制电路基板,控制所述电路结构体的所述半导体元件。

在本形态中,所述控制电路基板控制所述电路结构体的所述半导体元件,使所述电路结构体适当动作。

[本发明的实施方式的详情]

关于本发明,基于表示其实施方式的附图进行具体说明。以下,参照附图,说明本公开的实施方式的电路结构体及电气连接箱。需要说明的是,本发明没有限定为这些例示,由权利要求书公开,并意图包含与权利要求书等同的意思及范围内的全部变更。

以下,列举将本实施方式的电路结构体及电气连接箱适用于从电源向前照灯、雨刷等负载分配电力的电气连接箱的情况为例进行说明。

图1是表示本实施方式的电气连接箱100的外观的立体图,图2是本实施方式的电气连接箱100的分解图。

本实施方式的电气连接箱100呈大致箱体的形状,具备控制电路基板9、收容控制电路基板9的电路结构体10、覆盖电路结构体10的盖80、隔着电路结构体10而设置在与盖80相反的一侧并对电路结构体10发出的热量进行散热的散热片90。散热片90通过将螺钉70插入于在电路结构体10的四个角形成的贯通孔60并与在散热片90的四个角形成的螺纹孔91螺合而安装于电路结构体10。

在电路结构体10并列设置有多个半导体元件71~77(参照图3)。以下,为了便于说明,将半导体元件71~77也仅称为半导体元件7。而且,半导体元件71~77具有相同结构,因此为了便于说明而列举半导体元件71的情况为例进行说明,省略关于半导体元件72~77的说明。

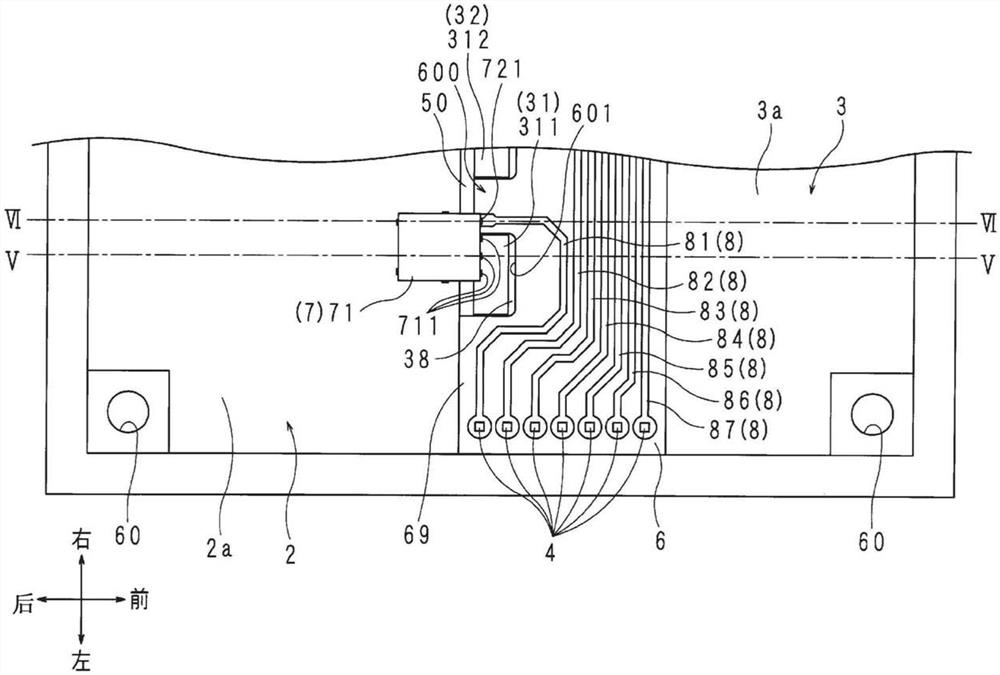

图3是本实施方式的电路结构体10的分解图,图4是将图3的方形的虚线部放大的放大图。

各半导体元件7例如为FET(更具体而言为面安装类型的功率MOSFET),具有三个源极端子711(第一端子)、栅极端子721(第二端子)及漏极端子731(参照图5及图6)。三个源极端子711与栅极端子721直线状地并列设置,漏极端子731(第三端子)设置在半导体元件7的下侧。

半导体元件71~77跨于第一通电体3(一体构件)和第二通电体2地安装,该第一通电体3具备第一母排3a(第一导电片),该第二通电体2具备第二母排2a(第二导电片)。即,在与半导体元件71~77的并列设置方向交叉的方向(前后方向)上,将第一通电体3与第二通电体2隔开规定的间隔50(第一间隔)地配置,将各半导体元件7的一端与第一通电体3连接,将与所述一端相对的另一端与第二通电体2连接。半导体元件71~77固定于第二通电体2。

第一通电体3及第二通电体2例如以大致矩形的各自的上表面齐平的方式配置。在这样的状态下,第一通电体3及第二通电体2收容于框体11内。第一通电体3的第一母排3a及第二通电体2的第二母排2a以各自的长度方向与框体11的长度方向一致的方式配置。框体11包围第一通电体3及第二通电体2的侧面而进行保持。

框体11为中空矩形,沿上下方向具有规定的厚度。与控制电路基板9连接的连接器端子5沿厚度方向贯通框体11的右侧侧壁地设置,一端向框体11的内侧突出,另一端向框体11的外侧突出。在框体11的右侧侧壁的外侧安装有对连接器端子5的另一端进行保护的圆筒形的壳体51。

第一通电体3由第一母排3a、绝缘部6及连接部31~37(连接部)构成。在第一通电体3设有从第一母排3a的前侧(长边侧)的侧面垂直立起的端子板39(参照图8)。端子板39与电源(蓄电池)或负载(前照灯、雨刷等)连接。端子板39贯通框体11的前侧的侧壁并向框体11的外侧突出。

在第二通电体2设有端子板21(参照图8),该端子板21从第二母排2a的后侧(长边侧)的侧面垂直立起。端子板21与电源(蓄电池)或负载(前照灯、雨刷等)连接。端子板21贯通框体11的后侧的侧壁并向框体11的外侧突出。

图5是图4的V-V线的纵向剖视图,图6是图4的VI-VI线的纵向剖视图。在前后方向上,第一通电体3的后侧的端部与第二通电体2的前侧的端部隔着间隔50相对。由此,将第一通电体3及第二通电体2绝缘。

第一通电体3在上表面中在前后方向的后侧半部设有绝缘部6。绝缘部6由例如PPS(聚苯硫醚)那样的耐热性高的热塑性树脂构成。而且,第一通电体3在前后方向的前侧半部设置第一母排3a。第一母排3a例如由纯铜或铜合金构成,在上表面实施镀镍。

绝缘部6为大致矩形板状,例如为绝缘基板。在绝缘部6的后侧的边缘(一边部)设有与半导体元件71~77的源极端子连接的连接部31~37。连接部31~37对于每个半导体元件7而与三个源极端子分别连接。例如,连接部31与半导体元件71的三个源极端子711连接(参照图4)。

更详细而言,绝缘部6在后侧的边缘,在除了两端部之外的部分形成有梳齿状部600(参照图9)。在梳齿状部600中,在绝缘部6的后侧的边缘的除了两端部之外的部分且与连接部31~37对应的部分形成有缺口部601~607。缺口部601~607是仿形于连接部31~37的一端部的矩形。

连接部31~37的所述一端部与梳齿状部600卡合。即,连接部31~37的各自的一端部分别位于缺口部601~607的内侧。由此,绝缘部6存在于连接部31~37彼此之间,进行连接部31~37彼此之间的绝缘。

连接部31~37例如呈弯曲成C字状的矩形板状,在内侧形成有空间61。连接部31~37沿着半导体元件71~77的并列设置方向,即,沿左右方向以等间隔并列设置。连接部31~37将一端与半导体元件71~77的源极端子连接,将另一端与第一母排3a连接。

连接部31~37的一端侧的端面311~317为矩形,在端面311~317连接半导体元件71~77的源极端子。例如,在连接部31的端面311连接半导体元件71的三个源极端子711。

另外,如上所述,绝缘部6的梳齿状部600与连接部31~37的所述一端部卡合,从而在连接部31~37彼此之间设置绝缘部6。即,在连接部31~37的端面311~317彼此之间、连接部31~37的端面311~317和第一母排3a之间设置绝缘部6。连接部31~37例如由纯铜或铜合金构成。

绝缘部6例如使用榫钉(未图示)或设置于框体11的内侧面的定位部(未图示),配置于连接部31~37的内侧。设有后述的导电部8的绝缘部6的上表面68(导电面)与连接部31~37的所述一端侧的端面311~317齐平(参照图5)。

在连接部31~37与绝缘部6的梳齿状部600之间形成有规定的间隔38(第二间隔)。详细而言,各连接部31~37在与连接部31~37的并列设置方向交叉的方向,即在前后方向上,从梳齿状部600的缺口部601~607的缘分离第二间隔38。

需要说明的是,将连接部31~37及第一母排3a一体地形成。例如,在对纯铜或铜合金的板材实施了镀镍处理之后,通过切断、切削、冲压加工等而一体形成。由此,在本实施方式的电路结构体10中,在第一通电体3处所谓连接点消失,能够降低电阻。

本实施方式的电路结构体10并不局限于此,也可以分别设置连接部31~37及第一母排3a而构成第一通电体3。

在绝缘部6的上表面68,导电部8呈线状地设置。导电部8例如为铜箔。在绝缘部6的上表面68,在左侧的端部突出设有与控制电路基板9连接的销状的多个连接端子4。导电部8将各半导体元件7的栅极端子分别连接于各连接端子4。

即,半导体元件71~77分别利用导电部81~87与各连接端子4连接。例如,也可以是,绝缘部6为绝缘基板,导电部81~87为在绝缘部6的上表面68印制的图案。

本实施方式并不局限于此。例如,各导电部81~87也可以由相互不干涉地形成于绝缘部6的上表面68的槽部和在上述的槽部的内侧设置的导电材料构成。

详细而言,各槽部从与固定于第二通电体2的各半导体元件71~77的栅极端子匹配的位置至分别对应的连接端子4凹陷设置,在各槽部内也可以涂布导电材料例如铜纳米粒子墨液。

这样,各连接端子4经由导电部81~87与各半导体元件71~77的栅极端子连接。

连接端子4与控制电路基板9连接,将控制电路基板9发送的对半导体元件71~77进行控制的控制信号经由导电部81~87向各半导体元件71~77的栅极端子传送。由此,控制半导体元件71~77,控制从第一通电体3向第二通电体2或者从第二通电体2向第一通电体3的通电。

如上所述,连接部31~37(半导体元件71~77)在绝缘部6中并列设置于后侧的边缘部(梳齿状部600),在所述边缘部中设置于除了左右方向的两端的部分。

另一方面,绝缘部6在后侧的边缘部的左右方向的两端具有间隔维持部69,该间隔维持部69维持第一母排3a与第二母排2a之间的间隔50。间隔维持部69在绝缘部6的所述边缘部的左右方向的两端部,向第二母排2a侧,换言之向第二通电体2及第一通电体3的分离方向突出设置间隔50。而且,并不局限于此,也可以将间隔维持部69的一部分介于间隔50。

这样,在本实施方式的电路结构体10中,从半导体元件71~77的位置分离地在绝缘部6的所述边缘部的左右方向的两端部设置间隔维持部69。因此,能够将在半导体元件71~77发热时由于间隔维持部69发生热膨胀而产生的问题等防患于未然。

在第二通电体2(第二母排2a)固定有半导体元件71~77。第二母排2a为矩形的板状,在上表面,在前侧的边缘部并列设置有半导体元件71~77。半导体元件71~77在下方具备漏极端子,因此通过将漏极端子例如钎焊于第二母排2a而将半导体元件71~77固定于第二母排2a。

例如,在半导体元件71中,漏极端子731钎焊于第二母排2a的前侧的边缘部。由此,将半导体元件71连接于第二母排2a,并固定于第二母排2a。

在控制电路基板9形成有电路图案,安装有微型计算机或控制IC等控制元件。控制电路基板9连接于连接端子4及连接器端子5。控制电路基板9根据经由连接器端子5输入的指示信号,将对半导体元件71~77的开闭进行控制的控制信号经由连接端子4及导电部81~87向半导体元件71~77发送。

由于具有以上那样的结构,因此本实施方式的电路结构体10即使在将具有多个端子且端子间的间距狭小的半导体元件7并列设置多个的情况下,也能够高精度地进行半导体元件7的各端子涉及的配线。

具体而言,在本实施方式的电路结构体10中,对于半导体元件7的源极端子进行基于连接部31~37的配线,对于栅极端子进行基于绝缘部6的导电部81~87的配线,由此能够高精度地进行配线,能够防止在源极端子的配线与栅极端子的配线间发生短路的情况。

此外,导电部8设置于绝缘部6,通过对导电部8进行图案化,能够将多个配线集中设置。

另外,本实施方式的电路结构体10如上所述,连接部31~37弯曲成C字状,在内侧形成有空间61。因此,连接部31~37的所述一端部能够沿上下方向变形。

此外,各连接部31~37在左右方向上在与梳齿状部600的缺口部601~607的缘之间形成第二间隔38,在与第二通电体2的第二母排2a之间形成间隔50。因此,连接部31~37的所述一端部能够沿前后方向变形。

根据以上的情况,在半导体元件71~77发热时,对应于这样的发热能够变形,能够缓和应力。而且,也能够应对由半导体元件71~77的发热引起的第二母排2a的膨胀。

以下,说明本实施方式的电路结构体10的制造方法。图7~图12是说明本实施方式的电路结构体10的制造方法的说明图。

首先,对由纯铜或铜合金构成且厚度为2~3mm的板材的表面实施镀镍处理,切断成规定的形状,成形第一通电体3及第二通电体2。特别是对于第一通电体3,成形为梳型之后,对于应成为连接部31~37的部分实施弯曲加工。此时,以连接部31~37的端面311~317齐平的方式进行弯曲加工。

将第一通电体3、第二通电体2及连接器端子5配置在嵌入成型用模具内,利用注塑成形机进行一体成型。成形树脂使用PPS(聚苯硫醚)那样的耐热性高的热塑性树脂。由此,成形中空矩形的框体11,以第二通电体2的上表面与连接部31~37的端面311~317齐平的方式配置。

将印刷有导电部8(例如,配线图案)的绝缘部6装配于第一通电体3的上侧且连接部31~37的内侧。

在第二通电体2的边缘部具备焊料安装用焊盘,并列在连接部31~37的端面311~317的附近。需要说明的是,在绝缘部6预先钎焊连接端子4。

在安装半导体元件71~77时,在焊接漏极端子的第二通电体2、焊接源极端子的连接部31~37的端面311~317、及绝缘部6的安装用焊盘涂布焊料膏剂40。然后,载置半导体元件71~77,利用回流焊炉进行钎焊。

由此,将半导体元件71~77的漏极端子与第二通电体2接合,将半导体元件71~77的源极端子接合于第一通电体3的连接部31~37的端面311~317。而且,将连接部31~37的栅极端子与绝缘部6的导电部8接合。

接下来,在形成于控制电路基板9的规定位置的通孔部(参照图3)钎焊连接端子4及连接器端子5。

应考虑的是本次公开的实施方式在全部的点上为例示而不是限制性内容。本发明的范围不是由上述的意思而由权利要求书公开,并意图包含与权利要求书等同的意思及范围内的全部变更。

标号说明

2 第二通电体

2a 第二母排

3 第一通电体

3a 第一母排

4 连接端子

5 连接器端子

6 绝缘部

7 半导体元件

8 导电部

9 控制电路基板

10 电路结构体

11 框体

21 端子板

31~37 连接部

38 第二间隔

39 端子板

50 间隔

51 壳体

61 空间

68 上表面

69 间隔维持部

71~77 半导体元件

80 盖

81~87 导电部

100 电气连接箱

311~317 端面

600 梳齿状部

711 源极端子

721 栅极端子

731 漏极端子。

- 电路结构体、电气连接箱及电路结构体的制造方法

- 电路结构体及电气连接箱