一种基于FDSOI技术的比特单元和存储器

文献发布时间:2023-06-19 11:21:00

技术领域

本发明涉及存储技术领域,具体涉及一种基于FDSOI技术的比特单元和存储器。

背景技术

计算机中存储数据的最小单位是bit,又称比特,每个比特单元存储一位二进制数据,每八位二进制数据组成一个字节。对于存储芯片来讲,开发一套合适的比特单元,对于存储芯片的时序收敛、物理收敛以及PPA(performance Power Area)都非常重要。在不同的比特单元的制造工艺上,都会有不同面积的比特单元可供选择。在先进工艺上,比特单元的面积都是以微米平方为单位,就比特单元的面积来说,比特单元的面积越大,读写速度越快,功耗也就越高。

目前,随着半导体技术的发展,比特单元的开发设计主要集中在平面体硅(BulkSilicon)工艺和之后的鳍式场效应晶体管(FinFET)工艺上,对于全耗尽绝缘体上硅(FDSOI)工艺,往往只是简单的将平面体硅工艺上的比特单元直接沿用到全耗尽绝缘体上硅工艺上,并没有利用全耗尽绝缘体上硅(FDSOI)特有的工艺特点对比特单元进行优化和改良,进而使利用全耗尽绝缘体上硅(FDSOI)工艺设计的比特单元在低速读写模式或者闲置模式下的功耗较高。

发明内容

鉴于背景技术的不足,本发明是提供了一种基于FDSOI技术的比特单元,所要解决的技术问题是目前利用全耗尽绝缘体上硅工艺设计的比特单元在低速读写模式或者闲置模式下的功耗较高。

为解决以上技术问题,本发明提供了如下技术方案:一种基于FDSOI技术的比特单元,包括第一NMOS管、第二NMOS管、第三NMOS管、第四NMOS管、第一PMOS管和第二PMOS管;第一NMOS管、第二NMOS管、第三NMOS管、第四NMOS管、第一PMOS管和第二PMOS管均为FDSOI器件。

第一NMOS管的栅极和第二NMOS管的栅极分别接入到数据线上,所述第一NMOS管的漏极接到第一比特线上,所述第二NMOS管的漏极接到第二比特线上;

第一NMOS管的源极分别和第一PMOS管的栅极、第三NMOS管的栅极、第二PMOS管的漏极和第四NMOS管的漏极电连接;所述第二NMOS管的源极分别和第一PMOS管的漏极、第三NMOS管的漏极、第二PMOS管的栅极和第四NMOS管的栅极电连接;

第三NMOS管的源极和第四NMOS管的源极分别接地,所述第一PMOS管的源极和第二PMOS管的源极分别接入第一电源;

第一NMOS管的衬底引线分别和第二NMOS管的衬底引线、第三NMOS管的衬底引线和第四NMOS管的衬底引线电连接,所第一PMOS管的衬底引线和第二PMOS管的衬底引线电连接。

作为进一步的技术方案,第一NMOS管的衬底引线输入第二电源,所述第一PMOS管的衬底引线输入第三电源。

更进一步地,比特单元在进行读写时第二电源的电压幅值和第一电源的电压幅值相同,第三电源的电压幅值为OV。

作为进一步的技术方案,比特单元在低压操作或者是维持状态时第一NMOS管的衬底引线输入电压值为负值的第一驱动电压,第一PMOS管的衬底引线输入电压值为正值的第二驱动电压。

一种基于FDSOI技术的存储器,应用上述的一种基于FDSOI技术的比特单元。

在实际使用时,由于第一至第四NMOS管和第一至第二PMOS管的衬底引线分别接入电源,使第一至第四NMOS管、第一至第二PMOS管的衬底接入反向偏压,可以降低本发明在进行低速读写时的操作电压和维持电压,远远小于采用平面体硅工艺设计的比特单元在使用时所需要的操作电压和维持电压。

本发明与现有技术相比所具有的有益效果是:在利用绝缘体上硅工艺设计比特单元时,通过对比特单元的MOS管的衬底引线接入反向偏压,可以降低比特单元在进行低速读写时的操作电压和维持电压,进而降低功耗。

附图说明

本发明有如下附图:

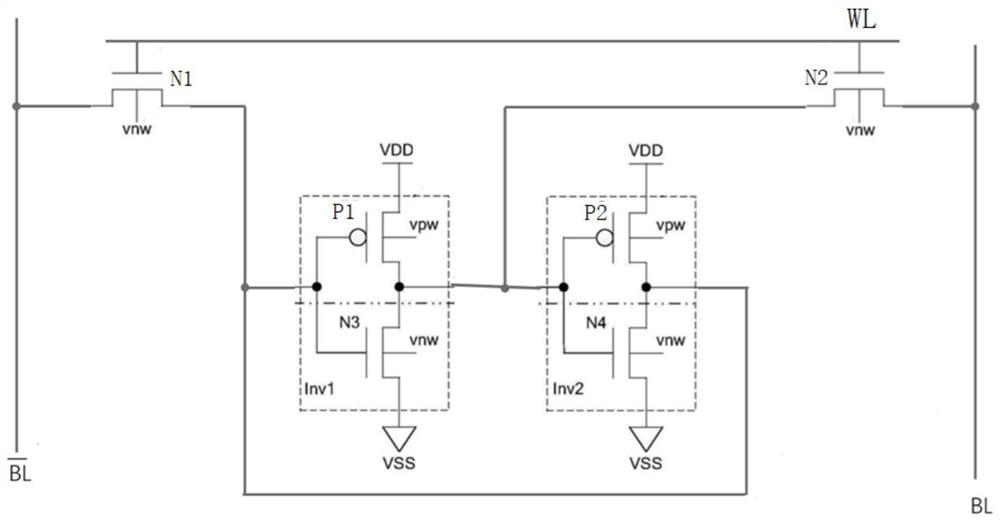

图1为本发明的比特单元的电路示意图。

具体实施方式

现在结合附图对本发明作进一步详细的说明。这些附图均为简化的示意图,仅以示意方式说明本发明的基本结构,因此其仅显示与本发明有关的构成。

如图1所示,一种基于FDSOI技术的比特单元,包括第一NMOS管N1、第二NMOS管N2、第三NMOS管N3、第四NMOS管N4、第一PMOS管P1和第二PMOS管P2;第一NMOS管、第二NMOS管、第三NMOS管、第四NMOS管、第一PMOS管和第二PMOS管均为FDSOI器件。

第一NMOS管N1的栅极和第二NMOS管N2的栅极分别接入到数据线WL上,第一NMOS管N1的漏极接到第一比特线BL|上,第二NMOS管N2的漏极接到第二比特线BL上;

第一NMOS管N1的源极分别和第一PMOS管P1的栅极、第三NMOS管N3的栅极、第二PMOS管P2的漏极和第四NMOS管N3的漏极电连接;第二NMOS管N2的源极分别和第一PMOS管P1的漏极、第三NMOS管N3的漏极、第二PMOS管P2的栅极和第四NMOS管N4的栅极电连接;

第三NMOS管N3的源极和第四NMOS管N4的源极分别接地,第一PMOS管P1的源极和第二PMOS管P2的源极分别接入第一电源VDD;

第一NMOS管N1的衬底引线、第二NMOS管N2的衬底引线、第三NMOS管N3的衬底引线和第四NMOS管N4的衬底引线分别接入第二电源vnw,第一PMOS管P1的衬底引线和第二PMOS管P2的衬底引线分别接入第三电源vpw。

在实际应用的过程中,比特单元在进行读写时第二电源vpw的电压幅值和第一电源VDD的电压幅值相同,第三电源vnw的电压幅值为OV。

在实际应用过程中,比特单元在低压操作或者是维持状态时比特单元在低压操作或者是维持状态时,第二电源的电压幅值是负值,第三电源的电压幅值是正值。

在实际应用过程中,比特单元的面积是0.108平方微米。

在实际使用时,由于第一至第四NMOS管N4和第一至第二PMOS管P2的衬底引线分别接入电源,使第一至第四NMOS管N4、第一至第二PMOS管P2的衬底接入反向偏压,可以降低本发明在进行低速读写时的操作电压和维持电压,远远小于采用平面体硅工艺设计的比特单元在使用时所需要的操作电压和维持电压。

一种基于FDSOI技术的存储器,应用上述的一种基于FDSOI技术的比特单元。由于上述的比特单元中的NMOS管和PMOS管分别接入反向偏压,能够降低比特单元在进行低速读写时的操作电压和维持电压,进而降低功耗,因此本发明中的存储器在实际使用时的功耗同样得到降低。

上述依据本发明为启示,通过上述的说明内容,相关工作人员完全可以在不偏离本项发明技术思想的范围内,进行多样的变更以及修改。本项发明的技术性范围并不局限于说明书上的内容,必须要根据权利要求范围来确定其技术性范围。

- 一种基于FDSOI技术的比特单元和存储器

- 一种基于电加工技术的相变存储器单元制备方法