产生标准单元库版图的方法

文献发布时间:2023-06-19 11:57:35

技术领域

本发明涉及集成电路软件技术领域,特别涉及一种产生标准单元库版图的方法。

背景技术

一般建立标准单元库的方法是在EDA辅助设计的工具环境中,使用电路设计流程去完成,最常见的流程是包括从标准单元线路设计开始至版图设计完成的一个流程。现有的如授权公告号CN107784136B的发明专利提出的建立标准单元库方法,由于标准单元库的种类和个数众多,约有1000个,若每一个新的标准单元都用这种方法来建立的话,费时费力;如授权公告号CN102279899B的发明专利提出的对精简标准单元库进行优化的方法,可以挑选需要的才做,或者如申请公布号为CN108846160 A的发明专利提出的标准单元库电路设计方法,选择一个已有工艺对应的标准单元库作为模板来减少工作量;但这些方法均是在EDA辅助设计的工具环境中,需要电路设计工程师和版图设计工程师一起完成标准单元的设计,费时费力。

发明内容

本发明的目的在于提供一种产生标准单元库版图的方法,以解决现有建立标准单元库的方法费时费力的问题。

为解决上述技术问题,本发明提供一种产生标准单元库版图的方法,包括:

将版图设计规则和电路设计参数输入至版图算法资料库,以利用所述版图算法资料库检测标准单元的各版图布局是否符合所述版图设计规则,并检测标准单元的各版图布局的电性规格是否符合使用要求;以及,

将符合所述版图设计规则以及电性规格符合使用要求的版图布局存储至标准单元库版图中。

可选的,在所述的产生标准单元库版图的方法中,所述版图算法资料库通过多个含内嵌算法的程序整合得到,不同的所述含内嵌算法的程序对应于不同的标准单元和布局方式。

可选的,在所述的产生标准单元库版图的方法中,所述利用版图算法资料库检测标准单元的各版图布局是否符合晶圆厂设计规则的方法包括:

利用相应所述内嵌算法将固定版图布局的每一个几何图形根据版图标准GDSII格式规定,按所述版图设计规则,逐个利用算法的方式来描述;

对于每个所述描述,利用指定算式检查是否符合设计规则。

可选的,在所述的产生标准单元库版图的方法中,所述利用版图算法资料库检测标准单元的各版图布局的电性规格是否符合使用要求的方法包括:

根据输入的所述电路设计参数,利用相应所述内嵌算法计算固定版图布局的规格参数值;以及,

根据计算得到的所述规格参数值,判断电性规格是否满足符合使用要求。

可选的,在所述的产生标准单元库版图的方法中,所述产生标准单元库版图的方法还包括:

若一固定版图布局的电性规格不符合晶圆厂设计规则,则依据电性规格规定调整所述内嵌算法中用于电路设计的规格参数变量,并重新执行所述含内嵌算法的程序,以判断所述固定版图布局是否符合晶圆厂设计规则,若符合,则将所述固定版图布局存储至所述标准单元库版图。

可选的,在所述的产生标准单元库版图的方法中,所述内嵌算法的程序利用获取不同算法子程序的组合方式来执行。

可选的,在所述的产生标准单元库版图的方法中,在将所述版图设计规则输入至所述版图算法资料库之前,所述产生标准单元库版图的方法还包括:

将所述版图设计规则的说明文本按预设规则转换为算法程序语言。

可选的,在所述的产生标准单元库版图的方法中,所述版图设计规则的文本包括版图层次资讯,所述预设规则包括第一规则,所述第一规则为:

Layer表示当前行为版图的层次;

XXX表示层次号码的3个整数位,不足部分补零;

DataType表示版图层次类型;

xxx表示层次类型的3个整数位,不足部分补零;

KeyName是版图层次名称的关键字,依据版图层次资讯表格中的关键字书写。

可选的,在所述的产生标准单元库版图的方法中,所述版图设计规则的文本包括版图设计规则资讯,所述预设规则包括第二规则,所述第二规则为:RuleXXXxxxNNNisddddNote;其中,

Rule表示当前行为版图层次的设计规则;

XXX表示版图层次号码的3个整数位号码,不足部分补零;

xxx表示层次类型的3个整数位,不足部分补零;

NNN表示设计规则的3个整数位编码,不足部分补零

dddd表示设计规则的4个整数位数值,单位是奈米,不足部分补零。

本发明还提供另一种产生标准单元库版图的方法,包括:

将版图设计规则输入至版图算法资料库,以利用所述版图算法资料库检测标准单元的各版图布局是否符合晶圆厂设计规则;

利用电路仿真软件获取晶圆厂提供的元器件模型,得到仿真的结果以判断标准单元的各版图布局是否符合电性规格;以及,

将符合晶圆厂设计规则以及电性规格符合使用要求的版图布局存储至标准单元库版图中。

综上所述,本发明提供的产生标准单元库版图的方法,首先,将版图设计规则和电路设计参数输入至版图算法资料库,以利用所述版图算法资料库检测标准单元的各版图布局是否符合晶圆厂设计规则,并检测标准单元的各版图布局的电性规格是否符合使用要求;或者,将版图设计规则输入至版图算法资料库,以利用所述版图算法资料库检测标准单元的各版图布局是否符合晶圆厂设计规则;利用电路仿真软件获取晶圆厂提供的元器件模型,得到仿真的结果以判断标准单元的各版图布局是否符合电性规格;而后将符合晶圆厂设计规则以及电性规格符合使用要求的版图布局存储至标准单元库版图中。与现有技术相比,具有如下优势:

(1)因无需版图工程师人工制定,直接生成,因此提高了版图生成速度;

(2)不需要版图编辑EDA工具。

附图说明

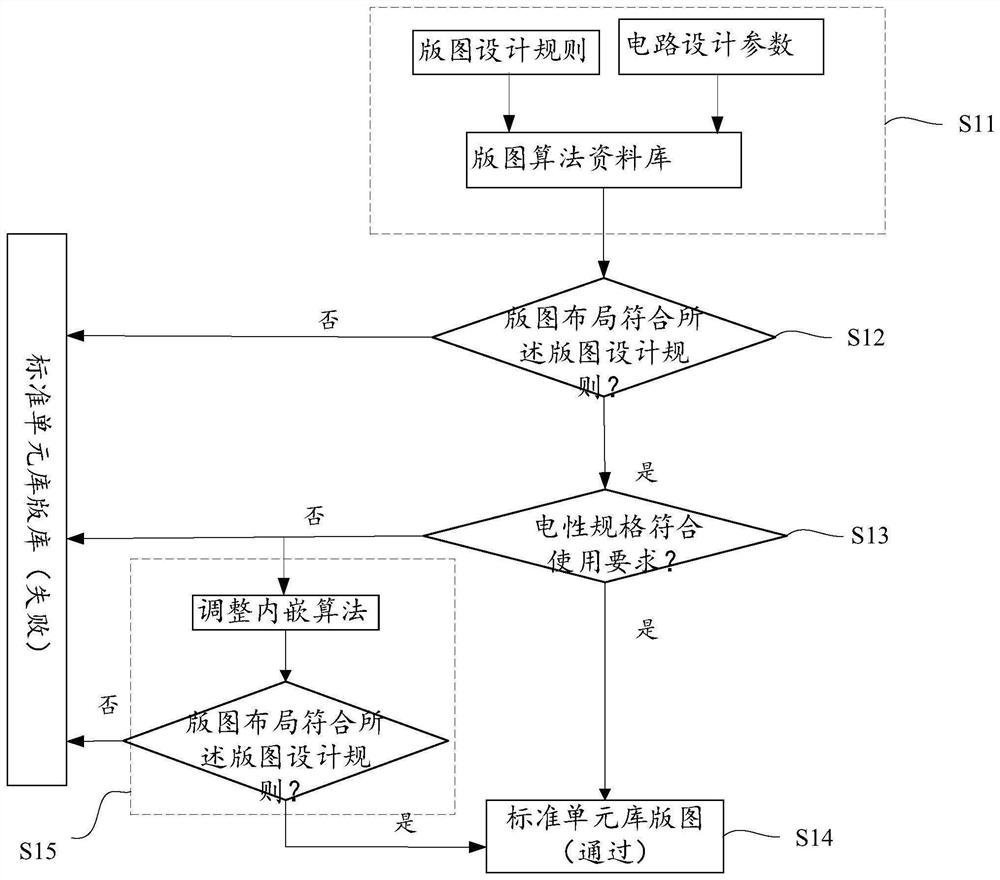

图1为本发明实施例一提供的产生标准单元库版图的方法的流程图;

图2为本发明实施例二提供的产生标准单元库版图的方法的流程图。

具体实施方式

为使本发明的目的、优点和特征更加清楚,以下结合附图和具体实施例对本发明作详细说明。需说明的是,附图均采用非常简化的形式且未按比例绘制,仅用以方便、明晰地辅助说明本发明实施例的目的。此外,附图所展示的结构往往是实际结构的一部分。特别的,各附图需要展示的侧重点不同,有时会采用不同的比例。

【实施例一】

如图1所示,本实施例提供一种产生标准单元库版图的方法,该方法包括如下步骤:

S11,将版图设计规则和电路设计参数输入至版图算法资料库;

S12,利用所述版图算法资料库检测标准单元的各版图布局是否符合所述版图设计规则;

S13,利用所述版图算法资料库检测标准单元的各版图布局的电性规格是否符合使用要求;

S14,将所述版图设计规则以及电性规格符合使用要求的版图布局存储至标准单元库版图中。

传统产生标准单元库版图的方法需在EDA辅助设计的工具环境中,由电路设计工程师和版图工程师合作一起完成上千个标准单元,费时费力,而本实施例提供的所述产生标准单元库版图的方法是在版图算法资料库中,利用内嵌算法,直接产生上千个标准单元的版图,因此,与传统方法相比,产生版图快,节省了人力,且不需要EDA辅助设计的工具。

本实施例中,所述版图设计规则是指标准单元版图需要遵守的晶圆厂设计规则;所述电路设计参数是指使用到元器件电性参数;对于不同标准单元和布局方式,有各自对应的算法,因此,本实施例中,所述版图算法资料库可通过对多个含内嵌算法的程序整合得到,不同的所述含内嵌算法的程序对应于不同的标准单元和布局方式,另外,由于标准单元和布局有许多重复相同部分,因此,所述含内嵌算法的程序可以利用获取不同子程序的组合方式来执行。

一般的,晶圆厂都会提供版图设计规则的说明文本,以及完成版图后,检视是否遵守设计规则的脚本。而晶圆厂提供的文本一般以例如表1和表2所示的表格文档形式存在,为了便于所述版图算法资料库能够对晶圆厂提供的版图设计规则的说明文本的内容进行读取,本实施例中,较佳的,在将版图设计规则输入至版图算法资料库之前,将所述版图设计规则的说明文本按预设规则转换为算法程序语言。

晶圆厂设计规则文档包括两部分资讯:(1)如表1所示的版图层次资讯;(2)如表2所示的版图设计规则资讯。

以下基于表1和表2示例的晶圆厂设计规则文档对上述过程进行说明。

表1

本实施例中,在对晶圆厂提供的如表1所示的版图层次资讯进行格式转为时,可采用第一规则为:LayerXXXDataTypexxx KeyName;其中,

Layer表示当前行为版图的层次;

XXX表示层次号码的3个整数位,不足部分补零;

DataType表示版图层次类型;

xxx表示层次类型的3个整数位,不足部分补零;

KeyName是版图层次名称的关键字,依据版图层次资讯表格中的关键字书写。

依据此第一规则,进行格式转换的结果例如:“Layer001DataType000Nwell”;“Layer007DataType000 M1”。

表2

本实施例中,在对晶圆厂提供的如表2所示的版图设计规则资讯进行格式转为时,可采用第二规则:RuleXXXxxxNNNisdddd Note;其中,

Rule表示当前行为版图层次的设计规则;

XXX表示版图层次号码的3个整数位号码,不足部分补零;

xxx表示层次类型的3个整数位,不足部分补零;

NNN表示设计规则的3个整数位编码,不足部分补零

dddd表示设计规则的4个整数位数值,单位是奈米,不足部分补零。

比如表2中第一行的设计规则编号Active_1是300奈米,从版图层次资讯表得到“Active”的层次号码是2(XXX=002),层次类型0(xxx=000),“_1”表示设计规则的编码是1(NNN=001),“300奈米”表示设计规则的数值是300(dddd=0300),故格式转换的结果为“Rule002000001is0300”;同理第五行的设计规则编号Active_5是20奈米,格式转换的结果为“Rule002000005is0020”。

基于上述进行格式转换的第一规则和第二规则,表1及表2的内容转换完成的结果为:

Layer001DataType000 Nwell

Layer002DataType000 Active

Rule002000001is0300 Active_P+_Enclosure

Rule002000002is0300 Active_N+_Enclosure

Rule002000003is0500 Active_Nwell_Enclosure

Rule002000004is0010 Active_Ptap_Enclosure

Rule002000005is0010 Active_Ntap_Enclosure

Rule002000006is0350 Active_Active

Layer003DataType000 Poly

Rule003000001is0600 Poly_PMOS5V

Rule003000002is0600 Poly_NMOS5V

Rule003000003is0250 Polygate_Extension

Rule003000004is0200 Poly_Width

Rule003000005is0300 Poly_Space

Rule003000006is0100 Poly_Active_Space

Layer004DataType000 P+

Rule004000001is0100 P+_Active_Space

Rule004000002is0400 P+_width

Rule004000003is0200 P+_Over_P+Active

Layer005DataType000 N+

Rule005000001is0100 N+_Active_Space

Rule005000002is0400 N+_width

Rule005000003is0200 N+_Over_N+Active

Layer006DataType000 Contact

Rule006000001is0250 Contact_Size

Rule006000002is0250 Contact_Space

Rule006000003is0300 Contact_Space4

Rule006000004is0010 CT_M1_Enclosure

Rule006000005is0050 CT_M1_LineEnd

Rule006000006is0070 CT_Poly_Enclosure

Rule006000007is0070 CT_Poly_LineEnd

Rule006000008is0070 CT_Active_Enclosure

Rule006000009is0150 CT_P+_Enclosure

Rule006000010is0150 CT_N+_Enclosure

Rule006000011is0150 CT_POLY_Space

Rule006000012is0200 CT_Active_onPOLY

Layer007DataType000 M1

Rule007000001is0250 M1_Width

Rule007000002is0250 M1_Space

Layer008DataType000 V1

Rule008000001is0290 V1_Size

Rule008000002is0290 V1_Space

Rule008000003is0010 V1_M1_Enclosure

Rule008000004is0060 V1_M1_LineEnd

Rule008000005is0010 V1_M2_Enclosure

Rule008000006is0060 V1_M2_LineEnd

Layer009DataType000 M2

Rule009000001is0300 M2_Width

Rule009000002is0300 M2_Space

Layer040DataType000 V2

Layer041DataType000 M3

Layer061DataType000 V3

Layer062DataType000 M4

Layer091DataType000 V4

Layer092DataType000 M5

Layer093DataType000 TV5

Rule093000001is0400 TV5_Size

Rule093000002is0400 TV5_Space

Rule093000003is0020 TV5_Mx_Enclosure

Rule093000004is0100 TV5_Mx_LineEnd

Rule093000005is0050 TV5_TM6_Enclosure

Rule093000006is0100 TV5_TM6_LineEnd

Layer094DataType000 TM6

Layer121DataType000 M1_TXT

Layer147DataType001 BoundryCell

另外,本实施例中,进一步的,所述利用版图算法资料库检测标准单元的各版图布局是否符合晶圆厂设计规则的方法具体可包括如下步骤:

利用相应所述内嵌算法将固定版图布局的每一个几何图形根据版图标准GDSII格式规定,按所述版图设计规则,逐个利用算法的方式来描述;以及,

对于每个所述描述,利用指定算式检查是否符合设计规则。

逻辑功能,非门为例,标准单元最下方有5个穿孔,由于穿孔为四边形,故可获取形成四边形GDSII描述的子程序,以及获取关于计算5个穿孔的座标的子程序,从而以完成对5个穿孔的描述。描述完成之后,对于该描述,利用检查穿孔之间的距离是否大于最小穿孔间距的算式来检测是否符合设计规则。

进一步的,所述利用版图算法资料库检测标准单元的各版图布局的电性规格是否符合使用要求的方法具体可包括如下步骤:

根据输入的所述电路设计参数,利用相应所述内嵌算法计算固定版图布局的规格参数值;以及,

根据计算得到的所述规格参数值,判断电性规格是否满足符合使用要求。

以TpHL为例,对应的所述内嵌算法为TpHL=0.69*(3/4)*(C*V/Idsatn)

从步骤S11输入的所述电路设计参数,可以得到单位沟道电容C和NMOS饱和电流Idsat,进而利用所述算法为TpHL=0.69*(3/4)*(C*V/Idsatn)可计算得到TpHL。

更进一步的,本实施例提供的所述产生标准单元库版图的方法还包括:若一固定版图布局的电性规格不符合晶圆厂设计规则,则依据电性规格规定调整所述内嵌算法中用于电路设计的规格参数变量,并重新执行所述含内嵌算法的程序,以判断所述固定版图布局是否符合晶圆厂设计规则,若符合,则将所述固定版图布局存储至所述标准单元库版图。如此,便可保证满足设计规则及符合电性规格的所有版图均能顺利进入标准单元库版图。

以逻辑功能,非门为例,其内嵌算法是检查电性规格TpHL和TpLH;可利用上述内嵌算法得到符合电性规格的PMOS沟道宽度Wpmin和NMOS沟道宽度Wnmin;已知现在版图PMOS沟道宽度Wpnow,NMOS沟道宽度Wnnow,最大总和Wsum;

如果Wpmin+Wnmin>W sum则无法调整;

如果是原来TpHL不符合,代表Wnnow太小,则调整后NMOS沟道宽度Wnafter=Wnmin;

如果Wnafter+Wpnow<=Wsum则PMOS沟道宽度不变动即调整后Wpafter=Wpnow;

但如果Wnafter+Wpnow>Wsum则调整后PMOS沟道宽度Wpafter=Wsum-Wnafter;

如果是原来TpLH不符合,代表Wpnow太小,则调整后pMOS沟道宽度Wpafter=Wpmin;

如果Wpafter+Wnnow<=Wsum则NMOS沟道宽度不变动即调整后Wnafter=Wnnow;

但如果Wpafter+Wnnow>Wsum则调整后NMOS沟道宽度Wpafter=Wsum-Wnafter;

如果是原来TpHL不符合,原来TpLH不符合则调整后NMOS沟道宽度Wnafter=Wnmin;调整后pMOS沟道宽度Wpafter=Wpmin。

然后将新产生的Wpafter和Wnafter代入,即调整内嵌电路设计算法中沟道宽度的变量,重新执行产生GDSII版图的算法,以判断所述固定版图布局是否符合晶圆厂设计规则,若符合,则存储到标准单元库版图中。

【实施例二】

如图2所示,本实施例提供一种产生标准单元库版图的方法,所述产生标准单元库版图的方法包括如下步骤:

S21,将版图设计规则输入至版图算法资料库,以利用所述版图算法资料库检测标准单元的各版图布局是否符合晶圆厂设计规则;

S22,利用电路仿真软件获取晶圆厂提供的元器件模型,得到仿真的结果以判断标准单元的各版图布局是否符合电性规格;以及,

S23,将符合晶圆厂设计规则以及电性规格符合使用要求的版图布局存储至标准单元库版图中。

与实施例一相比,本实施例提供的所述产生标准单元库版图的方法,仅对于标准单元的各版图布局是否符合电性规格的判断方式不同,因此,对于其他相同的部分请参照实施例一,在此不再赘述。

当采用内嵌算法进行电性规格的判断时,执行速度快,但可能存在精度达不到要求的情况,故在版图设计规则和电性规格变化不大的情况下,采用内嵌算法来判断标准单元的各版图布局是否符合电性规格。

对于精度要求比较高的情况下,可采用本实施例中所述,利用电路仿真软件获取晶圆厂提供的元器件模型(亦可理解实施一中所述电路设计参数),得到仿真的结果以判断标准单元的各版图布局是否符合电性规格。

综上所述,本发明提供的产生标准单元库版图的方法,首先,将版图设计规则和电路设计参数输入至版图算法资料库,以利用所述版图算法资料库检测标准单元的各版图布局是否符合晶圆厂设计规则,并检测标准单元的各版图布局的电性规格是否符合使用要求;或者,将版图设计规则输入至版图算法资料库,以利用所述版图算法资料库检测标准单元的各版图布局是否符合晶圆厂设计规则;利用电路仿真软件获取晶圆厂提供的元器件模型,得到仿真的结果以判断标准单元的各版图布局是否符合电性规格;而后将符合晶圆厂设计规则以及电性规格符合使用要求的版图布局存储至标准单元库版图中。与传统方法相比,产生版图快,节省了人力,且不需要EDA辅助设计的工具。

需要说明的是,本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可,此外,各个实施例之间不同的部分也可互相组合使用,本发明对此不作限定。

此外还应该认识到,虽然本发明已以较佳实施例披露如上,然而上述实施例并非用以限定本发明。对于任何熟悉本领域的技术人员而言,在不脱离本发明技术方案范围情况下,都可利用上述揭示的技术内容对本发明技术方案做出许多可能的变动和修饰,或修改为等同变化的等效实施例。因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所做的任何简单修改、等同变化及修饰,均仍属于本发明技术方案保护的范围。

- 一种标准单元版图、标准单元库版图及布线方法

- 标准单元库版图设计方法、布局方法及标准单元库