半导体装置及半导体装置的制造方法

文献发布时间:2023-06-19 10:03:37

本申请享有以日本专利申请2019-153718号(申请日:2019年8月26日)为基础申请的优先权。本申请通过参考该基础申请而包含基础申请的所有内容。

技术领域

实施方式涉及一种半导体装置及半导体装置的制造方法。

背景技术

已知有形成在半导体衬底上的MOS(metal oxide semiconductor,金属氧化物半导体)晶体管。在像该MOS晶体管一样的半导体装置中,将p型MOS晶体管与n型晶体管排列配置。

发明内容

实施方式提供一种能够抑制晶体管的阱耐压劣化且减少元件面积的半导体装置及半导体装置的制造方法。

实施方式的半导体装置具备:第2导电型的半导体衬底,是包含第1面的半导体衬底,且包含所述第1面侧的第1导电型的第1区域、在所述第1区域的所述第1面侧排列在沿着所述第1面的第1方向的第2导电型的2个第2区域、及包围所述第1区域且具有低于所述第1区域的所述第1面中的第1导电型杂质的浓度的第1导电型杂质的浓度的第1导电型的第3区域;导电体层,设置在所述第1区域中所述2个第2区域之间的第1部分的上方;以及第1绝缘体层,在所述半导体衬底的所述第1面侧,包围所述第3区域且与所述第3区域相接。所述第1区域中沿着所述第1方向而与所述第1部分排列的第2部分在所述第1面侧,未由绝缘体层夹着而沿着所述第1方向延伸。

附图说明

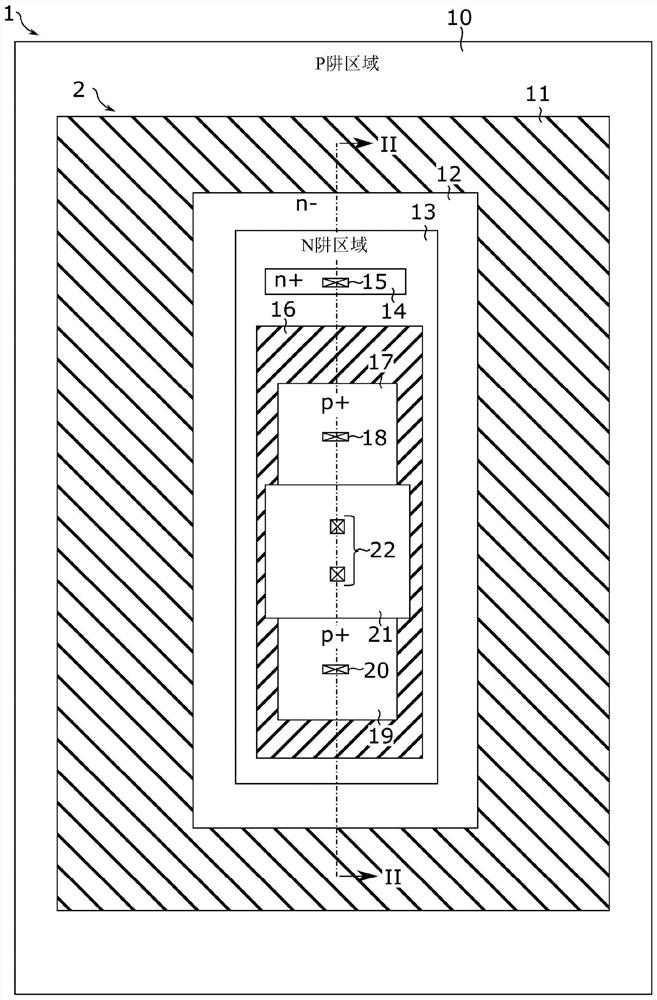

图1是从上方观察第1实施方式的半导体装置中所包含的p型晶体管的俯视图。

图2是沿着图1的II-II线的p型晶体管的剖视图。

图3~11是用来说明第1实施方式的半导体装置的制造工序的p型晶体管的剖视图。

图12是从上方观察第2实施方式的半导体装置中所包含的p型晶体管的俯视图。

图13是沿着图12的XIII-XIII线的p型晶体管的剖视图。

图14是用来说明第2实施方式的半导体装置的制造工序的p型晶体管的剖视图。

图15是从上方观察第3实施方式的半导体装置中所包含的p型晶体管的俯视图。

图16是沿着图15的XVI-XVI线的p型晶体管的剖视图。

图17~19是用来说明第3实施方式的半导体装置的制造工序的p型晶体管的剖视图。

图20是从上方观察第4实施方式的半导体装置中所包含的p型晶体管的俯视图。

图21是沿着图20的XXI-XXI线的p型晶体管的剖视图。

图22~25是用来说明第4实施方式的半导体装置的制造工序的p型晶体管的剖视图。

图26是从上方观察第3实施方式的变化例的半导体装置中所包含的p型晶体管的俯视图。

图27是从上方观察第4实施方式的变化例的半导体装置中所包含的p型晶体管的俯视图。

图28是表示包含作为各实施方式的半导体装置的应用例的半导体存储装置的存储器系统的整体构成的框图。

图29是表示作为各实施方式的半导体装置的应用例的半导体存储装置内的存储单元阵列的部分的电路图。

图30是表示作为各实施方式的半导体装置的应用例的半导体存储装置内的行解码器模块及驱动器模块的框图。

图31是表示作为各实施方式的半导体装置的应用例的半导体存储装置内的区块解码器的电路图。

具体实施方式

以下,参考附图对实施方式进行说明。各实施方式例示了用来使发明的技术性思想具体化的装置或方法。附图是示意性或概念性的图,各附图的尺寸及比率等未必与实物相同。本发明的技术思想并非由构成要素的形状、结构、配置等来特定。

此外,在以下的说明中,对具有大致相同的功能及构成的构成要素标注相同符号。构成参考符号的字符之后的数字是通过包含相同字符的参考符号来参考,且用来区分具有相同构成的要素彼此。在无需将由包含相同字符的参考符号表示的要素相互加以区分的情况下,这些要素分别通过仅包含字符的参考符号来参考。

1.第1实施方式

对第1实施方式的半导体装置进行说明。

1.1构成

首先,对第1实施方式的半导体装置的构成进行说明。第1实施方式的半导体装置例如包含形成在半导体衬底上的多个MOS(Metal Oxide Semiconductor)晶体管。多个MOS晶体管包含互不相同的导电型的晶体管(也就是说,n型晶体管及p型晶体管),这些晶体管配置于半导体衬底上。

图1是从上方观察第1实施方式的半导体装置中所包含的p型晶体管的俯视图。此外,在以下的图中,适当省略了半导体衬底上的层间绝缘膜等。

如图1所示,半导体装置1包含p型晶体管2。p型晶体管2例如形成在半导体衬底(例如,p型半导体衬底)中由p型的阱区域(P阱区域)10包围的区域上。在P阱区域10,例如形成未图示的n型晶体管。

p型半导体衬底中由P阱区域10包围的区域例如利用作为元件分离区域发挥功能的绝缘体层11而与P阱区域10电分离。p型晶体管2的区域例如可由该绝缘体层11的大小来规定。

在p型半导体衬底中由绝缘体层11包围的区域内,形成周围由n

在N阱区域13内,形成作为包围N阱区域13的一部分的元件分离区域发挥功能的绝缘体层16,并且在该绝缘体层16的外侧形成n

在由绝缘体层16包围的N阱区域13内,p

p

在p

在p

在以下的说明中,关于p型晶体管2,将p

也就是说,p

另外,N阱区域13中的沿着长度方向而与通道区域排列的区域包含n

图2是表示沿着在所述p型晶体管2的长度方向延伸的直线(图1中的II-II线)的p型晶体管2的剖视图。在以下的说明中,将从p型半导体衬底5中未形成阱区域的部分朝向p型半导体衬底5的表面的方向称为“上方”,将其相反方向称为“下方”。另外,将从p型半导体衬底5的表面朝向下方的长度称为“深度”。

如图2所示,P阱区域10及N阱区域13从p型半导体衬底5的表面形成到规定的深度为止。绝缘体层11的下端形成在比P阱区域10的下端浅的位置,n

栅极绝缘膜23例如包含氧化硅(SiO

在导电体层21的上表面上及侧面上分别形成绝缘体层26及27。绝缘体层26例如包含氮化硅(SiN),绝缘体层27例如包含氧化硅(SiO

1.2制造方法

使用图3~图11对第1实施方式的半导体装置中的p型晶体管2的制造工序的一例进行说明。图3~图11分别表示第1实施方式的半导体装置的制造工序中的包含与p型晶体管2对应的结构体的截面结构的一例。此外,在以下所参考的制造工序的剖视图中,包含与p型半导体衬底5的表面铅垂的截面。

首先,如图3所示,在p型半导体衬底5上形成抗蚀剂材料31。抗蚀剂材料31中形成N阱区域13的预定的区域上所形成的部分例如利用光刻法而去除,该区域的p型半导体衬底5露出。而且,对所露出的p型半导体衬底5选择性地离子注入n型杂质,形成N阱区域13。在形成N阱区域13之后,将抗蚀剂材料31去除。

接下来,如图4所示,在p型半导体衬底5上形成抗蚀剂材料32。抗蚀剂材料32中形成P阱区域10的预定的区域上所形成的部分例如利用光刻法而去除,该区域的p型半导体衬底5露出。而且,对所露出的p型半导体衬底5选择性地离子注入p型的杂质,形成P阱区域10。在形成P阱区域10之后,将抗蚀剂材料32去除。

接下来,如图5所示,在形成绝缘体层11及16的预定的区域,分别形成孔H_STI1及H_STI2。具体来说,首先,在形成有N阱区域13及P阱区域10之后的p型半导体衬底5上,依次积层栅极绝缘膜23、导电体层24、掩模材料33、及抗蚀剂材料34。抗蚀剂材料34中形成孔H_STI1及H_STI2的预定的区域例如利用光刻法而去除,掩模材料33露出。然后,利用使用了所形成的抗蚀剂材料34的图案的各向异性蚀刻,形成孔H_STI1及H_STI2。在形成孔H_STI1及H_STI2之后,将抗蚀剂材料34去除。

在本工序中形成的孔H_STI1在N阱区域13的外部贯通掩模材料33、导电体层24、及栅极绝缘膜23,到达P阱区域10。另外,在本工序中形成的孔H_STI2在N阱区域13的内部贯通掩模材料33、导电体层24、及栅极绝缘膜23,到达N阱区域13。本工序中的各向异性蚀刻例如为RIE(Reactive Ion Etching,反应性离子蚀刻)。

接下来,如图6所示,在孔H_STI1及H_STI2内填埋绝缘体层,分别形成绝缘体层11及16。具体来说,以填埋孔H_STI1及H_STI2内的方式,遍及整个面形成绝缘体层。使用掩模材料33作为终止膜将形成有绝缘体层之后的积层体的表面平坦化。然后,将掩模材料33去除,进而将绝缘体层11及16回蚀。本工序中的平坦化例如为CMP(Chemical MechanicalPolishing,化学机械抛光)。

接下来,如图7所示,在形成p型晶体管2的通道区域的预定的区域上,形成作为p型晶体管2的栅极发挥功能的预定的积层体(栅极结构)。具体来说,在将绝缘体层11及16回蚀之后的结构体的上表面上,进而形成导电体层24,由此使导电体层24厚膜化。在厚膜化的导电体层24上,依次积层导电体层25、绝缘体层26、及抗蚀剂材料35。抗蚀剂材料35中形成p型晶体管2的栅极结构的预定的区域以外的部分例如利用光刻法而去除,该区域的绝缘体层26露出。然后,利用使用了所形成的抗蚀剂材料35的图案的各向异性蚀刻将该图案中的绝缘体层26、导电体层25、及导电体层24的部分去除,利用绝缘体层26、导电体层25、及导电体层24的剩余的部分形成栅极结构。

接下来,如图8所示,遍及整个面选择性地离子注入n型杂质,在p型半导体衬底5中的绝缘体层11与N阱区域13之间的区域形成n

此外,在本工序中,n型杂质也可对形成n

接下来,如图9所示,在栅极结构的侧面上形成绝缘体层27并且将栅极绝缘膜23除与通道区域对应的部分以外而去除之后,遍及整个面形成抗蚀剂材料36。在抗蚀剂材料36中形成p

接下来,如图10所示,遍及整个面形成抗蚀剂材料37。在抗蚀剂材料37中形成n

对所露出的N阱区域13选择性地离子注入n型杂质,形成n

接下来,如图11所示,在n

1.3本实施方式的效果

根据第1实施方式,N阱区域13中沿着长度方向而与通道区域排列的部分未由绝缘体层16等元件分离区域夹着而沿着长度方向延伸。由此,第1实施方式的p型晶体管2与包含沿着长度方向且由元件分离区域夹着的部分的情况相比,因省略该元件分离区域及由元件分离区域夹着的部分,而能够减少沿着长度方向的元件面积。

如果进行补充说明,那么当在半导体衬底上将p型晶体管与n型晶体管并列设置的情况下,为了将两者电分离,而在之间形成元件分离区域。然而,存在如下可能性:由n型晶体管的制造工序引起,形成经由该元件分离区域的下方而n型晶体管内的p

另外,具有周围由n

根据第1实施方式,这些2个触点合并为1个触点15,该触点15经由设置在上表面上的n

2.第2实施方式

接下来,对第2实施方式的半导体装置进行说明。在第1实施方式中,在与绝缘体层16分离的区域选择性地形成n

2.1构成

图12是从上方观察第2实施方式的半导体装置中所包含的p型晶体管的俯视图,且与第1实施方式中的图1对应。

如图12所示,在N阱区域13内,形成包围N阱区域13的一部分的绝缘体层16,并且在该绝缘体层16的外侧形成n

在n

p

图13是沿着在所述p型晶体管2的长度方向延伸的直线(图12中的XIII-XIII线)的p型晶体管2的剖视图。

如图13所示,n

2.2制造方法

使用图14对第2实施方式的半导体装置中的p型晶体管2的制造工序的一例进行说明。图14是表示第2实施方式的半导体装置的制造工序中的包含与p型晶体管2对应的结构体的截面结构的一例,且与第1实施方式中的图10对应。

首先,利用与第1实施方式中的图3~图9所示的工序相同的工序,在p型半导体衬底5内,形成N阱区域13、P阱区域10、绝缘体层11及16、p型晶体管2的栅极结构、n

接下来,如图14所示,遍及整个面形成抗蚀剂材料37A。在抗蚀剂材料37A中包含形成n

对所露出的N阱区域13选择性地离子注入n型杂质,形成n

接下来,利用与第1实施方式中的图11所示的工序相同的工序,在n

2.3本实施方式的效果

根据第2实施方式,利用光刻法,除了形成n

3.第3实施方式

接下来,对第3实施方式的半导体装置进行说明。在第1实施方式中,对n

3.1构成

图15是从上方观察第3实施方式的半导体装置中所包含的p型晶体管的俯视图,且与第1实施方式中的图1对应。

如图15所示,在N阱区域13内,形成U字状的绝缘体层16B。U字状的绝缘体层16B中对向的2条边沿着p型晶体管2的长度方向延伸。在该绝缘体层16B的开口部分(也就是说,将绝缘体层16B的两端连接的区域)形成n

在由U字状的绝缘体层16B中对向的2条边夹着的N阱区域13内,p

p

p

图16是沿着在所述p型晶体管2的长度方向延伸的直线(图15中的XVI-XVI线)的p型晶体管2的剖视图。

如图16所示,绝缘体层16B的下端形成在比N阱区域13的下端浅的位置,p

3.2制造方法

使用图17~图19对第3实施方式的半导体装置中的p型晶体管2的制造工序的一例进行说明。图17~图19是表示第3实施方式的半导体装置的制造工序中的包含与p型晶体管2对应的结构体的截面结构的一例,分别与第1实施方式中的图5、图7、及图10对应。

首先,利用与第1实施方式中的图3及图4所示的工序相同的工序,在p型半导体衬底5内形成N阱区域13及P阱区域10。

接下来,如图17所示,在形成绝缘体层11及16B的预定的区域,分别形成孔H_STI1及H_STI2B。具体来说,首先,在形成N阱区域13及P阱区域10之后的p型半导体衬底5上,依次积层栅极绝缘膜23、导电体层24、掩模材料33、及抗蚀剂材料34。抗蚀剂材料34中形成孔H_STI1及H_STI2B的预定的区域例如利用光刻法而去除,掩模材料33露出。然后,利用使用了所形成的抗蚀剂材料34的图案的各向异性蚀刻,形成孔H_STI1及H_STI2B。形成孔H_STI1及H_STI2B之后,将抗蚀剂材料34去除。在本工序中所形成的孔H_STI2BN在阱区域13的内部贯通掩模材料33、导电体层24、及栅极绝缘膜23,到达N阱区域13。

接下来,如图18所示,利用与第1实施方式中的图6所示的工序相同的工序,在形成绝缘体层11及16B之后,在形成p型晶体管2的通道区域的预定的区域上,形成作为p型晶体管2的栅极发挥功能的预定的积层体。具体来说,在以填埋孔H_STI1及H_STI2B内的方式遍及整个面形成绝缘体层之后,在使表面上平坦化之后将掩模材料33去除,将绝缘体层11及16B进而回蚀。在将绝缘体层11及16B回蚀之后的结构体的上表面上,形成p型晶体管2的栅极结构的工序由于与第1实施方式同等,所以省略说明。

接下来,利用与第1实施方式中的图8及图9所示的工序相同的工序,形成n

接下来,如图19所示,遍及整个面形成抗蚀剂材料37B。抗蚀剂材料37B中形成n

对所露出的N阱区域13选择性地离子注入n型杂质,形成n

接下来,利用与第1实施方式中的图11所示的工序相同的工序,在n

3.3本实施方式的效果

根据第3实施方式,n

此外,绝缘体层16B不包围N阱区域13的一部分,具有矩形的一边开口的U字状的形状,不将n

4.第4实施方式

接下来,对第4实施方式的半导体装置进行说明。在第3实施方式中,对在p型晶体管2中漏极利用通道区域及元件分离区域而与源极分离的情况进行了说明。在第4实施方式中,对在p型晶体管2中漏极仅利用通道区域而与源极分离的情况进行说明。在以下的说明中,关于与第1实施方式或第3实施方式同等的构成及制造方法省略说明,主要对与第1实施方式或第3实施方式不同的构成及制造方法进行说明。

4.1构成

图20是从上方观察第4实施方式的半导体装置中所包含的p型晶体管的俯视图,且与第3实施方式中的图15对应。

如图20所示,在N阱区域13内,p

在包含p

图21是沿着在所述p型晶体管2的长度方向延伸的直线(图20中的XXI-XXI线)的p型晶体管2的剖视图。

如图21所示,在栅极绝缘膜23的上表面上,形成包含导电体层24C及25C的导电体层21C。导电体层24C形成在栅极绝缘膜23的上表面上,导电体层25C形成导电体层24C的上表面上。

在导电体层21C的上表面上及侧面上分别形成绝缘体层26C及27C。如上所述,包含导电体层21C及绝缘体层26C的栅极结构以包围p

4.2制造方法

使用图22~图25对第4实施方式的半导体装置中的p型晶体管2的制造工序的一例进行说明。图22~图25是表示第4实施方式的半导体装置的制造工序中的包含与p型晶体管2对应的结构体的截面结构的一例,且分别与第1实施方式中的图5、图7、图9、及图10对应。

首先,利用与第1实施方式中的图3及图4所示的工序相同的工序,在p型半导体衬底5内,形成N阱区域13及P阱区域10。

接下来,如图22所示,在形成绝缘体层11的预定的区域形成孔H_STI1。关于孔的形成工序,由于除了不形成孔H_STI2的方面以外与第1实施方式同等,所以省略说明。

接下来,如图23所示,利用与第1实施方式中的图6所示的工序相同的工序,在形成绝缘体层11之后,在形成p型晶体管2的通道区域的预定的区域上,形成作为p型晶体管2的栅极发挥功能的预定的积层体(栅极结构)。具体来说,在以填埋孔H_STI1内的方式遍及整个面形成绝缘体层之后,使表面平坦化之后将掩模材料33去除,将绝缘体层11进而回蚀。在绝缘体层11经回蚀的结构体的上表面上,进而形成导电体层24C,由此使导电体层24C厚膜化。在厚膜化的导电体层24C上,依次积层导电体层25C、绝缘体层26C、及抗蚀剂材料35C。抗蚀剂材料35C中形成p型晶体管2的栅极结构的预定的区域以外的部分例如利用光刻法而去除,该区域的绝缘体层26C露出。然后,利用使用了所形成的抗蚀剂材料35C的图案的各向异性蚀刻将该图案中的绝缘体层26C、导电体层25C、及导电体层24C的部分去除,利用绝缘体层26C、导电体层25C、及导电体层24C的剩余的部分形成栅极结构。

接下来,利用与第1实施方式中的图8所示的工序相同的工序,形成n

接下来,如图24所示,在栅极结构的内周面上及外周面上形成绝缘体层27C,并且将栅极绝缘膜23除了与通道区域对应的部分以外而去除之后,遍及整个面形成抗蚀剂材料36C。在抗蚀剂材料36C中形成p

接下来,如图25所示,遍及整个面形成抗蚀剂材料37C。抗蚀剂材料37C中形成n

对所露出的N阱区域13选择性地离子注入n型杂质,形成n

接下来,利用与第1实施方式中的图11所示的工序相同的工序,在n

4.3本实施方式的效果

根据第4实施方式,p

另外,n

此外,在N阱区域13内,由于不形成元件分离区域,所以n

5.变化例

此外,所述第1实施方式至第4实施方式(以下,也简称为“所述各实施方式”)能够进行各种变化。

例如,在所述第3实施方式中,对在n

图26及图27分别是从上方观察第3实施方式及第4实施方式的变化例的半导体装置中所包含的p型晶体管的情况下的俯视图。

如图26所示,以与n

另外,如图27所示,以与n

通过以如上的方式构成,能够将触点的数量减少1个,能够减少半导体装置1的制造负载。

6.应用例

对所述各实施方式的半导体装置的应用例进行说明。所述各实施方式的半导体装置例如可应用于能够非易失地存储数据的NAND(Not And,与非)型闪速存储器(半导体存储装置)。

6.1半导体存储装置的构成

图28是用来说明所述各实施方式的应用例的半导体存储装置的构成的框图。半导体存储装置100例如为NAND型闪速存储器,由外部的存储器控制器200来控制。半导体存储装置100与存储器控制器200之间的通信例如支持NAND接口标准。

如图28所示,半导体存储装置100例如具备存储单元阵列110、指令寄存器120、地址寄存器130、定序器140、驱动器模块150、行解码器模块160、以及感测放大器模块170。

存储单元阵列110包含多个区块BLK0~BLKn(n为1以上的整数)。区块BLK为能够非易失地存储数据的多个存储单元的集合,例如用作数据的删除单位。另外,在存储单元阵列110设置多条位线及多条字线。各存储单元例如与1条位线及1条字线建立关联。关于存储单元阵列110的详细的构成将在下文叙述。

指令寄存器120保存半导体存储装置100从存储器控制器200接收到的指令CMD。指令CMD例如包含使定序器140执行读出动作、写入动作、删除动作等的命令。

地址寄存器130保存半导体存储装置100从存储器控制器200接收到的地址信息ADD。地址信息ADD例如包含区块地址BA、页地址PA、及列地址CA。例如,区块地址BA、页地址PA、及列地址CA分别用于选择区块BLK、字线、及位线。

定序器140控制半导体存储装置100整体的动作。例如,定序器140基于保存在指令寄存器120中的指令CMD控制驱动器模块150、行解码器模块160、及感测放大器模块170等,执行读出动作、写入动作、删除动作等。

驱动器模块150产生读出动作、写入动作、删除动作等中所使用的电压。而且,驱动器模块150例如基于保存在地址寄存器130中的页地址PA,对与所选择的字线对应的信号线的电压施加所产生的电压。

行解码器模块160基于保存在地址寄存器130中的区块地址BA,选择对应的存储单元阵列110内的1个区块BLK。而且,行解码器模块160例如将施加至与所选择的字线对应的信号线的电压传输到所选择的区块BLK内的所选择的字线。

感测放大器模块170在写入动作中,根据从存储器控制器200接收到的写入数据DAT,对各位线施加所期望的电压。另外,感测放大器模块170在读出动作中,基于位线的电压判定存储在存储单元中的数据,将判定结果作为读出数据DAT传输到存储器控制器200。

以上所说明的半导体存储装置100及存储器控制器200也可利用它们的组合来构成1个半导体装置。作为这种半导体装置,例如可列举像SD(Secure Digital,安全数字)

6.2存储单元阵列的构成

图29是用来说明所述各实施方式的应用例的半导体存储装置的存储单元阵列的构成的电路图。图29表示存储单元阵列110中所包含的多个区块BLK中1个区块BLK。

如图29所示,区块BLK例如包含4个串单元SU0~SU3。各串单元SU包含与位线BL0~BLm(m为1以上的整数)分别建立关联的多个NAND串NS。各NAND串NS例如包含存储单元晶体管MT0~MT7、以及选择晶体管ST1及ST2。存储单元晶体管MT包含控制栅极及电荷储存层,且非易失地保存数据。选择晶体管ST1及ST2分别用于选择各种动作时的串单元SU。

在各NAND串NS中,存储单元晶体管MT0~MT7串联连接。选择晶体管ST1的漏极连接于被建立关联的位线BL,选择晶体管ST1的源极连接于串联连接的存储单元晶体管MT0~MT7的一端。选择晶体管ST2的漏极连接于串联连接的存储单元晶体管MT0~MT7的另一端。选择晶体管ST2的源极连接于源极线SL。

在同一区块BLK中,存储单元晶体管MT0~MT7的控制栅极分别共通连接于字线WL0~WL7。串单元SU0~SU3内的选择晶体管ST1的栅极分别共通连接于选择栅极线SGD0~SGD3。选择晶体管ST2的栅极共通连接于选择栅极线SGS。

在以上所说明的存储单元阵列110的电路构成中,位线BL由在各串单元SU分配有同一列地址的NAND串NS共有。源极线SL例如在多个区块BLK间共有。

在1个串单元SU内连接于共通的字线WL的多个存储单元晶体管MT的集合例如称为单元组件CU。例如,将包含分别存储1比特数据的存储单元晶体管MT的单元组件CU的存储容量定义为“1页数据”。单元组件CU根据存储单元晶体管MT所存储的数据的比特数,可具有2页数据以上的存储容量。

此外,所述各实施方式的应用例的半导体存储装置100所具备的存储单元阵列110的电路构成并不限定于以上所说明的构成。例如,各NAND串NS所包含的存储单元晶体管MT以及选择晶体管ST1及ST2的个数可分别设计为任意的个数。各区块BLK所包含的串单元SU的个数可设计为任意的个数。

6.3行解码器模块及驱动器模块的构成

图30是用来说明所述各实施方式的应用例的半导体存储装置的行解码器模块及驱动器模块的构成的框图。

如图30所示,行解码器模块160包含多个传输开关群161(161_0、161_1、…)、及多个区块解码器162(162_0、162_1、…)。

1个传输开关群161及1个区块解码器162例如分配到1个区块BLK。在图30的例中,传输开关群161_0及区块解码器162_0分配到区块BLK0,传输开关群161_1及区块解码器162_1分配到区块BLK1。在以下的说明中,将成为写入、读出、及删除的对象的区块BLK称为“选择区块BLK”,将选择区块BLK以外的区块BLK称为“非选择区块BLK”。

传输开关群161例如包含13个传输晶体管TTr(TTr0~TTr12)。

传输晶体管TTr0~TTr7分别将从驱动器模块150供给到配线CG(CG0~CG7)的电压传输到选择区块BLK的字线WL0~WL7。传输晶体管TTr0~TTr7分别包含连接于对应的区块BLK的字线WL0~WL7的第1端、及连接于配线CG0~CG7的第2端。

传输晶体管TTr8~TTr11分别将从驱动器模块150供给到配线SGDL(SGDL0~SGDL3)的电压传输到选择区块BLK的选择栅极线SGD0~SGD3。传输晶体管分别包含连接于对应的区块BLK的选择栅极线SGD0~SGD3的第1端、及连接于配线SGDL0~SGDL3的第2端。

传输晶体管TTr12将从驱动器模块150供给到配线SGSL的电压传输到选择区块BLK的选择栅极线SGS。传输晶体管TTr12包含连接于对应的区块BLK的选择栅极线SGS的第1端、及连接于配线SGSL的第2端。

此外,传输开关群161_0内的传输晶体管TTr0~TTr12的各栅极经由节点BLKSEL_0而共通连接于对应的区块解码器162_0,传输开关群161_1内的传输晶体管TTr0~TTr12的各栅极经由节点BLKSEL_1而共通连接于对应的区块解码器162_1。这样,同一传输开关群161内的传输晶体管TTr0~TTr12的各栅极经由同一节点BLKSEL而共通连接于对应的区块解码器162。

区块解码器162在数据的写入、读出、及删除时,将从地址寄存器130接收到的区块地址信号解码。区块解码器162在解码的结果判定为与该区块解码器162对应的区块BLK为选择区块BLK的情况下,将“H”电平的信号输出到对应的节点BLKSEL。另外,区块解码器162在判定为对应的区块BLK并非选择区块BLK的情况下,将“L”电平的信号输出到对应的节点BLKSEL。输出到节点BLKSEL的信号将传输晶体管TTr0~TTr12以“H”电平设为导通状态,以“L”电平设为断开状态。

通过以如上的方式构成,例如,在与选择区块BLK对应的传输开关群161中,传输晶体管TTr0~TTr12能够成为导通状态。由此,字线WL0~WL7分别连接于配线CG0~CG7,选择栅极线SGD0~SGD3分别连接于配线SGDL0~SGDL3,选择栅极线SGS连接于配线SGSL。

另外,在与非选择区块BLK对应的传输开关群161中,传输晶体管TTr0~TTr12能够成为断开状态。由此,字线WL从配线CG电切断,选择栅极线SGD及SGS分别从配线SGDL及SGSL电切断。

驱动器模块150根据从地址寄存器130接收到的地址ADD,对配线CG、SGDL、及SGSL供给电压。配线CG、SGDL、及SGSL将从驱动器模块150供给的各种电压分别传输到传输开关群161_0、161_1、…。也就是说,从驱动器模块150供给的电压经由与选择区块BLK对应的传输开关群161内的传输晶体管TTr0~TTr12,而传输到选择区块BLK内的字线WL、选择栅极线SGD及SGS。

6.4区块解码器的构成

图31是用来说明所述各实施方式的应用例的半导体存储装置的区块解码器的构成的电路图。

如图31所示,区块解码器162包含逻辑电路LC、与门电路AND、反相器INV1及INV2、n型晶体管Tr1、Tr2、及Tr3、以及p型晶体管Tr4。n型晶体管Tr2及Tr3、以及p型晶体管Tr4为相对于n型晶体管Tr1而栅极绝缘膜较厚的高耐压的晶体管。p型晶体管Tr4例如能够应用所述各实施方式的半导体装置中所包含的p型晶体管2。

逻辑电路LC基于从地址寄存器130输入的区块地址信号BA,将输出信号输出。逻辑电路LC在区块地址信号BA命中(hit)的区块解码器162中,所有输出信号成为“H”电平,在未命中的区块解码器162中,任一个输出信号成为“L”电平。

与门电路AND包含连接于逻辑电路LC的输出端的输入端、及连接于反相器INV1的输入端的输出端,且将来自逻辑电路LC的输出信号的与门结果输出到该输出端。反相器INV1包含连接于节点N1的输出端,且将从与门电路AND接收的信号的反转信号输出到节点N1。反相器INV2包含连接于节点N1的输入端、及连接于n型晶体管Tr1的第1端的输出端。反相器INV2将从反相器INV1接收的信号的反转信号(也就是说,从与门电路AND输出的信号)输出到n型晶体管Tr1的第1端。此外,逻辑电路LC、与门电路AND、以及反相器INV1及INV2由电源电压VDD驱动。

n型晶体管Tr1包含连接于n型晶体管Tr2的第1端的第2端、及被供给电源电压VDD的栅极。n型晶体管Tr2包含连接于节点BLKSEL的第2端、及被供给电源电压VDD的栅极。n型晶体管Tr1及Tr2可利用电源电压VDD而成为导通状态。

n型晶体管Tr3包含连接于节点VRDEC的第1端、连接于p型晶体管Tr4的第1端的第2端、及连接于节点BLKSEL的栅极。供给到节点VRDEC的电压例如为图30中所示的传输开关群161不将配线CG等的电压箝位便能够传输到字线WL等的程度的高电压。p型晶体管Tr4包含连接于节点BLKSEL的第2端、与p型晶体管Tr4的第1端一起连接于n型晶体管Tr3的第2端的背栅极、及连接于节点N1的栅极。

通过以如上的方式构成,区块解码器162在选择对应的区块BLK的情况下对节点BLKSEL输出“H”电平的信号,在未选择的情况下能够输出“L”电平的信号。

具体来说,区块解码器162在逻辑电路LC中区块地址信号BA命中的情况下,将“L”电平的信号输出到节点N1,并且将“H”电平的信号输出到节点BLKSEL。随之,p型晶体管Tr4成为导通状态并且n型晶体管Tr3成为弱导通状态,将利用n型晶体管Tr3箝位的节点VRDEC的电压传输到节点BLKSEL,节点BLKSEL的电压上升。n型晶体管Tr3利用上升的节点BLKSEL的电压成为强导通状态,且能够对节点BLKSEL传输更高的电压。通过重复所述动作,节点BLKSEL电平转换到供给到节点VRDEC的电压为止。

另外,区块解码器162当在逻辑电路LC中区块地址信号BA未命中的情况下,将“H”电平的信号输出到节点N1,并且将“L”电平的信号输出到节点BLKSEL。随之,n型晶体管Tr3及p型晶体管Tr4成为断开状态,利用供给到节点BLKSEL的电压而传输开关群161将配线CG等与字线WL等之间电切断。

6.5应用例的效果

在区块解码器162中,由于对节点BLKSEL传输高电压,所以n型晶体管Tr2及Tr3、以及p型晶体管Tr4设计为比n型晶体管Tr1更高耐压,且将这些相互邻接地形成在衬底上。在这种情况下,如上所述,存在如下可能性:由n型晶体管Tr2及Tr3的制造工序引起,经由n型晶体管Tr2及Tr3与p型晶体管Tr4之间所形成的元件分离区域的下方,形成n型晶体管Tr2及Tr3内的p

根据将所述各实施方式的p型晶体管2应用于p型晶体管Tr4的本应用例,N阱区域13由n

另外,p型晶体管Tr4由于取源极与背栅极共通连接于n型晶体管Tr3的第2端的构成,所以在本应用例中也能够应用第3实施方式及第4实施方式的p型晶体管2,所以能够发挥与第3实施方式及第4实施方式同等的元件面积削减效果。

7.其它

对本发明的几个实施方式进行了说明,但这些实施方式是作为示例而提出的,并不旨在限定发明的范围。这些新颖的实施方式能够以其它的各种方式实施,在不脱离发明的主旨的范围内,能够进行各种省略、置换、变更。这些实施方式或其变化包含在发明的范围或主旨中,并且包含在权利要求书中所记载的发明及其均等的范围中。

[符号说明]

1 半导体装置

2 p型晶体管

5 p型半导体衬底

10 P阱区域

11、16、16B、26、26C、27、27C 绝缘体层

12 n

13 N阱区域

14、14A、14B、14C n

15、18、20、22、28、29 触点

17、19 p

21、21C、24、24C、25、25C 导电体层

23 栅极绝缘膜

31、32、34、35、36、36C、37、37A、37B、37C 抗蚀剂材料

33 掩模材料

38 层间绝缘膜

100 半导体存储装置

110 存储单元阵列

120 指令寄存器

130 地址寄存器

140 定序器

150 驱动器模块

160 行解码器模块

161 传输开关群

162 区块解码器

170 感测放大器模块

200 存储器控制器

BLK 区块

SU 串单元

MT 存储单元晶体管

ST1、ST2 选择晶体管

BL 位线

WL 字线

SGD 选择栅极线

- 半导体光发射装置的制造方法、半导体光发射装置、半导体装置的制造方法、半导体装置、一种装置的制造方法、以及一种装置

- 碳化硅半导体装置的制造方法、半导体基体的制造方法、碳化硅半导体装置以及碳化硅半导体装置的制造装置