制造半导体器件和电子器件的方法

文献发布时间:2023-06-19 11:52:33

技术领域

本申请的实施例涉及制造半导体器件和电子器件的方法。

背景技术

随着半导体工业在追求更高的器件密度、更高的性能和更低的成本的过程中进入纳米技术工艺节点,来自制造和设计问题的挑战促进了高分辨率图案化操作(诸如极紫外(EUV)光刻)的发展。在光刻操作中,聚焦裕度是关键问题之一。聚焦裕度受衬底(晶圆)的表面形貌和/或衬底的变形(例如,翘曲)的影响。因此,重要的是,在高级光刻操作中获得较平坦的衬底表面。此外,衬底的变形和/或翘曲也影响其他半导体制造操作,并且可能降低半导体器件的可靠性。

发明内容

本申请的一些实施例提供了一种制造电子器件的方法,包括:制备包括具有不同热膨胀系数的两种或更多种材料的结构;以及对所述结构进行低温处理,其中,在所述低温处理期间,不执行其他制造操作。

本申请的另一些实施例提供了一种制造半导体器件的方法,所述方法包括:在衬底上或上方执行第一制造操作;在所述衬底上或上方执行第二制造操作;以及在所述第一制造操作与所述第二制造操作之间执行低温处理操作,其中,所述第一制造操作和所述第二制造操作中的至少一个包括在200℃或更高温度下进行的热操作,以及在所述低温处理期间,不执行其他制造操作。

本申请的又一些实施例提供了一种制造半导体器件的方法,所述方法包括:在衬底上或上方执行第一制造操作;在所述第一制造操作之后测量所述衬底的翘曲值;在所述衬底上或上方执行第二制造操作;以及在所述第一制造操作与所述第二制造操作之间执行低温处理操作,其中,在执行所述低温处理操作之前或之后执行测量所述翘曲值。

附图说明

当与附图一起阅读时,根据以下详细描述可最好地理解本发明。要强调的是,根据行业的标准实践,各种部件并未按照比例绘制,并且仅用于说明目的。实际上,为论述清楚,各种部件的尺寸可任意增加或减少。

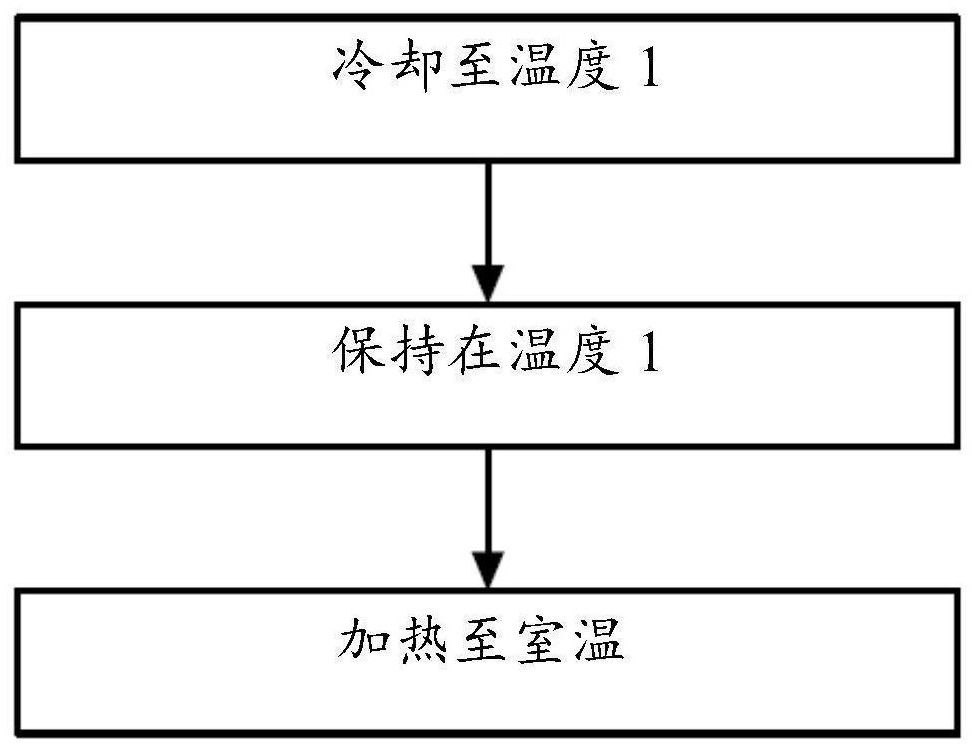

图1A是根据本发明的实施例的低温处理的流程。图1B示出根据本发明的实施例的低温处理中的温度变化。图1C示出翘曲的定义和测量。图1D和图1E示出说明低温处理的效果的示意图。

图2A示出根据本发明的实施例的用于测量低温处理的效果的样品结构。图2B和图2C示出根据本发明的实施例的相对于不同的金属图案比率低温处理操作在减小翘曲方面的效果。

图3示出根据本发明的实施例的相对于不同的条件低温处理操作在减小翘曲方面的效果。

图4A、图4B和图4C示出根据本发明的实施例的进行低温处理的各种结构。

图5示出根据本发明实施例的在半导体器件制造操作期间的低温处理的工艺流程。

图6A和图6B示出根据本发明实施例的在半导体器件制造操作期间的低温处理的工艺流程。

图7示出根据本发明实施例的在半导体器件制造操作期间的低温处理的工艺流程。

图8A、图8B和图8C示出根据本发明的实施例的用于低温处理的装置。

具体实施方式

可以理解,以下公开提供了用于实现本发明的不同特征的许多不同的实施例或实例。以下描述了元件和布置的实例的具体实施例以简化本发明。当然,这些仅仅是实例,并非旨在限制本发明。例如,元件的尺寸不限于所公开的范围或值,而是可以取决于工艺条件和/或器件的期望特性。此外,在以下描述中,在第二部件上方或上形成第一部件可以包括第一部件与第二部件直接接触的实施例,也可以包括形成为插入第一部件和第二部件的附加部件,使得第一部件与第二部件不直接接触的实施例。为了简明和清楚起见,可以以不同比例任意绘制各种部件。在附图中,为了简化起见,可以省略一些层/部件。

而且,为了便于描述,在此可以使用诸如“在…之下”、“在…下方”、“下部”、“在…之上”、“上部”等空间相对术语,以描述如图所示的一个元件或部件与另一个(或另一些)元件或部件的关系。除了各图中所描绘的取向之外,空间相对术语还旨在涵盖器件在使用或操作中的不同取向。器件可以以其他方式进行定向(旋转90度或者处于其他方向),而其中所使用的空间相关描述符可以做相应解释。另外,术语“由...制成”可以意指“包含”或“由...组成”。此外,在后续制造工艺中,在所描述的操作中/之间可存在一个或多个附加操作,并且可以改变操作的顺序。在本发明中,除非另有说明,否则短语“A、B和C中的一个”是指“A、B和/或C”(A、B、C、A和B、A和C、B和C或A、B和/或C),并且不意指来自A的一个元件、来自B的一个元件和来自C的一个元件。

在半导体器件制造过程中,执行各种热工艺。当在半导体晶圆或衬底上方的多层结构或图案化结构上执行热工艺(加热或退火)时,热膨胀系数(CTE)的失配会引起较高的内应力,进而导致晶圆或衬底翘曲(弯曲、挠曲、变形)或并最终导致变形。此种翘曲可能影响半导体集成电路(IC)制造或封装工艺的质量和良率。

减小翘曲的一些方法包括(1)改变工艺和/或材料,以及(2)通过外力施加高温的热压印工艺。然而,这些方法对于大批量制造不是优选的,因为工艺/材料的改变会缩小工艺窗口,并且热压印工艺可能会降低良率并且可能无法在具有富金属层的结构上工作。

在本发明中,将低温处理在对半导体器件进行连续制造操作期间应用于半导体晶圆,在切割工艺之前和/或之后应用于半导体芯片并且应用于模制在IC封装中的芯片,以减小晶圆、芯片和/或衬底的内应力和/或翘曲。

图1A是根据本发明的实施例的低温处理的流程。图1B示出根据本发明的实施例的低温处理中的温度变化。

在本发明中,低温处理(工艺)包括将主体结构(例如,其上具有一个或多个膜的半导体晶圆)从室温(例如,25℃)冷却至低温,将结构保持在低温下,并将结构加热至室温,如图1A和图1B所示。在一些实施例中,低温处理操作之前的晶圆或衬底的温度高于或低于室温。

冷却工艺增加了主体结构中的应力和/或变形。然后,将主体结构保持在低温下,在此期间内应力减小或松弛。然后,加热工艺进一步减小了应力和变形。如果主体结构的材料表现出塑性变形效果,则与初始应力/变形相比,低温处理后的应力/变形减小。低温处理会(通过热膨胀系数失配)提供与温度有关的应力并引起塑性变形,然后通过塑性变形效应减小室温下的内应力。

在一些实施例中,取决于期望的应力减小和/或各种冷却剂或冷却方法,将低温(保持温度)T1设定为在约-10℃至约-273℃范围内。在其他实施例中,保持温度T1设定成在约-20℃至约-269℃范围内。在其他实施例中,保持温度T1设定成在约-20℃至约-196℃范围内。在某些实施例中,保持温度T1设定成在约-30℃至约-100℃范围内。在某些实施例中,保持温度T1设定成在约-150℃至约-200℃范围内。

保持持续时间P2在一些实施例中在约0.1分钟至约120分钟范围内,而在其他实施例中在约1分钟至约60分钟范围内。在其他实施例中,保持持续时间P2在约2分钟至约30分钟范围内。在某些实施例中,保持持续时间P2在约5分钟至约10分钟范围内。如果保持持续时间P2短于这些范围,则翘曲减小的效果可能不足,并且如果保持持续时间P2大于这些范围,则将降低工艺效率。

在一些实施例中,在时间段P1中温度降低的速率(冷却速率)在约-0.1℃/分钟至约-100℃/分钟范围内。在其他实施例中,在时间段P1中温度降低的速率在约-1℃/分钟至约-50℃/分钟范围内。在其他实施例中,在时间段P1中温度降低的速率在约-5℃/分钟至约-10℃/分钟范围内。冷却速率太小,翘曲减小的效果可能不足,并且如果冷却速率太高,则可能对晶圆或衬底造成损伤(例如,破裂)。

在一些实施例中,时间段P3中温度升高的速率(加热速率)在约0.1℃/分钟至约100℃/分钟范围内。在其他实施例中,在时间段P3中温度升高的速率在约1℃/分钟至约50℃/分钟范围内。在某些实施例中,在时间段P3中温度升高的速率在约5℃/分钟至约10℃/分钟范围内。如果加热速率太小,则翘曲减小的效果可能不足,并且如果加热速率太高,则可能对晶圆或衬底造成损伤(例如,破裂)。

在一些实施例中,冷却速率等于加热速率(绝对值),而在其他实施例中,冷却速率大于或小于加热速率。冷却速率和/或加热速率可在冷却操作和/或加热操作期间改变。在一些实施例中,在时段P4处晶圆或衬底的温度高于或低于室温。

在一些实施例中,翘曲被定义为自由的、未夹紧的晶圆的中间表面到参考位置的最大距离与最小距离之间的差,如图1C所示。通过围绕晶圆边缘的三点平面或通过执行在测量扫描期间获取的中间表面数据的最小二乘拟合计算来计算中间表面的位置。然后通过找到与参考平面的最大偏差和与参考平面的最小差异来计算翘曲。最大差异定义为参考平面上方的最大距离,为正数,而最小差异定义为参考平面下方的最大距离,为负数。翘曲的测量工具和测量方法是本领域普通技术人员已知的。在一些实施例中,简单地将晶圆弯曲成具有弓形,并且针对弓形类似地限定和测量翘曲。在一些实施例中,在背面或正面或两侧上测量翘曲。

在一些实施例中,在低温处理操作之后,翘曲的值减小但可不为零。在一些实施例中,残余翘曲在约1μm至约10000μm范围内,并且在约10μm至约1000μm范围内。在其他实施例中,残余翘曲在约-1μm至约-10000μm范围内,并且在其他实施例中,在约-10μm至约-1000μm范围内。负号表示翘曲是凸形。

图1D示出说明低温处理的效果的概念图。如图1D所示,在硅晶圆上方形成金属层。金属膜形成包括热工艺,例如,在300℃下加热晶圆。然后,将晶圆冷却至室温。由于金属层与硅晶圆的热膨胀系数之间的差异,整个晶圆向下弯曲成凸形(弯曲翘曲)。另一方面,由于金属层和硅晶圆的热膨胀系数之间的差异,具有金属膜的硅晶圆在非常低的温度例如-60℃下冷却。整个晶圆具有内应力以使晶圆向下弯曲成凸形。在低温处理操作(温度处于室温)之后,如图1D所示,整个翘曲(弯曲)减小。

图1E示出说明低温处理的效果的另一示意图。向量示出应力,其可由σ

图2A至图2C和图3示出根据本发明的实施例的通过低温处理操作对减小翘曲的效果。图2A示出根据本发明的实施例的用于测量低温处理的效果的样品结构。

在一些实施例中,如图2A所示,在晶圆或衬底上方形成金属层。在一些实施例中,晶圆或衬底是硅晶圆。在一些实施例中,金属层被图案化。取决于图案,金属比率(整个晶圆上的金属图案面积或衬底面积)可能会改变。图2B和图2C示出根据本发明的实施例的相对于不同的金属材料和不同的金属图案比率的低温处理操作对减小翘曲的效果。如图2A和图2B所示,翘曲减小取决于图案比率和/或材料以及保持温度T1。

图3示出根据本发明的实施例的相对于不同的条件低温处理操作对减小翘曲的效果。在图3中,时间段P4是在低温处理操作至翘曲测量时间之后晶圆或衬底返回室温之后的持续时间。在一些实施例中,P4之前的时间对应于低温处理操作与下一个工艺操作之间的持续时间。

如图3所示,在一些实施例中,较低的保持温度提供较高的翘曲减小。在一些实施例中,翘曲减小效果没有示出对持续时间P4的特定依赖性,这意味着翘曲减小效果在执行低温处理操作之后是稳定的。

在本发明中,经过低温处理的结构包括:半导体晶圆(6英寸、8英寸、12英寸等)、从晶圆切割的半导体芯片、密封有半导体芯片的半导体封装、光掩模、用于显示器件(液晶显示器、发光器件显示器等)的透明衬底(例如,玻璃衬底)和/或布置有一个或多个电子器件的电路板。

在一些实施例中,半导体晶圆或衬底至少在其表面部分上包括单晶半导体层。晶圆或衬底包括单晶半导体材料,诸如但不限于Si、Ge、SiGe、GaAs、InSb、GaP、GaSb、InAlAs、InGaAs、GaSbP、GaAsSb和InP。在其他实施例中,晶圆或衬底是绝缘体上硅(SOI),其用于制造半导体器件和/或微机电系统。

在一些实施例中,光掩模包括由玻璃、石英或其他低热膨胀材料制成的透明衬底。光掩模包括金属层,在一些实施例中,诸如Cr基材料层。在其他实施例中,光掩模是反射掩模,并且包括Si和Mo、Ta、Ta合金和/或Ru的多层结构。

半导体封装包括模制树脂(例如,聚酰亚胺、环氧树脂)、陶瓷(例如,氧化铝)、金属、导电框架和引线以及其他材料。如上所述,不同的材料具有不同的热膨胀系数。

在一些实施例中,尽管通过低温处理减小了翘曲,但可保留残余翘曲(翘曲不为零)。

图4A、图4B和图4C示出根据本发明的实施例的在半导体制造操作期间出现的进行了低温处理的各种结构。

在一些实施例中,晶圆或衬底包括半导体晶圆、半导体衬底(芯片)、玻璃衬底、聚合物衬底等。在一些实施例中,半导体晶圆或衬底至少部分地掺杂有杂质。

在一些实施例中,如图4A和图4B所示,在晶圆或衬底的正面和/或晶圆或衬底的背面上形成一个或多个膜(层)。膜包括绝缘层、包括导电金属合金和金属的金属层,或半导体层。绝缘层包括氧化硅、氮化硅、SiON、SiOC、SiOCN、氧化铝、AlON、高k介电层(例如,HfO

在一些实施例中,金属层包括W、Cu、Ti、Ag、Al、Mn、Co、Pd、Ni、Re、Ir、Ru、Pt、Zr、Au、Ag、TiN、WN、TaN、TiAl、TiAlN、TaC、TaCN、TaSiN、TiAlC、TaAlC、硅化物,其合金,诸如Ti-Al、Ru-Ta、Ru-Zr、Pt-Ti、Co-Ni、WN

在一些实施例中,半导体层包括单晶、多晶或非晶Si、Ge、IV族化合物半导体(硅锗(SiGe)、碳化硅(SiC)、碳化硅锗(SiGeC)、GeSn、SiSn、SiGeSn))、掺杂或未掺杂的III-V族化合物半导体(例如,砷化镓(GaAs)、砷化铟镓(InGaAs)、砷化铟(InAs)、磷化铟(InP)、锑化铟(InSb)、磷砷化镓(GaAsP)或磷化铟镓(GaInP))。

通过热氧化、热氮化或等离子氮化、物理气相沉积(PVD)(诸如溅射法)、化学气相沉积(CVD)、等离子增强化学气相沉积(PECVD)、大气压化学气相沉积(APCVD)、低压CVD(LPCVD)、高密度等离子CVD(HDPCVD)、原子层沉积(ALD)、分子束外延、电镀和/或其他工艺来形成膜。

在一些实施例中,如图4C所示,对一个或多个层进行图案化。CTE的差异会导致内应力和/或翘曲,而不均匀的结构(图案或掺杂区)也会导致内应力和/或翘曲。

图5示出根据本发明实施例的在半导体器件制造操作期间的低温处理的工艺流程。

在一些实施例中,在图5的S501处接收晶圆或衬底作为进入的晶圆或衬底。在一些实施例中,进入的晶圆是在执行半导体制造工艺之前的裸硅晶圆。在一些实施例中,进入的晶圆是具有一个或多个被图案化或未被图案化的膜的经过处理的晶圆。

然后,在一些实施例中,在图5的S502处测量初始翘曲值。在图5的S503处,如果测得的初始翘曲值在阈值(例如,阈值范围)内,则在图5的S504处,使晶圆或衬底进行下一个制造工艺,例如光刻操作。光刻操作包括紫外线(UV)光刻(g线和i线光刻)、深UV(DUV)光刻(KrF和ArF光刻)、极UV(EUV)光刻或电子束光刻。如果测量的初始翘曲值不在阈值内,则在图5的S505处对晶圆或衬底进行低温处理操作。在一些实施例中,低温处理操作的条件是预定的,而在其他实施例中,根据测量的翘曲值来调整低温处理操作的条件。在低温处理操作之后,再次测量翘曲值。如果测得的翘曲值在阈值内,则晶圆或衬底进入下一个制造工艺,而如果测得的初始翘曲值不在阈值内,则以相同的或修改的低温处理操作条件对该晶圆或衬底再次进行低温处理操作。重复测量和低温处理操作,直到测得的翘曲值在阈值内。在一些实施例中,在低温处理操作期间,不执行物理上改变晶圆或衬底的结构的其他制造操作,诸如离子注入操作、蚀刻操作、图案化操作和膜沉积操作。

图6A和图6B示出根据本发明实施例的在半导体器件制造操作期间的低温处理的工艺流程。

在一些实施例中,如图6A所示,在执行制造工艺之后执行低温处理操作。在S601处,接收晶圆或衬底作为进入的晶圆或衬底。在一些实施例中,进入的晶圆是在执行半导体制造工艺之前的裸硅晶圆。在一些实施例中,进入的晶圆是具有一个或多个被图案化或未被图案化的膜的经过处理的晶圆。

然后,在图6A的S602处,对进入的晶圆执行一个或多个半导体制造操作。在一些实施例中,制造操作包括膜形成操作,诸如热氧化、CVD、ALD、PVD和任何其他膜形成方法。在一些实施例中,膜形成方法伴随热工艺,其中,在适合于相应膜形成方法的工艺温度下加热晶圆。在一些实施例中,工艺温度在约1000℃至1200℃范围内。在一些实施例中,工艺温度在约800℃至1000℃范围内。在一些实施例中,工艺温度在约500℃至800℃范围内。在一些实施例中,工艺温度在约250℃至500℃范围内。在一些实施例中,制造操作包括平坦化操作,诸如回蚀操作或化学机械抛光操作。

在一些实施例中,制造操作包括图案化操作,诸如干蚀刻和湿蚀刻。在一些实施例中,干蚀刻包括等离子干蚀刻或化学(非等离子)干蚀刻。在一些实施例中,干蚀刻操作包括热工艺,其中,在适合于相应干蚀刻方法的工艺温度下加热晶圆。在一些实施例中,工艺温度在约100℃至200℃范围内。在一些实施例中,工艺温度在约200℃至300℃范围内。在一些实施例中,工艺温度在约300℃至400℃范围内。在一些实施例中,工艺温度在约400℃至600℃范围内。在一些实施例中,湿蚀刻包括在约100℃至200℃的工艺温度下的H

在膜形成操作和/或图案化操作之后,将晶圆或衬底冷却至室温。

在图6A的S603处,测量翘曲值。然后,在图6A的S604处,在晶圆上执行低温处理操作。在一些实施例中,低温处理操作的条件是预定的,而在其他实施例中,根据测量的翘曲值来调整低温处理操作的条件(前馈)。在一些实施例中,在低温处理操作之后,可选地在S605处再次测量翘曲值。在S606处,如果测得的翘曲值在阈值内,则晶圆或衬底进入下一个制造工艺,而如果测得的初始翘曲值不在阈值内,则以相同的或修改的低温处理操作条件对该晶圆或衬底再次进行低温处理操作。重复测量和低温处理操作,直到测得的翘曲值在阈值内。在其他实施例中,如果测得的翘曲值超出期望范围,则将晶圆报废或不执行后续操作。在其他实施例中,在低温处理操作之后,在S605处使晶圆进行下一个制造操作而不测量翘曲值。在一些实施例中,在S605处测得的结果被反馈回S604,以用于进行低温处理操作的后续晶圆。

在一些实施例中,下一个制造操作S606包括光刻操作、测量操作、清洁操作、热操作(退火)、膜形成操作、蚀刻操作和/或离子注入操作。

在一些实施例中,如图6B所示,在执行制造工艺之前执行低温处理操作。在S611处,接收晶圆或衬底作为进入的晶圆或衬底。在一些实施例中,进入的晶圆是在执行半导体制造工艺之前的裸硅晶圆。在一些实施例中,进入的晶圆是具有一个或多个被图案化或未被图案化的膜的经过处理的晶圆。

在图6B的S612处,测量翘曲值。然后,在图6B的S613处,对晶圆执行低温处理操作。在一些实施例中,低温处理操作的条件是预定的,而在其他实施例中,根据测量的翘曲值来调整低温处理操作的条件(前馈)。在一些实施例中,在低温处理操作之后,可选地在再次测量翘曲值。在S614处,如果测得的翘曲值在阈值内,则晶圆或衬底进入下一个制造工艺,而如果测得的初始翘曲值不在阈值内,则以相同的或修改的低温处理操作条件对该晶圆或衬底再次进行低温处理操作。重复测量和低温处理操作,直到测得的翘曲值在阈值内。在其他实施例中,如果测得的翘曲值超出期望范围,则将晶圆报废或不执行后续操作。

在一些实施例中,在翘曲测量之后,使晶圆进行下一个制造工艺,而无需重复低温处理操作。在其他实施例中,在低温处理操作之后,使晶圆进行下一个制造工艺而不测量翘曲值。

然后,在图6B的S614处,对进入的晶圆执行一个或多个半导体制造操作。在一些实施例中,制造操作包括膜形成操作,诸如热氧化、CVD、ALD、PVD和任何其他膜形成方法。在一些实施例中,膜形成方法包括热工艺,其中,在适合于相应膜形成方法的工艺温度下加热晶圆。在一些实施例中,工艺温度在约1000℃至1200℃范围内。在一些实施例中,工艺温度在约800℃至1000℃范围内。在一些实施例中,工艺温度在约500℃至800℃范围内。在一些实施例中,工艺温度在约250℃至500℃范围内。

在一些实施例中,制造操作包括图案化操作,诸如干蚀刻和湿蚀刻。在一些实施例中,干蚀刻包括等离子干蚀刻或化学(非等离子)干蚀刻。在一些实施例中,干蚀刻操作包括热工艺,其中,在适合于相应干蚀刻方法的工艺温度下加热晶圆。在一些实施例中,工艺温度在约100℃至200℃范围内。在一些实施例中,工艺温度在约200℃至300℃范围内。在一些实施例中,工艺温度在约300℃至400℃范围内。在一些实施例中,工艺温度在约400℃至600℃范围内。在一些实施例中,湿蚀刻包括在约100℃至200℃的工艺温度下的H

在膜形成操作和/或图案化操作之后,将晶圆或衬底冷却至室温。

在一些实施例中,在S615处的测量结果被反馈回S613,以用于进行低温处理操作的后续晶圆。

图7示出根据本发明实施例的在半导体器件制造操作期间的低温处理的工艺流程。

在一些实施例中,在图7的S701处,在晶圆上方形成膜(例如,导电膜),然后执行包括一种或多种光刻的图案化操作以及蚀刻操作。取决于图案比率(剩余图案的总面积占蚀刻总面积的比),翘曲值会改变。在一些实施例中,在图7的S702处。获得操作S701的图案比率。可从用于图案化操作中的掩模图案的设计布局数据获得图案比率。然后,在图7的S703处,基于图案比率,调整或确定低温处理操作的一个或多个参数。在图7的S704中,基于调整后的参数,执行低温处理操作。在一些实施例中,在S701和S703之间执行一个或多个制造操作。

图8A、图8B和图8C示出根据本发明的实施例的用于低温处理的装置。

在一些实施例中,用于低温处理的装置是如图8A所示的接触型装置。在接触型装置中,将主体结构(晶圆或衬底)放置在被冷却剂冷却的冷却台上。在一些实施例中,冷却剂包括液体和/或冷却的气态氮、氧和/或氦、冷却的二氧化碳、冷却的碳氢化合物或任何其他合适的冷却剂。在一些实施例中,在低温处理操作期间,冷却剂由泵循环并且温度由温度控制器控制。台的温度由温度控制器控制。在一些实施例中,例如通过将液氮与气态氮混合和/或通过电加热器或珀耳帖(Peltier)器件加热/冷却台来控制冷却剂的温度。在一些实施例中,腔室处于真空下。在其他实施例中,腔室填充有干燥气体,诸如干燥惰性气体。在腔室内填充的气体温度下,将干燥气体的湿度控制在露点以下。

在其他实施例中,用于低温处理的装置是如图8B所示的环境型装置。将冷却的气体引入腔室。冷却的气体包括空气、氮气、二氧化碳、氧气、氦气、碳氢化合物和任何其他合适的气体中的一种或多种。气体的湿度控制在露点以下。在一些实施例中,在低温处理操作期间,冷却的气体由泵循环并且温度由温度控制器控制。气体的温度由温度控制器控制。在一些实施例中,图8A和图8B的温度控制方法一起使用。

在其他实施例中,如图8C所示,用于低温处理的装置是浸入总线类型。在一些实施例中,冷却剂(诸如液氮)或其他合适的冷却剂存储在具有入口和出口的总线中,并且将经过低温处理操作的一个或多个晶圆浸入该冷却剂中。在一些实施例中,将存储在晶圆盒或支架中的晶圆浸入冷却液中的速度是受控参数。在一些实施例中,保持一个或多个晶圆的晶圆盒保持在冷却剂(例如,液氮)的上表面上方,以冷却晶圆而不浸入。

在一些实施例中,根据本发明的实施例的用于低温处理的装置是独立装置或集成在诸如膜沉积装置、等离子处理装置或任何其他半导体制造装置等另一装置中。

在一些实施例中,在低温处理操作期间,晶圆没有被固定或夹紧到晶圆台,使得晶圆不受外力作用。在其他实施例中,在低温处理操作的一部分或全部其中,通过例如夹具或静电夹持机构将晶圆紧密地固定到晶圆台。在一些实施例中,在图1B所示的时间段P1、P2、P3和P4中的至少一个期间,晶圆不受外力作用。在一些实施例中,在冷却时间段(图1B的P1)期间,晶圆不受外力(没有夹持),并且在低温处理操作的剩余时间段(图1B的P2、P3)中将晶圆夹持到晶圆台。在其他实施例中,在保持时间段(图1B的P2)期间,晶圆不受外力作用,并且在剩余时间段(图1B的P1、P3)中,将晶圆夹持到晶圆台。在其他实施例中,在加热时间段(图1B的P3)期间,晶圆不受外力作用,并且在剩余时间段(图1B的P1、P2)中,将晶圆夹持到晶圆台。

在其他实施例中,将低温处理操作应用于封装和/或组装操作,诸如背磨工艺、切割工艺、预烧工艺、模制工艺、引线接合工艺等。

在一些实施例中,在晶圆上的操作完成之后,通过研磨晶圆的背面来使晶圆变薄。在一些实施例中,在研磨之前和/或之后,执行低温处理操作以减小翘曲或内应力。然后,将减薄的晶圆通过框架附接至粘合膜上,然后进行切割以将晶圆分离成多个芯片。在一些实施例中,在切割之前和/或之后,对附接至粘合膜的晶圆或芯片进行低温处理操作,以减小翘曲或内应力。在一些实施例中,使用如图8C所示的浸入总线执行低温处理操作。

切割后,拾取每个芯片(管芯),并进行管芯键合操作,以将芯片附接至引线框架,并通过导线将芯片接合至引线。在引线键合操作之后,芯片和引线框架由树脂模制。在一些实施例中,在模制操作之前和/或之后,执行低温处理操作以减小翘曲或内应力。此外,在一些实施例中,将中介层附接至模制芯片,以将模制芯片附接至另一衬底,诸如布线板。在附接中介层之前和/或之后,执行低温处理操作以减小翘曲或内应力。

将认为,并非在本文中必须讨论所有优点,没有特定优点对于所有实施例都是需要的,并且其他实施例可以提供不同的优点。

根据本发明的一个方面,在制造电子器件的方法中,制备包括具有不同热膨胀系数的两种或更多种材料的结构,并且对该结构进行低温处理。在所述低温处理期间,不执行其他制造操作。在前述和以下实施例中的一个或多个中,该结构包括半导体晶圆并且一个或多个层形成在该半导体晶圆上。在一个或多个前述和以下实施例中,所述低温处理包括:将所述结构冷却至在-10℃至-273℃范围内的第一温度;将所述结构在所述第一温度下保持在0.1分钟至120分钟范围内的持续时间;以及将所述结构从所述第一温度加热至高于0℃的第二温度。在一个或多个前述和以下实施例中,所述持续时间在约1分钟至约60分钟范围内。在一个或多个前述和以下实施例中,所述第一温度在-10℃至-100℃范围内。在一个或多个前述和以下实施例中,所述第一温度在-50℃至-200℃范围内。在一个或多个前述和以下实施例中,所述冷却或所述加热中的至少一种包括以逐步方式改变温度。在一个或多个前述和以下实施例中,在所述低温处理之前执行一个或多个半导体制造操作。在一个或多个前述和以下实施例中,所述一个或多个半导体制造操作包括在200℃或更高的温度下进行的热操作。在一个或多个前述和以下实施例中,所述一个或多个半导体制造操作包括图案化操作。在一个或多个前述和以下实施例中,在所述低温处理之前执行一个或多个半导体制造操作。在一个或多个前述和以下实施例中,所述一个或多个半导体制造操作包括光刻操作。

根据本发明的另一方面,在制造半导体器件的方法中,在衬底上或上方执行第一制造操作;在所述衬底上或上方执行第二制造操作;以及在所述第一制造操作与所述第二制造操作之间执行低温处理操作。所述第一制造操作和所述第二制造操作中的至少一个包括在200℃或更高温度下进行的热操作。在所述低温处理期间,不执行其他制造操作。在一个或多个前述和以下实施例中,所述低温处理包括:将所述结构冷却至在-10℃至-273℃范围内的第一温度;将所述结构在所述第一温度下保持在0.1分钟至120分钟范围内的持续时间;以及将所述结构从所述第一温度加热至高于0℃的第二温度。在一个或多个前述和以下实施例中,所述冷却中的冷却速率在-0.1℃/分钟至约-100℃/分钟范围内。在一个或多个前述和以下实施例中,所述加热中的加热速率在0.1℃/分钟至约100℃/分钟范围内。在一个或多个前述和以下实施例中,通过控制放置所述衬底的台的温度或控制放置所述衬底的腔室的环境温度中的至少一个来控制所述第一温度。在一个或多个前述和以下实施例中,在所述低温处理操作之后,所述衬底包括非零值的翘曲。

根据本发明的另一方面,在制造半导体器件的方法中,在衬底上或上方执行第一制造操作;在所述第一制造操作之后测量所述衬底的翘曲值;在所述衬底上或上方执行第二制造操作;以及在所述第一制造操作与所述第二制造操作之间执行低温处理操作。在执行所述低温处理操作之前或之后执行所述翘曲值的测量。在一个或多个前述和以下实施例中,在执行所述低温处理操作之前执行所述翘曲值的测量,并且所述方法还包括基于测得的翘曲值来调整所述低温处理操作的一个或多个参数。在一个或多个前述和以下实施例中,在执行所述低温处理操作之前执行所述翘曲值的测量,当测得的翘曲值超出阈值范围时,执行附加低温处理操作,并且当所述测得的翘曲值在所述阈值范围内时,执行所述第二制造操作。在一个或多个前述和以下实施例中,所述第一制造操作包括膜形成工艺、蚀刻工艺、平坦化工艺和热工艺中的一种或多种,以及所述第二制造操作包括EUV光刻操作。

前文概述了若干实施例或实例的部件,以使得本领域技术人员可更好地理解本发明的各方面。本领域的技术人员应该理解的是,他们可以轻松地将本发明作为基础来设计或修改用于实施与本文所介绍实施例的相同目的和/或实现相同的优点的其他工艺或结构。本领域技术人员还应认识到,这种等效结构并不背离本发明的精神和范围,并且其可以进行各种更改、替换和变更而不背离本发明的精神和范围。

- 半导体基板、半导体基板的制造方法、电子器件、以及电子器件的制造方法

- 电子器件、半导体器件以及制造电子器件的方法