过电压保护

文献发布时间:2023-06-19 12:16:29

本申请要求于2020年2月4日提交的法国申请号20/01096的优先权,该申请通过引用结合于此。

技术领域

本公开总体上涉及电子电路,并且更具体地,涉及防止能够在这种电子电路的焊盘之间(特别是在静电放电之后)发生的过电压。

背景技术

能够借助于电磁波,例如借助于射频波进行通信的无线通信设备。当第一设备的天线接收到由第二设备发射的电磁波时,由第一设备的天线接收的电力可用于向第一设备的电路(例如集成电路)供电。为此目的,第一设备通常包括整流电压桥,整流电压桥被配置为接收在耦合到第一设备的天线的导电绕组的相应端的两个焊盘或端子之间可用的电压,并传递整流后的电源电压。

然而,例如由静电放电引起的过电压可能发生在耦合到天线的导电绕组的相应端的两个焊盘之间。这种过电压能够恶化,或者甚至破坏耦合到两个焊盘中的至少一个焊盘的第一设备的电路,特别是耦合到焊盘的整流桥。

发明内容

需要克服已知无线通信设备的全部或部分缺点,特别是关于保护这些设备不受过电压(例如由静电放电引起的过电压)的影响,该过电压能够发生在耦合到天线的导电绕组的相应端的焊盘之间。

一种实施例克服了已知无线通信设备的全部或部分缺点。

一种实施例克服了已知无线通信设备的全部或部分缺点,这些缺点是由于例如由静电放电引起的过电压造成的,这些过电压能够发生在耦合到这些设备的天线的导电绕组的相应端的焊盘之间。

一种实施例克服了已知电压整流桥的全部或部分缺点,电压整流桥被配置为整流在耦合到无线通信设备的天线的导电绕组的相应端的两个焊盘之间可用的电压。

一种实施例提供了包括整流桥的设备,整流桥包括:第一分支,连接在桥的第一输入节点和第二输入节点之间并包括桥的第三输出节点;第二分支,包括串联连接在第一节点和第二节点之间的第一MOS晶体管和第二MOS晶体管,第一晶体管和第二晶体管的源极被耦合到桥的第四输出节点;第一电阻器,连接在第一晶体管的栅极和第二节点之间;第二电阻器,连接在第二晶体管的栅极和第一节点之间;以及电路,对于第一晶体管和第二晶体管中的每一个,该电路与晶体管相关联并包括连接到晶体管的漏极的第一端子和连接到晶体管的栅极的第二端子,该电路被配置为当电路的第一端子与另一电路的第一端子之间的电压的绝对值大于或等于电路的阈值的绝对值并且电压具有与阈值相同的符号时,电耦合电路的第一端子和第二端子。

根据一种实施例,每个电路还被配置为当电路的第一端子和另一电路的第一端子之间的电压的绝对值小于电路的阈值的绝对值时,并且当电压具有与电路的阈值的符号相反的符号时,电隔离电路的第一端子和第二端子。

根据一种实施例,桥的第一分支包括串联连接在第一节点和第二节点之间的第三MOS晶体管和第四MOS晶体管,并且每个均被组装成二极管,第三晶体管和第四晶体管的源极连接到第三节点。

根据一种实施例,第一晶体管、第二晶体管、第三晶体管和第四晶体管具有相同的N沟道或P沟道。

根据一种实施例,每个电路包括分支,分支包括反串联耦合的具有二极管功能的第一偶极子和具有二极管功能的第二偶极子,分支的一端连接到电路的第一端子,并且分支的另一端连接到另一电路的第一端子。

根据一种实施例,在每个电路中,第一偶极子和第二偶极子被配置为:当电路的第一端子和另一电路的第一端子之间的电压的绝对值小于电路的阈值的绝对值、并且当电压具有与电路的阈值的符号相反的符号时阻断电流,并且当电路的第一端子与另一电路的第一端子之间的电压的绝对值大于或等于电路的阈值的绝对值且电压具有与阈值相同的符号时传导电流。

根据一种实施例,每个电路被配置为使得电路的第一偶极子中的电流的传导引起电路的第一端子和第二端子的电耦合。

根据一种实施例,在电路中的至少一个电路中,优选地在每个电路中,电路分支的另一端连接到电路的第二端子。

根据一种实施例,在电路的至少一个电路中,优选地,在每个电路中,电路的分支包括:第五节点、第六节点和第七节点;第三电阻器,串联连接到第五节点和第六节点之间的第一偶极子;以及第四电阻器,连接在第六节点和第七节点之间,每个电路还包括晶体管,晶体管具有连接到第六节点的控制端子,并且具有分别连接到第五节点和第七节点的导电端子,第四电阻器中的电压降调节晶体管的导通。

根据一种实施例,在电路中的至少一个电路中,优选地在每个电路中:第二偶极子连接在电路的第一端子和第五节点之间,第七节点连接到电路的第二端子;或者第二偶极子连接在第七节点和电路的第二端子之间,第五节点连接到电路的第一端子;或者第二偶极子连接在电路的第一端子和第七节点之间,第五节点连接到电路的第二端子;或者第二偶极子连接在第五节点和电路的第二端子之间,第七节点连接到电路的第一端子。

根据一种实施例,在至少一个电路中,优选地在每个电路中,电路分支的另一端连接到电路的第三端子,电路的第三端子连接到另一电路的第一端子。

根据一种实施例,在至少一个电路中,优选地在每个电路中,分支包括与第一偶极子和第二偶极子串联的第三电阻器,每个电路还包括晶体管,该晶体管具有连接到第三电阻器的端子的控制端子,具有耦合到电路的第一端子的第一导电端子,并且具有耦合到电路的第二端子的第二导电端子,第三电阻器中的电压降调节晶体管的导通。

根据一种实施例,在至少一个电路中,优选地在每个电路中,第二偶极子连接在电路的第一端子和晶体管的第一导电端子之间,晶体管的第二导电端子连接到电路的第二端子。

根据一种实施例,至少一个电路,优选每个电路,还包括具有二极管功能的第三偶极子,该第三偶极子串联连接到电路的第一端子和第二端子之间的电路的晶体管,第三偶极子连接到电路的第二端子,并且电路的分支连接到电路的第一端子和第三端子之间。

根据一种实施例,第一偶极子由齐纳二极管、相互并联连接的多个齐纳二极管的组件,或者由多个串联连接的MOS晶体管的组件形成,每个MOS晶体管是组装二极管。

另一实施例提供了一种集成电路,其包括如所述的设备。

附图说明

上述特征和优点以及其它特征和优点将在以下参考附图以说明而非限制的方式给出的特定实施例的描述中详细描述,在附图中:

图1以电路的形式示出了包括整流桥的示例的设备的一部分;

图2示出了说明不同MOS晶体管导通操作的多条曲线;

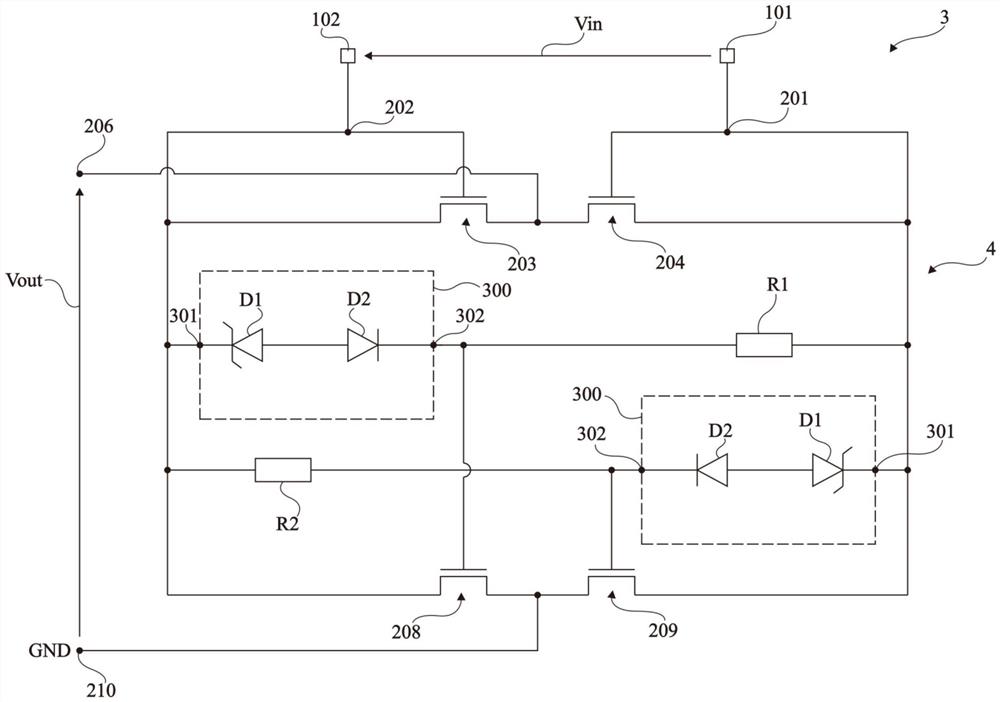

图3以电路的形式示出了根据一实施例的包括整流桥的设备的一部分;

图4以电路的形式示出了根据另一实施例的包括整流桥的设备的一部分;

图5以电路的形式示出了根据又一实施例的包括整流桥的设备的一部分;和

图6以电路的形式示出了根据又一实施例的包括整流桥的设备的一部分。

具体实施方式

在各种附图中,相同的特征已经由相同的参考标号标出。特别地,在各种实施例中共同的结构和/或功能特征可以具有相同的参考标号,并且可以设置相同的结构、尺寸和材料特性。

为了清楚起见,仅详细说明和描述了对理解在此描述的实施例有用的步骤和元件。特别地,没有详细描述各种无线通信协议,特别是通过射频波的无线通信协议及其实现,所描述的实施例与已知的无线通信协议和此类协议的已知实现兼容。此外,还没有描述由包括耦合到设备的两个焊盘的电压整流桥的已知设备实现的功能,在两个焊盘之间有待整流的电压可用,所描述的实施例与这种已知设备的通常功能兼容。

除非另有指示,当提及连接在一起的两个元件时,这表示没有除导体之外的任何中间元件的直接连接,并且当提及耦合在一起的两个元件时,这表示这两个元件可以连接或者它们可以经由一个或多个其它元件耦合。

在以下公开中,除非另有指示,当参考诸如术语“前”、“后”、“顶”、“底”、“左”、“右”等的绝对位置限定符,或诸如术语“上”、“下”、“高”、“低”等的相对位置限定符,或诸如“水平”、“垂直”等的定向限定符时,参考图中所示的定向。

除非另有说明,表达“大约”、“近似”、“基本上”和“以…的顺序”表示在10%以内,并且优选在5%以内。

在下面的描述中,除非另有指示,所有电位和电压都相对于相同的参考电位参考,通常是接地GND,或者换句话说,零参考电压。

图1以电路的形式示出了包括整流桥2的示例的设备1的一部分。

在该示例中,设备1是包括导电天线绕组或电感或线圈(未示出)的无线通信设备,其端部分别连接到设备1的焊盘或端子101和焊盘或端子102。在以下描述中,设备1是射频通信设备,例如,近场通信或NFC设备1的情况被考虑为一个示例。

例如,可以在焊盘101和焊盘102之间连接具有N沟道(未示出)的MOS(金属氧化物半导体)晶体管,以实现由设备1的设备的天线接收的电磁场的逆向调制(retromodulation)功能。逆向调制MOS晶体管具有第一导电端子,例如其源极耦合(优选地连接)到焊盘102,以及第二导电端子,例如其漏极耦合(优选地连接)到焊盘101。

例如,电容器(未示出)可以设置在焊盘101和102之间,以调节设备1的天线的谐振频率。

图1更具体地示出了设备1的电压整流桥2。

桥2耦合到焊盘101和102以接收待整流的电压Vin。电压Vin对应于节点102的电位和节点101的电位之间的差,并且在本示例中电压参照节点101。作为示例,电压Vin具有小于6V的最大幅度,例如等于5.5V(电压Vin例如范围从-5.5V到+5.5V)。

整流桥2被配置为将整流电源电压Vout传送到设备1的电路(未示出)。电压Vout对应于桥2的输出节点206的电位与桥2的输出节点210的电位之间的差,并且电压Vout在本示例中参照节点210。在该示例中,节点210处于参考电位GND,典型地为地。

整流桥2包括耦合到相应焊盘101和焊盘102的两个节点或端子201和端子202。在所示的示例中,节点201和节点202连接到相应的焊盘101和焊盘102。根据未示出的另一示例,节点201和节点202分别通过低值电阻器(通常为几欧姆)耦合到焊盘101和焊盘102。

整流桥2包括并联在输入节点201和202之间的两个分支。

两个分支中的一个包括串联连接在节点201和节点202之间的两个N沟道MOS晶体管203和204。晶体管203和晶体管204在桥2的节点206的电平上彼此连接,或者换句话说,晶体管203和204中的每一个都连接到节点206。每个晶体管203、204是组装二极管(diode-assembled),即其栅极和漏极彼此连接。在所示的示例中,晶体管203的漏极和栅极连接到节点202,晶体管204的漏极和栅极连接到节点201,晶体管203和204的源极连接到节点206,或者换句话说,在节点206的电平上连接在一起。

根据未示出的另一示例,晶体管203和晶体管204中的每一个晶体管可以用二极管替换,例如,通过用其阳极连接到节点202并且其阴极连接到节点206的二极管替换晶体管203,并且用其阳极连接到节点201并且其阴极连接到节点206的另一二极管替换晶体管204。

整流桥2的两个分支中的另一个包括串联连接在节点201和202之间的两个N沟道MOS晶体管208和209。晶体管208和晶体管209在整流桥2的节点210的电平上彼此连接,或者换句话说,晶体管208和晶体管209中的每一个都连接到节点210。例如,晶体管208的漏极连接到节点202,源极连接到节点210,栅极连接到节点201,晶体管209的漏极连接到节点201,源极连接到节点210,栅极连接到节点202。

晶体管208和209使其主体区或沟道形成区耦合,优选地连接到节点210,以处于节点210的电位。

在操作中,当AC电压Vin在焊盘101和102之间可用时,因此在本示例中,在节点201和节点202之间可用时,整流桥2传递整流电压Vout。特别地,当节点202的电位充分大于节点201的电位时,晶体管203和209导通,晶体管204和208截止。相反,当节点201的电位充分大于节点202的电位时,晶体管203和209截止,晶体管204和208导通。

考虑过电压发生在焊盘102和焊盘101之间,并且因此发生在节点201和202之间,这种过电压例如对应于焊盘102的电位相对于焊盘101的电位的增加,或者正过电压。根据人体模型或HBM,正过电压例如来自焊盘102上的静电放电,例如1.5kV或甚至2kV的静电放电。这种静电放电例如由人触摸焊盘102或耦合到焊盘102的设备1的导电天线绕组引起。

焊盘102和101之间的这种正过电压导致在焊盘102和101之间流动例如至少1A的显著电流,例如经由晶体管208从焊盘102流向节点210,并且经由基底(主体)和晶体管209的漏极之间的正向偏置二极管从节点210流向焊盘101的正电流。

由于晶体管208的栅极和源极基本上处于相同的电位,即节点210的电位,因此晶体管208应当截止。然而,当MOS晶体管208的漏极和源极之间的电位差超过称为快回(snapback)阈值的阈值时,MOS晶体管208的寄生双极晶体管开始导通,并且电流从MOS晶体管208的漏极流到源极。这样的电流然后经由晶体管209的主体(基底)区域和漏极之间的正向二极管流到节点201。晶体管208的漏极和源极之间的电流传导在晶体管208的导电端子之间具有负的差分阻抗,这引起了一个问题。

当借助于并联连接的多个基本MOS晶体管来实现MOS晶体管208时,出现这种问题的示例。实际上,由于制造分散,这些基本晶体管中的第一个基本晶体管的快回阈值可能低于所有其它基本晶体管的快回阈值。因此,第一基本MOS晶体管的寄生双极晶体管的导通发生在其它基本MOS晶体管的寄生双极晶体管的导通之前。然后,流过MOS晶体管208的所有电流流过第一基本MOS晶体管,这可能导致第一基本MOS晶体管的劣化或甚至破坏。

尽管这没有详细说明,但是上文所示的在焊盘102和焊盘101之间的正过电压期间,与晶体管208有关的问题以对称的方式针对在焊盘102和焊盘101之间的过电压期间的晶体管209提出,该过电压对应于节点201的电位相对于节点202的电位的增加,或者负过电压。

为了克服整流桥2的全部或部分缺点,发明人在此提供了与晶体管208和晶体管209中的每一个相关联的所谓的导通电路,该导通电路具有分别连接到晶体管208或晶体管209的漏极和栅极的第一端子和第二端子,该晶体管208或209具有与其相关联的电路。此外,电阻器连接在晶体管208的栅极和节点201(晶体管209的漏极)之间,另一电阻器连接在晶体管209的栅极和节点202(晶体管208的漏极)之间。

每个导通电路被配置成当其第一端子与另一电路的第一端子之间的电压大于或等于电路的阈值时电耦合其第一端子和第二端子。换句话说,与晶体管208相关联的导通电路中的第一导通电路被配置为当其第一端子(晶体管208的漏极-节点202)和与晶体管209相关联的第二导通电路的第一端子(晶体管209的漏极-节点201)之间的电压超过第一电路的阈值时,电耦合其第一端子和第二端子,第二电路被配置为当其第一端子和第一电路的第一端子之间的电压超过第二电路的阈值时,电耦合其第一端子和第二端子。该电路的第一端子和另一电路的第一端子之间的电压超过所考虑的导通阈值表示节点201和节点202之间的过电压。

此外,每个导通电路被配置为当电路的第一端子和另一电路的第一端子之间的电压小于电路的阈值时,使其第一端子和第二端子彼此电隔离或去耦合。换句话说,第一电路被配置为:当第一电路的第一端子和第二电路的第一端子之间的电压小于第一导通电路的阈值时,电隔离其第一端子和第二端子,第二电路被配置为:当第二电路的第一端子和第一电路的第一端子之间的电压小于第二电路的阈值时,电隔离其第一端子和第二端子。因此,在节点201和节点202之间不存在过电压的情况下,整流桥的操作不因导通电路的存在而改变,并且类似于结合图1描述的整流桥2操作。

在下面的描述和权利要求中,术语具有二极管功能的偶极子表示具有两个端子的组件或电路,在两个端子之间,组件或电路起二极管的作用。偶极子的端子中的一个端子被称为偶极子的阴极,偶极子的另一端子称为偶极子的阳极。偶极子在其阳极和阴极之间具有与二极管分别在其阳极和阴极之间具有的行为相同的行为。

根据一实施例,每个导通电路包括分支,该分支包括反串联耦合的具有二极管功能的第一偶极子和具有二极管功能的第二偶极子,该分支的一端连接到导通电路的第一端子,而该分支的另一端耦合到另一导通电路的第一端子。包括具有反串联耦合的二极管功能的第一偶极子和第二偶极子的术语分支表示在该分支中,第一偶极子和第二偶极子的阳极耦合在一起,或者它们的阴极耦合在一起的情况。

根据一实施例,每个导通电路包括连接到另一电路的第一端子的第三端子。在这种实施例中,在每个导通电路中,包括反串联的第一偶极子和第二偶极子的分支连接在电路的第一端子和第三端子之间,或者换句话说,分支的一端连接到电路的第一端子,而分支的另一端连接到电路的第三端子。

根据另一实施例,在每个导通电路中,包括反串联的第一偶极子和第二偶极子的分支连接在电路的第一端子和第二端子之间,或者换句话说,分支的一端连接到电路的第一端子,而分支的另一端连接到电路的第二端子。

根据一实施例,在每个导通电路中,第一偶极子和第二偶极子被配置为当电路的第一端子和另一电路的第一端子之间的电压小于电路的阈值时阻断电流。

根据一实施例,在每个导通电路中,第一偶极子和第二偶极子还被配置为当电路的第一端子和另一电路的第一端子之间的电压大于或等于电路的阈值时传导电流。

根据一实施例,每个导通电路被配置为使得电路的第一偶极子中的电流的传导引起电路的第一端子和第二端子的电耦合。

根据一实施例,在每个导通电路中,第二偶极子的正向导通阈值和第一偶极子的反向导通阈值至少部分地确定导通电路的阈值。具有二极管功能的偶极子的正向导通阈值这一术语指定(designate)偶极子阳极相对于偶极子阴极的电压值,高于该值,偶极子将正电流从其阳极传导到其阴极。类似地,术语具有二极管功能的偶极子的反向导通阈值指定偶极子阴极相对于偶极子阳极的电压值,高于该值,偶极子将正电流从其阴极传导到其阳极。

图2示出了曲线C0、C2、C3、C4、C5和C6,这些曲线示出了MOS晶体管(本例中为N沟道)的不同导通情况。每个曲线说明当晶体管的源极接地GND并且晶体管漏极的电位Vd增加时,晶体管的漏极和源极之间的电流Is的变化。每个曲线对应于施加到晶体管栅极的不同电位。

图2中的曲线C0说明了施加到晶体管栅极的电位为零或换句话说等于地电位GND的情况。当晶体管的漏极电位Vd增加超过晶体管快回阈值Vsb时,晶体管然后在其导电端子之间具有负差分阻抗。更具体地,只要电位Vd低于阈值Vsb,电流Is为零或接近零。此外,在电位Vd已经达到阈值Vsb之后,非零电流Is流过晶体管,由于晶体管的负差分阻抗,电流Is在电位Vd减小的同时增加。

曲线C2、C3、C4、C5和C6示出施加到晶体管栅极的电位为非零的情况,该电位对于曲线C3比对于曲线C2高,对于曲线C4比对于曲线C3高,对于曲线C5比对于曲线C4高,并且对于曲线C6比对于曲线C5高。

可以观察到,对于曲线C2的情况,所考虑的晶体管仍然具有负差分阻抗,即,该曲线具有电流Is增大而电位Vd减小但负阻抗的值小于曲线C0的情况的部分。对于曲线C3、C4、C5和C6的情况,这种负差分阻抗被抑制。

进一步可以观察到,晶体管栅极上的电位越高,电位Vd所能取的最大值就越低。

还可以观察到,对于给定的电位值Vd,晶体管栅极上的电位越高,电流Is值越高。

因此,提供与各个晶体管208和209相关联的导通电路,使得在节点201和节点202之间的导致晶体管之一的漏极电位增加的过电压期间,与晶体管相关联的导通电路能够导致晶体管的栅极电位的相应增加。因此,晶体管如曲线C3、C4、C5和C6所示工作,不再具有负差分阻抗。此外,对于给定的漏极电位,在节点201和节点202之间的过电压期间,该晶体管的栅极电位将越高,在晶体管的导电端子之间流动的电流Is就越高,因此允许更有效地防止过电压。

现在将结合图3至图6描述导通电路的几个实施例和变型。

图3以电路的形式示出了包括整流桥4的设备3的一部分,整流桥4设置有根据一实施例的导通电路。

设备3类似于图1中的设备1,这里仅详述设备1和设备3之间的差异。

更具体地,设备3与设备1的不同之处在于其电压整流桥4,与电压整流桥2不同。与整流桥2相比,整流桥4包括连接在节点201和晶体管208的栅极之间的电阻器R1,以及连接在节点202和晶体管209的栅极之间的电阻器R2。整流桥4与整流桥2的进一步不同之处在于,对于晶体管208和209中的每一个,整流桥4包括与晶体管相关联的导通电路300。每个电路300包括第一端子301和第二端子302。与晶体管208(分别为209)相关联的电路300的端子301连接到晶体管208(分别为209)的漏极,并且其端子302连接到晶体管208(分别为209)的栅极。

每个电路300包括分支,该分支包括反串联耦合在一起的具有二极管功能D1的第一偶极子和具有二极管功能D2的第二偶极子。

在图3所示的实施例中,在每个电路300中,包括反串联的偶极子D1和D2的分支连接在电路的端子301和302之间,或者换句话说,具有连接到电路300的端子301的一端和连接到电路300的端子302的另一端。

在图3的示例中,在每个电路300中,偶极子D1和D2的阴极连接在一起并且它们的阳极分别连接到端子301和302。在未示出的另一示例中,在每个电路300中,偶极子D1和D2的阳极连接在一起并且它们的阴极分别连接到端子301和302。

桥4的正常操作,即在节点201和202之间不存在过电压的情况下,如下所示。由于节点201和202之间不存在过电压,节点202和201之间的电压(节点202相对于节点201的电压)小于与晶体管208相关联的电路300的阈值,并且节点201和202之间的电压(节点201相对于节点202的电压)小于与晶体管209相关联的电路300的阈值。然后,与晶体管208(分别为209)相关联的电路300的偶极子D1和D2阻断在与晶体管208(分别为209)相关联的电路的端子301和302之间的电流的流动,并阻断电流通过电阻器R1(分别为R2)。因此,节点202(分别为201)的电位存在于晶体管209(分别为208)的栅极上。

更具体地,在图3的示例中,当节点202的电位大于节点201的电位时,与晶体管209相关联的电路300的偶极子D2被反向偏置并且等效于开路。此外,与晶体管208相关联的电路300的偶极子D1也被反向偏置,但其两端的电压小于其反向导通电压,由此偶极子D2等效于开路。此外,一旦节点202和节点201之间的电压变得大于晶体管209的阈值电压,晶体管209就切换到导通状态并将节点201电耦合到节点210,晶体管208处于截止状态。

当节点201的电位大于节点202的电位时,桥4的正常操作可以通过对称性从上述操作中推导出来。

在节点201和202之间的过电压期间桥4的操作如下。正过电压的情况被认为是一个示例。晶体管209及其相关联的电路300然后表现为正常操作,或者换句话说,与晶体管209相关联的电路300等效于其端子301和302之间的开路,并且晶体管209导通。此外,一旦节点202和节点201之间的电压变得大于与晶体管208相关联的电路300的阈值,电流就流过电路的偶极子D1和D2并流过电阻器R1。因此,晶体管208的栅极电位随着节点202的电位而增加。换句话说,晶体管208的栅极上的电位然后等于节点202的电位减去与晶体管208相关联的电路300的偶极子D1和D2中的电压降。在图3的示例中,每个电路300的阈值等于偶极子D1的反向导通阈值和偶极子D2的正向导通阈值之和。

在节点201和202之间的负过电压情况下的桥4的操作可以通过对称性从上文的在正过电压情况下的操作中推导出来。

图4以电路的形式示出了根据另一种实施例的包括整流桥4-1的设备3-1的一部分。

设备3-1类似于图3中的设备3,这里只详细说明了设备3-1和设备3之间的差异。更具体地,设备3-1与设备3的不同之处在于其电压整流桥4-1,与电压整流桥4不同,整流桥4-1包括导通电路300-1而不是整流桥4的每个电路300。每个电路300-1包括第一端子301和第二端子302。与晶体管208(分别为209)相关联的电路300-1的端子301连接到晶体管208(分别为209)的漏极,并且其端子302连接到晶体管208(分别为209)的栅极。

每个电路300-1包括分支,该分支包括反串联耦合在一起的具有二极管功能D1的第一偶极子和具有二极管功能D2的第二偶极子。

在图4所示的实施例中,在每个电路300-1中,包括反串联的偶极子D1和D2的分支连接在电路的端子301和302之间。在每个电路300-1中,包括反串联的偶极子D1和D2的分支还包括串联连接到节点401和节点402之间的第一偶极子D1的电阻器R3,以及连接到节点402和节点403之间的电阻器R4。每个电路300-1还包括晶体管T,晶体管T具有连接到节点402的控制端子,并且具有分别连接到端子401和403的导电端子。每个电路被配置为使得其电阻R4中的电压降调节其晶体管T的导通。

根据一实施例,如图4所示,在每个电路300-1中,晶体管T是P沟道MOS晶体管,晶体管T的源极和漏极然后耦合,优选地分别连接到节点403和401。优选地,晶体管T的主体区耦合到晶体管T的源极,使得晶体管T的主体区和源极区处于相同的电位。

在未示出的替代实施例中,在每个电路300-1中,晶体管T被PNP双极晶体管取代,其基极形成晶体管的控制端子并连接到节点402,其发射极连接到节点403,并且其集电极连接到节点401。

根据一实施例,如图4所示,在每个电路300-1中,偶极子D2连接在节点401和电路300-1的端子302之间。更具体地,在本示例中,偶极子D2的阴极连接到电路300-1的端子302。然后,在本示例中,节点403连接到端子301。在未示出的替代实施例中,在每个电路300-1中,偶极子D2连接在端子301和电路300-1的节点403之间。更具体地,偶极子D2的阳极例如连接到电路300-1的端子301,节点401例如连接到端子302。

桥4-1的正常操作类似于前面描述的桥4(图3)的正常操作。特别地,在每个电路300-1中,当没有电流流过电路300-1的偶极子D1和D2时,电阻R4两端的电压为零,并且晶体管T截止。因此,没有电流在电路300-1的端子301和302之间流动,也没有电流流过电阻器R1和R2。

在节点201和202之间的过电压期间桥4的操作如下。正过电压的情况被认为是一个示例。与正常操作中一样,与晶体管209相关联的电路300-1等效于其端子301和302之间的开路,并且晶体管209导通。此外,一旦节点202和节点201之间的电压变得大于与晶体管208相关联的电路300-1的阈值,电流就流过偶极子D1和D2,并流过电路的电阻器R3和R4。一旦电阻器R4中的电压降大于晶体管T的阈值电压,晶体管T导通,并且电流不仅经由电阻器R4和R3以及偶极子D1,而且经由晶体管T,在节点403和401之间流动。因此,一旦节点202和节点201之间的电压变得大于与晶体管208相关联的电路300-1的阈值,晶体管208的栅极电位就随着节点202的电位而增加。特别地,一旦电路300-1的晶体管T导通,晶体管208的栅极上的电位等于节点202的电位减去晶体管T的阈值电压、电阻器R3中的电压降、以及电路300-1的偶极子D1和D2中的电压降。

在图4-1的示例中,每个电路300-1的阈值等于偶极子D1的反向导通阈值和偶极子D2的正向导通阈值之和。此外,在每个电路300-1中,当电路的端子301和302之间的电压超过偶极子D1的反向导通阈值、偶极子D2的正向导通阈值和晶体管T的阈值电压之和时,晶体管T切换到导通状态。

在节点201和202之间的负过电压情况下的桥4-1的操作可以通过对称性从上文描述的在正过电压情况下的操作中推导出来。

电路300-1相对于电路300的优点在于,一旦其晶体管T导通,它能够在其端子301和302之间传导更大的电流,由此与之相关联的晶体管208或209的栅极上的电位更高。

电路300-1相对于电路300的另一优点是,一旦电路的晶体管T导通,偶极子D1中的电流较小。当偶极子D1未被配置为传导显著电流和/或偶极子D1的内部电阻为高时,这是特别有利的。

虽然这在图4中未示出,但是在每个电路300-1中,频率补偿电容器可以设置在节点401和403之间和/或频率补偿电容器可以设置在节点401和402之间。这样的电容器允许电路300-1在过电压的情况下有更快的响应。然而,这些电容器中的每一个的值优选地被选择为相对低,例如低于1pF,以避免在焊盘101和102之间不存在过电压的情况下干扰桥4-1的操作。

图5以电路的形式示出了根据又一种实施例的包括整流桥4-2的设备3-2的一部分。

设备3-2类似于图4中的设备3-1,这里只详细说明了设备3-2和设备3-1之间的差异。更具体地,设备3-2与设备3-1的不同之处在于其电压整流桥4-2,整流桥4-2包括导通电路300-2,而不是整流桥4-1的每个电路300-1。每个电路300-2包括第一端子301、第二端子302以及在该实施例中的第三端子303。与晶体管208(分别为209)相关联的电路300-2的端子301连接到晶体管208(分别为209)的漏极,其端子302连接到晶体管208(分别为209)的栅极,并且其端子303连接到节点201(分别为202)。

每个电路300-2包括分支,该分支包括反串联耦合在一起的具有二极管功能D1的第一偶极子和具有二极管功能D2的第二偶极子。

在该实施例中,在每个电路300-2中,包括反串联的偶极子D1和D2的分支连接在电路的端子301和303之间。在每个电路300-2中,包括反串联的偶极子D1和D2的分支还包括串联连接到偶极子D1和D2的电阻器R4。每个电路300-2还包括晶体管T,晶体管T具有连接到电阻器R4的端子502的控制端子,具有耦合到电路300-2的端子301的导电端子503,以及具有耦合到电路300-2的端子302的另一导电端子504。每个电路300-2被配置为使得其电阻器R4中的电压降调节其晶体管T的导通。

根据一实施例,如图5所示,在每个电路300-2中,晶体管T是P沟道MOS晶体管,其源极503耦合到电路300-2的端子301,其漏极504耦合到电路的端子302。电阻器R4的与端子502相反的端子然后连接到晶体管T的端子503。优选地,晶体管T的主体区耦合到晶体管T的源极,使得晶体管T的主体区和源极区处于相同的电位。根据未示出的替代实施例,在每个电路300-2中,晶体管T被PNP双极晶体管取代,其基极形成晶体管的控制端子并连接到电阻器R4的端子502,其发射极503耦合到电路300-2的端子301,并且其集电极505耦合到电路300-2的端子302。在该变型中,电阻器R4的与端子502相反的端子然后连接到晶体管的发射极503。

根据一实施例,如图5所示,在每个电路300-2中,晶体管T的端子503连接到电路300-2的端子301,偶极子D2连接在晶体管T的端子503和电路300-2的端子303之间,例如,其阴极位于电路的端子303侧,例如连接到端子303。然后,电路300-2进一步包括具有二极管功能D3的偶极子,该偶极子串联连接到晶体管T,在晶体管T的端子503和端子302之间,优选地在晶体管T的端子504和电路300-2的端子302之间,偶极子D3的阴极例如连接到电路300-2的端子302。偶极子D3被配置为当电路300-2的端子301和另一电路300-2的端子301之间的电压小于该电路的阈值时,阻断电路300-2的端子301和302之间的电流。换句话说,偶极子D3被配置为当桥处于正常操作时,即,特别是当端子302上的电位大于该电路的端子301上的电位时,阻断电路300-2的端子301和302之间的电流。

桥4-2的正常操作类似于前面描述的桥4(图3)的正常操作。特别地,在每个电路300-2中,没有电流流过电路300-2的偶极子D1、D2和D3,由此在电路300-2的端子301与电路的端子302和303中的每一个之间没有电流流动。

在节点201和202之间的过电压期间桥4-2的操作如下。正过电压的情况被认为是一个示例。与正常操作中一样,与晶体管209相关联的电路300-2等效于其端子301和302之间的开路,并且晶体管209导通。此外,一旦节点202和节点201之间的电压变得大于与晶体管208相关联的电路300-2的阈值,电流就流过电路偶极子D1和D2,并因此流过电阻器R4。一旦电阻器R4中的电压降大于晶体管T的阈值电压,晶体管T就切换到导通状态,并且电流在电路的端子301和302之间流动,从而流过电阻器R4。因此,晶体管208的栅极电位随着节点202的电位而增加。换句话说,晶体管208的栅极上的电位然后等于节点202的电位减去晶体管T的端子503和504之间的电压降和偶极子D3中的电压降。在图5的示例中,每个电路300的阈值等于偶极子D1的反向导通阈值、偶极子D2的正向导通阈值和晶体管T的阈值电压之和。

作为示例,考虑偶极子D2和D3具有等于0.6V的正向导通阈值且偶极子D1具有等于5V的反向导通阈值的情况。在这种情况下,当电流由于端子301和303之间的电压(相对于端子303)大于电路300-2的阈值而从端子301流向端子302时,晶体管T的栅极上的电压至多可以等于5.6V,即偶极子D2的正向导通阈值和偶极子D1的反向导通阈值之和。然后电阻R4承受晶体管T的栅极上的电压和端子301上的电压之间的差值。一旦晶体管T导通,端子301和302之间的电压降等于偶极子D3的正向导通阈值,忽略晶体管T的导通端之间的电压降。因此,然后端子302上的电压等于节点202上的电压减去D3中的0.6V,并且当节点202上的电压为7V时,端子302上的电压可以等于6.4V。通过在图4的情况下使用这样的数值示例,电路的端子302上的电压至多等于节点202上的电压减去D2的正向导通阈值、D1的反向导通阈值和晶体管T的导通阈值之和,例如等于0.7V,这导致端子302上的电压等于0.7V,并且比图5的情况小得多。

在节点201和202之间的负过电压情况下的桥4-2的操作可以通过对称性从上文描述的在正过电压情况下的操作中推导出来。

在未示出的替代实施例中,在每个电路300-2中,偶极子D2连接在电路300-2的端子301和晶体管T的端子503之间,例如,偶极子D2的阳极连接到端子301。在该变型中,晶体管T的端子504连接到电路300-2的端子302。此外,在该变型中,可以省略偶极子D3,其电流阻断功能由偶极子D2确保。然而,在本变型中,修改晶体管T的主体区的连接,以避免在正常操作中,当端子302的电位大于端子301的电位时,晶体管T的漏极体二极管正向导通,并且可能导通晶体管T的NPN双极晶体管,其发射极对应于晶体管T的漏极,其基极对应于其中形成有晶体管T的N型阱,其集电极对应于其中形成有N型阱的P型基底。例如,然后可以设置晶体管T与交叉连接在晶体管T的源极和漏极之间的两个MOS晶体管相关联,以确保晶体管T的N阱处于晶体管T的两个源极和漏极电位中的较低电位。

本领域技术人员能够基于上述操作描述根据该变型的桥4-2的操作。

与电路300-1相比,电路300-2的上述实施例和变型的优点在于,一旦其晶体管T导通,其能够减小其端子301和302之间的电压降。因此,与其相关联的晶体管208或209的栅极上的电位更高。

尽管这在图5中未示出,但频率补偿电容器可与偶极子D1并联设置和/或频率补偿电容器可与晶体管T并联设置。这些电容器允许在过电压的情况下电路300-2的更快响应。然而,这些电容器中的每一个的值优选地选择为相对低,例如低于1pF,以避免在焊盘101和102之间不存在过电压的情况下干扰桥4-2的操作。

图6以电路的形式示出了根据又一实施例的包括整流桥4-3的设备3-3的一部分。

设备3-3类似于图4中的设备3-1,这里只详细说明了设备3-3和设备3-1之间的差异。更具体地,设备3-3与设备3-1的不同之处在于其电压整流桥4-3,整流桥4-3包括导通电路300-3,而不是整流桥4-1的每个电路300-1。每个电路300-3包括第一端子301和第二端子302。与晶体管208(分别为209)相关联的电路300-3的端子301连接到晶体管208(分别为209)的漏极,其端子302连接到晶体管208(分别为209)的栅极。

每个电路300-3包括分支,该分支包括反串联耦合在一起的具有二极管功能D1的第一偶极子和具有二极管功能D2的第二偶极子。

在该实施例中,在每个电路300-3中,包括反串联的偶极子D1和D2的分支连接在电路的端子301和302之间。在每个电路300-3中,包括反串联的偶极子D1和D2的分支还包括串联连接到节点601和节点602之间的第一偶极子D1的电阻器R3,以及连接在节点602和节点603之间的电阻器R4。每个电路300-3还包括晶体管Tb,晶体管Tb具有连接到节点602的控制端子,并且具有分别连接到节点601和603的导电端子。每个电路被配置为使得其电阻器R4中的电压降调节其晶体管Tb的导通。

根据一实施例,如图6所示,在每个电路300-3中,晶体管Tb是NPN双极晶体管,然后晶体管Tb的发射极和集电极分别被耦合(优选地连接)到节点603和601。在未示出的替代实施例中,在每个电路300-3中,双极晶体管Tb被N沟道MOS晶体管取代,N沟道MOS晶体管的栅极形成连接到节点602的晶体管的控制端子,源极连接到节点603,漏极连接到节点601。优选地,然后将MOS晶体管的主体区耦合到晶体管的源极,使得晶体管的主体区和源极区处于相同的电位。

根据一实施例,如图6所示,在每个电路300-3中,偶极子D2连接在节点603和电路300-2的端子302之间,偶极子D2的阴极例如连接到电路300-1的端子302。在未示出的替代实施例中,在每个电路300-2中,偶极子D2连接在电路300-3的端子301和节点601之间,偶极子D2的阳极例如连接到电路300-3的端子301。

桥4-3的正常操作类似于前面描述的桥4(图3)的正常操作。特别地,在每个电路300-3中,当没有电流流过电路300-3的偶极子D1和D2时,电阻R4两端的电压为零,晶体管Tb截止。因此,在电路300-3的端子301和302之间没有电流流动,在电阻器R1和R2中也没有电流流动。

在节点201和202之间的过电压期间,桥4-3的操作如下。正过电压的情况被认为是一个示例。与正常操作中一样,与晶体管209相关联的电路300-3等效于其端子301和302之间的开路,并且晶体管209导通。此外,一旦节点202和节点201之间的电压变得大于与晶体管208相关联的电路300-3的阈值,电流就流过电路的偶极子D1和D2并流过电阻器R4。一旦电阻器R4中的电压降大于晶体管Tb的阈值电压,电流不仅经由电阻器R3和R4以及偶极子D1,而且经由晶体管Tb,在节点601和603之间流动。因此,一旦节点202和节点201之间的电压变得大于电路300-3的阈值,晶体管208的栅极电位就随着节点202的电位而增加。特别地,一旦电路300-3的晶体管Tb导通,晶体管208的栅极上的电位就等于节点202的电位减去晶体管Tb的阈值电压、电阻器R3中的电压降以及电路300-3的偶极子D1和D2中的电压降。

在图6的示例中,每个电路300-3的阈值等于偶极子D1的反向导通阈值和偶极子D2的正向导通阈值之和。此外,一旦电路的端子301和302之间的电压超过偶极子D1的反向导通阈值、偶极子D2的正向导通阈值和晶体管Tb的阈值之和,晶体管Tb就切换到导通状态。

在节点201和202之间的负过电压情况下的桥4-3的操作可以通过对称性从上文描述的在正过电压情况下的操作中推导出来。

电路300-3相对于电路300的优点在于,一旦其晶体管Tb导通,电路300-3能够在其端子301和302之间传导更显著的电流,由此与之相关联的晶体管208或209的栅极上的电位更高。

虽然这在图6中未示出,但是在每个电路300-3中,频率补偿电容器可以设置在节点601和603之间和/或频率补偿电容器可以设置在节点601和602之间。这种电容器允许电路300-3在过电压的情况下的更快响应。然而,这些电容器中的每一个的值优选地选择为相对低,例如低于1pF,以避免在焊盘101和102之间不存在过电压的情况下干扰桥4-3的操作。

根据一实施例,上述电路300-1、300-2和300-3的偶极子D1由单个齐纳二极管实现。

根据另一实施例,上述电路300、300-1、300-2和300-3的偶极子D1借助于并联的多个齐纳二极管来实现,这使得当电流流过偶极子D1时,能够减小偶极子D1的内阻并因此减小其端子之间的电压降。

根据又一实施例,上述电路300、300-1、300-2和300-3的偶极D1通过串联的多个MOS晶体管来实现,每个MOS晶体管是组装二极管,即,其漏极和栅极连接在一起,晶体管漏极位于偶极子阴极侧。这使得能够以增加偶极子D1的内阻为代价,降低或更精细地调整偶极子D1的反向导通阈值,并由此调整电路300、300-1、300-2和300-3的反向导通阈值。电路300、300-1、300-2和300-3的偶极子D1以及电路300-2的可能偶极子D3均通过二极管或组装成二极管的MOS晶体管来实现。

为了保护设备1免受过电压的影响,而不是提供电路300、300-1、300-2和300-3,它可以设计成在焊盘101和102中的每一个与处于地电位的节点210之间放置过电压保护。然而,提供这种保护将导致具有比设备3、3-1、3-2和3-3更大表面积的设备。此外,这种保护会在每个焊盘101和102上引入杂散电容和电阻,在没有过电压的情况下,这会干扰整流桥的操作。

根据其中设备3、3-1、3-2或3-3包括连接在其焊盘101和102之间的逆向调制MOS晶体管的实施例,可以将逆向调制MOS晶体管提供给分别与逆向调制晶体管相关联的两个电路300、300-1、300-2或300-3,以在焊盘101和102中的一个或另一个上发生过电压时导通逆向调制晶体管。然后,两个电路300、300-1、300-2或300-3中的第一个电路的端子301连接到焊盘102,其可能的端子303连接到焊盘101,其端子302连接到逆向调制晶体管的栅极并通过电阻器耦合到焊盘101。然后,两个电路中的第二个电路的端子301连接到焊盘101,其可能的端子303连接到焊盘102,其端子302连接到逆向调制晶体管的栅极并通过另一电阻器耦合到焊盘102。

尽管本文中没有要求保护这一点,但是如上,两个导通电路可以与逆向调制晶体管相关联,而不需要晶体管208和209各自与导通电路相关联。

根据未示出的实施例,相同设备3、3-1、3-2或3-3的导通电路可以彼此不同,包括当这些电路与逆向调制晶体管相关联时。例如,与晶体管208相关联的桥3的电路300可以用电路300-1、300-2或300-3代替。

根据一实施例,整流桥4、4-1、4-2或4-3和设备3、3-1、3-2或3-3的焊盘101和102分别属于同一集成电路,导电天线绕组优选地在集成电路外部。

虽然本文中已经描述了无线通信设备3、3-1、3-2和3-3,例如NFC型(近场通信)设备或根据ISO标准14443或15693的设备,但是整流桥4、4-1、4-2和4-3可以在其它设备中实现,以保护这些其它设备的电路免受可能的过电压,例如由在两个焊盘中的一个或另一个上的静电放电引起的过电压,两个焊盘具有耦合到其上的整流桥的相应节点201和202。

此外,本领域技术人员能够将上述公开适用于晶体管208和209具有P沟道的情况,例如,通过将所有的N型和P型以及前述电压的值反相,例如,通过将每个N沟道MOS晶体管分别替换为P沟道MOS晶体管(分别为N沟道MOS晶体管),通过将每个NPN晶体管(分别PNP晶体管)替换为PNP晶体管(分别为NPN晶体管),通过将耦合到最低电位的电路的P基底替换为耦合到最高电位的N基底,等等。在这种情况下,导通电路的阈值是负的,并且在绝对值上等于图2至图6的导通电路的阈值。然后,如果该电路的端子301与另一导通电路的端子301之间的电压具有与阈值相同的符号且绝对值大于阈值的绝对值,则该电压被称为大于该电路的阈值。换句话说,无论晶体管208和209具有N沟道还是P沟道,导通电路被配置为当该电路的端子301和另一电路的端子301之间的电压具有与电路阈值相同的符号并且具有比阈值的绝对值大的绝对值时,电耦合其端子301和302,并且当电路的端子301和另一导通电路的端子301之间的电压具有比阈值的绝对值小的绝对值时,并且当该电压具有与电路阈值相反的符号时,隔离其端子301和302。

已经描述了各种实施例和变型。本领域技术人员将理解,可以组合这些实施例的某些特征,并且本领域技术人员将容易想到其它变型。

最后,基于上文给出的功能指示,所描述的实施例和变型的实际实现在本领域技术人员的能力之内。特别地,本领域技术人员能够根据目标应用,即根据在正常操作(没有过电压)中能够在节点201和202之间存在的最大电压和/或能够在节点201和202之间出现的过电压的最大幅度,选择电阻值、可能的频率补偿电容的值、偶极子D2的正向导通阈值、可能的偶极子D3的正向导通阈值和/或偶极子D1的反向导通阈值。例如,电阻R1和R2的值应当足够低,以避免通过引入R*C型传播延迟(C是晶体管208和209的栅极的电容)而在正常操作中干扰桥,例如小于10kΩ,并且应当足够高,以使得导通电路能够增加晶体管208和209的栅极上的电压,例如大于100Ω,电阻R1和R2例如各自具有大约1kΩ的值,例如等于1kΩ。

这样的变更、修改和改进旨在成为本公开的一部分,并且旨在在本发明的精神和范围内。因此,上述描述仅是示例性的,而不是限制性的。本发明仅由所附权利要求及其等同物中所定义的限制。

- 包括至少一个过电压保护器和与过电压保护器串联连接的热触发的开关装置的过电压保护装置

- 在与供电网相连的系统中过电压保护方法,过电压保护设备和带有这种过电压保护设备的装置