隔离型半导体器件

文献发布时间:2023-06-19 13:46:35

技术领域

本发明涉及半导体技术领域,尤其是涉及一种隔离型半导体器件。

背景技术

隔离型半导体器件主要包括数字信号隔离器或隔离式栅极驱动器。隔离型半导体器件包括内部预埋有发射线圈的芯片,以及叠置式设在芯片上且内部预埋有接收线圈的隔离层。申请人的科研人员经过大量研究发现,这种隔离型半导体器的耦合系数过高,导致其电隔离性偏弱,难以抑制高频通讯信号所带来的干扰,容易致使器件失效。

发明内容

为了解决上述全部或部分问题,本发明提供一种隔离型半导体器件,其具有更好的的电隔离效果和更合理的耦合系数,保证该隔离型半导体器件能更好地抵抗高频通讯信号的干扰,降低了器件失效的风险。

本发明提供了一种隔离型半导体器件,其包括层叠设置的上芯片、隔离层及下芯片,其中所述上芯片包括内置的第一线圈,所述下芯片包括内置的第二线圈,所述隔离层隔离所述上芯片与下芯片;所述第一线圈和第二线圈中的一个为发射线圈,而另一个为接收线圈;所述第一线圈与第二线圈的耦合系数大于等于0.15,且二者之间的电隔离性不小于5kV,所述第一线圈与第二线圈之间的间距为150um~200um,所述第一线圈与第二线圈的线圈直径为350um~750um。

进一步地,所述上芯片厚度为100um~150um,下芯片的厚度为100um~200um,所述隔离层的厚度为10um~100um,优选为20um~50um。

进一步地,所述第一线圈的线圈直径D为530um~600um,匝数为16-24;所述第二线圈的线圈直径D为530um~600um,匝数为16-24。

进一步地,所述上芯片具有平坦化的研磨背面,贴平于所述隔离层。

进一步地,所述上芯片包括嵌设在其正面内的第一端子,所述下芯片包括嵌设在其正面内的第二端子,所述上芯片和隔离层在长度或宽度方向上的尺寸均短于所述下芯片在长度或宽度方向上的尺寸,使得所述第二端子不被所述上芯片和隔离层所覆盖。

进一步地,所述隔离层在长度或宽度方向上的尺寸大于所述上芯片在长度或宽度方向上的尺寸,所述隔离层在长度和宽度方向上的尺寸小于所述下芯片在长度和宽度方向上的尺寸。

进一步地,所述上芯片还包括与所述第一线圈和第一端子相连的发送电路,所述下芯片还包括与所述第二线圈相连的接收电路,以及连接所述接收电路和第二端子的驱动电路。

进一步地,所述隔离层为单层结构或多层结构,其中所述单层结构为芯片黏膜,所述多层结构包括中间隔层、用以将所述中间隔层与所述上芯片相连的第一粘连层及用以将所述中间隔层与所述下芯片相连的第二粘连层,其中所述中间隔层为由苯并环丁烯、聚酰亚胺或二氧化硅形成,所述第一粘连层和第二粘连层为芯片黏膜。

进一步地,所述第一线圈和第二线圈皆为圆形、四边形、六边形或八边形的单环线圈;或者,所述第一线圈和第二线圈皆为8字型双环线圈。

进一步地,所述隔离型半导体器件为数字信号隔离器或隔离式栅极驱动器。

如背景技术所描述一样,现有技术为单芯片结构。本发明的隔离型半导体器件采用的是双芯片结构,即将两个线圈分别内置于上下两个芯片中,并在两个芯片之间增加隔离层,这种方式相比于单芯片结构可以有效提高第一线圈和第二线圈的相对距离,且充分利用隔离层的电隔离能力,有效提高隔离型半导体器件的电隔离效果。

同时,本发明实施例隔离型半导体器件采用双芯片结构,相比于单芯片外部连接耦合线圈结构而言,可以简化制程复杂和降低生产成本。

此外,本发明的隔离型半导体器件具有更好的的电隔离效果和更合理的耦合系数,保证该隔离型半导体器件能更好地抵抗高频通讯信号的干扰,降低了器件失效的风险。

附图说明

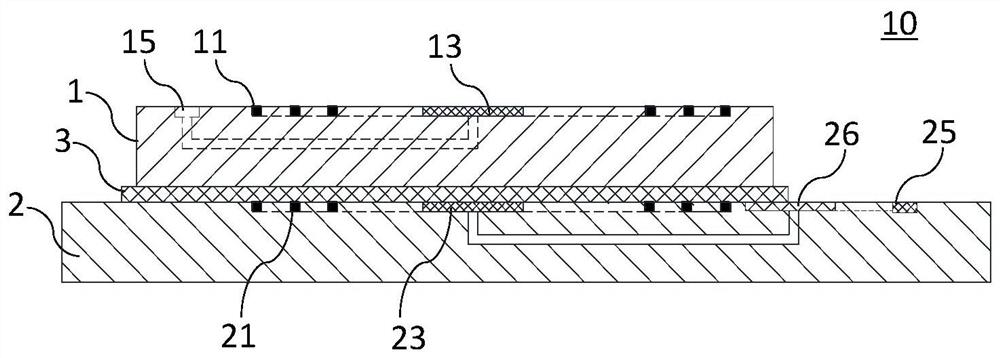

图1为本发明实施例的隔离型半导体器件的主视图。

图2为本发明实施例的隔离型半导体器件的剖视图。

图3为本发明实施例的隔离型半导体器件的上芯片。

图4为本发明实施例的隔离型半导体器件的下芯片。

图5是耦合线圈的耦合系数在不同线圈直径下的变化情况。

图6是耦合线圈的自感在不同线圈直径下的变化情况。

图7是耦合线圈的感抗在不同线圈直径下的变化情况。

图8是耦合线圈的谐振频率在不同线圈直径下的变化情况。

附图标记说明:1、上芯片;2、下芯片;3、隔离层;10、隔离型半导体器件;11、第一线圈;13、发送电路;15、第一端子;21、第二线圈;23、接收电路;25、第二端子;26、驱动电路。

具体实施方式

以下结合附图1-8对本发明作进一步详细说明。

本发明的实施例提供了一种隔离型半导体器件10。隔离型半导体器件10可选为需要使用耦合线圈来实施信号隔离的半导体器件,例如数字信号隔离器或隔离式栅极驱动器等。

如图1和图2所示,隔离型半导体器件10包括层叠设置的上芯片1、隔离层3及下芯片2,其中隔离层3能对上芯片1与下芯片2实施隔离。上芯片1包括内置的第一线圈11,下芯片2包括内置的第二线圈21。第一线圈11和第二线圈21中的一个为发射线圈,而另一个为接收线圈。

如背景技术所描述一样,现有技术为单芯片结构。本发明实施例隔离型半导体器件10采用的是双芯片结构,即将两个线圈分别内置于上下两个芯片中,并在两个芯片之间增加隔离层3,这种方式相比于单芯片结构可以有效提高第一线圈11和第二线圈21的相对距离,且充分利用隔离层3的电隔离能力,有效提高隔离型半导体器件10的电隔离效果。此外,本发明实施例隔离型半导体器件10采用双芯片结构,相比于单芯片外部连接耦合线圈结构而言,可以简化制程复杂和降低生产成本。

为了适用于一般电子产品、尤其是高频通讯的需求,隔离型半导体器件10的传输信号的增益应控制为20dB±5dB。为了达到这样增益效果,需要保证隔离型半导体器件10具有更合理的耦合系数和更好的的电隔离效果,即第二线圈21与第一线圈11的耦合系数大于等于0.15,且二者之间的电隔离性不小于5kV。

如图5所示,当第一线圈11与第二线圈21之间的间距L为150um时,为了达到0.15的耦合系数,第一线圈11与第二线圈21的线圈直径D可选为300um~750um。当第一线圈11与第二线圈21之间的间距L为200um时,为了达到0.15的耦合系数,第一线圈11与第二线圈21的线圈直径D可选为350um~750um。因此,当第一线圈11与第二线圈21之间的间距L为150um~200um,第一线圈11与第二线圈21的线圈直径D应选为350um~750um,也只有这样才能保证第二线圈21与第一线圈11的耦合系数大于等于0.15,且二者之间的电隔离性不小于5kV。

通过大量研究发现,为了保证第二线圈21与第一线圈11的耦合系数大于等于0.15,且二者之间的电隔离性不小于5kV,并保证上芯片1和下芯片2也能辅助隔离层3来实施隔离,那么隔离层3的厚度可选为10um~100um,上芯片1和下芯片2的各自厚度可选为100um~200um。在此基础之上,为了保证上芯片1和下芯片2能更好地辅助隔离层3来实施隔离,并降低隔离层3的厚度以保证堆叠芯片的结构稳定性和性能稳定性,隔离层3的厚度选为20um~50um,上芯片1厚度选为100um~150um,下芯片2的厚度选为100um~200um。

以通讯领域为例,在外径一定的情况下调整耦合线圈(即第一线圈11和第二线圈21)的匝数可以降低电感,提高谐振频率,匝数越小电感值越小,谐振频率越高,但是需要消耗更多的电流才能达到相同的发射信号电压。

当本实施例的隔离型半导体器件10应用在通讯领域中时,由于受到传输信号带宽的要求,载波频率越高越好。载波频率至少为300MHz,最大可以高达1GHz。载波频率受到线圈谐振频率的限制,线圈外径越大,匝数越多,说明线圈的自感就越大,谐振频率就越低,因此线圈直径D直接影响线圈的谐振频率。基于以上的分析可知线圈直径D最大可为600um,才能够实现谐振频率大于等于300MHz载波的目标,详见图7和图8。

由此可知,当本实施例的隔离型半导体器件10应用在高频通讯技术中时,为了达到高频通讯隔离的严苛要求,第一线圈11与第二线圈21之间的间距L应为150um~200um,上芯片1厚度应为100um~150um,下芯片2的厚度应为100um~200um,隔离层3的厚度应为20um~50um,第一线圈11的线圈直径D应为530um~600um,匝数应为16-24;第二线圈21的线圈直径D应为530um~600um,匝数应为16-24。

表1:

由表1可知,实施例1~3的隔离型半导体器件10可以有效满足高频通讯技术的需求,即第二线圈21与第一线圈11的耦合系数大于等于0.15,二者之间的电隔离性不小于5kV,电感大于等于200nH,且谐振频率大于等于300MHz。

在本实施例中,上芯片1具有平坦化的研磨背面,并贴平于隔离层3。通知这种方式,可以有利于保持第一线圈11与第二线圈21之间的平行度,不会受到上芯片1的贴装影响。

在本实施例中,上芯片1包括嵌设在其正面内的第一端子15,下芯片2包括嵌设在其正面内的第二端子25,上芯片1和隔离层3在长度或宽度方向上的尺寸均短于下芯片2在长度或宽度方向上的尺寸,使得第二端子25不被上芯片1和隔离层3所覆盖,详见图2。本实施例所采用的结构可以将第一端子15和第二端子25分别暴露在上芯片1和下芯片2外,这可以方便二者通过键合线直接连接隔离型半导体器件10的对应引脚。

在本实施例中,隔离层3在长度或宽度方向上的尺寸大于上芯片1在长度或宽度方向上的尺寸,隔离层3在长度和宽度方向上的尺寸小于下芯片2在长度和宽度方向上的尺寸。这样可以有效保证隔离层3能够充分隔离上芯片1和下芯片2。

在本实施例中,上芯片1还包括与第一线圈11和第一端子15相连的发送电路13,详见图3。下芯片2还包括与第二线圈21相连的接收电路23,以及连接接收电路23和第二端子25的驱动电路26,详见图4。在其他实施例中,也可将接收电路23和驱动电路26设在上芯片1中,而将发送电路13设在下芯片中。其中,发送电路13、接收电路23和驱动电路26皆为本领域的已知结构,在此不再赘述。

在本实施例中,隔离层3可选为单层结构或多层结构。当隔离层3选为单层结构,其最好选为粘合材料制作,比如芯片黏膜(DAF,Die Attach Film)。通过这种方式,隔离层3可以直接将上芯片1与下芯片2连接,有助于简化整个器件的制作工艺。当隔离层3选为多层结构时,其包括中间隔层、用以将中间隔层与上芯片1相连的第一粘连层及用以将中间隔层与下芯片2相连的第二粘连层。其中,中间隔层优选为由苯并环丁烯、聚酰亚胺或二氧化硅形成,而第一粘连层和第二粘连层皆选为芯片黏膜。通过这种方式,隔离层3不但可以直接将上芯片1与下芯片2连接并简化整个器件的制作工艺,而可以保证了自身具有更好的电隔离性能。

在本实施例中,第一线圈11和第二线圈21皆可为圆形、四边形、六边形或八边形的单环线圈。在一个未示出的实施例中,第一线圈11和第二线圈21皆为8字型双环线圈。需要说明的是,当第一线圈11和第二线圈21为四边形、六边形或八边形的非圆形单环线圈时,其线圈直径D可近似理解为非圆形单环线圈的内接圆直径。当第一线圈11和第二线圈21为8字型双环线圈时,其线圈直径D可近似理解为8字型双环线圈中一个环的直径。

综上所述,本发明实施例的隔离型半导体器件10具有更好的的电隔离效果和更合理的耦合系数,保证该隔离型半导体器件10能更好地抵抗高频通讯信号的干扰,降低了器件失效的风险。

由于耦合系数在不同测试方法中会出现不同的结果,所以耦合系数在本申请中的理解是由以下方法测得:在隔离型半导体器件10的输入引脚上输入100MHz、1V的正弦波电压,用数字示波器测量隔离型半导体器件10的输出引脚的电压,然后将输出电压除以输入电压的得数作为耦合系数。

以上均为本发明的较佳实施例,并非依此限制本发明的保护范围,故:凡依本发明的结构、形状、原理所做的等效变化,均应涵盖于本发明的保护范围之内。