一种芯片封装装置

文献发布时间:2023-06-19 10:11:51

技术领域

本发明涉及电子领域,尤其涉及一种芯片封装装置。

背景技术

处理器的封装体可能具有使用被称为微BGA的球闸阵列(Ball Grid Array),以0.65mm的间距被拉出的100个以上(有时为100个)的端子。即使对于存储器,例如NAND型快闪记忆体(Flush Memory),也存在48个等较多的端子数。这样,主机板的配线为了在这些球闸阵列之间进行通过,除了需要较细之外,还需要以避开与之不连接的其他电极的贯穿孔的方式进行配线,因此只能被弯曲成非常复杂的形状。如图6所示为现有技术中的芯片的典型封装结构,基板1’的下方为焊球5’,上方为裸片2’。裸片2’通过键合线4’连接到基板。裸片2’和键合线4’通过树脂3’封装于树脂3’中。然而在实现信号的高速化时,弯曲的键合线4’的形状可能会导致寄生电容和寄生电感的增加,进而产生信号的传播迟延,或引起发生多余的电磁干扰现象(称EMI,Electromagnetic Interference)。为了解决这个问题,现有技术的做法是在芯片外套设金属屏蔽壳体,然而该壳体占用空间巨大,难以适应便携式电子设备的小型化要求。

除此之外,片上天线,即在芯片上整合天线对于无线装置具有重要性;例如,使用蜂窝和/或无线网路(例如4G与5G蜂窝与WiFi网路)的装置。或者可在毫米波频率下工作的天线在涉及感测、雷达、超高速通信、及医学成像的应用中具有重要性。下一代无线通信装置将使用毫米波频率来因应对于数据不断增加的需求,如何在减少EMI的情况下提高片上天线的性能是本领域亟需解决的技术问题。

发明内容

为了解决现有技术中的上述问题,本申请实施例提供的技术方案如下:

一种芯片封装装置,包括:

基板1,包括上表面和下表面;所述基板1的上表面开设有凹槽11,裸片2设置于所述凹槽11内;所述裸片2的上表面与所述基板1的上表面平齐;

金属导体6,为一端开口的罩体,设置于所述凹槽11的上方,覆盖所述裸片2与所述基板1之间的键合线4;金属导体6密封于树脂3内;

所述裸片2与所述基板1的每个焊盘之间的 所述键合线4为至少两根;

辐射贴片7,通过穿过通孔61的馈电线72馈电,并且通过接地线73连接到所述金属导体6;

寄生元件71,设置于辐射贴片7的四周,被配置为与所述辐射贴片7保持预定耦合距离。

优选地,所述基板1的下表面设置有焊球5。

优选地,金属导体6具有多个由其一角或侧边延伸而出的支撑脚结合至基板1。

优选地,裸片2通过胶粘层21固定于凹槽11的内壁底部。

优选地,在金属导体6的表面开设有至少一个通孔61;通孔61具有能够使得树脂注入的直径。

优选地,所述寄生元件71为环状结构,设置于辐射贴片7的四周,被配置为与所述辐射贴片7保持预定耦合距离。

优选地,寄生元件71为沿着所述辐射贴片7的周长方向周期性排列的贴片。

与现有技术相比,本发明具有如下有益效果:本发明的芯片封装装置在整合了高性能天线的同时能够在减少高速数字电路EMI,缩减芯片封装装置的体积,并且减少寄生参数的产生,提高信号完整性。即使由于加工工艺或者外接环境因素造成个别键合线虚焊也不会导致电气连接断开,提高了芯片的环境适应性。

附图说明

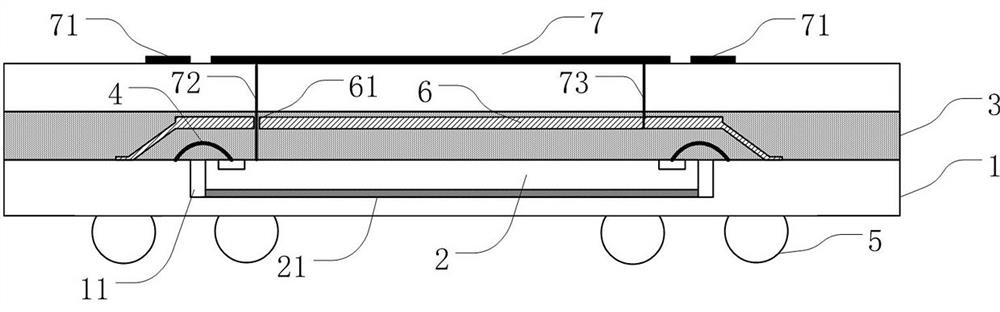

图1为本发明实施例一的芯片封装装置结构示意图;

图2为本发明实施例一的芯片封装装置的键合线结构示意图;

图3为本发明实施例一的金属导体的俯视图;

图4为本发明的一种寄生元件的结构示意图;

图5为本发明的另一种寄生元件的结构示意图;

图6为现有技术的芯片封装装置的结构示意图。

具体实施方式

下面结合附图和具体实施方式,对本发明的技术方案做详细描述。

在下面的描述中阐述了很多具体细节以便于充分理解本申请。但是本申请能够以很多不同于在此描述的其它方式来实施,本领域技术人员可以在不违背本申请内涵的情况下做类似推广,因此本申请不受下面公开的具体实施的限制。

如图1-3所示为本发明实施例一的芯片封装装置结构示意图,包括:

基板1,包括上表面和下表面;所述基板1的上表面开设有凹槽11,裸片2设置于所述凹槽11内;所述裸片2的上表面与所述基板1的上表面平齐。

金属导体6,为一端开口的罩体,设置于所述凹槽11的上方,覆盖所述裸片2与所述基板1之间的键合线4;金属导体6密封于树脂3内;在金属导体6的表面开设有至少一个通孔61;通孔61具有能够使得树脂注入的直径;

所述裸片2与所述基板1的每个焊盘之间的所述键合线4为至少两根;

辐射贴片7,通过穿过通孔61的馈电线72馈电,并且通过接地线73连接到所述金属导体6;

寄生元件71,设置于辐射贴片7的四周,被配置为与所述辐射贴片7保持预定耦合距离。

该基板1为裸片载体,例如:印刷电路板(printed circuit board,PCB)、软性电路板(flexible printed circuit,FPC)等。在基板1上开设凹槽11,把裸片2放置于该槽内,并且将裸片2的上表面配置为与所述基板1的上表面平齐相对于图6中的现有技术能够显著缩短键合线4的长度,减少键合线4的寄生电感和寄生电容的产生,提高信号完整性。优选地,凹槽11的大小为刚好能够容纳裸片2的体积,尽可能地减少键合线4的跨接距离。同时,由于裸片2放置于基板1的凹槽内,相比于现有技术布置于基板1上表面的技术方案,在层叠方向上显著降低了封装装置的高度。

所述基板1的下表面设置有焊球5,用于使得本发明的芯片封装装置能够对外电性连接。所述的焊球5的数量能够根据设计需要调整,本发明并不以此为限。

金属导体6为铜、铝或其它高导电率材料。金属导体6可具有多个由其一角或侧边延伸而出的支撑脚结合至基板1。优选地,金属导体6可利用表面贴装技术(surface mounttechnology,SMT)将支撑脚固定在基板1表面1,并支撑该金属导体6于裸片2正上方。金属导体6嵌入树脂3内,以罩的形式覆盖裸片2和键合线4,能够提供较强的机械强度与支撑性。

优选地,裸片2通过胶粘层21固定于凹槽11的内壁底部。典型地,所述胶粘层21为银胶,其主要成份是环氧树脂、银粉和少量添加剂。环氧树脂和添加剂主要起粘结作用,而银粉主要起导电导热作用。

图2为本发明实施例一的芯片封装装置的键合线结构示意图。如图2所示,所述裸片2与所述基板1的每个焊盘之间的所述键合线4为至少两根。由此,每两个焊盘之间的多根键合线4可以形成一并联电路,从而减少单根键合线所产生的寄生电感。并且,至少两根键合线4也提高了焊盘之间电气连接的稳定性。即使由于加工工艺或者外接环境因素造成个别键合线虚焊也不会导致电气连接断开,提高了芯片的环境适应性。此外,金属导体6与键合线4之间也能够产生电容性耦合。由于降低了裸片2的高度,键合线4的长度和高度都得以降低,键合线4不易触及金属导体6而导致短路,同时键合线4与金属导体6的间距较为平均。因此,可以通过调整金属导体6与键合线4之间的距离来调节二者之间产生的寄生电容C

图3为本发明实施例一的金属导体的俯视图。如图3所示,在金属导体6的表面开设有通孔61。通孔61具有能够使得树脂注入的直径。当注入的树脂3固化之后,嵌入通孔61内的树脂形成固定柱,从而能够通过这些通孔61紧密地固定金属导体6,以避免金属导体6剥离或脱落。

通孔61的数量至少为一个,本领域技术人员能够知晓,通孔61的数量应当是合适的,可以根据实际情况调整数量和排布方式。然而通孔61也不宜过于密集设置,否则将导致信号泄露,影响EMI的屏蔽效果。

辐射贴片7例如为工作于毫米波的辐射天线单元。本领域技术人员可以知晓辐射贴片7还可以工作于其它无线通信频段,本发明并不以此为限。辐射贴片7通过穿过通孔61的馈电线72馈电,并且通过接地线73连接到所述金属导体6。如图4所示,根据本发明的一个方面,寄生元件71为环状结构,设置于辐射贴片7的四周,被配置为与所述辐射贴片7保持预定耦合距离。调整预定耦合距离能够调整耦合,可降低寄生元件71与辐射贴片7之间的镜像电流,从而提高天线增益与效率。如图5所示,根据本发明的另一个方面,寄生元件71为沿着所述辐射贴片7的周长方向周期性排列的贴片。调整周期性排列的贴片的几何尺寸和间距使其形成为高阻抗表面,从而能够降低辐射贴片7周围的表面电流,提高天线增益与效率。

辐射贴片7,通过穿过通孔61的馈电线72馈电,并且通过接地线73连接到所述金属导体6。由此,金属导体6能够作为辐射贴片7的反射表面提高天线的方向性。同时,调整接地线73的位置能够对辐射贴片7调谐,从而提高辐射贴片7的辐射性能。

表一:不同实施例的天线性能对比

由上表可知,在-10dB阻抗带宽带宽基本不变的情况下,加入寄生元件,使得反射损耗更低,实现高增益辐射。

本申请虽然以较佳实施例公开如上,但其并不是用来限定本申请,任何本领域技术人员在不脱离本申请的精神和范围内,都可以做出可能的变动和修改,因此本申请的保护范围应当以本申请权利要求所界定的范围为准。

- 供膜及贴膜装置、具有该装置的半导体芯片封装件制造装置以及半导体芯片封装件制造方法

- 一种芯片封装系统及应用于芯片封装工艺的检测装置