一种晶圆系统级三维扇出型封装结构及其制作方法

文献发布时间:2023-06-19 09:44:49

技术领域

本发明属于半导体封装领域,涉及一种晶圆系统级三维扇出型封装结构及其制作方法。

背景技术

随着5G通讯和人工智能(AI)时代的到来,应用于此类相关领域的芯片所要传输和高速交互处理的数据量非常巨大,该类芯片通常具有数量巨大的pad引脚(几百甚至上千个)、超精细的管脚大小和间距(几个微米甚至更小)。另一方面,移动互联网以及物联网方面的需求越来越强劲,电子终端产品的小型化和多功能化成为产业发展的大趋势。如何将多个不同种类的高密度芯片集成封装在一起构成一个功能强大且体积功耗又比较小的系统或者子系统,成为半导体芯片先进封装领域的一大挑战。

目前针对此类高密度芯片的多芯片集成封装,业界通常都是采用硅穿孔(TSV)、硅转接板(Si interposer)等方式进行,从而把芯片的超精细引脚进行引出和有效互联从而形成一个功能模块或者系统,但该技术的成本比较高,从而大大局限了它的应用范围。

随着人们对更高功能、更好的性能和更高的能源效率、更低的制造成本和更小的尺寸的不断需求,扇出晶圆级封装(FOWLP)技术已经成为满足电子设备对移动和网络应用需求的最有前途的技术之一。扇出型封装技术采用重构晶圆和重新布线RDL的方式为实现多芯片的集成封装提供了很好的平台,但是现有的扇出型封装技术中由于布线精度有限从而使得封装体的面积较大厚度较高,而且存在工序繁多、可靠性不高等诸多问题。

为适应微电子封装技术的多功能、小型化、便携式、高速度、低功耗和高可靠性发展趋势,系统级封装SIP(System In Package)技术作为新兴异质集成技术,成为越来越多芯片的封装形式,系统级封装是将多种功能芯片和元器件集成在一个封装内,从而实现一个完整的功能。系统级封装是一种新型封装技术,具有开发周期短,功能更多,功耗更低,性能更优良、成本价格更低,体积更小,质量轻等优点。

然而,随着对封装组件及功能越来越高的需求,现有的系统级封装会占用越来越大的面积及厚度,不利于集成度的提高。

发明内容

鉴于以上所述现有技术的缺点,本发明的目的在于提供一种晶圆系统级三维扇出型封装结构及其制作方法,用于解决现有技术中系统级封装体积难以缩小的问题。

为实现上述目的及其他相关目的,本发明提供一种晶圆系统级三维扇出型封装结构的制作方法,包括以下步骤:

形成重新布线层,所述重新布线层包括相对设置的第一面与第二面,且所述重新布线层包括在垂直方向上堆叠的至少一层介质层及至少一层金属布线层;

形成导电连接柱于所述重新布线层的第二面,所述导电连接柱与所述重新布线层电性相连;

提供贴片元件,将所述贴片元件接合于所述重新布线层的第二面上,所述贴片元件与所述重新布线层电性相连;

形成塑封层于所述重新布线层的第二面上,所述塑封层覆盖所述导电连接柱及所述贴片元件;

减薄所述塑封层以显露所述导电连接柱;

形成多个焊料凸点于所述塑封层背离所述重新布线层的一侧,至少一所述焊料凸点与所述导电连接柱电性相连;

切割所述重新布线层及所述塑封层,得到多个第一封装体;

提供第二封装体,将所述第二封装体接合于所述第一封装体的所述重新布线层的第一面,所述第二封装体与所述重新布线层电性相连。

可选地,还包括以下步骤:提供一载体,形成释放层于所述载体上,其中,所述重新布线层形成于释放层上,所述重新布线层的第一面与所述释放层连接。

可选地,在切割之前,先去除所述载体及所述释放层以暴露出所述重新布线层的第一面。

可选地,还包括以下步骤:形成通孔,所述通孔自所述重新布线层的第一面开口,并往所述重新布线层的第二面方向延伸,以显露所述金属布线层。

可选地,采用激光打孔法形成所述通孔。

可选地,所述第二封装体的一面设有导电凸块,所述导电凸块伸入所述通孔中以与所述金属布线层电性相连。

可选地,还包括形成绝缘层于所述塑封层背离所述重新布线层的一面,并形成凸点下金属层于所述绝缘层表面的步骤,所述焊料凸点形成于所述凸点下金属层背离所述塑封层的一面。

可选地,所述贴片元件包括被动元件。

本发明还提供一种晶圆系统级三维扇出型封装结构,包括:

重新布线层,包括相对设置的第一面与第二面,所述重新布线层包括在垂直方向上堆叠的至少一层介质层及至少一层金属布线层;

贴片元件,接合于所述重新布线层的第二面,并与所述重新布线层电性相连;

塑封层,位于所述重新布线层的第二面,并覆盖所述贴片元件;

导电连接柱,在垂直方向上贯穿所述塑封层,并与所述重新布线层电性相连;

多个焊料凸点,分布于所述塑封层背离所述重新布线层的一侧,至少一所述焊料凸点与所述导电连接柱电性相连;

封装体,接合于所述重新布线层的第一面,所述封装体与所述重新布线层电性相连。

可选地,所述重新布线层中设有通孔,所述通孔自所述重新布线层的第一面开口,并往所述重新布线层的第二面方向延伸,以显露所述金属布线层,所述封装体的一面设有导电凸块,所述导电凸块伸入所述通孔中以与所述金属布线层电性相连。

可选地,还包括绝缘层及凸点下金属层,所述绝缘层位于所述塑封层背离所述重新布线层的一面,所述凸点下金属层位于所述焊料凸点面向所述塑封层的一面,并与所述绝缘层接触。

可选地,所述贴片元件包括被动元件。

如上所述,本发明的晶圆系统级三维扇出型封装结构及其制作方法先采用晶圆级封装在重新布线层的一面将贴片元件塑封,并切割得到多个第一封装体,再将第二封装体接合于重新布线层的另一面,得到双面塑封系统级封装结构。本发明能够增加扇出型封装结构的功能整合性,提升单一芯片功能及效率,并优化体积。

附图说明

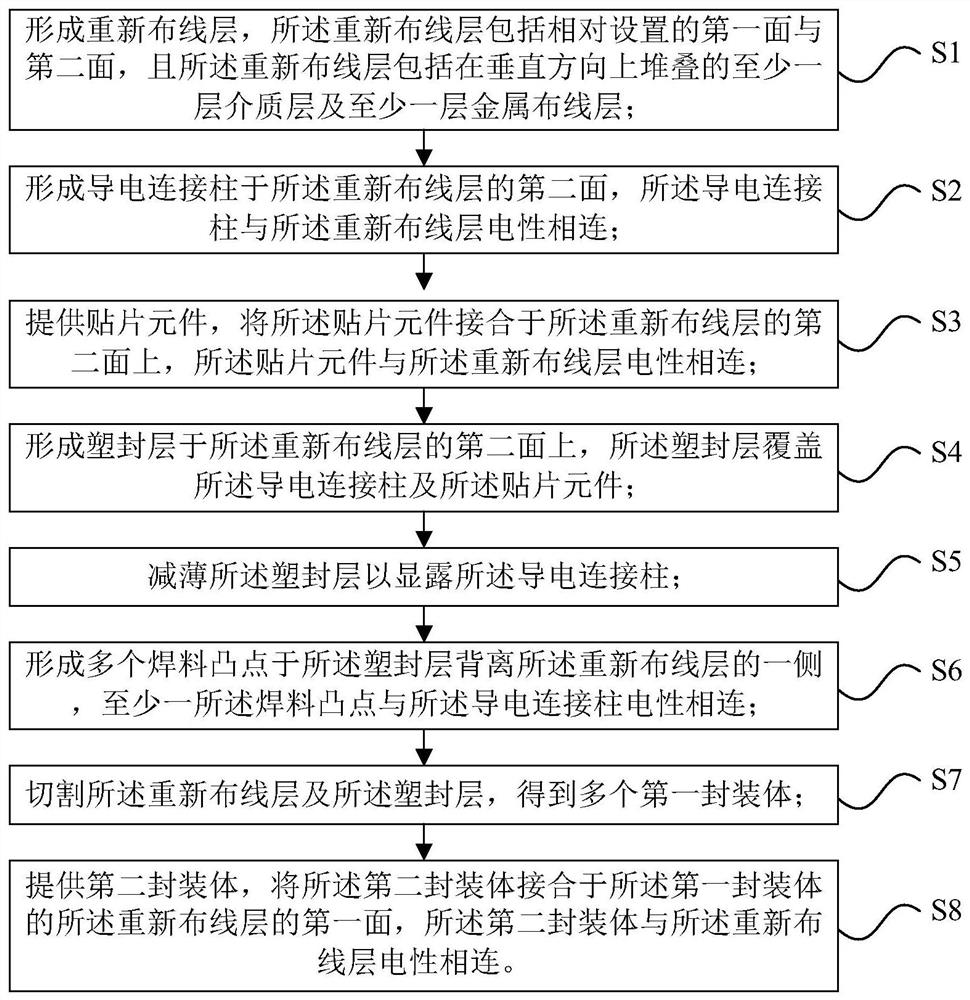

图1显示为本发明的晶圆系统级三维扇出型封装结构的制作方法的工艺流程图。

图2显示为本发明的晶圆系统级三维扇出型封装结构的制作方法提供一载体的示意图。

图3显示为本发明的晶圆系统级三维扇出型封装结构的制作方法形成释放层于所述载体上的示意图。

图4显示为本发明的晶圆系统级三维扇出型封装结构的制作方法形成重新布线层于所述释放层上的示意图。

图5显示为本发明的晶圆系统级三维扇出型封装结构的制作方法形成导电连接柱于所述重新布线层的第二面的示意图。

图6显示为本发明的晶圆系统级三维扇出型封装结构的制作方法提供贴片元件,将所述贴片元件接合于所述重新布线层的第二面上的示意图。

图7显示为本发明的晶圆系统级三维扇出型封装结构的制作方法形成塑封层于所述重新布线层的第二面上的示意图。

图8显示为本发明的晶圆系统级三维扇出型封装结构的制作方法减薄所述塑封层以显露所述导电连接柱的示意图。

图9显示为本发明的晶圆系统级三维扇出型封装结构的制作方法形成多个焊料凸点于所述塑封层背离所述重新布线层的一侧的示意图。

图10显示为本发明的晶圆系统级三维扇出型封装结构的制作方法进一步去除所述载体及所述释放层以暴露出所述重新布线层的第一面的示意图。

图11显示为本发明的晶圆系统级三维扇出型封装结构的制作方法在所述重新布线层中的介质层中形成通孔的示意图。

图12显示为本发明的晶圆系统级三维扇出型封装结构的制作方法切割所述重新布线层及所述塑封层,得到多个第一封装体。

图13显示为本发明的晶圆系统级三维扇出型封装结构的制作方法提供第二封装体,将所述第二封装体接合于所述第一封装体的所述重新布线层的第一面的示意图。

元件标号说明

S1~S8 步骤

1 载体

2 释放层

3 重新布线层

301 介质层

302 金属布线层

4 导电连接柱

5 贴片元件

6 塑封层

7 焊料凸点

8 绝缘层

9 凸点下金属层

10 蓝膜

11 金属框架

12 第二封装体

13 导电凸块

14 通孔

具体实施方式

以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

请参阅图1至图13。需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,遂图式中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

本实施例提供一种晶圆系统级三维扇出型封装结构的制作方法,请参阅图1,显示为该方法的工艺流程图,包括以下步骤:

S1:形成重新布线层,所述重新布线层包括相对设置的第一面与第二面,且所述重新布线层包括在垂直方向上堆叠的至少一层介质层及至少一层金属布线层;

S2:形成导电连接柱于所述重新布线层的第二面,所述导电连接柱与所述重新布线层电性相连;

S3:提供贴片元件,将所述贴片元件接合于所述重新布线层的第二面上,所述贴片元件与所述重新布线层电性相连;

S4:形成塑封层于所述重新布线层的第二面上,所述塑封层覆盖所述导电连接柱及所述贴片元件;

S5:减薄所述塑封层以显露所述导电连接柱;

S6:形成多个焊料凸点于所述塑封层背离所述重新布线层的一侧,至少一所述焊料凸点与所述导电连接柱电性相连;

S7:切割所述重新布线层及所述塑封层,得到多个第一封装体;

S8:提供第二封装体,将所述第二封装体接合于所述第一封装体的所述重新布线层的第一面,所述第二封装体与所述重新布线层电性相连。

首先请参阅图2至图4,执行步骤S1:形成重新布线层,所述重新布线层包括相对设置的第一面与第二面,且所述重新布线层包括在垂直方向上堆叠的至少一层介质层及至少一层金属布线层。

具体的,如图2所示,先提供一载体1。所述载体1用于防止封装过程中层结构开裂、翘曲、断裂等,所述载体1的形状可以是晶圆状、面板状和其他任何需要的形状,其包括但不限于玻璃、金属、半导体、聚合物、陶瓷中的任意一种。本实施例中,所述载体1的材质选用玻璃,其成本较低,容易在其表面形成释放层,且能降低后续的剥离工艺的难度。

如图3所示,形成释放层2于所述载体1上。所述释放层2可由胶带或聚合物等材料构成,可以采用紫外光固化或热固化方式。

如图4所示,形成重新布线层3形成于所述释放层2上,所述重新布线层3的第一面与所述释放层2连接。

作为示例,所述重新布线层3包括在垂直方向上堆叠的至少一层介质层301及至少一层金属布线层302。

作为示例,制作所述重新布线层3包括以下步骤:

(1)采用化学气相沉积工艺、物理气相沉积或其它合适的工艺于所述释放层表面形成第一介质层,所述第一介质层的材质包括但不限于环氧树脂、硅胶、PI、PBO、BCB、氧化硅、磷硅玻璃,含氟玻璃中的一种或两种以上组合。本实施例中,所述第一介质层的材质选用为PI(聚酰亚胺),以进一步降低工艺难度以及工艺成本。

(2)采用溅射、电镀、化学镀或其它合适的工艺于所述第一介质层表面形成第一金属层,并对所述第一金属层进行刻蚀形成图形化的第一金属布线层。所述第一金属布线层的材料包括铜、铝、镍、金、银、钛中的一种或两种以上组合。

(3)采用化学气相沉积工艺、物理气相沉积或其它合适的工艺于所述图形化的所述第一金属布线层表面形成第二介质层,并对所述第二介质层进行刻蚀形成具有图形化通孔的第二介质层。所述第二介质层的材料包括但不限于环氧树脂、硅胶、PI、PBO、BCB、氧化硅、磷硅玻璃,含氟玻璃中的一种或两种以上组合。本实施例中,所述第二介质层的材料选用为PI(聚酰亚胺),以进一步降低工艺难度以及工艺成本。

本实施例中显示为所述重新布线层3中包含两层介质层及一层金属布线层的情形,位于上层的介质层中设有显露金属布线层的通孔。在其它实施例中,也可以继续执行吸收步骤:

(4)采用溅射、电镀、化学镀或其它合适的工艺于所述图形化通孔内填充导电栓塞,然后采用采用溅射、电镀、化学镀或其它合适的工艺于所述第二介质层表面形成第二金属层,并对所述金属层进行刻蚀形成图形化的第二金属布线层。所述第二金属布线层的材质包括但不铜、铝、镍、金、银、钛中的一种或两种以上组合。

接着,可以根据需要重复进行上述步骤(3)~(4)一次或多次,以形成具有多层堆叠结构的重新布线层,以实现不同的布线功能,并且最后,位于顶层的介质层中具有显露顶层金属布线层的通孔。

再请参阅图5,执行步骤S2:采用焊线工艺、沉积工艺或其它合适的工艺形成导电连接柱4于所述重新布线层3的第二面,所述导电连接柱4与所述重新布线层3电性相连。

再请参阅图6,执行步骤S3:提供贴片元件5,将所述贴片元件5接合于所述重新布线层3的第二面上,所述贴片元件5与所述重新布线层3电性相连。

作为示例,所述贴片元件5包括被动元件,例如电阻、电感、电容等,可通过表面贴装工艺将所述贴片元件5接合于所述重新布线层3的第二面上,以实现与所述重新布线层3的电性连接。

再请参阅图7,执行步骤S4:形成塑封层6于所述重新布线层3的第二面上,所述塑封层6覆盖所述导电连接柱4及所述贴片元件5。

作为示例,形成所述塑封层6的方法包括但不限于压缩成型、传递模塑成型、液封成型、真空层压及旋涂中的任意一种,所述塑封层6的材质可以是可固化材料,如聚合物基材料、树脂基材料、聚酰胺、环氧树脂及其任何组合。

再请参阅图8,执行步骤S5:减薄所述塑封层6以显露所述导电连接柱4。

再请参阅图9,执行步骤S6:形成多个焊料凸点7于所述塑封层6背离所述重新布线层3的一侧,至少一所述焊料凸点7与所述导电连接柱4电性相连。

作为示例,先形成绝缘层8于所述塑封层6背离所述重新布线层3的一面,并形成凸点下金属层9于所述绝缘层8表面,然后再在所述凸点下金属层9背离所述塑封层6的一面形成所述焊料凸点7。所述绝缘层8的材质包括但不限于氧化硅,所述凸点下金属层9的材质包括但不限于铜、镍、锡银等,所述焊料凸点7可由金属柱、焊点组成,也可以只是锡球。

再请参阅图10,进一步去除所述载体1及所述释放层2以暴露出所述重新布线层3的第一面。

具体的,根据所述释放层2的类型采用相应的方法使得所述释放层2粘性下降,进而剥离所述载体1及所述释放层2。例如,当所述释放层2采用光热转换材料时,可采用激光照射所述光热转换层,以使所述光热转换层与所述重新布线层3及所述载体1分离。

再请参阅图11,采用激光打孔法或其它合适的方法在所述重新布线层3中的介质层中形成通孔14,所述通孔14自所述重新布线层3的第一面开口,并往所述重新布线层3的第二面方向延伸,以显露所述金属布线层。

再请参阅图12,执行步骤S7:切割所述重新布线层3及所述塑封层6,得到多个第一封装体。例如,可在前述所得结构具有所述焊料凸点7的一面覆盖一层蓝膜10,并固定在金属框架11上,然后通过刀片进行切割。

再请参阅图13,执行步骤S8:提供第二封装体12,将所述第二封装体12接合于所述第一封装体的所述重新布线层3的第一面,所述第二封装体12与所述重新布线层3电性相连。

作为示例,所述第二封装体12中可设有至少一种功能芯片,包括但不限于系统级芯片、电源管理芯片、存储芯片等。由所述第一封装体与所述第二封装体12组成的三维堆叠封装结构将各种功能芯片与贴片元件整合在一个封装结构中,可实现多种不同的系统功能需求,提高封装系统的性能。

作为示例,所述第二封装体12的一面设有导电凸块13,所述导电凸块13伸入所述通孔14中以与所述金属布线层302电性相连。

至此,制作得到一种晶圆系统级三维扇出型封装结构,如图13所示,该晶圆系统级三维扇出型封装结构包括第一封装体及第二封装体12,所述第一封装体包括重新布线层3、贴片元件5、塑封层6、导电连接柱4及多个焊料凸点7,其中,所述重新布线层3包括相对设置的第一面与第二面,并包括在垂直方向上堆叠的至少一层介质层301及至少一层金属布线层302;所述贴片元件5接合于所述重新布线层3的第二面,并与所述重新布线3层电性相连;所述塑封层6位于所述重新布线层3的第二面,并覆盖所述贴片元件5;所述导电连接柱4在垂直方向上贯穿所述塑封层6,并与所述重新布线层3电性相连,多个所述焊料凸点7分布于所述塑封层6背离所述重新布线层3的一侧,至少一所述焊料凸点7与所述导电连接柱4电性相连;所述第二封装体12接合于所述第一封装体的所述重新布线层3的第一面,并与所述重新布线层3电性相连。

作为示例,所述重新布线层3中设有通孔14,所述通孔14自所述重新布线层3的第一面开口,并往所述重新布线层3的第二面方向延伸,以显露所述金属布线层302,所述第二封装体的一面设有导电凸块13,所述导电凸块13伸入所述通孔14中以与所述金属布线层302电性相连。

作为示例,所述晶圆系统级三维扇出型封装结构还包括绝缘层8及凸点下金属层9,所述绝缘层8位于所述塑封层6背离所述重新布线层3的一面,所述凸点下金属层9位于所述焊料凸点7面向所述塑封层6的一面,并与所述绝缘层8接触。

作为示例,所述贴片元件5包括被动元件,例如电阻、电感、电容等。

综上所述,本发明的晶圆系统级三维扇出型封装结构及其制作方法先采用晶圆级封装在重新布线层的一面将贴片元件塑封,并切割得到多个第一封装体,再将第二封装体接合于重新布线层的另一面,得到双面塑封系统级封装结构。本发明能够增加扇出型封装结构的功能整合性,提升单一芯片功能及效率,并优化体积。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

- 一种晶圆系统级三维扇出型封装结构及其制作方法

- 一种晶圆系统级扇出型封装结构及其制作方法