一种半导体封装结构及其制作方法

文献发布时间:2023-06-19 10:14:56

技术领域

本发明涉及半导体技术领域,尤其是涉及一种半导体封装结构及其制作方法。

背景技术

近年来,随着大电流,高功率电源芯片的发展,再分布层(RDL)布线受到广泛的应用,但是在封装结束后,在做高加速温湿度及偏压测试(bias HAST)实验时,相邻不同电位的RDL会发生金属扩散的问题(主要发生在RDL的底部),导致不同的RDL发生短路。

在专利CN107808865A中,揭示了一种抑制潮湿环境下的金属离子表面迁移的封装结构,如图1所示,在该专利中,采用不同高度的介质层设计,让相邻的两个RDL340(1)、340(2)处于不同的高度,其中RDL340(1)下面具有垫高的介质层330(1),通过该垫高的介质层330(1),RDL340(1)的高度332高于RDL340(2)的高度,从而拉大了两个相邻RDL之间的距离334,使得金属离子迁移路径加大,降低了相邻金属之间被短路的风险。

然而这种增加路径的方法,虽然一定程度上缓解了短路的风险,但是并没有本质上解决潮湿环境下的金属离子迁移。现在有一种做法是在RDL的表面覆盖一层聚合物层(Polymer;PI),用PI来阻止水汽的侵入,进而阻止RDL上金属的扩散(水汽的侵入,会加速铜迁移)。

然而,PI本身是一种吸收性材料,在长期潮湿的环境下,PI层亦会受到水汽的侵入,从而使得相邻的RDL之间的绝缘性能降低。另一方面,PI层和器件表面的介质层(通常为氧化层)之间具有不同的杨氏模量参数,导致两者的界面出具有较强的应力,该应力会导致PI层翘曲并形成一定层度的分离,最终导致两相邻的RDL之间电化学飘逸和相邻金属层之间的电流泄露或短路。

因此,有必要对现有技术中存在的缺陷进行改善并提出一种新的封装结构。

发明内容

有鉴于此,本发明的目的在于提出一种新的半导体封装结构,能够克服现有技术中RDL之间因金属离子迁移造成的短路问题,从而改善器件的性能和使用寿命。

根据本发明的目的提出的一种半导体封装结构,包括

基板,所述基板包括位于表面的第一介质层和位于所述第一介质层下方的半导体器件结构,所述半导体器件结构至少包括临近所述第一介质层的顶层金属层以及位于所述顶层金属层下方的第二金属层;

再分布导电层,设置在所述第一介质层上,所述再分布导电层包括第一RDL段和与所述第一RDL段相邻的第二RDL段,

所述顶层金属层具有图形化结构,该图形化结构使得所述顶层金属层包括与所述第一RDL段电性相连的第一导电线、与所述第二RDL段电性相连的第二导电线,以及设置在所述第一导电线和所述第二导电线之间的空白区,

所述第一介质层对应所述空白区上方的区域设有至少一个开槽,所述开槽阻断所述第一RDL段和所述第二RDL段的至少一漏电路径上,所述开槽的深度大于所述第一介质层表面至所述顶层金属层表面的距离,以及

至少在所述第一RDL段和所述第二RDL段之间的第一介质层上覆有第二介质层,该第二介质层充满于所述开槽中。

优选的,所述开槽为条状开槽,该条状开槽的长度方向与所述第一RDL段的长度方向一致。

优选的,所述开槽为孔状开槽。

优选的,所述孔状开槽包括复数个孔组成的孔阵列,所述孔阵列为规则阵列、错位阵列或非规则阵列中的一种。

优选的,所述开槽的深度小于所述第二金属层表面至所述第一介质层表面的距离。

优选的,所述第一介质层为钝化层,所述第二介质层为PI层。

根据本发明的目的还提出了一种如上所述的半导体封装结构的制作方法,包括步骤:

提供一基板,在所述基板上依次制作半导体器件结构中的各个金属层,所述半导体器件结构至少包括第二金属层和顶层金属层,所述顶层金属层位于所述第二金属层的上方,

对所述顶层金属层进行图形化,使得所述顶层金属层至少包括第一导电线、第二导电线以及位于所述第一导电线和第二导电线之间的空白区,

在所述顶层金属层上制作第一介质层,

在所述第一介质层上制作再分布导电层,对所述再分布导电层刻蚀形成第一RDL段和第二RDL段,且露出所述第一RDL段和所述第二RDL段之间的所述第一介质层,所述第一RDL段与所述第一导电线电性相连,所述第二RDL段与所述第二导电线电性相连;

对所述第一RDL段和所述第二RDL段之间的第一介质层刻蚀,形成至少一个开槽,使所述开槽的深度至少大于所述第一介质层表面至所述顶层金属层表面的距离;

制作第二介质层,使第二介质层至少覆盖所述第一RDL段和所述第二RDL段之间的第一介质层上,且该第二介质层充满于所述开槽中。

根据本发明的目的还提出了一种如上所述的半导体封装结构的制作方法,包括步骤:

提供一基板,在所述基板上依次制作半导体器件结构中的各个金属层,所述半导体器件结构至少包括第二金属层和顶层金属层,所述顶层金属层位于所述第二金属层的上方,

对所述顶层金属层进行图形化,使得所述顶层金属层至少包括第一导电线、第二导电线以及位于所述第一导电线和第二导电线之间的空白区,

在所述顶层金属层上制作第一介质层,

对第一介质层进行图形化,刻蚀出对应第一导电线和第二导电线位置处的若干个金属孔柱,以及对应空白区位置处的至少一个开槽,使所述开槽的深度至少大于所述第一介质层表面至所述顶层金属层表面的距离;;

在所述第一介质层上制作再分布导电层,对所述再分布导电层刻蚀形成第一RDL段和第二RDL段,且露出对应所述空白区位置处的所述第一介质层,所述第一RDL段与所述第一导电线电性相连,所述第二RDL段与所述第二导电线电性相连;

制作第二介质层,使第二介质层至少覆盖所述第一RDL段和所述第二RDL段之间的第一介质层上,且该第二介质层充满于所述开槽中。

优选的,对所述顶层金属层进行图形化的步骤中,所述金属孔柱和所述开槽在一道光刻程序中同步刻蚀完成。

优选的,对所述金属孔柱和所述开槽进行刻蚀时,以所述顶层金属层作为停止层。与现有技术相比,本发明具有如下的技术效果:

1、器件中的顶层金属层被特殊图形化,在对应开槽的位置留空,使得钝化层上的开槽深度可以达到顶层金属甚至更深的位置,从而可以让PI层的附着力提升。

2、利用金属孔洞工艺,在不增加光罩的基础上,能够实现对钝化层的开槽,并且由于利用了顶层金属层的停止作用,可以很好的控制开槽的刻蚀深度。

附图说明

图1是现有技术中的半导体封装结构的示意图。

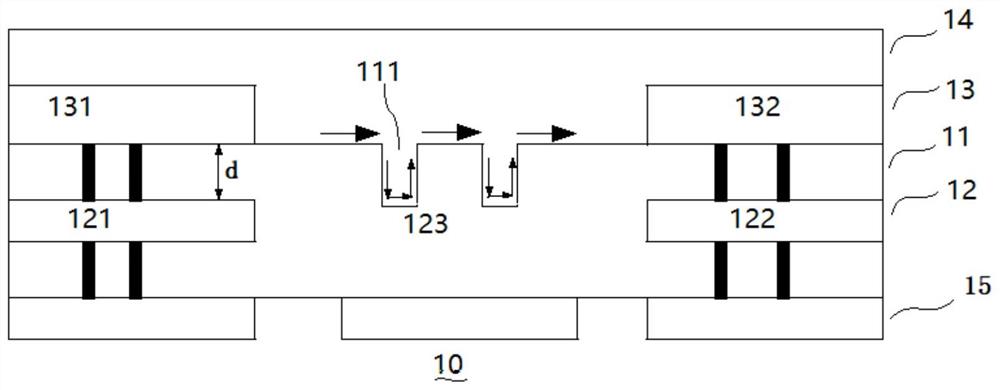

图2是本发明的封装结构剖视图。

图3是本发明第一实施方式下的封装结构俯视图。

图4是本发明第二实施方式下的封装结构俯视图。

图5是本发明第一实施方式下的封装结构制作方法流程示意图。

图6是本发明第二实施方式下的封装结构制作方法流程示意图。

具体实施方式

以下将结合附图所示的具体实施方式对本发明进行详细描述,但这些实施方式并不限制本发明,本领域的普通技术人员根据这些实施方式所做出的结构、方法、或功能上的变换均包含在本发明的保护范围内。

如背景技术中所述的,现有的半导体封装结构中,尽管通过覆盖PI层,让金属离子无法在相邻的RDL之间迁移,但是由于PI层的杨氏模量与下方的钝化层不同,界面上将有较大的应力产生,导致PI层发生脱落分离的现象,从而降低对金属离子的阻挡作用。时间一长,器件依然面临短路的风险。

为了让PI层更好的附着在钝化层上,可以考虑在钝化层上开槽,一方面可以增加附着力,另一方面,也可以增加金属离子在两层间的移动距离,增加抗短路的能力,然而受限于钝化层和顶层金属层之间的距离,开槽的深度如何控制将成为开槽工艺的难题,因为如果开槽的深度过浅,会使得PI层和钝化层之间的附着力提升有限,而如果开槽较深的话,会把下方的顶层金属层暴露出来,这样金属离子一旦移动到开槽内,就会与顶层金属层接触,使得顶层金属层间不同电位的金属线段形成短路。

因此,本发明为了解决上述问题,提出了一种新的半导体封装结构和制作工艺,让钝化层上的开槽深度能够突破顶层金属层的限制,并且在刻蚀时,能够利用现有的半导体结构,对刻蚀深度起到控制作用,从而较精确的实现想要的开槽深度,从而解决PI层和钝化层之间的应力问题,使得器件的短路风险降低,提升了器件的品质。

下面将通过具体实施方式对本发明的技术方案做详细描述。

请参见图2,图2是本发明的半导体封装结构的剖面示意图。如图所示,该半导体封装结构,包括基板10,基板10内部经过半导体器件的制程工艺,已经形成具有特定功能的半导体器件或部分器件的结构(图中未示出),这些结构比如为实现半导体导通或截至的PN结,以及提供上述PN节相应电位的金属或非金属的器件导电层。通常器件导电层可以包括不同的层,每一层通过图形化工艺形成不同的导电线图案。图2中,仅给出了位于顶部的顶部金属层12和该顶部金属层(top metal)12下方的第二金属层15,一般地,对于一个复杂结构的半导体器件而言,该器件导电层会包括更多的金属层或其它材质的导电层。

在本发明中,顶部金属层12的图形化具有一定的特殊性,在图示中,该顶层金属层12包括第一导电线121,第二导电线122以及位于该第一导电线121和第二导电线122之间的空白区123。空白区123是指在图形化过程中利用刻蚀工艺将该区域的金属进行刻蚀,从而使该区域的金属分布具有非连贯的特性,这种非连贯性至少让第一导电线121和第二导电线122之间形成电隔离,对于刻蚀区域的大小可以使工艺以及器件的具体需求而定,比如第一导电线121和第二导电线122之间为了满足器件的电连接需要而设定的最短距离,或者为了让后续的刻蚀具有可操作的空间(满足刻蚀出槽的最低空间需求)等。

另一方面,为了满足基板10内部的半导体器件或部分器件结构的物理强度或电气性能,该基板10的表面需要设置第一介质层11,在一种实际应用中,该第一介质层11以钝化层(passivation layer)的形式制作在基板10的表面,从而至少覆盖内部的器件结构,尤其是对顶部金属层12的覆盖,从而达到保护和电气隔离的作用。同时,由于空白区123的存在,使得第二金属层15位于该空白区123下方的区域与该第一介质层11具有接触,使得该第一介质层11在空白区123所在的区域具有更厚的深度。

第一介质层11上设有再分布导电层13(RDL),该再分布导电层13被图案化从而形成不同的RDL段,每个RDL段以满足半导体器件与外部电子元器件之间的输入输出特性而占居对应的位置。基础的,该再分布导电层13至少包括第一RDL段131和与RDL段131相邻的第二RDL段132,第一RDL段131和第二RDL段132之间相互电隔离,且当半导体器件工作时,第一RDL段131和第二RDL段132之间具有一个电位差,比如第一RDL段131上接有高电位,而第二RDL段132上接地或接入一个低电位,从而形成电位差。该电位差有可能来自半导体器件本身的工作特性要求,也有可能是对外部器件的响应及匹配需求。

一般地,再分布层13的图形与设置在第一介质层11下的顶层金属层12有一定的对应关系,两者之间通过设置在第一介质层11内的若干导电孔柱实现电连接。如图2所示,第一RDL段131对应连接在第一导电线121、第二RDL段132对应连接在第二导电线122,第一导电线121和第二导电线122通过第一RDL段131和第二RDL段132,得以在空间上延申到与外部器件连接所需的位置。

在第一介质层11上,还设有第二介质层14,该第二介质层14覆盖第一RDL段131和第二RDL段132之间的区域上。该第二介质层14比如是聚合物层(PI),填充在再分布导电层13上可以用来隔离各个RDL段。

请再参见图2,第一介质层11对应空白区123上方的区域设有至少一个开槽111,该开槽111阻断第一RDL段131和第二RDL段132的至少一漏电路径上。即如果在第一RDL段131和第二RDL段132发生金属离子迁移时,该开槽111会使得金属离子落入该开槽111中,如图中箭头所示,这些箭头表示金属离子运动轨迹。

并且,当第二介质层14覆盖在第一介质层11上时,将会对开槽111进行填充,较优地,开槽111中充满第二介质层14。尤其是,在本发明中,得益于空白区123的存在,使得开槽111的深度至少不小于第一介质层11到第一金属层12之间的距离d。如此深度不仅可以增加金属离子的迁移路径,而且在第二介质层14附着之后,将加大对该第二介质层14的吸附力,从而可以防止第二介质层14因应力错配导致的翘起和脱落风险。

请参见图3,图3是本发明第一实施方式下的封装结构的俯视图。如图所示,在该第一实施方式中,开槽111为条状开槽,该条状开槽的长度方向与第一RDL段131(或第二RDL段132)的长度方向一致。即如果发生金属离子迁移,那么该条状开槽的长度方向与离子迁移的方向垂直,这样可以最大程度的阻挡离子迁移的路径。图示的实施例仅给出了1条开槽的情况,作为简单的扩展,也可以设置成多条平行的凹槽,这样可以增加离子迁移的难度。

请参见图4,图4是本发明第二实施方式中的封装结构的俯视图。如图所示,在该实施方式中,所述开槽111’为孔状开槽,孔状开槽包括复数个孔组成的孔阵列。孔的数量可以视第一导电线121和第二导电线122之间的间距而定,最少为1个。图4中的孔阵列为规则矩阵,也可以形成错位矩阵,即相邻行之间的孔错位设置,这样一来可以增加对漏电路径的阻挡作用。还可以设置成非规则阵列,通过随机覆盖在金属离子的迁移路径上,使得金属离子被阻挡的概率大大增加。

下面再对本发明的封装结构的制作方法进行描述。

请参见图5,图5是本发明第一实施方式下的半导体封装结构制作方法流程示意图,包括步骤:

S1、提供一基板,在所述基板上依次制作半导体器件结构中的各个金属层,所述半导体器件结构至少包括第二金属层和顶层金属层,所述顶层金属层位于所述第二金属层的上方。顶层金属层和第二金属层之间,可以通过金属孔柱进行电连接,也可以彼此电绝缘,一般在制作这些金属层时,从位于底部的金属层开始制作,比如通过化学气相沉积或物理气相沉积等方法,将金属层制作到半导体基材上。

S2、对顶层金属层进行图形化,使得所述顶层金属层至少包括第一导电线、第二导电线以及位于所述第一导电线和第二导电线之间的空白区。应当理解,尽管在传统工艺中,不同金属层上本身就会实施相应的图形化工艺,然而在本发明中,针对该顶层金属层,在其图形化工艺中,特别的设计使得第一导电线和第二导电线之间形成空白区,该空白区的作用就是可以配合下面的制作工艺进行专有的开槽工艺,使得开槽深度能够达到或突破该顶层金属层所在的位置,从而形成足够深度的开槽。

S3、在所述顶层金属层上制作第一介质层。第一介质层比如是钝化层,覆盖在顶层金属层上,起到保护和电隔离的作用。

S4、在第一介质层上制作再分布导电层,对该再分布导电层刻蚀形成第一RDL段和第二RDL段,且露出对应空白区位置处的第一介质层,所述第一RDL段与所述第一导电线电性相连,所述第二RDL段与所述第二导电线电性相连。再分布层导电层的图形以满足将下方半导体器件中的电引出的需求而定,应当理解,该再分布导电层除了第一RDL段和第二RDL段之外,还会包括更多的电极引出段,在本发明中为了突出发明意图,仅以第一RDL段和第二RDL段进行示意。

S5、对第一RDL段和所述第二RDL段之间的第一介质层刻蚀,形成至少一个开槽,使所述开槽的深度至少大于所述第一介质层表面至所述顶层金属层表面的距离。

S6、制作第二介质层,使第二介质层至少覆盖所述第一RDL段和所述第二RDL段之间的第一介质层上,且该第二介质层充满于所述开槽中。

请参见图6,图6是本发明第二实施方式下的半导体封装结构制作方法流程示意图

S1’、提供一基板,在所述基板上依次制作半导体器件结构中的各个金属层,所述半导体器件结构至少包括第二金属层和顶层金属层,所述顶层金属层位于所述第二金属层的上方。顶层金属层和第二金属层之间,可以通过金属孔柱进行电连接,也可以彼此电绝缘,一般在制作这些金属层时,从位于底部的金属层开始制作,比如通过化学气相沉积或物理气相沉积等方法,将金属层制作到半导体基材上。

S2’、对顶层金属层进行图形化,使得所述顶层金属层至少包括第一导电线、第二导电线以及位于所述第一导电线和第二导电线之间的空白区。应当理解,尽管在传统工艺中,不同金属层上本身就会实施相应的图形化工艺,然而在本发明中,针对该顶层金属层,在其图形化工艺中,特别的设计使得第一导电线和第二导电线之间形成空白区,该空白区的作用就是可以配合下面的制作工艺进行专有的开槽工艺,使得开槽深度能够达到或突破该顶层金属层所在的位置,从而形成足够深度的开槽。

S3’、在所述顶层金属层上制作第一介质层。第一介质层比如是钝化层,覆盖在顶层金属层上,起到保护和电隔离的作用。

S4’、对第一介质层进行图形化,刻蚀出对应第一导电线和第二导电线位置处的若干个金属孔柱,以及对应空白区位置处的至少一个开槽,使所述开槽的深度至少大于所述第一介质层表面至所述顶层金属层表面的距离。

S5’、在第一介质层上制作再分布导电层,对该再分布导电层刻蚀形成第一RDL段和第二RDL段,且露出对应空白区位置处的第一介质层,所述第一RDL段与所述第一导电线电性相连,所述第二RDL段与所述第二导电线电性相连。再分布层导电层的图形以满足将下方半导体器件中的电引出的需求而定,应当理解,该再分布导电层除了第一RDL段和第二RDL段之外,还会包括更多的电极引出段,在本发明中为了突出发明意图,仅以第一RDL段和第二RDL段进行示意。

S6’、制作第二介质层,使第二介质层至少覆盖所述第一RDL段和所述第二RDL段之间的第一介质层上,且该第二介质层充满于所述开槽中。

在第二实施方式中,对应于在第一介质层中制作金属孔柱,可以用于后续的再分布导电层与顶层金属层之间的电性连接。在制作金属孔柱的时候,利用同一道光刻程序,就可以实现对开槽的同步刻蚀,节省了光刻次数。

优选的,在该实施方式中,可以以顶层金属层作为停止层,即在刻蚀金属孔柱和开槽的时候,当深度达到顶层金属层时停止刻蚀,这样一来,对于开槽可以确保具有足够深度的刻蚀,且不至于失去对刻蚀深度的控制,使其能够停留在顶层金属层的深度位置,从而达到本发明的发明目的。

此时步骤S4包括步骤:

S41:设计一光罩,该光罩的图形包括对应第一导电线和第二导电线处的多个金属孔柱图形和对应空白处的至少一个开槽图形。

S42:利用该光罩对该半导体器件进行光刻,以露出对应光罩图形位置处的第一介质层。

S43:利用湿法刻蚀或干法刻蚀,以所述顶层金属层作为停止层进行刻蚀,以形成所述金属孔柱和所述开槽。

综上所述,本发明提出了一种半导体封装结构,该封装结构通过对顶层金属层进行图形化,留出空白区,并且利用该顶层金属层作为停止层,对钝化层表面开槽,使得开槽的深度可以达到顶层金属层的深度,增加PI层的吸附力,且能够吸收部分界面处产生的应力,从而降低了PI层翘曲的风险,增加了半导体器件的品质和使用寿命。

尽管为示例目的,已经公开了本发明的优选实施方式,但是本领域的普通技术人员将意识到,在不脱离由所附的权利要求书公开的本发明的范围和精神的情况下,各种改进、增加以及取代是可能的。

- 一种半导体封装结构制作方法及半导体封装结构

- 一种半导体封装结构制作方法及半导体封装结构