一种电路节点初始化实现方法

文献发布时间:2023-07-05 06:30:04

技术领域

本发明涉及电路节点初始化技术,特别是一种电路节点初始化实现方法。

背景技术

在复位检测电路及一些其他芯片中,由于一些模拟节点信号建立需要一定延迟时间,可能导致节点初始状态不确定。经常需要在电源上电时,设置内部节点初始化状态,保证电源上电初始瞬间信号正确。通常做法是在一些模拟节点加对电源或者对地电容。当有些节点对电源加电容时,虽然能保证其初始化状态正确,但当电源上电结束后,如果VCC出现瞬态变化,这些节点的驱动能力往往比较弱,这时初始化电容上产生的电流可能大于节点对GND的驱动能力,使该节点升高,后续逻辑错误翻转。

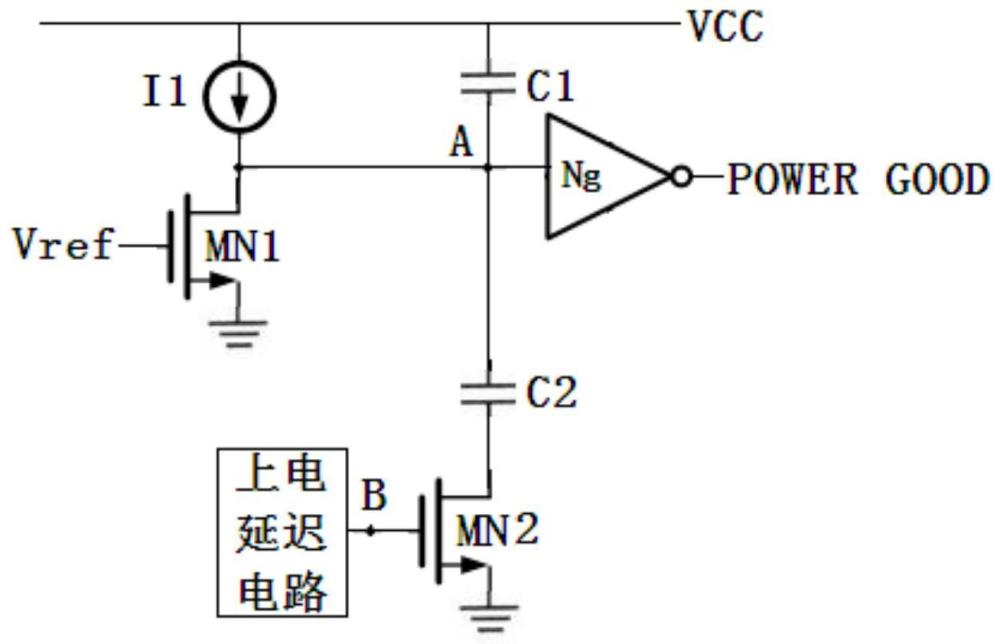

图5是现有技术中电路节点初始化结构示意图。如图5所示,该电路检测Vref电压,当Vref电压大于MN1阈值电压,且Vref电压足够高,使MN1电流能力大于I1时,使A节点为低,经过反相器Ng,POWER_GOOD信号为高。由于电路上电过程中,I1电流和Vref建立都需要一定时间,所以在电路加入电容C1,保证上电初始时,A点为高,POWER_GOOD信号为低,保证初始逻辑正确性。

但该电路存在如下问题,由于设计需要,一般Vref电压不会比MN1阈值电压高很多,使MN1驱动能力不会很强。在电路建立完成后,如果VCC上出现瞬态向上的波动,C1两端瞬间电压变化,会产生从电源到A点的瞬态电流,该电流可能大于MN1驱动能力,导致此时A点电压上升,高于反相器翻转阈值而使反相器错误翻转,POWER_GOOD会输出一次错误的低脉冲信号。

发明内容

本发明针对现有技术中存在的缺陷或不足,提供一种电路节点初始化实现方法。

本发明的技术解决方案如下:

一种电路节点初始化实现方法,其特征在于,包括设置了初始化状态的内部节点,所述内部节点为反相器输入端,所述反相器的输出端用于输出POWER GOOD指示信号,将所述反相器输入端作为第一节点,所述第一节点第一路通过第一电容连接电源电压端,第二路通过第一电流源连接电源电压端,第三路连接第一NMOS管的漏极,第四路通过第二电容连接第二NMOS管的漏极,所述第二NMOS管的源极接地,所述第二NMOS管的栅极作为第二节点连接上电延迟电路,所述第一NMOS管的源极接地,所述第一NMOS管的栅极连接参考电压端。

设所述第二电容的电容值为C2,所述第一电容的电容值为C1,则C2>>C1。

所述上电延迟电路包括第一电阻和第三电容,所述第二节点第一路连接所述第一电阻的一端,第二路连接所述第三电容的一端,所述第一电阻的另一端连接电源电压端,所述第三电容的另一端接地。

所述上电延迟电路包括第一电阻和第三电容,所述第二节点第一路连接所述第一电阻的一端,第二路连接所述第三电容的一端,所述第一电阻的另一端连接参考电压端,所述第三电容的另一端接地。

所述上电延迟电路包括第一电阻、第二电阻和第四电容,所述第二节点第一路连接所述第一电阻的一端,第二路连接所述第四电容的一端,第三路连接所述第二电阻的一端,所述第一电阻的另一端连接电源电压端,所述第四电容的另一端接地,所述第二电阻的另一端接地。

本发明的技术效果如下:本发明一种电路节点初始化实现方法,通过针对设置了初始化状态的内部节点形成第一电容、第一电流源、第一NMOS管、反相器、第二电容、第二NMOS管、上电延迟电路的组合,既能够保证初始状态,又能够避免节点在VCC快速变化使电路出现错误状态。

附图说明

图1是实施本发明一种电路节点初始化实现方法所形成的结构示意图。

图2是图1中上电延迟电路第一种示例结构示意图。

图3是图1中上电延迟电路第二种示例结构示意图。

图4是图1中上电延迟电路第三种示例结构示意图。

图5是现有技术中电路节点初始化结构示意图。

附图标记列示如下:Vref-参考电压端或参考电压;VCC-电源电压端或电源电压;I1-第一电流源;C1~C4-第一电容至第四电容;R1~R2-第一电阻至第二电阻;MN1~MN2-第一NMOS管至第二NMOS管;Ng-反相器;A~B-第一节点至第二节点;POWER GOOD-电源良好指示信号。

具体实施方式

下面结合附图(图1-图4)对本发明进行说明。

图1是实施本发明一种电路节点初始化实现方法所形成的结构示意图。图2是图1中上电延迟电路第一种示例结构示意图。图3是图1中上电延迟电路第二种示例结构示意图。图4是图1中上电延迟电路第三种示例结构示意图。参考图1至图4所示,一种电路节点初始化实现方法,包括设置了初始化状态的内部节点,所述内部节点为反相器输入端,所述反相器Ng的输出端用于输出POWER GOOD指示信号,将所述反相器输入端作为第一节点A,所述第一节点A第一路通过第一电容C1连接电源电压端VCC,第二路通过第一电流源I1连接电源电压端VCC,第三路连接第一NMOS管MN1的漏极,第四路通过第二电容C2连接第二NMOS管MN2的漏极,所述第二NMOS管MN2的源极接地,所述第二NMOS管MN2的栅极作为第二节点B连接上电延迟电路,所述第一NMOS管MN1的源极接地,所述第一NMOS管MN1的栅极连接参考电压端Vref。设所述第二电容的电容值为C2,所述第一电容的电容值为C1,则C2>>C1。

所述上电延迟电路包括第一电阻R1和第三电容C3,所述第二节点B第一路连接所述第一电阻R1的一端,第二路连接所述第三电容C3的一端,所述第一电阻R1的另一端连接电源电压端VCC,所述第三电容C3的另一端接地。所述上电延迟电路包括第一电阻R1和第三电容C3,所述第二节点B第一路连接所述第一电阻R1的一端,第二路连接所述第三电容C3的一端,所述第一电阻R1的另一端连接参考电压端Vref,所述第三电容C3的另一端接地。所述上电延迟电路包括第一电阻R1、第二电阻R2和第四电容C4,所述第二节点B第一路连接所述第一电阻R1的一端,第二路连接所述第四电容C4的一端,第三路连接所述第二电阻R2的一端,所述第一电阻R1的另一端连接电源电压端VCC,所述第四电容C4的另一端接地,所述第二电阻R2的另一端接地。

本发明通过在电路上电结束后接入电容C2,使C2远大于C1,既能保证初始状态,又避免了节点在VCC快速变化使电路出现错误状态。

参考图1,在VCC上电时,B点为0,MN2处于截至状态,C2悬空接于A点,并不会对A点产生影响。上电时,C1起作用,使A节点开始跟随VCC,电路正常初始化,POWER_GOOD信号为低。在经过一定的延迟时间后,B点升高,使MN2导通,电容C2连接于A点与地之间。从而当VCC上电结束后,由于C2远大于C1,如果VCC上出现瞬态向上的波动时,A点状态几乎不变,不会造成反相器错误翻转。

本发明说明书中未作详细描述的内容属于本领域专业技术人员公知的现有技术。在此指明,以上叙述有助于本领域技术人员理解本发明创造,但并非限制本发明创造的保护范围。任何没有脱离本发明创造实质内容的对以上叙述的等同替换、修饰改进和/或删繁从简而进行的实施,均落入本发明创造的保护范围。