一种基于双路的数据采集并行数据传输及存储的装置及方法

文献发布时间:2023-06-19 11:39:06

技术领域

本发明涉及一种基于双路的数据采集并行数据传输及存储的装置及方法,属于计算机的嵌入式开发技术领域。

背景技术

由于计算机领域嵌入式技术的发展,使得数据采集实现智能化;并且物联网的广泛应用也使得目前对实时数据采集的需求越来越多,而单一的外部采集模块所容纳的采集通道有限,无法满足大量数据采集的需求。现有的数据采集方法大都需要更多的采集模块,而大量的数据被采集并传输进入微控制器的缓存区通常需要再次取出并存放至外部数据存储模块。在需要控制产品成本的情况下,微控制器内的缓存相对有限,需要将采集的数据进行传输并实时存储至外部存储模块。然而,由于数据采集模块的多路采集模式使得微控制器很难在实时数据采集的同时实现数据的外部存储。

并且,在数据采集和处理速度已经极大提高的前提下,单一数据传输通道及存储模块不仅降低了数据传输的效率,而且导致微控制器的存储压力过大。此时,能够采用DMA控制器来完成实际的数据传输并将数据放入缓存区。发明专利CN107430566B、CN102844743A及CN102844743B等都公开了一种具有多个DMA引擎的DMA控制器。通过采用多个DMA引擎,能够对多个采集模块实时采集得到的数据分别进行多路传输并存储。然而,上述发明中公开的DMA控制器,只是单纯的利用多通道DMA的方法来传输数据,并没有采用微控制器中的其他资源来协调,不能提高数据传输的效率。

为了达到最快的采集、传输及存储速度,在采集模块进行数据实时采集的同时进行数据传输并将采集的数据放到入外部存储器,微控制器需要进行资源调配,以协调数据采集模块、传输模块及存储模块,实现同步运行,从而提高数据采集、传输及存储的效率。

发明内容

为了解决目前多路实时采集数据的传输及存储效率不高的问题,本发明的技术方案通过对微控制器的内置资源进行重新配置,提供了一种能够实现双路的数据采集并行数据传输及存储的装置及方法,达到了最大化数据采集、传输及存储速率的效果。

根据本发明的基于双路的数据采集并行数据传输及存储的方法及装置,其具体技术方案如下:

一种基于双路的数据采集并行数据传输及存储的装置,具体包括:双路数据采集模块,微控制器,SPI总线、FSMC总线及外部存储模块;其中,数据采集模块包括第一采集模块和第二采集模块;并且,微控制器设置有定时器、DMA控制器以及缓存区。

根据本发明所述的装置,微控制器的定时器包括第一定时器、第二定时器和第三定时器;DMA控制器包括第一DMA和第二DMA;缓存区包括第一缓存区和第二缓存区;其中,第一DMA及第二DMA分别通过SPI总线与第一采集模块及第二采集模块连接,并分别连接至第一缓存区及第二缓存区;第一定时器与第二定时器相连接,第二定时器与第三定时器相连接,第一定时器与第一DMA相连接,第二定时器与第二DMA相连接;并且,第一缓存区及第二缓存区通过FSMC总线与外部数据存储模块相连接。

根据本发明所述的装置,可选地,微控制器的缓存区还包括第一备用缓存区和第二备用缓存区;并且第一备用缓存区和第二备用缓存区能够通过FSMC总线与外部数据存储模块相连接。

根据本发明所述的装置,本发明提供了一种基于双路的数据采集并行数据传输及存储的方法,具体而言,该方法能够包括如下步骤:

步骤1),微控制器将第三定时器的定时频率设定为SPI总线、FSMC总线、第一采集模块及第二采集模块的最大采集频率,并且,将第二定时器的定时频率设定为第二采集模块串行传输数据的频率,将第一定时器的定时频率设定为第一采集模块串行传输数据的频率;

步骤2),将第三定时器设置为主模式,将第二定时器设置为内置事件触发从模式,由第三定时器触发第二定时器,第二定时器的事件更新触发第二DMA进行一次数据传输,以接收第二采集模块的数据;

步骤3),当第二DMA完成一次数据接收之后,将第二定时器设置为主模式,同时将第一定时器设置为内置事件触发从模式,由第二定时器触发第一定时器;并且第一定时器的事件更新触发第一DMA进行一次数据传输,以接收第一采集模块的数据;

步骤4),当第一DMA完成一次数据接收之后,再次将第三定时器设置为主模式,将第二定时器设置为内置事件触发从模式,由第三定时器再次触发第二定时器。

根据本发明所述的方法,可选地,第一DMA将接收到的数据传输至第一缓存区,第二DMA将接收到的数据传输至第二缓存区。

根据本发明所述的方法,可选地,当微控制器中的第一缓存区和第二缓存区的数据存储量达到上限时,微控制器控制FSMC总线将第一缓存区和第二缓存区的数据传输至外部数据存储模块;并且,微控制器同时将第一采集模块和第二采集模块的数据传输目的地设置为第一缓存备用区和第二缓存备用区。

根据本发明所述的方法,可选地,第一缓存备用区及所述第二缓存备用区通过FSMC总线与外部数据存储模块相连接,并且,当微控制器中的第一缓存备用区和第二缓存备用区的数据存储量达到上限时,微控制器控制FSMC总线将第一缓存备用区和第二缓存备用区的数据传输至所述外部数据存储模块;并且微控制器同时将第一采集模块和第二采集模块的数据传输目的地再次设置为第一缓存区和第二缓存区。

根据本发明所述的方法,可选地,第一DMA和第二DMA接替被触发,微控制器一旦开启第三定时器,第三定时器、第二定时器及第一定时器之间的相互控制使得第一DMA和第二DMA的数据传输能够自动运行,实现数据传输的流水线操作。

根据本发明所述的方法,可选地,微控制器采用定时器控制第一DMA和第二DMA进行数据交替接收的同时,第一DMA和第二DMA同步将接收到的数据分别传输至第一缓存区和第二缓存区,使得微处理器在数据存储的过程中同时开始新的数据采集,保持数据采集、传输及存储同步并行。

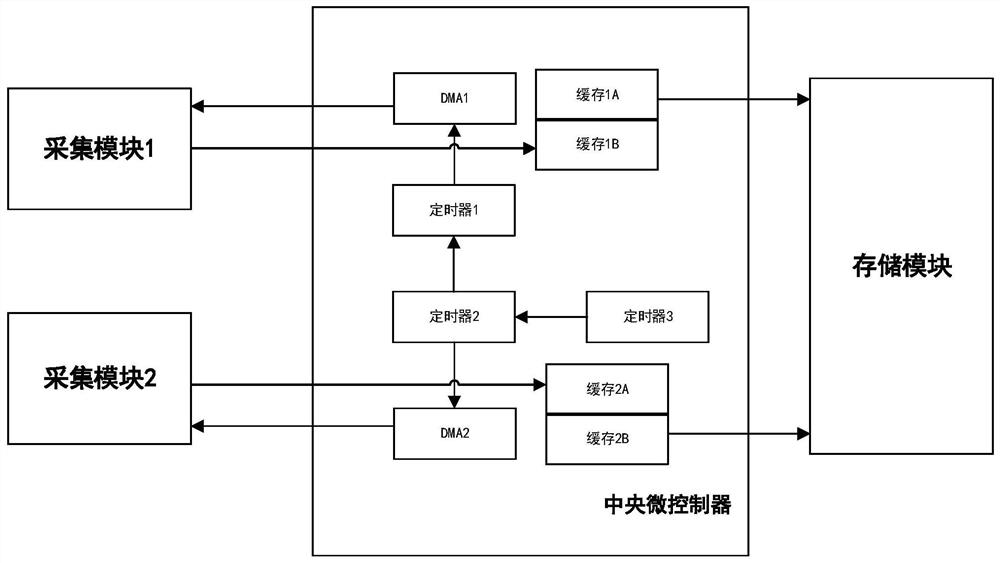

根据本发明所述的装置,如图1所示,用于对双路的数据采集并行数据传输及存储的中央微控制器设置有定时器、DMA以及缓存区,双路的数据采集模块包括采集模块1和采集模块2,分别具有独立的采集功能。微控制器中的定时器包括定时器1、定时器2和定时器3,DMA控制器包括DMA1和DMA2,并且缓存区设置有四个分配空间,分别为缓存区1A、缓存区1B、缓存备用区2A和缓存备用区2B。其中,DMA1及DMA2分别通过SPI总线与采集模块1及采集模块2连接,并分别连接至缓存区1A及缓存区2A;定时器1与定时器2相连接,定时器2与定时器3相连接,定时器1与DMA1相连接,定时器2与DMA2相连接;并且,缓存区1A及缓存区2A通过FSMC总线与外部数据存储模块相连接。

进一步,根据本发明所述的方法,首先,将微控制器中定时器3的定时频率设定为采集模块1、采集模块2及SPI总线,FSMC总线的最大采集频率,用来模拟采集控制的频率;并且,将定时器2的定时频率设定为采集模块2串行传输数据的频率,将定时器1的定时频率设定为采集模块1串行传输数据的频率。进一步,将定时器3设置为主模式,将定时器2设置为内置事件触发从模式,由定时器3触发定时器2,定时器2的事件更新能够触发DMA2进行一次数据传输,接收采集模块2的数据;并且,当DMA2完成一次数据接收之后,将定时器2设置主模式,将定时器1设置为内置事件触发从模式,由定时器2触发定时器1;定时器1的事件更新能够触发DMA1进行一次数据传输,接收采集模块1的数据;最后,DMA1进行一次数据接收之后,再次将定时器3设置为主模式,将定时器2设置为内置事件触发从模式,由定时器3再次触发定时器2。

根据本发明所述的方法,可选地,DMA1将接收到的数据传输至缓存区1A,DMA2将接收到的数据传输至缓存区2A。根据本发明所述的方法,进一步可选地,当微控制器中的缓存区1A和缓存区2A的数据存储量达到上限时,微控制器控制FSMC总线将缓存区1A和缓存区2A的数据传输至外部数据存储模块;并且,同时微控制器控制SPI总线将采集模块1和采集模块2的数据传输目的地设置为缓存备用区1B和缓存备用区2B。

根据本发明所述的方法,可选地,定时器2由定时器3触发,定时器1由定时器2触发,并且在定时器2定时结束后启动定时器1,定时器1结束后由定时器3再次触发定时器2,从而DMA1和DMA2接替被触发,定时器2的定时频率与采集模块2串行传输数据的频率相同,定时器1的定时频率与采集模块1串行传输数据的频率相同,能够保证数据在采集模块2的数据被DMA2接收之后进行采集模块1的数据传输,并且在采集模块1的数据被DMA1接收之后再次进行采集模块2的数据传输。进一步,微控制器一旦开启定时器3,定时器3、定时器2以及定时器1之间的相互控制使得DMA1和DMA2的数据传输能够自动运行,实现数据传输的流水线操作。

根据本发明所述的方法,可选地,微控制器采用定时器控制DMA1和DMA2进行数据交替接收的同时,第一DMA和第二DMA同步将接收到的数据分别传输至缓存区1A和第二缓存区2A,使得微处理器在数据存储的过程中同时开始新的数据采集,保持数据采集、传输和存储的同步并行。

根据本发明所述的方法,可选地,在缓存区1A和缓存区2A的数据存储量达到上限之后,微控制器将缓存区1A和缓存区2A的数据传输至外部存储模块,同时启用缓存备用区1B和缓存区备用区2B,从而能够在数据采集的过程中同时对微处理器缓存区中的数据进行外部存储,并进一步节省数据传输的时间。

本发明的有益效果是:

根据本发明的技术方案,微控制器能够采用多个定时器进行内部资源的控制调配,并且在配置前针对每个采集模块计算好进行一次数据采集所需时间、采集得到的数据进行一次传输所需时间以及数据传输到存储端进行一次存储所需时间。并且,微控制器能够根据计算得到的时间设定定时器的指定频率,能够提高数据的采集、传输及存储速度。

进一步,根据本发明的技术方案,微控制器一旦开启第三定时器,定时器之间的相互控制能够接替触发第一DMA和第二DMA分别进行数据接收,从而DMA控制器对数据的传输能够自动运行,实现数据传输的流水线操作。并且,第一DMA和第二DMA能够对从两个数据采集模块接收到的数据同步进行数据传输,将接收到的数据分别传输至第一缓存区和第二缓存区;使得微处理器能够在数据存储的过程中同时开始新的数据采集,保持数据采集、传输和存储的同步并行。

更进一步地,根据本发明的技术方案,在缓存区的数据存储量达到上限之后,微控制器将缓存区的数据取出并传输至外部存储模块,同时启用缓存备用区,使得微处理器能够在数据采集的过程中同时对微控制器缓存区的数据进行外部存储,从而极大配置了微控制器的资源,节省了数据传输的时间,实现高效的数据采集、传输及存储。

本发明的基于双路的数据采集并行数据传输及存储方法,根据一个优选实施方案,采用微控制器内置定时器之间相互启动的方式来实现双路DMA的并行传输及存储,能够有效缩减数据传输的时间,无需数据等待,实现数据传输的流水线控制;并且在定时器控制双路DMA进行数据交替接收的同时,双路DMA同步将接收到的数据分别进行存储,使得微处理器在数据存储的过程中同时开始新的数据采集,从而实现双路的数据采集、传输和存储的同步并行,能够提升30%以上的数据传输效率。并且,根据本发明的上述方法,完全基于微控制器内部资源的配置,实现数据的高效传输和存储,极大节约了成本。

附图说明

为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

图1是根据本发明的基于双路的数据采集并行数据传输及存储装置的示意图。

图2是根据一个优选实施例,本发明的基于双路的数据采集并行数据传输及存储方法的具体流程图。

具体实施方式

为使本发明的目的、技术方案和优点更加清楚,下面将结合附图对本发明实施方式作进一步地详细描述。

根据本发明的一个优选实施方案,根据本发明的基于双路的数据采集并行数据传输及存储的装置,具体包括:双路数据采集模块,微控制器,SPI总线、FSMC总线及外部存储模块;其中双路的数据采集模块包括采集模块1和采集模块2,分别具有独立的采集功能。微控制器中的定时器包括定时器1、定时器2和定时器3,DMA控制器包括DMA1和DMA2,并且缓存区设置有四个分配空间,分别为缓存区1A、缓存区1B、缓存备用区2A和缓存备用区2B。其中,DMA1及DMA2分别通过SPI总线与采集模块1及采集模块2连接,并分别连接至缓存区1A及缓存区2A;定时器1与定时器2相连接,定时器2与定时器3相连接,定时器1与DMA1相连接,定时器2与DMA2相连接;并且,缓存区1A及缓存区2A通过FSMC总线与外部数据存储模块相连接。

根据本发明的一个优选实施方案,缓存备用区2A和缓存备用区2B能够通过FSMC总线与外部数据存储模块相连接。

根据本发明的一个优选实施方案,微控制器采用STM32F407的控制芯片(此外,还能够采用STM32F2系列芯片和STM32F5系列芯片等具有Cortex-M3和Cortex-M4内核的芯片),该控制芯片拥有8个定时器资源和双通道DMA控制器,并且,该芯片具有FSMC总线和SPI总线资源。

根据本发明的优选实施方案,采集模块1和采集模块2采用AD7606芯片(还能够采用AD7616、CL1606等支持多通道总线传输方式的高速采集芯片),该芯片拥有8通道采集,采集频率最高可达100kHz;外部存储模块采用NAND Flash芯片,采用的型号为K9F1G08U0C(还可以采用HY27UF082G2B、K9G4G08U0B等其他8位或16位数据宽度并支持总线传输的NANDFlash芯片)。根据本发明的优选实施方案,采用SPI总线与AD7606芯片进行通信,并进行采集模块1和采集模块2的数据接收,采用FSMC总线将采集得到的数据传输至外部数据存储模块NAND Flash中进行存储。

根据本发明的优选实施方案,根据上述装置,本发明的基于双路的数据采集并行数据传输及存储的方法具体分为如下步骤:

步骤1),设置定时器1、定时器2和定时器3的定时频率:将定时器3的定时频率设置为系统最大的采集频率,即SPI总线、FSMC总线和采集模块1、采集模块2的AD7606芯片中的上限频率;将定时器2的定时频率设置为采集模块2串行传输数据的频率,即DMA2控制SPI总线进行一次发送及一次接收的频率;将定时器1的定时频率设定为采集模块1串行传输数据的频率,即DMA1控制SPI总线进行一次发送及一次接收的频率。

步骤2),将定时器3设置为主模式,将定时器2设置为内置事件触发从模式,从而定时器3能够在指定时间触发定时器2启动;由定时器3触发定时器2,定时器2的事件更新能够触发DMA2进行一次数据传输,以接收采集模块2的数据;

步骤3),当DMA2完成一次数据接收之后,将定时器2设置为主模式,将定时器1设置为内置事件触发从模式,由定时器2触发定时器1;定时器1的事件更新触发DMA1进行一次数据传输,以接收采集模块1的数据;

步骤4),当DMA1完成一次数据接收之后,再次将定时器3设置为主模式,将定时器2设置为内置事件触发从模式,由定时器3再次触发定时器2。

根据本发明的优选实施方案,采集模块1、采集模块2及SPI总线,FSMC总线的上限频率为80kHz,因此,定时器3的定时频率设置为80kHz。定时器3每定时达到指定频率,就会发送触发更新事件。根据上述方法,定时器2由定时器3触发,定时器1由定时器2触发,并且在定时器2定时结束后启动定时器1,定时器1结束后由定时器3再次触发定时器2,从而DMA1和DMA2接替被触发。

根据本发明的优选实施方案,由于定时器2的定时频率与DMA2控制SPI总线进行一次发送、接收的频率相同,定时器1的定时频率与DMA1控制SPI总线进行一次发送、接收的频率相同,从而保证在采集模块2的数据被DMA2接收之后,由定时器2触发定时器1,DMA1开始接收采集模块1的数据,并且在采集模块1的数据被DMA1接收之后,由定时器3再次触发定时器2,由DMA2再次开始接收采集模块2的数据。

根据本发明的优选实施方案,微控制器芯片STM32F407的总线主频为84MHz,设置定时器3的预分频值TIM_Prescaler=1,以及计数值TIM_Period=524,从而保证定时频率为80Khz。将定时器3设置为主模式,定时器2被定时器3触发,定时器2的事件更新会直接触发DMA2进行SPI总线的发送,并从采集模块2的AD7606芯片接收一次数据,设置定时器2的预分频值TIM_Prescaler=1,重复计数周期次数为TIM_RepetitionCounter=7,计数值TIM_Period=33,保证占空比为50%,其变换状态计数值TIM_Pulse=17;并且,定时器2设置为从模式TIM_SlaveMode_Trigger,且被触发条件设置为TIM_TS_ITR2。进一步,定时器1是被定时器2触发,定时器1的事件更新会直接触发DMA1进行SPI的发送,从采集模块1的AD7606芯片接收一次数据,此时定时器2要设置为主模式TIM_MasterSlaveMode_Enable且输出事件设置为TIM_TRGOSource_OC1。定时器1的同理要被设置为TIM_SlaveMode_Trigger从模式,并触发条件为TIM_TS_ITR0,其定时值应和定时器2相同,预分频值TIM_Prescaler=1,重复计数周期次数为TIM_RepetitionCounter=7,计数值TIM_Period=33。

根据本优选实施方案,进一步,由于DMA1和DMA2接替被触发,微控制器一旦开启定时器3,定时器3、定时器2以及定时器1之间的相互控制使得DMA1和DMA2的数据传输自动运行。定时器2和定时器1分别能够发送DMA请求,让DMA控制SPI总线对数据进行传输,由于SPI总线工作在全双工模式,SPI总线的接收需要通过发送的频率来控制,定时器2和定时器1分别定时发送指定频率的更新事件来让DMA1和DMA2分别控制SPI总线进行一次发送,并完成一次数据接收。同时DMA控制器管理缓存区,由于微控制器中设置了双缓存区,DMA1和DMA2能够分别将接收的采集数据传输至缓存区1A和缓存区2A中。从而,微控制器采用定时器控制DMA1和DMA2进行数据交替接收的同时,DMA1和DMA2同步将接收到的数据分别传输至第一缓存区和第二缓存区,使得微处理器在数据存储的过程中同时开始新的数据采集,保持数据采集、传输及存储同步并行。

根据本优选实施方案,更进一步,当缓存区1A和缓存区2A中的数据存储量达到上限之后发出缓存溢出事件,然后微控制器控制FSMC总线将缓存区1A和缓存区2A中的数据取出并存入NAND Flash中,同时切换SPI总线接收数据的缓存地址,将接收地址分别替换为缓存区1B和缓存区2B。从而,微处理器能够在将数据存储至外部存储器的过程中同时开始新的数据采集,能够进一步节省数据传输的时间,提高数据传输的效率。

根据本发明的优选实施方案,最大采集频率为80KHz的数据采集模块,由于微控制器内部的资源配置,设置了每个定时器的定时频率,并且设置定时器之间的相互触发,从而微控制器一旦开启定时器3,定时器3、定时器2以及定时器1之间的相互控制使得DMA1和DMA2的数据传输自动运行;进一步,定时器控制DMA1和DMA2进行数据交替接收的同时,DMA1和DMA2同步将接收到的数据分别传输至缓存区1A和第二缓存区2A,使得微处理器在数据存储的过程中同时开始新的数据采集。采用本发明的双路数据采集、传输和存储的同步并行的方法,每秒传输比特率能够达到20.48Mb/s,根据本实施方案,实测每秒传输比特率达到20.12Mb/s,基本达到实时数据采集、传输及存储的同步状态。

根据本发明的优选实施方案,采用微控制器内置的定时器之间相互启动的方式来实现双路DMA的并行传输及存储,有效地缩减了数据传输的时间,无需数据等待,能够实现数据传输的流水线控制;并且在定时器控制双路DMA进行数据交替接收的同时,双路DMA同步将接收到的数据分别传输至缓存区,使得微处理器在数据存储的过程中同时开始新的数据采集,从而保持基于双路的数据采集、传输和存储的同步并行。更进一步,当微控制器中的缓存区达到上限之后,由于缓存备用区的配置,微处理器能够在数据采集的过程中同时将微控制器缓存区中的数据存储至外部存储模块,从而极大地配置微控制器的内部资源,更进一步节省了数据传输的时间。据本发明的上述优选实施方案,能够提升30%以上的数据传输效率。根据本发明的上述方法,完全基于微控制器内部资源的配置,实现数据的高效传输和存储,极大节约了成本。

本发明实施例中的部分步骤,可以利用软件实现,相应的软件程序可以存储在可读取的存储介质中,如光盘或硬盘等。

以上仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 一种基于双路的数据采集并行数据传输及存储的装置及方法

- 一种双路并行译码存储设备及方法