一种共源共栅级联功率及其制备方法

文献发布时间:2024-01-17 01:21:27

技术领域

本发明涉及一种半导体技术领域,特别地涉及一种共源共栅级联功率及其制备方法。

背景技术

在半导体器件领域,基于应用场景,常常需要将两个或两个以上的器件封装在一起构成一个具有一定功能的半导体器件,既能提高器件集成度,又减少了由于器件之间的外部电连接而引入的寄生参数,因而这种形式的器件得到了广泛的应用。

参见图1,图1是公告号为CN 218160367 U、名称为“Cascode封装结构”的中国发明专利公开的一种Cascode封装结构示意图。图中的Cascode器件包括金属-氧化物半导体场效应晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor,简称金氧半场效晶体管或MOSFET)芯片和高电子迁移率晶体管(High electron mobility transistor,简称HEMT)芯片,HEMT芯片为一种氮化镓(GaN)基半导体芯片,其直接封装在基岛上,而MOSFET芯片通过基板间接封装在基岛上,基岛封装在引线框架上。MOSFET芯片和HEMT芯片之间通打线的方式电连接。图1中的Cascode封装结构引入了基板,MOSFET芯片和HEMT芯片并列水平设置,增加了封装尺寸,不利于器件的小型化,提高了器件成本,而且还引入了较大的寄生参数。

参见图2,图2是公告号为US8847408B2、名称为“封装中堆叠有FET的Ⅲ族氮化物晶体管(Ⅲ-Nitride Transistor Stacked With FET in a Package)”的美国专利公开的一种封装结构示意图,其中的硅基MOSFET芯片放置于Ⅲ族氮化物晶体管之上,虽然能够获得更小的封装尺寸,但是硅基MOSFET芯片的散热路径需要经过Ⅲ族氮化物晶体管,增加了硅基MOSFET芯片散热路径长,导致硅基MOSFET芯片散热特性差,而且会导致Ⅲ族氮化物晶体管的热量分布不均匀,影响Ⅲ族氮化物晶体管的性能。

发明内容

针对现有技术中存在的技术问题,本发明提出了一种共源共栅级联功率及其制备方法,用以解决半导体器件散热特性与封装尺寸无法兼顾的技术问题。

为了解决上述技术问题,本发明提供了一种半导体器件,其管芯结构包括第一管芯和第二管芯,所述第一管芯包括第一区域和第二区域,所述第一区域为所述第一管芯的功能区,其中包括由III-V族半导体层构成的第一异质结和多个第一电极,所述多个第一电极中的部分第一电极与所述第一异质结耦合;所述第二管芯位于所述第一管芯的第二区域的上方,所述第二管芯包括多个第二电极,多个第一电极中的部分第一电极通过第一导电层电连接多个第二电极中的部分第二电极;其中,所述第一管芯和所述第二管芯位于同一封装体中。

为了解决上述技术问题,本发明提供了一种上述半导体器件的制备方法,其中包括:

提供第一管芯,其包括第一区域和第二区域,所述第一区域为所述第一管芯的功能区,其中包括由III-V族半导体层构成的第一异质结和多个第一电极,所述多个第一电极中的部分第一电极与所述第一异质结耦合;

在所述第一管芯的所述第二区域的上方提供第二管芯,所述第二管芯包括多个第二电极;以及

提供第一导电层用以电连接所述多个第一电极中的部分第一电极和多个第二电极中的部分第二电极;

其中,所述第一管芯和所述第二管芯在同一封装体中。

为了解决上述技术问题,本发明还提供了一种半导体器件,其包括:

第一管芯,其包括第一区域和第二区域,所述第一区域为所述第一管芯的功能区;以及

第二管芯,所述第二管芯位于所述第一管芯的第二区域的上方,所述第一管芯与所述第二管芯通过第一导电层电连接;以及

散热结构,所述散热结构与所述第二管芯具有导热接触;

其中,所述第一管芯和所述第二管芯位于同一封装体中。

为了解决上述技术问题,本发明还提供了一种上述半导体器件的制备方法,其中包括:

提供第一管芯,其包括第一区域和第二区域,所述第一区域为所述第一管芯的功能区;

在所述第一管芯的所述第二区域的上方提供第二管芯;

提供第一导电层用以电连接所述第一管芯与所述第二管芯;以及

提供散热结构,所述散热结构与所述第二管芯具有导热接触;

其中,所述第一管芯和所述第二管芯在同一封装体中。

为了解决上述技术问题,本发明还提供了一种共源共栅级联功率器件,其管芯结构包括:

耗尽型GaN管芯,其包括有源区和无源区,其中所述有源区包括由III-V族半导体层构成的第一异质结及HEMT源极、HEMT栅极和HEMT漏极,所述HEMT源极和HEMT漏极与所述第一异质结耦合;以及

增强型MOSFET管芯,其包括MOSFET漏极、MOSFET源和极MOSFET栅极,所述增强型MOSFET管芯位于所述无源区上方;

其中,所述HEMT源极与所述MOSFET漏极通过第一导电层电连接;所述耗尽型GaN管芯和所述增强型MOSFET管芯位于同一封装体中。

为了解决上述技术问题,本发明还提供了一种共源共栅级联功率器件的制备方法,包括以下步骤:

提供耗尽型GaN管芯,其包括有源区和无源区,其中所述有源区包括由III-V族半导体层构成的第一异质结及HEMT源极、HEMT栅极和HEMT漏极,所述HEMT源极和HEMT漏极与所述第一异质结耦合;

在所述耗尽型GaN管芯的所述无源区的上方提供增强型MOSFET管芯;以及

在所述耗尽型GaN管芯的有源区提供延伸到所述无源区的第一导电层,至少用以电连接所述HEMT源极和增强型MOSFET管芯的MOSFET漏极;

其中,所述耗尽型GaN管芯和所述增强型MOSFET管芯位于在同一封装体中。

为了解决上述技术问题,本发明还提供了一种驱动合封功率器件,其管芯结构包括:

GaN管芯,其包括第一区域和第二区域,所述第一区域中制备有HEMT的源极、栅极和漏极;

控制管芯,其位于所述第二区域上方,包括驱动电路或其一部分,所述控制管芯至少包括驱动输入端和驱动输出端;以及

导电层,其至少在所述第一区域电连接所述HEMT的栅极,并延伸到所述第二区域电连接所述驱动输出端;

其中,所述GaN管芯和所述控制管芯位于同一封装体中。

为了解决上述技术问题,本发明还提供了一种上述驱动合封功率器件的制备方法,其中包括:

提供GaN管芯,其包括第一区域和第二区域,所述第一区域中形成有HEMT,其包括栅极、源极和漏极;

在所述GaN管芯的所述第二区域上方提供控制管芯,其包括驱动电路或其一部分,所述控制管芯至少包括驱动输入端和驱动输出端;以及

提供导电层,其在所述第一区域电连接所述HEMT的栅极,并延伸到所述第二区域电连接所述驱动输出端;

其中,所述GaN管芯和所述控制管芯位于同一封装体中。

本发明提供的半导体器件的第一管芯通过第二区域为第二管芯提供了支撑平台,能够有效地减小两个管芯的距离,并且使两个管芯的电连接由现有技术中的打线方式改为通过导电层电连接的方式,因而既减小了封装尺寸,也减小了因增加额外材料及引线而引起的寄生参数,两个管芯有各自的散热路径,互不影响,因而整体器件的散热特性好。

附图说明

下面,将结合附图对本发明的优选实施方式进行进一步详细的说明,其中:

图1是公告号为CN 218160367 U、名称为“Cascode封装结构”的中国发明专利公开的一种Cascode封装结构示意图;

图2是公告号为US8847408B2、名称为“封装中堆叠有FET的Ⅲ族氮化物晶体管”的美国专利公开的一种封装结构示意图;

图3是根据本发明实施例一的一种共源共栅级联功率器件的原理电路图;

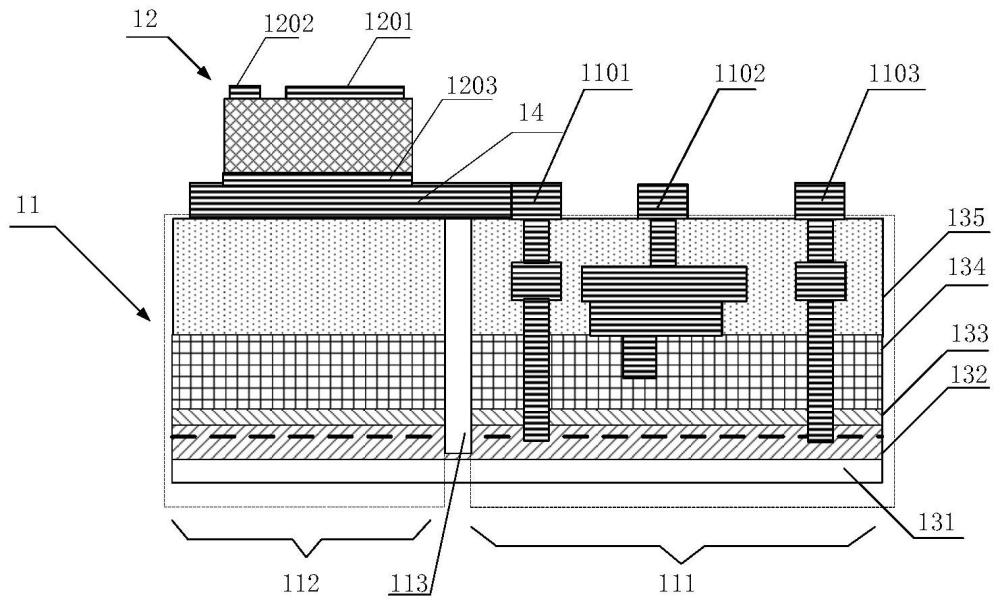

图4是根据本发明实施例一的一种Cascode器件管芯结构的侧面示意图;

图5是根据本发明实施例一的一种Cascode器件管芯结构的正面示意图;

图6是根据本发明实施例一的Cascode器件封装结构示意图;

图6A是根据本发明实施例一的Cascode器件的制备方法流程图;

图7是根据本发明实施例二的一种Cascode器件的原理电路图;

图8是根据本发明实施例二的一种Cascode器件管芯结构的侧面示意图;

图9是图8所示的Cascode器件管芯结构的另一个侧面示意图;

图10是根据本发明实施例二的Cascode器件管芯结构的另一个侧面示意图;

图11是根据本发明实施例二的Cascode器件封装结构示意图;

图12是根据本发明实施例三的一种Cascode器件结构的侧面示意图;

图12A是根据本发明实施例三的一种Cascode器件的制备方法流程图;

图13是根据本发明实施例四的一种Cascode器件管芯结构的侧面示意图;

图14是根据本发明实施例五的一种Cascode器件结构的侧面示意图;

图15是根据本发明实施例六的一种Cascode器件结构的侧面示意图;

图16是根据本发明实施例七的一种Cascode器件结构的侧面示意图;

图17是根据本发明实施例八的一种驱动合封功率器件的原理电路图;

图18是根据本发明实施例八的一种驱动合封功率器件管芯结构的侧面示意图;

图19是根据本发明实施例八的一种驱动合封功率器件封装主体结构的正面示意图;

图19A根据本发明实施例八的一种驱动合封功率器件制备方法流程图;

图20是根据本发明实施例九的一种驱动合封功率器件封装主体结构的正面示意图;

图21是根据本发明实施例十的一种驱动合封功率器件管芯结构侧面示意图;

图22是根据本发明实施例十一的一种驱动合封功率器件管芯结构侧面示意图;

图23是根据本发明实施例十二的一种驱动合封功率器件管芯结构的侧面示意图;以及

图24是根据本发明实施例十二的一种驱动合封功率器件封装主体结构的正面示意图。

具体实施方式

为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

在以下的详细描述中,可以参看作为本申请一部分用来说明本申请的特定实施例的各个说明书附图。在附图中,相似的附图标记在不同图式中描述大体上类似的组件。本申请的各个特定实施例在以下进行了足够详细的描述,使得具备本领域相关知识和技术的普通技术人员能够实施本申请的技术方案。应当理解,还可以利用其它实施例或者对本申请的实施例进行结构、逻辑或者电性的改变。

本发明提供了一种半导体器件,其包括第一管芯、第二管芯和将两个管芯封装的封装体。第一管芯包括第一区域和第二区域,所述第一区域为所述第一管芯的功能区,用于得到第一管芯的具体结构。所述第二管芯位于所述第一管芯的第二区域的上方,所述第一管芯与所述第二管芯通过导电层电连接。本发明的第一管芯为第二管芯提供了支撑平台,能够有效地减小两个管芯的距离,并且使两个管芯的电连接由现有技术中的打线方式改为通过导电层电连接,因而既减小了封装尺寸,也减小了因增加额外材料及引线而引起的寄生参数,两个管芯有各自的散热路径,互不影响,因而整体器件的散热特性好。当第一管芯和第二管芯分别为耗尽型GaN管芯和增强型MOSFET管芯时构成了Cascode器件,当第一管芯和第二管芯分别为GaN管芯和控制管芯或控制芯片时构成了驱动合封功率器件。以下通过具体实施例对本发明提供的半导体器件进行详细说明。

实施例一

图3是根据本发明实施例一的一种共源共栅级联功率器件(简称Cascode器件)的原理电路图,图4是根据本发明实施例一的一种Cascode器件管芯结构的侧面示意图。图5是根据本发明实施例一的一种Cascode器件管芯结构的正面示意图。其中,图4及图5中所示的各个结构的形状、比例、布局等仅是一种示意,本领域的技术人员可根据实际需求作出适应性地调整。结合图3至图5,所述Cascode器件封装主体结构包括作为第一管芯的耗尽型GaN管芯11、作为第二管芯的增强型MOSFET管芯12和封装体(图中未示出)。所述耗尽型GaN管芯11包括衬底131及外延得到的沟道层132和势垒层133、第一介质层134和第二介质层135,第一介质层134和第二介质层135构成了介质层。

其中,所述衬底131的材料例如为本征GaN或诸如硅(Si)、碳化硅(SiC)或蓝宝石(Al

所述沟道层132的材料例如为GaN,所述势垒层133的材料例如为AlGaN,沟道层132和势垒层133构成了异质结,其中提供有二维载流子气310,如二维电子气(2DEG)或二维空穴气(2DHG)。构成异质结的所述沟道层132和所述势垒层133的材料还可以是其他III-V族半导体材料,如AlN、GaN、InN及这些材料的化合物,如AlGaN、InGaN、AlInGaN等。

耗尽型GaN管芯11包括两个区域,如图中所示的有源区111和无源区112。有源区111和无源区112之间具有隔离区113,所述的隔离区113例如为使有源区111和无源区112在物理上实现分离填充了介质的隔离槽,也可以通过在该区域从顶层向下注入绝缘离子得到的电绝缘带。

有源区111作为第一区域,其为耗尽型GaN管芯11的功能区,通过对有源区111刻蚀、生长金属进而得到HEMT源极1101、HEMT栅极1102和HEMT漏极1103。其中的HEMT源极1101和HEMT漏极1103分别与异质结耦合。在有源区111上表面沉积有导电层14,所述导电层14与HEMT源极1101电连接,并向无源区112延伸。其中,导电层14可覆盖所述无源区112的部分区域或全部区域。通过控制导电层14的厚度和面积能够减小所述第一管芯与所述第二管芯之间互连结构的寄生参数,如寄生电阻和寄生电感。

所述增强型MOSFET管芯12例如为MOSFET晶体管,其包括MOSFET源极1201、MOSFET栅极1202和MOSFET漏极1203。在本实施例中,MOSFET漏极1203位于增强型MOSFET管芯12的下方,MOSFET源极1201、MOSFET栅极1202位于增强型MOSFET管芯12的上方,所述增强型MOSFET管芯12的MOSFET漏极1203贴装在所述无源区112上方的导电层14上,从而实现MOSFET漏极1203与HEMT源极1101的电连接。在将所述增强型MOSFET管芯12的MOSFET漏极1203贴装在所述无源区112上方的导电层14时,可以通过共晶粘贴法、焊接粘贴法、导电胶粘贴法和玻璃胶粘贴法等方法实现。

图6是根据本发明实施例一的Cascode器件封装结构示意图(图中未示出封装体),在本实施例中,耗尽型GaN管芯11贴装在引线框架15上,并通过引线16进行互联。如图中所示,通过引线16将MOSFET栅极1202引到框架的第一引脚151作为所述Cascode器件的栅极G,通过引线16将HEMT栅极1102、MOSFET源极1201与框架主体153电连接,并作为所述Cascode器件的源极S,通过引线16将HEMT漏极1103引到框架的第二引脚152作为所述Cascode器件的漏极D。图6中的引线16仅为示意,根据需要,同一连接关系的引线16可以为一根或多根,也可以为符合电流参数的金属带。而后可参考本领域常用的工艺完成Cascode器件的其他工艺步骤进而完成Cascode器件的制备,在图6所示的结构的基础上进行塑封得到封装体,进而得到完整的带有引脚的Cascode器件,在此不再赘述。

综合图3至图6可见,本实施例中的耗尽型GaN管芯11作为第一管芯,其提供了作为第一区域的有源区111和作为第二区域的无源区112,耗尽型GaN管芯11在有源区111包括由III-V族半导体层构成的第一异质结和多个电极。第二区域的无源区112为增强型MOSFET管芯12提供了支撑平台,使增强型MOSFET管芯12位于作为第二区域的无源区112上方,其底层的漏极通过导电层与GaN源极电连接,与通过引线电连接的方式相比,既有效减小了两个管芯的距离,也减小了两个电极之间由于巨大压差对MOSFET管芯12产生的冲击及寄生参数。本实施例中的增强型MOSFET管芯12直接置于GaN管芯11上,不需要现有技术中的基板,既进一步减少了两个管芯的距离及寄生参数,也减小了器件的整体封装体积,并且两个管芯有各自的散热路径,互不影响,因而整体器件的散热特性好。

本实施例中的耗尽型GaN管芯11根据实际需要还可以包括其他半导体层,如在第二介质层135上层再增加一层钝化层以提供保护,或者在势垒层133和第一介质层134之间增加一层帽层,以保护势垒层133,还可以在衬底层131中增加成核层等等。

图6A是根据本发明实施例一的Cascode器件的制备方法流程图,其中包括以下步骤:

步骤S11,提供管芯结构。其中,提供管芯结构的步骤具体包括:

步骤S111,提供耗尽型GaN管芯11,其包括有源区111和无源区112,所述源区111为所述耗尽型GaN管芯11的功能区。例如,首先选择衬底131,衬底131的材料例如为本征GaN或非本征GaN。而后在衬底131上依次外延得到沟道层132和势垒层133。继续在势垒层133上沉积介质,如得到第一介质层134作为栅极介质。而后制作栅极场板、源极和漏极。然后再沉积第二介质层135,并将栅极、源极和漏极引出到第二介质层135上表面,进而得到HEMT源极1101、HEMT栅极1102和HEMT漏极1103。

步骤S112,在有源区111上沉积导电层14,并使导电层14延伸、覆盖所述无源区112的部分区域,且在有源区111与HEMT源极1101电连接。

步骤S113,在所述无源区112的导电层14上方提供增强型MOSFET管芯12。例如以通过共晶粘贴法、焊接粘贴法、导电胶粘贴法和玻璃胶粘贴法等方法将所述增强型MOSFET管芯12的MOSFET漏极1203贴装在所述无源区112上方的导电层14。

步骤S12,提供引线框15并进行器件互联。例如,将耗尽型GaN管芯11贴装在引线框架15上,再根据需要采用引线16进行互联。

步骤S13,塑封。采用塑封料对完成器件互联的结构进行塑封,进而得到完整的带有引脚的Cascode器件。

实施例二

图7是根据本发明实施例二的一种Cascode器件的原理电路图,图8是根据本发明实施例二的一种Cascode器件管芯结构的侧面示意图。图9是图8所示的Cascode器件管芯结构的另一个侧面示意图。与实施例一相比,本实施例在耗尽型GaN管芯11的无源区112内置有一个电容31。其中,耗尽型GaN管芯11中形成的异质结由隔离区113分为两部分,第一异质结在作为第一区域的有源区111中与HEMT源极1101和HEMT漏极1103耦合,第二异质结在作为第二区域的无源区112中,第二异质结形成了一个导电平面,其作为电容31的下极板,通过金属312引到无源区112的上表面,并与上表面的作为下电极313的第二导电层电连接。本实施例利用导电层14作为电容31的上极板,同时也是电容上电极,与MOSFET漏极1203直接电连接,既充分利用了导电层,还减少了器件互联引起的寄生参数。

参见图11,图11是根据本发明实施例二的Cascode器件封装结构示意图。与图6所示的结构相比,本实施例的无源区112上表面包括电容的下电极313,在器件互联工艺中,通过引线16连接下电极313和HEMT栅极1102、MOSFET源极1201或框架主体153,从而实现如图7所示原理图中的电容连接关系。

由于耗尽型GaN管芯11的无源区112具有足够的位置,因而可以在无源区112实现一些无源器件,如本实施例中的电容31,当然也可以实现其他的无源器件,如图10所示的电阻32,图10是根据本发明实施二所示的Cascode器件管芯结构的另一个侧面示意图。电阻32置于无源区112内,其两个连接端分别通过金属引出到无源区112上表面,第一连接端与导电层14电连接,进而与MOSFET漏极1203直接电连接,第二连接端与无源区112上表面的第二导电层321电连接。在Cascode器件封装结构的器件互联工艺中,第二导电层321通过引线16与HEMT栅极1102、MOSFET源极1201或框架主体153电连接,从而实现在MOSFET11的漏源两极之间增加电阻的目的。在无源区112增加的无源器件还可以是二极管或电感,或者是这些无源器件的各种组合,在此不再一一赘述。

前述两个实施例提供的结构仅是一种示意,需要说明的是,实施例一和实施例二中的无源区112中也可以不包括异质结,当在实施例二中不包括异质结时,可以通过在距离无源区112上表面一定距离的位置沉积金属得到的金属层作为电容31的下极板。

在制备本实施例中的Cascode器件过程中,在图6A所示的流程中,在完成步骤S111的过程中制备无源区112中的无源器件。例如,针对图8和图9所示的电容31,在将栅极、源极和漏极引出到第二介质层135上表面的同时,从第二介质层135上表面向下刻蚀直到第二异质结310,再通过生长金属312将第二异质结310形成的导电平面作为电容31下极板,并引到无源区112的上表面,在无源区112的上表面沉积金属层作为电容31的下电极313。类似地可以得到电阻、二极管、电感等无源器件。

实施例三

图12是根据本发明实施例三的一种Cascode器件结构的侧面示意图。在本实施例中,所述Cascode器件的管芯结构包括作为第一管芯的增强型MOSFET管芯12和作为第二管芯的耗尽型GaN管芯11。所述增强型MOSFET管芯12包括第一区域121和第二区域122,所述第一区域121为所述增强型MOSFET管芯12的功能区,其中形成有MOSFET源极1201、MOSFET栅极1202和MOSFET漏极1203。作为第二管芯的耗尽型GaN管芯11包括耗尽型GaN管芯11和HEMT源极1101、HEMT栅极1102和HEMT漏极1103。增强型MOSFET管芯12的上表面沉积有导电层14,其与MOSFET漏极1203电连接在一起并延伸到第二区域122,并与耗尽型GaN管芯11的HEMT源极1101电连接。在本实施例中,通过贴装的方式将耗尽型GaN管芯11置于所述第二区域122,HEMT源极1101完全贴装在导电层14上,既提高了贴装的牢固性,也增加了电接触面积。为了提高耗尽型GaN管芯11的散热,将所述耗尽型GaN管芯11和增强型MOSFET管芯12倒置,且所述耗尽型GaN管芯11的上表面贴装在所述引线框架15上,通过引线框架15实现对耗尽型GaN管芯11的散热。而后再通过封装材料进行塑封得到封装体17。

本领域的普通技术人员应知,本实施例在对所述耗尽型GaN管芯11和增强型MOSFET管芯12进行倒置封装时,还可以包括倒置封装时所需、本实施例未提及的其他材料或制程,例如,采用焊料或导电粘合剂将耗尽型GaN管芯11贴装在所述引线框架15上。焊料可采用共晶锡/铅或无铅(98.2%锡、1.8%银)焊料。在焊接完成之后,对管芯和引线框架之间的空隙进行填充,填充料例如为经过专门工程处理的环氧树脂。经过管芯贴装和填充步骤以外,还包括其他处理步骤,如对晶片四周进行封装得到所需要各种规格的封装结构,在此不再赘述。

另外,虽然本实施例中以引线框架作为管芯倒装封装时的载体,但并不排除其载体,如基板,具体以实际制备需求而定。

另外,第二区域122中也可以制备无源器件,如电阻、电容、二极管、电感等,其结构及与耗尽型GaN管芯11和增强型MOSFET管芯12的连接关系与实施例二中类似,例如,以导电层14作为一个电容极板,在第二区域122内部形成的金属板作为第二电容极板,并将其引出到第二区域122表面,用于进行互联,在此不再赘述。

图12A是根据本发明实施例三的一种Cascode器件的制备方法流程图,其中包括以下步骤:

步骤S21,提供管芯结构。其中,提供管芯结构的步骤具体包括:

步骤S211,提供增强型MOSFET管芯12,其包括第一区域121和第二区域122,所述第一区域121为所述增强型MOSFET管芯12的功能区,其中形成有MOSFET源极1201、MOSFET栅极1202和MOSFET漏极1203。

步骤S212,在第一区域121上沉积导电层14,与MOSFET漏极1203电连接在一起并延伸到第二区域122。

步骤S213,在所述第二区域122的导电层14上方以贴装的方式将耗尽型GaN管芯11置于所述第二区域122,HEMT源极1101完全贴装在导电层14上。

步骤S22,将管芯结构倒置贴装在引线框架15上并进行器件互联。具体地,所述耗尽型GaN管芯11的上表面贴装在所述引线框架15上,从而可以实现通过引线框架15散热的目的。

步骤S23,塑封。采用塑封料对完成器件互联的结构进行塑封,进而得到完整的带有引脚的Cascode器件。

实施例四

图13是根据本发明实施例四的一种Cascode器件管芯结构的侧面示意图。在本实施例中,与实施例一相比,在向无源区112贴装增强型MOSFET管芯12之前,对无源区112进行刻蚀,刻蚀深度可根据实际情况确定。在本实施例中,刻蚀深度以将增强型MOSFET管芯12贴装在无源区112上的导电层14后的高度与有源区111的电极高度相当为准,如图13所示。通过对无源区112的刻蚀,减小无源区112的厚度,从而缩短MOSFET管芯12的散热路径,提高了器件的整体散热性能。

在制备本实施例中的Cascode器件过程中,参照图6A所示的流程,在得到耗尽型GaN管芯11后,对无源区112进行刻蚀,而后再执行其他步骤,从而得到本实施例中的Cascode器件。

实施例五

图14是根据本发明实施例五的一种Cascode器件结构的侧面示意图。参见图14,在本实施例中,所述Cascode器件的管芯结构包括作为第一管芯的增强型MOSFET管芯12和作为第二管芯的耗尽型GaN管芯11。在向增强型MOSFET管芯12的无源区贴装耗尽型GaN管芯11之前,对贴装的第二区域122进行刻蚀,而后再沉积导电层14,使导电层14电连接MOSFET漏极1203,并延伸到第二区域122,而后再通过贴装的方式将耗尽型GaN管芯11置于所述第二区域122。耗尽型GaN管芯11的下表面包括多个HEMT源极1101,其完全贴装在导电层14上,既提高了贴装的牢固性,也增加了电接触面积。增强型MOSFET管芯12贴装在引线框架15上,并通过塑封料进行塑封得到封装体17。本实施例通过减小第二区域122的厚度缩短了耗尽型GaN管芯11的散热路径,并由引线框架13对耗尽型GaN管芯11散热。

在制备本实施例中的Cascode器件过程中,参照图12A所示的流程,在得到增强型MOSFET管芯12后,对第二区域122进行刻蚀,而后再执行其他步骤,从而得到本实施例中的Cascode器件。

实施例六

图15是根据本发明实施例六的一种Cascode器件结构的侧面示意图。本实施例与实施例五相比,在第二区域122中还包括多个散热孔1220,内注有散热材料,所述散热孔1220与所述引线框架15相接触。本实施例通过在第二区域中增加散热孔进一步提高散热性能。

类似地,还可以在图4、图13等所示实施例中增加散热孔来提高对第二管芯的散热能力。具体结构可参考图15,在此不再赘述。

在制备本实施例中的Cascode器件过程中,参照图12A所示的流程,在得到增强型MOSFET管芯12后,对第二区域122进行刻蚀以减小第二区域122的厚度,而后再刻蚀散热孔1220,并向其中填加散热材料,而后再执行其他步骤,从而得到本实施例中的Cascode器件。

实施例七

图16是根据本发明实施例七的一种Cascode器件结构的侧面示意图。在本实施例中,所述Cascode器件的管芯结构包括作为第一管芯的增强型MOSFET管芯12和作为第二管芯的耗尽型GaN管芯11。在增强型MOSFET管芯12的第一区域121沉积导电层14,导电层14与MOSFET漏极1203(参见图12)电连接并延伸到第二区域122,而后再通过贴装的方式将耗尽型GaN管芯11置于所述第二区域122。耗尽型GaN管芯11的下表面包括HEMT源极1101(参见图12),其完全贴装在导电层14上,既提高了贴装的牢固性,也增加了电接触面积。增强型MOSFET管芯12贴装在引线框架15上,并通过塑封料进行塑封得到封装体17。在本实施例中,为了实现对耗尽型GaN管芯11的散热,在其上表面设置导热件18,其粘结面通过绝缘导热胶与所述对耗尽型GaN管芯11的表面粘接在一起,其散热面露出所述封装体17。所述的导热件18例如为导热性能良好的金属件。另外,还可以在本实施例的基础上结合以上实施五或实施六的结构,从而进一步提高散热性能。

在制备本实施例中的Cascode器件过程中,参照图12A所示的流程,在完成步骤S11b得到管芯结构后,将增强型MOSFET管芯12的下表面贴装在引线框架15上。然后在耗尽型GaN管芯11主体上表面通过绝缘导热胶粘接导热件18,而后通过塑封料进行塑封得到封装体17,其中在塑封时保证导热件18的散热面露出所述封装体17。

另外,在前述作为第一管芯的增强型MOSFET管芯12的无源区上贴装作为第二管芯的耗尽型GaN管芯11的各个实施例中,所述耗尽型GaN管芯11源极与增强型MOSFET漏极通过导电层连接,另外,也可以根据需要采用另一个导电层的对其他电极进行互联,如耗尽型GaN管芯11栅极与增强型MOSFET的源极电极通过另一导电层电连接。其中,耗尽型GaN管芯11的电极可全部置于一侧,如上表面,也可以分置于两侧,如分置于上表面和下表面。根据互联需要,在贴装耗尽型GaN管芯11时,可以使耗尽型GaN管芯11的上表面贴装在增强型MOSFET管芯12的无源区上,也可以使耗尽型GaN管芯11下表面贴装在增强型MOSFET管芯12的无源区上。

实施例八

图17是根据本发明实施例八的一种驱动合封功率器件的原理电路图,图18是根据本发明实施例八的一种驱动合封功率器件管芯结构的侧面示意图。图19是根据本发明实施例八的一种驱动合封功率器件封装主体结构的正面示意图。在本实施例八中,所述的驱动合封功率器件包括GaN管芯21和控制管芯22,在本实施例中,所述的GaN管芯21包括第一区域211和第二区域212,在所述第一区域211中形成有增强型HEMT的三个电极,即HEMT源极2101、HEMT栅极2102和HEMT漏极2103。控制管芯22包括驱动电路或其一部分,在本实施例中,控制管芯22包括驱动输入端2201、驱动输出端2202、电源端2203和接地端2204,驱动输出端2202与HEMT栅极2102电连接,接地端2204与HEMT源极2101电连接。

参见图18和图19,控制管芯22置于GaN管芯21的第二区域212上方。所述GaN管芯21包括衬底231及外延得到的沟道层232和势垒层233、第一介质层234和第二介质层235及位于第一区域211中势垒层233上方的P-型层236。在本实施例中,所述衬底231的材料例如为本征GaN或诸如Si、SiC或Al

所述沟道层232的材料例如为GaN,所述势垒层233的材料例如为AlGaN,沟道层232和势垒层233的界面构成了异质结,其中提供有二维载流子气,如二维电子气(2DEG)或二维空穴气(2DHG)。构成异质结的所述沟道层232和所述势垒层233的材料还可以是其他III-V族半导体材料,如AlN、GaN、InN及这些材料的化合物如AlGaN、InGaN、AlInGaN等。通过对第一区域211的半导体层进行刻蚀、生长金属进而得到HEMT源极2101和HEMT漏极2103,并与势垒层233下的异质结耦合。第一区域的势垒层233上方的P-型层236为带正电(P型)的GaN层,P-型层236中的正电荷具有内置电压,该电压大于压电效应产生的电压,因此会耗尽2DEG中的电子而形成增强型结构。在P-型层236上形成栅极并引出到管芯表面得到HEMT栅极2102。

GaN管芯21的第一区域211上表面沉积有导电层24,其中源极导电层241与HEMT源极2101电连接,栅极导电层242与HEMT栅极2102电连接,源极导电层241和栅极导电层242相互隔离并向第二区域212延伸。其中与HEMT源极2101电连接的源极导电层241与接地端2204电连接,与HEMT栅极2102电连接的栅极导电层242与驱动输出端2202电连接。GaN管芯21置于引线框架25上,通过引线26对HEMT电极、控制管芯的各个电连接端及引线框架25等进行互联,且引线框架25上包括有多个用于引出的引脚251。本实施例中的引线框架25的结构、连接点及数量可根据实际需要而定,本实施例中的引脚251的布局及数量仅用于示例,而非限制。

在本实施例中,GaN管芯21包括第一区域和第二区域,在第一区域形成增强型HEMT,并包括HEMT的三个电极,在第二区域上贴装控制管芯,并通过在GaN管芯21沉积导电层来电连接控制管芯的驱动输出端和HEMT栅极、控制管芯的接地端和HEMT源极。两个管芯是否通过导电层连接可根据控制管芯中具体驱动电路及与外部电路连接的需要而定,本实施例中的电连接关系仅是举例而已,两个管芯通过导电层进行连接的关系并不局限于本实施例。由于控制管芯22贴装在GaN管芯21上,并且两个管芯在电连接时可以通过导电层电连接,相对于并列式布局、采用引线互联的结构,不但能够减小器件的整体体积,而且通过控制导电层的厚度和面积还能够有效减小两个管芯之间互连是产生的寄生参数,如寄生电阻和寄生电感。

图19中的引线26仅为示意,根据需要,同一连接关系的引线26可以为一根或多根,也可以为符合电流参数的金属带。而后可参考本领域常用的工艺完成器件的其他工艺步骤,如在图19所示的结构的基础上进行塑封得到封装体,进而得到完整的带有引脚的驱动合封功率器件,在此不再赘述。

图19A根据本发明实施例八的一种驱动合封功率器件制备方法流程图,所述方法包括:

步骤S31,提供管芯结构。其中,提供管芯结构的步骤具体包括:

步骤S311,提供GaN管芯21,其包括第一区域211和第二区域212,所述第一区域211为所述GaN管芯21的功能区。在本实施例中,所述GaN管芯21中形成有增强型HEMT。例如,首先选择衬底231,衬底231的材料例如为本征GaN或非本征GaN。而后在衬底231上依次外延得到沟道层232和势垒层233。继续在势垒层233上沉积P-型层236,而后沉积第一介质层234作为栅极介质。而后制作栅极场板、源极和漏极。然后再沉积第二介质层235,并将栅极、源极和漏极引出到第二介质层235上表面,进而得到HEMT源极2101、HEMT栅极2102和HEMT漏极2103。

步骤S312,在第一区域211上沉积导电层24。其中所述导电层24包括源极导电层241和栅极导电层242,所述源极导电层241与HEMT源极2101电连接,栅极导电层242与HEMT栅极2102电连接,源极导电层241和栅极导电层242相互隔离并延伸到第二区域212。

步骤S313,在所述第二区域212的导电层24上方提供控制管芯22。例如以通过共晶粘贴法、焊接粘贴法、导电胶粘贴法和玻璃胶粘贴法等方法使控制管芯22的接地端2204与所述源极导电层241电连接,控制管芯22的驱动输出端2202与栅极导电层242电连接。

步骤S32,提供引线框25并进行器件互联。例如,将GaN管芯21的主体下表面贴装在引线框架25上,再根据需要采用引线26进行互联。

步骤S33,塑封。采用塑封料对完成器件互联的结构进行塑封,进而得到完整的带有引脚的驱动合封功率器件。

实施例九

图20是根据本发明实施例九的一种驱动合封功率器件封装主体结构的正面示意图。与实施例八相比,在本实施例九中,所述的驱动合封功率器件的GaN管芯21包括第一区域211和第二区域212。第一区域211包括两个增强型HEMT结构,如图20中的HEMT 1和HEMT2,控制管芯22中的驱动电路包括两个驱动输入端和两个驱动输出端。HEMT与控制管芯22的电连接与实施例八相同,如驱动输出端2202通过导电层与HEMT栅极2102电连接,接地端2204通过导电层与HEMT源极2101电连接。其中,为了充分利用GaN管芯21表面积并达到良好的电接触,驱动输出端2202和接地端2204位于控制管芯22的下方,与HEMT源极2101电连接的导电层延伸到第二区域212,与HEMT栅极2102电连接的导电层延伸到第二区域212,当将控制管芯22置于第二区域212时,驱动输出端2202和接地端2204分别置于对应的导电层上方,如图中虚线所示,通过设置接触面的面积及对应导电层的厚度能够达到减小互联产生的寄生参数。HEMT 2与控制管芯22的连接及位置关系与HEMT 1与控制管芯22的连接及位置关系相同,在此不再赘述。

对图20所示的结构填充塑封料进行塑封得到的封装体,从而得到一个封装完整的驱动合封功率器件。本实施例中的引线框架25的结构、连接点、引脚251布局及数量可根据实施需要而定,本实施例仅用于示例,而非限制。

虽然本实施例中的GaN管芯21的第一区域211中包括两个增强型HEMT结构,但是并不限制更多数量的HEMT结构,多个HEMT结构既可以都是增强型HEMT结构,也可以都是耗尽型HEMT结构,或者这两种结构并存。

在制备本实施例中的驱动合封功率器件时,参考图19A所示的流程,其中在制备GaN管芯21时生成两个增强型HEMT,当需要多个HEMT结构及相应的类型时,按照预置的布局及预置类型对应的结构生成相应的GaN管芯结构,其生成过程与前述实施例相类似,在此不再赘述。

实施例十

图21是根据本发明实施例十的一种驱动合封功率器件管芯结构侧面示意图。与实施例八相比,在向第二区域212贴装控制管芯22之前,对第二区域212进行刻蚀,刻蚀深度可根据实际情况确定。在本实施例中,刻蚀深度以将控制管芯22贴装在第二区域212上的导电层24后的高度与第一区域211的电极高度相当为准,如图21所示。通过对第二区域212的刻蚀,减小第二区域212的厚度,从而缩短控制管芯22到引线框架25的散热路径,提高了器件的整体散热性能。

本实施例中的驱动合封功率器件的制备方法参考图19A的流程,与图19A的不同在于在得到管芯结构后对第二区域212进行刻蚀以减小第二区域212的厚度,而后再提供导电层24,再提供控制管芯22等后续步骤。

实施例十一

图22是根据本发明实施例十一的一种驱动合封功率器件封装主体结构侧面示意图。本实施例与实施例十相比,在第二区域212中还包括多个散热孔2120,内注有散热材料,所述散热孔2120与所述引线框架25相接触。本实施例通过在第二区域212中增加散热孔进一步提高散热性能。

类似地,还可以在图18、图20等所示实施例中增加散热孔来提高对控制管芯的散热能力。具体结构可参考图22,在此不再赘述。

本实施例中的驱动合封功率器件的制备方法参考图19A的流程,与图19A的不同在于在得到管芯结构后对第二区域212进行刻蚀以减小无源区212的厚度,而后再刻蚀散热孔2120,并向其中填加散热材料,而后再执行其他步骤。

实施例十二

图23是根据本发明实施例十二的一种驱动合封功率器件管芯结构的侧面示意图(仅示出部分结构)。图24是根据本发明实施例十二的一种驱动合封功率器件封装主体结构的正面示意图。在本实施例中,控制管芯22包括第一区域221和第二区域222,GaN管芯21HEMT结构,并在其底侧包括HEMT源极2101、HEMT栅极2102和HEMT漏极2103。控制管芯22的第一区域221包括驱动电路或其一部分,控制管芯22包括驱动输入端2201、驱动输出端2202、电源端2203和接地端2204。本实施例共有3个分离的导电层,即源极导电层241、栅极导电层242和漏极导电层243,其中,源极导电层241在第一区域221与接地端2204电连接,并向第二区域222延伸。栅极导电层242在第一区域221与驱动输出端2202电连接。漏极导电层243在第二区域的边缘,用于与导线框加中的漏极管脚251电连接。GaN管芯21置于控制管芯22的第二区域222,底部的HEMT源极2101置于源极导电层241上,底部的HEMT栅极2102置于栅极导电层242上,HEMT漏极2103置于漏极导电层243,从而实现了控制管芯22的驱动输出端2202与GaN管芯21的HEMT栅极2102电连接,控制管芯22的接地端2204与GaN管芯21的HEMT源极2101电连接。

本实施例中的驱动合封功率器件的制备方法参考图19A的流程,与图19A所述流程不同在于,在原步骤S31提供管芯结构时,首先提供控制管芯,包括第一区域和第二区域,所述第一区域中包括驱动电路或其一部分,所述控制管芯至少包括驱动输入端和驱动输出端;而后在所述第一区域提供导电层,导电层与驱动输出端电连接并延伸到所述第二区域;然后在所述控制管芯的所述第二区域上方提供GaN管芯,所述GaN管芯包括HEMT的源极、栅极和漏极,至少其漏极与导电层电连接,从而使所述驱动输出端电连接到所述HEMT的栅极。而后步骤与图19A相同,不再赘述。

本发明前述实施例提供的驱动合封功率器件中的控制管芯仅是为了描述方便将其命名为控制管芯,虽然前述实施例中只提及了部分端子,本领域的普通技术人员可知根据控制需要,还可以包括其他的电连接端、电路元件。例如控制管芯的驱动输入端用于连接到外接的输入信号源,驱动输出端连接到HEMT栅极。控制管芯中包括电容器,其连接电源端VCC和输出侧的接地端之间,用于去耦和滤波。控制管芯中还包括电阻,其连接在驱动输出端和HEMT的栅极之间,用于调节栅极驱动的上升沿和下降沿。控制管芯中还包括反并联二极管,其连接在驱动输出端和输出侧的接地端之间,用于提供米勒电流的旁路。HEMT的漏极用于连接到负载电路。因而控制管芯可以是业界常称的“GaN控制芯片”或“GaN控制IC”,可以为现有的芯片,也可以是根据需要定制的芯片,本领域的普通技术人员可以参考现有技术中的GaN驱动电路或控制电路,在此不再赘述。

综上所述,本发明提供的半导体器件可以根据需要构成多种不同功能的器件,应用范围广、体积小、寄生参数少。

上述实施例仅供说明本发明之用,而并非是对本发明的限制,有关技术领域的普通技术人员,在不脱离本发明范围的情况下,还可以做出各种变化和变型,因此,所有等同的技术方案也应属于本发明公开的范畴。