一种低压低漏电瞬态电压抑制器及其制备方法

文献发布时间:2024-01-17 01:28:27

技术领域

本发明涉及TVS领域,尤其涉及一种低压低漏电瞬态电压抑制器及其制备方法。

背景技术

TVS是一种二极管形式的高效能保护器件。当TVS二极管的两极受到反向瞬态高能量冲击时,它能以10的负12次方秒量级的速度,将其两极间的高阻抗变为低阻抗,吸收高达数千瓦的浪涌功率,使两极间的电压箝位于一个预定值,有效地保护电子线路中的精密元器件,免受各种浪涌脉冲的损坏。由于它具有响应速度快、瞬态功率大、漏电流低、击穿电压偏差小、箝位电压较易控制、无损坏极限、体积小等优点,已广泛应用于计算机系统、通讯设备、交/直流电源、汽车、电子镇流器、家用电器、仪器仪表(电度表),RS232/422/423/485、I/O、LAN、ISDN、ADSL、USB、MP3、PDAS、GPS、CDMA、GSM、数字照相机的保护、共模/差模保护、RF耦合/IC驱动接收保护、电机电磁波干扰抑制、声频/视频输入、传感器/变速器、工控回路、继电器、接触器噪音的抑制等各个领域。

TVS在系统中的主要功能是保护电子系统免受高能瞬态脉冲的影响,如静电放电(ESD)、雷电浪涌和电快速瞬态脉冲(EFT)。TVS通常被建议放在连接器旁边,因为静电放电、浪涌和电快速瞬态脉冲通常通过连接器进入系统。当这些高能量瞬态脉冲通过连接器进入系统时,它们将触发TVS,TVS将立即进入低阻抗状态,TVS将瞬态脉冲的能量导向系统的接地端(GND)。

TVS器件的关键参数有

(1)工作峰值反向电压VRWM(Working peak reverse voltage)

VRWM是TVS二极管能够保持高电阻状态的最小反向电压值。一般VRWM会低于85%Vc而高于正常工作电压,以便TVS接入电路而不影响正常。

(2)反向击穿电压VBR(Reverse breakdown voltage)

VBR是通过TVS二极管的反向电压是指TVS保护二极管开启时的电压,从此点开始器件进入雪崩击穿,是在测试电流IT下测得的。

(3)钳位电压VC(Clamp voltage)

VC是钳位电压,施加规定波形的峰值脉冲电流IPP时,TVS两端测得的峰值电压。在相同IPP下的VC越小,说明TVS的钳位特性越好。TVS的耐脉冲电流冲击能力可以参考IPP,同型号的TVS,IPP越大,耐脉冲电流冲击能力越强。

(4)反向漏电流IR(Reverse Leakage Current)

漏电流,也称待机电流。在规定温度和最高工作电压条件下,流过TVS的最大电流。TVS的漏电流一般是在工作峰值反向电压VRWM(Working peak reverse voltage)下测量的漏电值。

(5)峰值脉冲电流IPP(Peak pulse current)

IPP是在TVS保护二极管本身损坏之前可以分流的峰值浪涌电流。也是器件能承受浪涌能力的一个主要指标参数。IPP越大器件浪涌能力越强。

在实际应用中我们希望有一个VC低,IR小,且IPP大的防浪涌器件。但是传统的TVS设计方案和工艺思路。提高IPP和降低VC的方向是扩大芯片版面,这样虽然可以有效的提高IPP和VC的性能。但是大的版面带来的成本的升高和漏电的变大。一对矛盾是无法调和的。

而且为了降低器件的VC,我们在设计芯片上会把VBR值做的很小。这对于低压(10V以下的)TVS产品。较低的电压会带来漏电的明显上升。这一对矛盾也是无法调和的。

发明内容

基于上述问题,本发明提供一种低电压低漏电TVS器件的设计思路,旨在达到在有效降低漏电的同时提高了IPP水平并降低了VC值的目的。

一种低压低漏电瞬态电压抑制器,包括:

衬底,包括上表面侧,于上表面侧形成有:

第一深结,由上之下深入衬底的内部,呈现纵向插指形状;

第一浅结,与第一深结衔接,位于衬底的上表面侧的顶层;

第一边缘深结,位于第一深结的左右两侧,并与第一浅结衔接。

进一步的,衬底还包括与上表面侧相对的下表面侧,于下表面侧形成有:

第二深结,由下至上深入衬底的内部,呈现纵向插指形状;

第二浅结,与第二深结衔接,位于衬底的下表面侧的底层;

第二边缘深结,位于第二深结的左右两侧,并与第二浅结衔接。

进一步的,第一深结和第二深结上下错开设置。

进一步的,位于第一深结右侧的第一边缘深结的横向宽度大于位于第二深结右侧的第二边缘深结的横向宽度;

位于第二深结左侧的第二边缘深结的横向宽度大于位于第一深结左侧的第一边缘深结的横向宽度。

一种低压低漏电瞬态电压抑制器的制备方法,包括:

步骤A1,准备衬底;

步骤A2,于衬底的上表面侧形成第一深结和第一边缘深结,第一深结由上之下深入衬底的内部,呈现纵向插指形状;

步骤A3,于衬底的上表面侧的顶层形成第一浅结,第一浅结分别与第一深结和第一边缘深结衔接;

其中,第一边缘深结位于第一深结的左右两侧。

进一步的,包括:

在步骤A2中还包括:于衬底的下表面侧形成第二边缘深结和第二深结,第一深结由上之下深入衬底的内部,呈现纵向插指形状;

在步骤A3中,还包括:于衬底的下表面侧的底层形成第二浅结,第二浅结分别与第二深结和第二边缘深结衔接;

其中,第二边缘深结位于第二深结的左右两侧。

进一步的,在步骤A2中,第一深结和第二深结上下错开设置。

进一步的,步骤A201,生长一层氧化层作为第一氧化层;

步骤A202,除去第一预定区域的第一氧化层;

步骤A203,注入硼元素,退火,形成第一边缘深结;

步骤A204,生长一层氧化层,与第一氧化层结合作为第二氧化层,

步骤A205,除去第二预定区域的第二氧化层;

步骤A206,旋涂硼元素并进行扩散,退火,形成第一深结。

进一步的,步骤A3包括:

步骤A301,生长一层氧化层,与第二氧化层共同作为第三氧化层;

步骤A302,去除第三预定区域的第三氧化层;

步骤A303,进行硼元素注入;

步骤A304,进行氧化推结,形成第一浅结以及第一浅结外表面的第四氧化层;

步骤A305,除去第一浅结的外表面的第四氧化层。

进一步的,步骤A4,在衬底的上表面侧上生长第一金属层,在衬底的下表面侧生长第二金属层。

本发明的有益技术效果在于:优化TVS器件纵向结构,采用高耐压深结与低电压浅结结合的方法,对器件电场进行整形。可以有效的降低低电压PN结表面的电场强度,从而有效的降低漏电。

附图说明

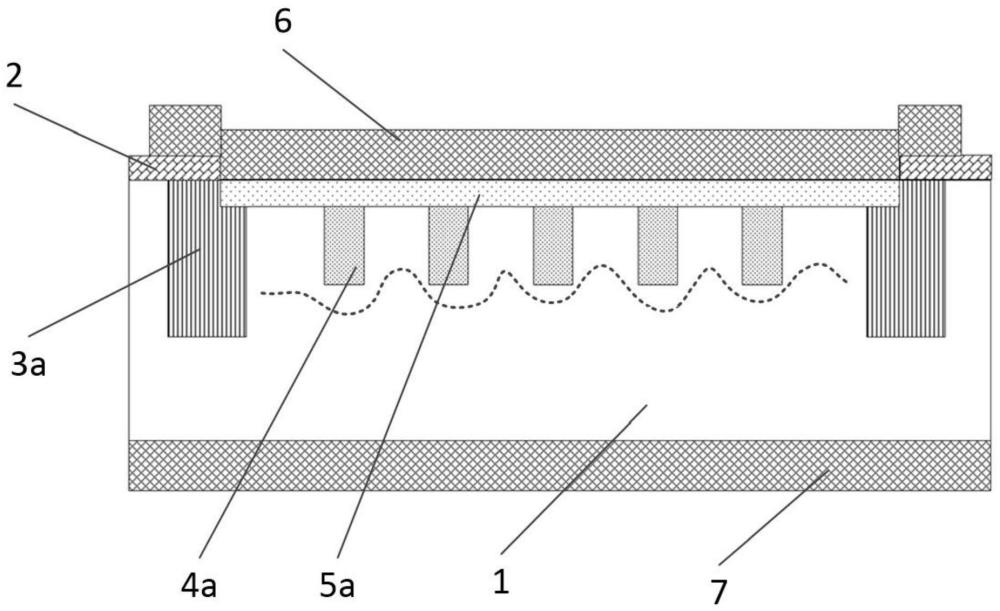

图1为本发明一种单向低压低漏电的TVS器件结构示意图;

图2为本发明一种双向低压低漏电的TVS器件结构示意图;

图3为现有技术一种单向TVS器件结构示意图;

图4为现有技术一种双向TVS器件结构示意图;

图5-7为本发明一种低压低漏电的TVS器件制备方法的步骤流程图;

图8-17为本发明一种单向低压低漏电的TVS器件制备方法的过程结构图;

图18-19为本发明一种双向低压低漏电的TVS器件制备方法的过程结构图;

1-衬底;

2-氧化层;

3a-第一边缘深结;

3b-第二边缘深结;

4a-第一深结;

4b-第二深结;

5a-第一浅结;

5b-第二浅结;;

6-第一金属层;

7-第二金属层。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动的前提下所获得的所有其他实施例,都属于本发明保护的范围。

需要说明的是,在不冲突的情况下,本发明中的实施例及实施例中的特征可以相互组合。

下面结合附图和具体实施例对本发明作进一步说明,但不作为本发明的限定。

参见图1,本发明提供一种低压低漏电瞬态电压抑制器,包括:

衬底(1),包括上表面侧,于上表面侧形成有:

第一深结(4a),由上之下深入衬底(1)的内部,呈现纵向插指形状;

第一浅结(5a),与第一深结((4a))衔接,位于衬底(1)的上表面侧的顶层;

第一边缘深结(3a),位于第一深结(4a)的左右两侧,并与第一浅结(5a)衔接。

本发明通过优化TVS器件纵向结构,采用高耐压深结与低电压浅结结合的方法,对TVS器件电场进行整形。可以有效的降低低电压PN结表面的电场强度,从而有效的降低漏电。此外,第一深结使用纵向插指形状。结合图1和图3,本发明可以在相同的芯片面积内,形成波浪形(图1中虚线所示)的有效结面积,相比于现有技术中没有高耐压深结形成的直线型(图3中虚线所示)有效结面积,本发明的波浪形有效结面积显然更大。从而提高器件浪涌能力。且可以有效的降低器件残压。

本发明针对10V以下低电压TVS器件具有明显的效果,如反向漏电流IR变小,峰值脉冲电流IPP提高,和钳位电压VC减少。

具体的,衬底(1)为P型衬底,第一边缘深结(3a)和第一深结(4a)为硼源。

作为本发明的一种具体实施方式,仅在衬底(1)的第一面形成第一边缘深结(3a)、高耐压的第一深结(4a)以及低电压的第一浅结(5a),从而获得单向低压低漏电的TVS器件。

对于单向低压低漏电的TVS器件,在衬底(1)的上表面侧顶部的低电压的第一浅结的外表面生长有第一金属层(6),在衬底的下表面侧生长有第二金属层(7),单向低压低漏电的TVS器件中,第一金属层为正面金属层,第二金属层为背面金属层。第一金属层(6)为钛镍银金属复合层,第二金属层(7)钛镍银复合金属层。

参见图2,进一步的,衬底(1)还包括与上表面侧相对的下表面侧,于下表面侧形成有:

第二深结(4b),由下至上深入衬底(1)的内部,呈现纵向插指形状;

第二浅结(5b),与第二深结(4b)衔接,位于衬底(1)的下表面侧的底层;

第二边缘深结(3b),位于第二深结(4b)的左右两侧,并与第二浅结(5b)衔接。

进一步的,第一深结(4a)和第二深结(4b)上下错开设置。

作为本发明的一种具体实施方式,在衬底(1)的上表面侧和相对于上表面侧的下表面侧均形成边缘深结、高耐压深结以及低电压浅结,两侧面的高耐压深结均为纵向插指形状,并且上下相互错开设置,均形成波浪线(参见图2所示的虚线)的有效结面积,比现有技术中直线型(参见图4中的虚线)有效结面积不增加芯片面积的同时,获得双向低压低漏电的TVS器件。

对于双向低压低漏电的TVS器件,在衬底(1)的上表面侧的低电压浅结层的外表面生长有第一金属层(6),在衬底(1)的下表面侧的低电压浅结层的外表面生长有第二金属层(7)。第一金属(6)为钛镍银金属复合层,第二金属层(7)钛镍银复合金属层。

进一步的,位于第一深结右侧的第一边缘深结的横向宽度大于位于第二深结右侧的第二边缘深结的横向宽度;

位于第二深结左侧的第二边缘深结的横向宽度大于位于第一深结左侧的第一边缘深结的横向宽度。

在横向方向上,位于同一侧的第一边缘深结背向第一深结的一侧面和第二边缘深结背向第二深结的一侧面纵向上齐平,在横向方向上的宽度有所差别,例如位于第一深结右侧的第一边缘深结的横向宽度大于位于第二深结右侧的第二边缘深结的横向宽度位于第二深结左侧的第二边缘深结的横向宽度大于位于第一深结左侧的第一边缘深结的横向宽度,可以使内部的第一深结和第二深结在结构上错开,插指状的第一深结指向插指状的第二深结的间隙,第二深结指向第一深结的间隙。

参见图5,本发明还提供一种低压低漏电瞬态电压抑制器的制备方法,包括:

步骤A1,准备衬底;

步骤A2,于衬底的上表面侧形成第一深结和第一边缘深结,第一深结由上之下深入衬底的内部,呈现纵向插指形状;

步骤A3,于衬底的上表面侧的顶层形成第一浅结,第一浅结分别与第一深结和第一边缘深结衔接;

其中,第一边缘深结位于第一深结的左右两侧。

在步骤A1中,衬底可以为P型衬底。取出晶圆,对晶圆进行激光打标,并使用HF溶液处理,之后去离子水清洗干净。

参见图6,进一步的,步骤A201,生长一层氧化层作为第一氧化层;

步骤A202,除去第一预定区域的第一氧化层;

步骤A203,注入硼元素,退火,形成第一边缘深结;

步骤A204,生长一层氧化层,与第一氧化层结合作为第二氧化层,

步骤A205,除去第二预定区域的第二氧化层;

步骤A206,旋涂硼元素并进行扩散,退火,形成第一深结。

在步骤A201中,进行第一次氧化层的生长,如图8所示。

在步骤A202中,通过光刻、显影、腐蚀、去除多余氧化层,即去除第一预定区域的第一氧化层。第一预定区域为需要形成边缘深结的衬底区域,如图9所示。

在步骤A203中,注入硼元素,注入条件90keV 2.0E15cm-2,之后进行去胶处理。NH4F溶液去除表面的含有杂质的氧化层。之后进行退火处理,此时边缘深结的形成完成,如图10所示。

在步骤A204中,进行第二次氧化层的生长,从而形成第二氧化层,如图11所示。

在步骤A205中,之后重复步骤A202的光刻、腐蚀的工艺。去除多余氧化层以及光刻胶,即去除第二预定区域的第二氧化层,第二预定区域为需要形成第一深结的衬底区域,如图12所示。

在步骤A206中,通过硼涂布,旋涂硼源,之后高温进行纵向扩散,之后对表面进行漂洗。之后进行高温退火,之后对表面进行清洗,形成第一深结,即构成高耐压深结层,如图13所示。

参见图7,进一步的,步骤A3包括:

步骤A301,生长一层氧化层,与第二氧化层共同作为第三氧化层;

步骤A302,去除第三预定区域的第三氧化层;

步骤A303,进行硼元素注入;

步骤A304,进行氧化推结,形成第一浅结以及第一浅结外表面的第四氧化层;

步骤A305,除去第一浅结的外表面的第四氧化层。

进一步的,步骤A4,在衬底的上表面侧上生长第一金属层,在衬底的下表面侧生长第二金属层。

在步骤A301中,进行第三次氧化层的生长,与第二氧化层共同作为第三氧化层,如图12所示。

在步骤A302中,重复光刻腐蚀工艺,去除表面多余的氧化层和光刻胶。第三预定区域为需要形成低电压浅结层的区域。

在步骤A305中,再次光刻,腐蚀去除低电压浅结层表面的氧化层,如图17所示。

进一步的,步骤A4,生长金属层。通过生长金属层并且进行光刻和腐蚀。得到设计的焊接面图形。在步骤A4中,还在衬底的第二面生长金属层,形成背面金属层。之后,进行封装,SMB封装。

如图18所示,进一步的,包括:

在步骤A2中还包括:于衬底的下表面侧形成第二边缘深结和第二深结,所述第二深结由下之上深入所述衬底的内部,呈现纵向插指形状,如图18所示;

在步骤A3中,还包括:于衬底的下表面侧的底层形成第二浅结,第二浅结分别与第二深结和第二边缘深结衔接,如图19所示;

其中,第二边缘深结位于第二深结的左右两侧。

进一步的,在步骤A2中,第一深结和第二深结上下错开设置。

通过在衬底的下表面侧也形成边缘深结、高耐压深结层和低电压浅结层,从而得到双向TVS器件。下表面侧形成边缘深结、高耐压深结层和低电压浅结层的过程和上表面侧形成的边缘深结、高耐压深结层和低电压浅结层过程相同。

实施例1

本实施例1主要形成一款5V单向低漏电TVS器件的制作,过程如下:

步骤A1,准备衬底;取5英寸晶圆,厚度350微米,电阻率0.25Ωcm,激光打标以及清洗,使用HF溶液处理30S,之后去离子水清洗干净。

步骤A2,于衬底的上表面侧形成边缘深结和高耐压深结,主要步骤如下:

步骤A201,生长一层氧化层作为第一氧化层,1150℃环境下生长第一氧化层30分钟。第一氧化层厚度2微米。

步骤A202,除去第一预定区域的第一氧化层;光刻显影腐蚀去除多余氧化层。

步骤A203,注入硼元素,退火,形成边缘深结;硼注入的注入条件为90keV2.0E15cm-2,之后进行去胶处理。NH4F溶液去除表面的含有杂质的氧化层。1250℃30分钟退火处理。形成边缘深结。

步骤A204,生长一层1微米氧化层,与第一氧化层结合作为第二氧化层,

步骤A205,除去第二预定区域的第二氧化层;即重复光刻腐蚀的工艺。去除多余氧化层以及光刻胶。

步骤A206,旋涂硼元素并进行扩散,退火,形成高耐压深结。硼涂布,旋涂硼源后,在900度温度进行纵向扩散,之后对表面进行漂洗,接着退火,使用1100℃温度以及20分钟条件进行退火,之后对表面进行清洗。

步骤A3,于上表面侧的高耐压深结的外表面形成低电压浅结。包括如下步骤:

步骤A301,生长一层氧化层,与第二氧化层共同作为第三氧化层;

步骤A302,去除第三预定区域的第三氧化层;即去除表面多余的氧化层和光刻胶。

步骤A303,进行硼元素注入;注入条件,140Kev计量为8E14。

步骤A304,进行氧化推结,形成低电压浅结以及低电压浅结外表面的第四氧化层;氧化推结的电性工艺是1050摄氏度30分钟。此时得到的击穿电压是6.5V。

步骤A305,除去低电压浅结的外表面的第四氧化层。再次光刻,腐蚀去除低电压浅结的外表面的第四氧化层。

在步骤A4中,衬底第一面生长钛镍银金属,且进行光刻和腐蚀。得到设计的焊接面图形。衬底第二面生长钛镍银双金属。

封装形成TVS器件,封装形式为SMB封装。

封装后对器件进行静态和浪涌测试。针对于相同芯片大小和相同封装工艺的产品,本发明的TVS器件漏电典型值由0.2μA减小到了0.08μA。器件浪涌能力加强,以10/1000μS浪涌波形为例,IPP极限值由100A上升到120A,VC由9.8V降低到9.5V,器件性能优于传统工艺水平。

实施例2

本实施例2主要形成一款3.3V双向低漏电TVS器件的制作,过程如下:

基本过程通实施离,不同的在于,对衬底的上表面侧和下表面侧均进行边缘深结、高耐压深结和低电压浅结形成。不同的是步骤A206,旋涂硼元素并进行纵向扩散清洗后,在1200度退火25分钟。生长金属层,对器件进行封装。本双向TVS器件进行SMC封装。本实施例2制备的3.3V器件产品实际击穿电压4.5V,漏电值相对传统工艺减少了80%,IPP提升了20%,VC值降低了15%,性能优于传统TVS结构。

以上仅为本发明较佳的实施例,并非因此限制本发明的实施方式及保护范围,对于本领域技术人员而言,应当能够意识到凡运用本发明说明书及图示内容所作出的等同替换和显而易见的变化所得到的方案,均应当包含在本发明的保护范围内。