锗硅源漏结构及其制造方法

文献发布时间:2023-06-19 09:29:07

技术领域

本发明涉及半导体集成电路制造领域,特别是涉及一种锗硅源漏结构。本发明还涉及一种锗硅源漏的制造方法。

背景技术

随着集成电路的发展,场效应尺寸越来越小,半导体制造中引入了应力技术来改变沟道中的晶格结构,从而提高沟道中的载流子的迁移率;从现有的研究来看在沟道上施加拉应力能提高电子的迁移率,而施加压应力则能提高空穴的迁移率。嵌入式SiGe技术被广泛应用以提高PMOS的的性能,嵌入式SiGe技术通过在PMOS在源区和漏区嵌入SiGe材料,能够向沟道区施加压应力,使得PMOS的性能得到显著的提升。

在现有嵌入式锗硅工艺中,由于外延生长主体层锗浓度越高,转换生长盖帽层的过渡中就越容易变形,导致形貌难控制,应力容易释放,影响器件性能。

如图1A至图1E所示,是现有锗硅源漏的制造方法各步骤中的器件结构图。现有锗硅源漏的制造方法包括如下步骤:

步骤一、如图1A所示,提供半导体基体101。

现有方法中,所述半导体基体101为硅基体。

如图1B所示,在所述半导体基体101的选定区域中进行刻蚀形成凹陷102。

所述凹陷102的剖面结构为U型或者为∑形状。

所述凹陷102为对所述半导体基体101的(100)面进行刻蚀形成;

步骤二、如图1C所示,在所述凹陷102结构的内侧表面外延生长锗硅种子层103。

步骤三、如图1D所示,进行外延生长在所述锗硅种子层103上形成将所述凹陷102完全填充的锗硅主体层104。

所述锗硅主体层104的顶部表面突出到所述凹陷102的顶部表面之上。

步骤四、如图1E所示,在所述锗硅主体层104的表面形成盖帽层105。

所述盖帽层105的材料为锗硅且采用外延生长工艺形成。

由于所述锗硅主体层104的锗浓度较高,而所述盖帽层105的外延生长工艺通常和所述锗硅主体层104的外延生长工艺不同,所述盖帽层105的外延生长工艺和所述锗硅主体层104的外延生长工艺之间需要进行转换,工艺转换过程中,较高锗浓度在高温如工艺转换过程中的工艺温度作用下会使所述锗硅主体层104产生形变,比较图1E和图1D所示可知,图1E中所述锗硅主体层104的顶部表面形貌和图1D的不同,图1E中的所述锗硅主体层104的形貌变化后,而所述锗硅主体层104的应力和形貌相关,最后应力会部分释放,最后会减少对沟道区产生的应力,从而降低器件的性能。

发明内容

本发明所要解决的技术问题是提供一种锗硅源漏结构,能使锗硅主体层的形貌得到很好的控制,从而能防止由于锗硅主体层的变形而产生应力释放并进而影响器件的性能,最后能提高器件的性能。为此,本发明还提供一种锗硅源漏的制造方法。

为解决上述技术问题,本发明提供的锗硅源漏结构包括:

形成于半导体基体中的凹陷。

在所述凹陷的内侧表面形成有锗硅种子层。

锗硅主体层形成于所述锗硅种子层上并将所述凹陷完全填充。

硅固化层形成在所述锗硅主体层表面,所述锗硅主体层和所述硅固化层都采用外延工艺形成,所述硅固化层是在所述锗硅主体层的外延生长完成后通过不间断的外延生长形成,以实现对所述锗硅主体层的形貌固化,从而防止所述锗硅主体层顶部表面直接暴露时产生形貌变化。

在所述硅固化层的表面形成有盖帽层。

进一步的改进是,所述半导体基体为硅基体。

进一步的改进是,所述凹陷的剖面结构为U型或者为∑形状。

进一步的改进是,所述锗硅主体层的顶部表面突出到所述凹陷的顶部表面之上。

进一步的改进是,所述凹陷为对所述半导体基体的(100)面进行刻蚀形成;突出在所述凹陷的顶部表面之上的所述锗硅主体层的侧面具有(111)面。

进一步的改进是,锗硅源漏用于形成PMOS的源区和漏区,在所述半导体基体上还形成有所述PMOS的栅极结构,所述凹陷形成在所述栅极结构两侧的所述半导体基体中。

在所述锗硅源漏中还形成有P型重掺杂的源漏注入区以组成所述源区和所述漏区,所述源漏注入区和所述栅极结构自对准。

在所述源区和所述漏区之间的所述半导体基体上形成有N型掺杂的沟道区。

进一步的改进是,所述栅极结构包括依次叠加的栅介质层和栅极导电材料层。

进一步的改进是,所述栅介质层为二氧化硅层或者为高介电常数层;所述栅极导电材料层为多晶硅栅或者为金属栅。

进一步的改进是,所述盖帽层的材料为硅或锗硅。

为解决上述技术问题,本发明提供的锗硅源漏的制造方法包括如下步骤:

步骤一、提供半导体基体,在所述半导体基体的选定区域中进行刻蚀形成凹陷。

步骤二、在所述凹陷结构的内侧表面外延生长锗硅种子层。

步骤三、进行外延生长在所述锗硅种子层上形成将所述凹陷完全填充的锗硅主体层,在所述锗硅主体层的外延生长的基础上继续进行不间断的外延生长形成硅固化层,利用不间断外延实现所述硅固化层对所述锗硅主体层形貌的固化,以防止所述锗硅主体层顶部表面直接暴露时由高温而产生的形貌变化。

步骤四、在所述硅固化层的表面形成盖帽层。

进一步的改进是,所述半导体基体为硅基体。

进一步的改进是,所述凹陷的剖面结构为U型或者为∑形状。

进一步的改进是,所述锗硅主体层的顶部表面突出到所述凹陷的顶部表面之上。

进一步的改进是,所述凹陷为对所述半导体基体的(100)面进行刻蚀形成;突出在所述凹陷的顶部表面之上的所述锗硅主体层的侧面具有(111)面。

进一步的改进是,锗硅源漏用于形成PMOS的源区和漏区,在所述半导体基体上还形成有所述PMOS的栅极结构,所述凹陷形成在所述栅极结构两侧的所述半导体基体中。

在所述锗硅源漏中还形成有P型重掺杂的源漏注入区以组成所述源区和所述漏区,所述源漏注入区和所述栅极结构自对准。

在所述源区和所述漏区之间的所述半导体基体上形成有N型掺杂的沟道区。

进一步的改进是,所述栅极结构包括依次叠加的栅介质层和栅极导电材料层。

进一步的改进是,所述栅介质层为二氧化硅层或者为高介电常数层;所述栅极导电材料层为多晶硅栅或者为金属栅。

进一步的改进是,步骤四中,所述盖帽层的材料为硅或锗硅且采用外延生长工艺形成。

本发明通过设置采用不间断的连续外延生长工艺在锗硅主体层表面形成硅固化层,硅固化层能实现对锗硅主体层的形貌固化,从而防止能锗硅主体层顶部表面直接暴露时产生形貌变化,这样,在形成盖帽层后,锗硅主体层的形貌能保持为外延生长形成的形貌,这样能防止由于锗硅主体层的形貌改变而是应力被释放,所以最后能得到应力最大的锗硅主体层结构,最后能使沟道区得到最大的应力并从而能提高器件的性能。

同时,同一半导体基体上往往集成有多个锗硅源漏结构,本发明还能使同一半导体基体上各锗硅源漏的形貌均匀,最后使器件性能的均一性提高。

本发明实施例还更加有利于所述盖帽层沿(111)面的生长,从而能改善电阻的均匀性并从而改善性能。

附图说明

下面结合附图和具体实施方式对本发明作进一步详细的说明:

图1A-图1E是现有锗硅源漏的制造方法各步骤中的器件结构图;

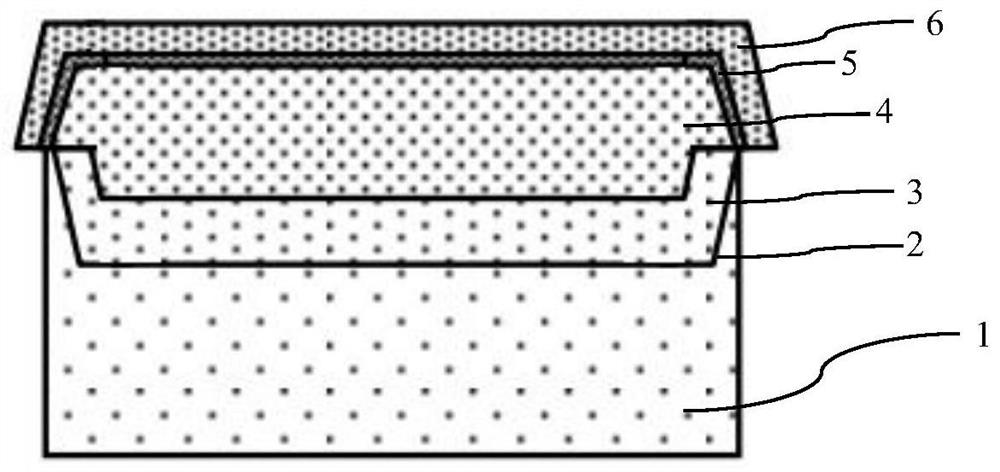

图2是本发明实施例锗硅源漏的结构图;

图3A-图3D是本发明实施例方法各步骤中的器件结构图。

具体实施方式

如图2所示,是本发明实施例锗硅源漏的结构图;本发明实施例锗硅源漏结构包括:

形成于半导体基体1中的凹陷2。

本发明实施例中,所述半导体基体1为硅基体。

所述凹陷2的剖面结构为U型。在其他实施例中,也能为:所述凹陷2的剖面结构为∑形状。

在所述凹陷2的内侧表面形成有锗硅种子层3。

锗硅主体层4形成于所述锗硅种子层3上并将所述凹陷2完全填充。

硅固化层5形成在所述锗硅主体层4表面,所述锗硅主体层4和所述硅固化层5都采用外延工艺形成,所述硅固化层5是在所述锗硅主体层4的外延生长完成后通过不间断的外延生长形成,以实现对所述锗硅主体层4的形貌固化,从而防止所述锗硅主体层4顶部表面直接暴露时产生形貌变化,现有未覆盖所述硅固化层5的所述锗硅主体层4的形貌容易变化主要是由于所述锗硅主体层4容易在高温如盖帽层6的外延工艺温度的作用下产生形貌变化。

在所述硅固化层5的表面形成有盖帽层6。

本发明实施例中,所述锗硅主体层4的顶部表面突出到所述凹陷2的顶部表面之上。其中,所述凹陷2的顶部表面和所述半导体基体1的顶部表面相平。

所述凹陷2为对所述半导体基体1的(100)面进行刻蚀形成;突出在所述凹陷2的顶部表面之上的所述锗硅主体层4的侧面具有(111)面。

所述盖帽层6的材料为锗硅,通常采用外延生长形成。和图1E相比,本发明实施例中图2的所述硅固化层5的表面更加有利于所述盖帽层6的外延生长,如有利于使所述盖帽层6沿(111)面生长。

锗硅源漏用于形成PMOS的源区和漏区,在所述半导体基体1上还形成有所述PMOS的栅极结构,所述凹陷2形成在所述栅极结构两侧的所述半导体基体1中。

在所述锗硅源漏中还形成有P型重掺杂的源漏注入区以组成所述源区和所述漏区,所述源漏注入区和所述栅极结构自对准。

在所述源区和所述漏区之间的所述半导体基体1上形成有N型掺杂的沟道区。被所述栅极结构覆盖的所述沟道区的表面用于形成沟道。

所述栅极结构包括依次叠加的栅介质层和栅极导电材料层。所述栅介质层为二氧化硅层或者为高介电常数层;所述栅极导电材料层为多晶硅栅或者为金属栅。其中,所述栅介质层为二氧化硅层即栅氧化层以及所述栅极导电材料层为多晶硅栅时,所述栅极结构为多晶硅栅极结构。

所述栅介质层为高介电常数层;所述栅极导电材料层为金属栅时,所述栅极结构为HKMG,HK表示高介电常数层,MG表示金属栅。HKMG通常需要采用栅极后形成工艺(Gatelast)实现,这时需要利用伪栅极结构,所述伪栅极结构由栅氧化层和伪多晶硅栅叠加而成,最后形成源区和漏区之后,还会形成层间膜,之后使层间膜和伪多晶硅栅的顶部表面相平并使伪多晶硅栅顶部表面暴露,之后再去除所述伪多晶硅栅和栅氧化层,之后在所述伪栅极结构去除的区域中形成HKMG。

本发明实施例通过设置采用不间断的连续外延生长工艺在锗硅主体层4表面形成硅固化层5,硅固化层5能实现对锗硅主体层4的形貌固化,从而防止能锗硅主体层4顶部表面直接暴露时产生形貌变化,这样,在形成盖帽层6后,锗硅主体层4的形貌能保持为外延生长形成的形貌,这样能防止由于锗硅主体层4的形貌改变而是应力被释放,所以最后能得到应力最大的锗硅主体层4结构,最后能使沟道区得到最大的应力并从而能提高器件的性能。

同时,同一半导体基体1上往往集成有多个锗硅源漏结构,本发明实施例还能使同一半导体基体1上各锗硅源漏的形貌均匀,最后使器件性能的均一性提高。

本发明实施例还更加有利于所述盖帽层6沿(111)面的生长,从而能改善电阻的均匀性并从而改善性能。

如图3A至图3D所示,是本发明实施例方法各步骤中的器件结构图。本发明实施例锗硅源漏的制造方法包括如下步骤:

步骤一、如图3A所示,提供半导体基体1。

本发明实施例方法中,所述半导体基体1为硅基体。

如图3B所示,在所述半导体基体1的选定区域中进行刻蚀形成凹陷2。

本发明实施例方法中,所述凹陷2的剖面结构为U型。其他实施例方法中也能为:所述凹陷2的剖面结构为∑形状。

所述凹陷2为对所述半导体基体1的(100)面进行刻蚀形成;

步骤二、如图3C所示,在所述凹陷2结构的内侧表面外延生长锗硅种子层3。

步骤三、如图3D所示,进行外延生长在所述锗硅种子层3上形成将所述凹陷2完全填充的锗硅主体层4,在所述锗硅主体层4的外延生长的基础上继续进行不间断的外延生长形成硅固化层5,利用不间断外延实现所述硅固化层5对所述锗硅主体层4形貌的固化,以防止所述锗硅主体层4顶部表面直接暴露时产生形貌变化。现有未覆盖所述硅固化层5的所述锗硅主体层4的形貌容易变化主要是由于所述锗硅主体层4容易在高温如后续盖帽层6的外延工艺温度的作用下产生形貌变化。

步骤四、如图2所示,在所述硅固化层5的表面形成盖帽层6。

所述盖帽层6的材料为锗硅且采用外延生长工艺形成。

所述锗硅主体层4的顶部表面突出到所述凹陷2的顶部表面之上。突出在所述凹陷2的顶部表面之上的所述锗硅主体层4的侧面具有(111)面。和图1E相比可知,本发明实施例方法更加有利于所述盖帽层6沿(111)面的生长,从而能改善电阻的均匀性并从而改善性能。

本发明实施例方法中,锗硅源漏用于形成PMOS的源区和漏区,在所述半导体基体1上还形成有所述PMOS的栅极结构,所述凹陷2形成在所述栅极结构两侧的所述半导体基体1中。

在所述锗硅源漏中还形成有P型重掺杂的源漏注入区以组成所述源区和所述漏区,所述源漏注入区和所述栅极结构自对准。

在所述源区和所述漏区之间的所述半导体基体1上形成有N型掺杂的沟道区。

所述栅极结构包括依次叠加的栅介质层和栅极导电材料层。所述栅介质层为二氧化硅层或者为高介电常数层;所述栅极导电材料层为多晶硅栅或者为金属栅。

其中,所述栅介质层为二氧化硅层即栅氧化层以及所述栅极导电材料层为多晶硅栅时,所述栅极结构为多晶硅栅极结构。所述栅介质层为高介电常数层;所述栅极导电材料层为金属栅时,所述栅极结构为HKMG,

对于多晶硅栅极结构,步骤一形成所述凹陷2之前,在所述半导体衬底1的表面形成有所述多晶硅栅极结构。所述源漏注入区对应的源漏注入工艺在步骤四完成后进行并和所述多晶硅栅极结构自对准。

对于HKMG,步骤一形成所述凹陷2之前,在所述半导体衬底1的表面形成有伪栅极结构,所述伪栅极结构由栅氧化层和伪多晶硅栅叠加而成。所述源漏注入区对应的源漏注入工艺在步骤四完成后进行并和所述伪栅极结构自对准。在所述源区和所述漏区形成后,还包括形成接触刻蚀停止层(CESL)和层间膜的步骤,之后进行回刻使层间膜和伪多晶硅栅的顶部表面相平并使伪多晶硅栅顶部表面暴露,之后再去除所述伪多晶硅栅和栅氧化层,之后在所述伪栅极结构去除的区域中形成HKMG。

以上通过具体实施例对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

- 具有锗硅源漏的PMOS管的制造方法

- 具有锗硅源漏的PMOS管的制造方法