一种网格化容错计算机平台的监控系统

文献发布时间:2023-06-19 09:36:59

技术领域

本申请涉及航空机载容错计算机体系结构技术领域,具体涉及一种网格化容错计算机平台的监控系统。

背景技术

经典冗余计算机系统以完整资源构成的通道为核心实现容错能力(如图1所示),与单机系统相比可提升整机的安全与可靠工作特性,但由于独立资源与通道概念捆绑,因此这种经典的体系结构对资源的利用率偏低,对产品可靠性的提升受限,仅单主处理器故障就会将其所属通道完全切除,其未故障的局部资源不能得到有效利用;通道间仅存在交叉传输链路,一旦失效则双通道间将失去通信互联而导致监控能力丧失;主控制计算应用与计算机平台通道仲裁都由通道内主处理器完成,导致应用层软件开发较复杂,用户不能专注于核心控制应用的开发;产品的系统功能集成度低,不能有效降低系统负荷。

发明内容

为了解决上述技术问题,本申请提供一种网格化容错计算机平台的监控系统,能够提高产品的系统功能集成度,有效降低系统负荷。

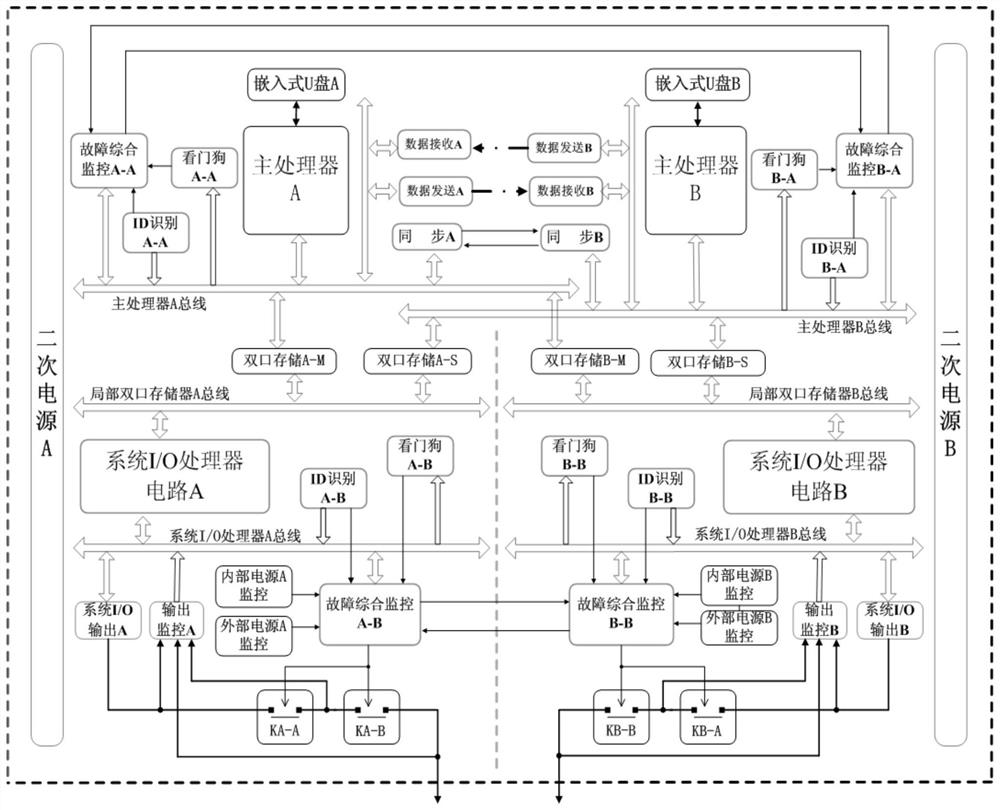

本申请提供一种网格化容错计算机平台的监控系统,所述系统包括主处理器A、主处理器B、系统I/O处理器电路A和系统I/O处理器电路B,其中:

主处理器A通过主处理器A总线连接看门狗A-A、ID识别A-A、同步A、数据发送A、数据接收A、双口存储A-M、双口存储B-M;主处理器A连接嵌入式U盘A;

主处理器B通过主处理器B总线连接看门狗B-A、ID识别B-A、同步B、数据发送B、数据接收B、双口存储A-S、双口存储B-S;主处理器B连接嵌入式U盘B,看门狗B-A;;

系统I/O处理器电路A通过局部双口存储器A总线连接双口存储A-M、双口存储A-S;系统I/O处理器电路A通过系统I/O处理器A总线连接ID识别A-B、看门狗A-B、系统I/O输出A、输出监控A、故障综合监控A-B,ID识别A-B、内部电源A监控;

系统I/O处理器电路B通过局部双口存储器B总线连接双口存储B-M、双口存储B-S;系统I/O处理器电路B通过系统I/O处理器B总线连接ID识别B-B、看门狗B-B、系统I/O输出B、输出监控B、故障综合监控B-B、ID识别B-B、内部电源B监控。

具体的,主处理器A通过USB总线连接嵌入式U盘A。

具体的,主处理器B通过如USB总线连接嵌入式U盘B。

具体的,看门狗A-A、ID识别A-A输出的监控结果信号连接故障综合监控A-A,故障综合监控A-A的输出指示信号连接故障综合监控B-A。

具体的,ID识别B-A输出的监控结果信号连接故障综合监控B-A。

具体的,故障综合监控A-A的输出指示信号连接故障综合监控A-A。

具体的,外部电源A监控的输出指示信号连接故障综合监控A-B,故障综合监控A-B的输出信号连接控制开关KA-A、控制开关KA-B;系统I/O输出A所输出的信号、KA-A开关输出信号、KA-B开关输出信号连接输出监控A,故障综合监控A--B输出指示信号连接故障综合监控B-B。

具体的,外部电源B监控的输出指示信号连接故障综合监控B-B,故障综合监控B-B的输出信号连接控制开关KB-A、控制开关KB-B;系统I/O输出B所输出的信号、KB-A开关输出信号、KB-B开关输出信号连接输出监控B,故障综合监控B-B输出指示信号连接故障综合监控A-B。

综上所述,本申请提供的网格化容错计算机平台的监控系统,具有以下特点:1.监控功能全资源部署,融合了看门狗监控、ID监控、自监控、指示监控、同步监控、数据通讯监控、电源监控、监控记录等等;2.主处理器电路采用“减负”的监控设计,不实现对输出信号的直接开关控制;3.针对系统I/O处理器电路采用强化的监控设计,监控结果信号直接参与对输出信号的开关控制。

附图说明

图1为现有技术中的经典并联系统可靠性结构框图

图2为现有技术中的网格化可靠性结构框图

图3为本申请提供的一种网格化容错计算机平台的监控体系结构设计示意。

具体实施方式

为了克服经典冗余计算机在可靠性方面的不足,目前针对军用无人机中最核心的飞管计算机已经提出了网格化的容错计算机体系结构,其中监控能力的设计是进一步确保该体系结构的容错计算机在实际应用中能够安全可靠稳定运行的关键。经典冗余计算机系统的监控功能设计是以主处理器电路为核心,在网格化可靠性结构框架下的容错计算机必须采用一种新的监控体系结构。本方案所述体系结构具体包括3方面内容:1.监控功能全资源部署,融合了看门狗监控、ID监控、自监控、指示监控、同步监控、数据通讯监控、电源监控、监控记录等等;2.主处理器电路采用“减负”的监控设计,不实现对输出信号的直接开关控制;3.针对系统I/O处理器电路采用强化的监控设计,监控结果信号直接参与对输出信号的开关控制。

针对上述技术背景需求,本提案给出了一种监控体系结构设计(如图3所示),以应用于网格化后的容错计算机平台。具体包括3方面内容:1.监控功能全资源部署,融合了看门狗监控、ID监控、自监控、指示监控、同步监控、数据通讯监控、电源监控、监控记录等等;2.主处理器电路采用“减负”的监控设计,不实现对输出信号的直接开关控制;3.针对系统I/O处理器电路采用强化的监控设计,监控结果信号直接参与对输出信号的开关控制。详细内容如下:

1.监控功能全资源部署。如图3所示主处理器A、主处理器B、系统I/O处理器电路A、系统I/O处理器电路B各部分均设置相应的监控功能。其中的“故障综合监控”、“ID识别”、“看门狗”等监控电路属共有设计,嵌入式U盘A、嵌入式U盘B、数据发送、数据接收、同步等电路是主处理器专署监控使用,“嵌入式U盘”用于对监控数据的记录,数据发送与数据接收为主处理器A和主处理器B之间提供交叉数据传输监控通路,“同步”为主处理器A和主处理器B之间提供同步监控指示;“输出监控”、对“内部电源”及“外部电源”的监控是系统I/O处理器电路部分专署监控使用。

2.主处理器电路采用减负的监控结构设计。主处理器A通过主处理器A总线连接看门狗A-A、ID识别A-A、同步A、数据发送A、数据接收A、双口存储A-M、双口存储B-M,实现对这些监控以及支持电路的控制访问,主处理器A通过专用数据通信线路(如USB总线)连接嵌入式U盘A,看门狗A-A、ID识别A-A输出的监控结果信号连接故障综合监控A-A,故障综合监控A-A的输出指示信号连接故障综合监控B-A;主处理器B通过主处理器B总线连接看门狗B-A、ID识别B-A、同步B、数据发送B、数据接收B、双口存储A-S、双口存储B-S,实现对这些监控电路的控制访问,主处理器B通过专用数据通信线路(如USB总线)连接嵌入式U盘B,看门狗B-A、ID识别B-A输出的监控结果信号连接故障综合监控B-A,故障综合监控A-A的输出指示信号连接故障综合监控B-A。

3.针对系统I/O处理器电路采用强化的监控结构设计。系统I/O处理器电路A通过局部双口存储器A总线连接双口存储A-M、双口存储A-S,系统I/O处理器电路A通过系统I/O处理器A总线连接ID识别A-B、看门狗A-B、系统I/O输出A、输出监控A、故障综合监控A-B,ID识别A-B、看门狗A-B、内部电源A监控、外部电源A监控的输出指示信号连接故障综合监控A-B,故障综合监控A-B的输出信号连接控制开关KA-A、KA-B,系统I/O输出A所输出的信号、KA-A开关输出信号、KA-B开关输出信号连接输出监控A,故障综合监控A-B输出指示信号连接故障综合监控B-B;

系统I/O处理器电路B通过局部双口存储器B总线连接双口存储B-M、双口存储B-S,系统I/O处理器电路B通过系统I/O处理器B总线连接ID识别B-B、看门狗B-B、系统I/O输出B、输出监控B、故障综合监控B-B,ID识别B-B、看门狗B-B、内部电源B监控、外部电源B监控的输出指示信号连接故障综合监控B-B,故障综合监控B-B的输出信号连接控制开关KB-A、KB-B,系统I/O输出B所输出的信号、KB-A开关输出信号、KB-B开关输出信号连接输出监控B,故障综合监控B-B输出指示信号连接故障综合监控A-B。

综上所述,为了克服经典冗余计算机在可靠性方面的不足,目前针对军用无人机中最核心的飞管计算机已经提出了网格化的容错计算机体系结构(如图2所示),其中监控能力的设计是进一步确保该体系结构的容错计算机在实际应用中能够安全可靠稳定运行的关键。经典冗余计算机系统的监控功能设计是以主处理器电路为核心,在网格化可靠性结构框架下的容错计算机必须采用一种新的监控体系结构。

- 一种网格化容错计算机平台的监控系统

- 基于模块化结构的三余度容错计算机平台