具有JFET区布图设计的半导体器件

文献发布时间:2023-06-19 09:41:38

技术领域

本发明涉及半导体领域,更具体而言,涉及具有JFET区布图设计的半导体器件。

背景技术

半导体器件,例如碳化硅(SiC)金属-氧化物半导体场效应晶体管(MOSFET),在工业中有广泛应用。在某些场合,例如功率应用中,期望半导体器件具有高耐压(例如达几千伏)、大电流等特性。然而,现有的半导体器件,例如碳化硅MOSFET,存在体电阻太大而影响器件的电流特性。此外又由于栅区介电层下的电场过高而使得器件容易遭受击穿或失效,无法承受期望的电压,这也影响器件的可靠性和鲁棒性。

发明内容

本发明提出具有JFET区布图设计的半导体器件,以解决现有技术中上述一个或多个技术问题。

根据本发明的一方面,提供一种半导体器件。半导体器件包括半导体层、阱区、源区、栅区、漏电极层、以及JFET区。半导体层具有第一面和与第一面相对的第二面,半导体层包括第一导电类型的基底和设置在基底上的漂移区。阱区具有第二导电类型,阱区设置在漂移区中并且从第一面朝向基底的方向延伸,第二导电类型与第一导电类型不同。源区设置在阱区中,并且从第一面朝向基底的方向延伸。栅区设置在第一面上并且与源区和阱区接触。漏电极层设置在第二面上。JFET区具有第一导电类型,JFET区设置在漂移区中并且从第一面朝向基底的方向延伸,JFET区与栅区接触,JFET区包括多个JFET子区,在顶平面视图下,相邻JFET子区被阱区隔开。

根据本发明的另一方面,提供一种半导体器件。半导体器件包括半导体层、阱区、源区、栅区、漏电极层、以及JFET区。半导体层具有第一导电类型,半导体层具有第一面和与第一面相对的第二面,半导体层包括基底和设置在基底上的漂移区。阱区设置在漂移区中并且从第一面朝向基底的方向延伸,阱区具有与第一导电类型不同的第二导电类型。源区设置在阱区中,并且从第一面朝向基底的方向延伸。栅区设置在第一面上并且与源区和阱区接触。漏电极层设置在第二面上并且与半导体层形成欧姆接触。JFET区具有第一导电类型,JFET区设置在漂移区中并且从第一面朝向基底的方向延伸,JFET区与栅区接触,JFET区包括多个JFET子区,在平面视图下,多个JFET子区中的每个JFET子区被阱区包围,以使得每个JFET子区与相邻的阱区实现电荷平衡。

根据本发明一个或多个实施例的半导体器件具有许多优点。例如,由于JFET区的杂质浓度可比漂移区的杂质浓度更高,由此可降低半导体器件的体电阻,这对于器件的电流能力是十分有利的。此外,JFET区可包括多个JFET子区,每个JFET子区可与周围掺杂类型相反的阱区形成电荷平衡,这可降低靠近栅区的半导体层中的电场,避免电场过高或电流过大引起的器件击穿或失效。因此,根据本发明一个或多个实施例的半导体器件可承受更高的电压,具有更好的可靠性、稳定性、和使用寿命,可适于更多的工业应用。

本发明的其他实施例和更多技术效果将在下文详述。

附图说明

多个实施例通过与之对应的附图进行示例性说明,这些示例性说明并不构成对实施例的限定。为方便计,相同或相似的元件在附图中采用相同或相似的附图标记,除非有特别说明,附图中的图不构成比例限制,其中,

图1a示出根据本发明一实施例的半导体器件的半导体层的顶平面视图;

图1b示出根据本发明一实施例的半导体器件的一截面示意图;

图1c示出根据本发明一实施例的半导体器件的另一截面示意图;

图1d示出根据本发明一实施例的半导体器件的沿一截面的JFET子区和阱区杂质浓度的示意图;

图2示出根据本发明另一实施例的半导体器件的截面示意图;

图3a示出根据本发明又一实施例的半导体器件的半导体层的顶平面视图;

图3b示出根据本发明又一实施例的半导体器件的截面示意图;

图3c示出根据本发明又一实施例的半导体器件的相邻两个JFET子区的顶平面视图;

图4示出根据本发明再一实施例的半导体器件的截面示意图;

图5示出根据本发明一些实施例的半导体器件的制造方法的流程图。

具体实施方式

为了便于理解本发明,以下将结合相关附图描述多个示例性实施例。本领域技术人员要理解的是,本文实施例仅出于例示本发明的目的,而决非对本发明的限制。

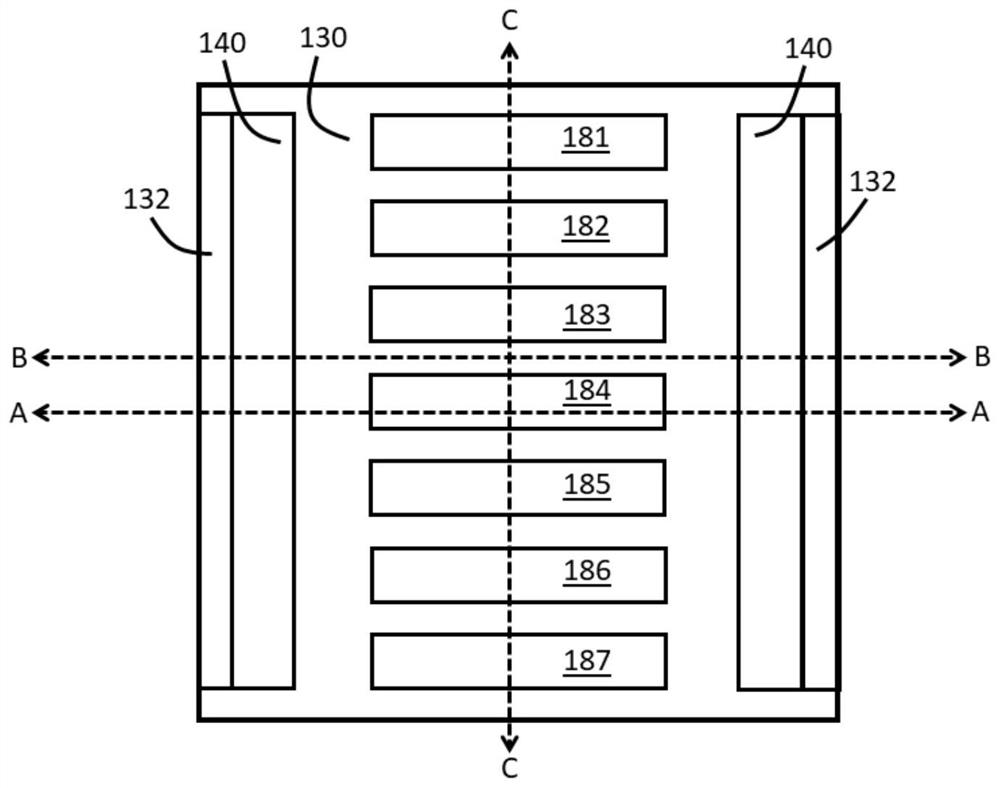

根据本发明的一方面,图1a-1d示出根据一些实施例的半导体器件的不同方面或部分的示意图。图1a是半导体器件的半导体层的顶平面视图或平面图案。图1b是沿着图1a的虚线A-A的截面示意图。注意的是,在图1b的截面示意图中,包括了栅区等。图1c是沿着图1a的虚线B-B的截面示意图图(包括了栅区等)。图1d是沿着图1a的虚线C-C的截面的阱区和JFET子区的杂质浓度示意图。

图1b示出半导体器件10。半导体器件10例如是MOSFET。半导体器件10可以周期性地重复设置在管芯上,例如在图1b中,半导体器件10的左侧和右侧可以是重复设置的半导体器件。在这种情况下,半导体器件10可视为最小的重复单元或元胞。

半导体器件10包括半导体层100。半导体层100具有第一面或顶面102、以及与第一面102相对的第二面或底面或背面104。半导体层100包括半导体材料,半导体材料例如是碳化硅、硅、氮化镓、或其他合适的半导体材料。在本特定实施例中,半导体层100是碳化硅(SiC)层,即包括SiC材料,例如单晶4H-SiC。

半导体层100具有第一导电类型,例如n型。半导体层100包括基底110和设置在基底110上的漂移区120。漂移区120的顶面即为半导体层100的第一面102,基底110的底面即为半导体层100的第二面104。在本特定实施例中,基底110是重掺杂的n型(n+)碳化硅。n型杂质例如可以是氮或磷,杂质浓度例如是1E19cm

在漂移区120中设置有阱区130。阱区130从第一面102朝向基底110方向延伸。阱区130具有第二导电类型,例如p型,p型杂质例如可以是硼、铝等。在本特定实施例中,阱区130的杂质浓度在1E17cm

在阱区130中设置有源区140,源区140从第一面102朝向基底110方向延伸。源区140具有第一导电类型,例如n型,且杂质浓度较高,例如为1E19cm

在第一面102上设置有栅区160。栅区160包括栅电极162(例如掺杂多晶硅、金属、或其组合)以及介质层或介质膜164。介质层164是氧化层、层间介质等绝缘材料的统称。栅区160与阱区130和源区140的至少一部分接触,用于控制沟道电流的流动。

第一面102上还设置有顶金属层或第一金属层150。顶金属层150与阱接触区132和源区140接触以形成低阻接触(例如欧姆接触)。第二面104上设置有漏电极层或背金属层或第二金属层170用于作为半导体器件10的源极或另一电极。

如图1b所示,在漂移区120中还设置有结型场效应管(JFET)区180。JFET区180从第一面102朝向基底110的方向延伸。在图1b的截面示意图中,JFET区180夹置在阱区130之间,并且与阱区130接触。JFET区180从第一面102朝向基底110方向延伸的深度d0与阱区130的深度相同(阱区130的深度例如也称为其结深)。d0可根据实际需要而设置,例如在本特定实施例中,d0为1.2um至1.8um范围。

JFET区180的导电类型与漂移区120相同,均为第一导电类型。JFET区180的杂质浓度可高于漂移区120的杂质浓度。例如在本特定实施例中,JFET区180的杂质浓度为5E15cm

参考图1a的顶平面视图,JFET区180包括多个JFET子区,相邻两个子区之间的距离可根据实际需要而调整。在本特定实施例中示出了七个JFET子区181、182、183、184、185、186、187,相邻JFET子区之间的距离例如可在0.5um至3.0um范围,例如2.5um。相邻JFET子区被阱区130分开或隔开,因此在沿着B-B虚线的截面示意图中(图1c),看到的是连通的阱区130,而看不到JFET区180。

在图1d中,在本特定实施例中示出了七个JFET子区的杂质浓度分别示出为181A、182A、183A、184A、185A、186A、187A,而阱区130的杂质浓度为130A。JFET子区的杂质浓度与阱区的杂质浓度相同或基本相同,可实现很好的电荷平衡。

本发明人注意到,在反向偏压下,JFET区180靠近栅区160的区域的电场较强,电流较大,这会限制半导体器件的反向击穿电压或阻断电压的大小。而通过本实施例对JFET区的布图设计,可极大降低JFET区靠近栅区的电场强度,从而提高半导体器件的反向击穿电压或电压阻断能力。此外,根据本实施例的设计,为了达到相同的电压能力,JFET区的杂质浓度可更高,从而可进一步降低半导体器件的体电阻(或导通电阻),获得更高的正向电流,这对于半导体器件的应用是有利的。由此,根据本实施例的设计的半导体器件不易击穿或失效,具有更好的鲁棒性、可靠性、稳定性、以及更长的使用寿命,并且应用范围更宽,比如可用于需要大电流、大电压的电气系统中。

根据本发明的另一方面,图2示出根据本发明另一实施例的半导体器件的截面示意图。图2示出了半导体器件20、半导体层200、栅区260、顶金属层250、漏电极层270。半导体层200包括基底210和漂移区220。漂移区220中设置有阱区230和JFET区280。阱区230中设置有阱接触区232和源区240。栅区260包括栅电极262和介质层264。

与图1b相比,在图2中,JFET区280向基底220方向延伸的深度dJ小于阱区230的深度dw。在本特定实施例中,例如,dJ在0.6um至1.7um范围,dw在1.0um至2.0um范围。

根据本发明的又一方面,图3a-3c示出根据一些实施例的半导体器件的不同方面或部分的示意图。图3a是半导体器件的半导体层的顶平面视图或平面图案。图3b是沿着图3a的虚线D-D的截面示意图。注意的是,在图3b的截面示意图中,包括了栅区等。图3c例示相邻两个JFET子区。

图3b示出了半导体器件30、半导体层300、栅区360、顶金属层350、漏电极层370。半导体层300具有第一面302和第二面304。半导体层300包括基底310和漂移区320。漂移区320中设置有阱区330和JFET区380。阱区330中设置有阱接触区332和源区340,还有相邻半导体器件的源区340’。栅区360包括栅电极362和介质层364。

与图1b相比,在图3b中,JFET区380并没有与阱区330接触,而是JFET区380与阱区330被漂移区320隔开或分开。JFET区380左侧与阱区330的距离为dl,右侧与阱区330的距离为dr。根据实际需要,dl可以与dr相同或不同。在本特定实施例中,dl为0.1um至0.25um范围,dr为0.1um至0.25um范围。

参照图3a,JFET区380包括多个JFET子区。在本特定实施例中示出七个JFET子区381、382、383、384、385、386、387。相邻JFET子区被漂移区320和阱区330隔开。在顶平面视图中,每个JFET子区被漂移区320和阱区330中的任一者包围或围绕。

图3c例示JFET子区383和384的顶平面视图。二者之间的距离L1可根据实际需要灵活调整,例如在1.0um至3.0um范围。在顶平面视图中,沿着与图3a的D-D虚线相垂直的方向上,JFET子区383被漂移区320包围的尺寸分别为dt和db。dt和db可根据实际需要而调整。在本特定实施例中,dt为0.1um至0.25um范围,db为0.1um至0.25um范围。

根据本发明的再一方面,图4示出根据本发明另一实施例的半导体器件的截面示意图。图4示出了半导体器件40、半导体层400、栅区460、顶金属层450、漏电极层470。半导体层400包括基底410和漂移区420。漂移区420中设置有阱区430和JFET区480。阱区430中设置有阱接触区432和源区440。栅区460包括栅电极462和介质层464。

与图3b相比,在图4中,JFET区480向基底410方向延伸的深度小于阱区430在该方向延伸的深度。在本特定实施例中,JFET区480向基底420方向延伸的深度为0.6um至1.7um,阱区430的深度为1.0um至2.0um。

图5示出根据本发明一些实施例的半导体器件的制造方法的流程图。图5所示的制造方法例如可用来制造图1a-1d、图2、图3a-3b、或图4所例示的半导体器件。

在框51,提供半导体层。半导体层例如可以是半导体层100、200、300、或400。半导体层例如可包括基底和漂移区,漂移区可包括一层或多层外延层。半导体层可具有期望的杂质浓度。在本特定实施例中,半导体层是n型掺杂的碳化硅层。

在框52,形成阱区。例如,可利用适当的掩膜,通过单次离子注入,或多次离子注入得到期望的杂质分布。杂质分布可以是均匀或基本上均匀的,也可以具有一定的梯度。在本特定实施例中,阱区是p型掺杂,并且掺杂浓度的分布基本均匀。

在框53,形成阱接触区。阱接触区可通过离子注入形成。在本特定实施例中,通过对半导体层表面进行图案化,暴露出用于离子注入的窗口,然后进行铝离子注入形成重掺杂的p型阱接触区。

在框54,形成源区。源区可通过离子注入形成。在本特定实施例中,通过对半导体层表面进行图案化,暴露出用于离子注入的窗口,然后进行氮离子注入形成重掺杂的n型源区。

在框55,形成JFET区。可利用适当的掩膜,通过单次离子注入,或多次离子注入形成具有期望杂质分布的JFET区。JFET区的顶平面视图下的布图可设计成例如以上图1a或3a所示的布局。

在形成JFET区之后,可利用适当的工艺形成栅区和金属层以及这些层的适当封装。这些适当的工艺包括但不限于例如化学气相沉积、光刻、反应离子刻蚀、退火、注入溅射之类的金属沉积工艺、钝化等。

上述实施例只是为了例示本发明思想的目的,而非对本发明的限制。例如在图1a和图3a中,例示了七个JFET子区。本领域技术人员要理解的是,这只是为了例示本发明思想的目的。根据实际的需要,JFET子区的个数可以是二至六个,也可以是多于七个。

在上述实施例中,半导体器件例示为垂直结构的MOSFET。本领域技术人员要理解的是,其他类型的半导体器件是可能的,例如在一些实施例中,半导体器件可以是其他结构的MOSFET、绝缘栅双极晶体管(I GBT)、或其他合适类型的半导体器件。

在上述实施例中,例如图1b中,例示了半导体器件10作为最小重复单元的重复结构。本领域技术人员要理解的是,这只是出于在不损害一般性前提下,更简洁地例示本发明的思想的目的,而绝非对本发明的实施例的限制。例如,在一些实施例中,不同类型的半导体器件设置在同一半导体层上。

在上述实施例中,一般性地用碳化硅作为示例。本领域技术人员要理解的是,以上实施例的半导体层可适于其他半导体材料,例如硅、氮化镓。

以上图5示出了制造半导体器件的一个示例。本领域技术人员要理解的是,这只是出于例示的目的。图5流程图的示例也不表示给出的顺序是唯一的。例如,阱接触区、源区、JFET区的形成可以根据实际需要而适当调整。例如在一些实施例中,可以先形成JFET区,在形成阱接触区和源区。在另一些实施例中,可先形成源区,再形成阱接触区和JFET区。其他的一些组合也是可能的。

此外,虽然以上描述实施例时,使用术语诸如第一、第二等表示各个元件(例如第一面、第二面),但是可以理解的是,这些元件不应被上述术语所限制。上述术语仅用于区分一个元件和另一个元件。例如,第一元件可以被命名为第二元件,相似地,第二元件可以被命名为第一元件,上述所作之命名并不用于限制本发明的保护范围。

在上述实施例中,第一导电类型为n型,第二导电类型为p型。本领域技术人员要理解的是,第一导电类型也可以为p型,第二导电类型也可以为n型。

在上述实施例中,为例示性目的,漂移区120、220、320、420示出为仅一层。本领域技术人员要理解的是,漂移区可包括两层或更多层,例如可包括一层或多层的缓冲层、外延层、及其组合。

在以上实施例中,数据范围包括了端点。例如,在“相邻JFET子区之间的距离例如可在0.5um至3.0um范围”表述中,表示相邻JFET子区之间的距离可以是0.5um与3.0um之间的数值,也可以是0.5um或3.0um。

本领域技术人员还要理解的是,为了清楚例示的目的,在各个附图中的要素(例如元件、区域、层等)并非按照比例画出。此外,附图中的各个要素也不一定是其实际形状。例如,在以上实施例中,在截面示意图中,阱区、阱接触区、源区、JFET区示出为方形,本领域技术人员要理解的是,这些只是为了例示的目的,例如,实际的掺杂轮廓通常具有一定的过渡区或坡度或梯度,而不是梯度在某个点或边界无限大的轮廓。

此外,本领域技术人员要理解的是,以上实施例试图从不同方面例示本发明,它们并非是孤立的;而是,本领域技术人员可根据上述示例,将不同实施例进行适当的组合,以得到其他的技术方案示例。

除非另外限定,本文所使用的技术和科学术语具有作为本发明所属领域的普通技术人员通常所理解的相同的含义。在非限定性实施例中例示了本发明的实施方式。在上述公开的实施例的基础上,本领域技术人员能想到的各种变型,都落入本发明的范围。

- 具有JFET区布图设计的半导体器件

- 具有点状布图设计的半导体器件