3D NAND结构中氮化硅的蚀刻和二氧化硅的沉积控制

文献发布时间:2023-06-19 09:52:39

相关申请的交叉引用

本申请要求于2018年7月20日提交的名称为“Etching of Silicon Nitride andSilica Deposition Control in 3D NAND Structures,[3D NAND结构中的氮化硅的蚀刻和二氧化硅沉积控制]”的美国临时专利申请号62/701,398的优先权,该美国临时专利申请的披露内容通过援引以其全文明确并入本文。

技术领域

本发明涉及半导体制造和半导体装置的领域,并且更特别涉及一种用于湿法蚀刻微加工结构的方法。

背景技术

3D NAND闪存是一种闪存类型,其中存储单元垂直多层堆叠,并且这种结构代表了半导体装置制造中的独特困难。在3D NAND和其他多层结构的制造中,湿法蚀刻工艺是用于选择性去除不同材料层的重要步骤。过去,一般的趋势是使蚀刻浴的温度尽可能的高,以使得蚀刻速率高并且使得蚀刻过程尽可能短。然而,高的蚀刻速率可能导致各种问题,包括蚀刻产物在多层结构上的再沉积。

发明内容

描述了一种湿法蚀刻微加工结构的方法。该方法包括在蚀刻处理系统的槽中提供蚀刻溶液,该蚀刻处理系统被配置为控制蚀刻溶液的温度、蚀刻溶液的浓度以及蚀刻溶液在槽内的流动;将衬底浸入蚀刻溶液中,该衬底包含具有第一材料和第二材料的交替层的微加工结构,该蚀刻溶液包括蚀刻第一材料的第一酸,并以第一蚀刻速率开始第一材料的蚀刻,该第一材料的蚀刻导致要从该衬底上移除的蚀刻产物。该方法进一步包括监测蚀刻溶液内蚀刻产物的浓度,并响应于识别出蚀刻产物的浓度大于预定值,将第一蚀刻速率降低至第二蚀刻速率。

根据另一个实施例,该方法包括监测蚀刻溶液内蚀刻产物的浓度,并响应于识别出蚀刻产物的浓度下降至低于预定值,将第一蚀刻速率增加至第二蚀刻速率。

根据另一个实施例,该方法包括监测蚀刻溶液内蚀刻产物的浓度,并将蚀刻溶液内蚀刻产物的浓度维持在低于预定值,以防止蚀刻产物以阻碍通过蚀刻溶液蚀刻第一材料的量沉积在第二材料上。

附图说明

通过参考以下在结合附图考虑时的具体实施方式,由于本发明变得更好理解而将容易获得对本发明及其许多附带优点的更完整的理解,其中:

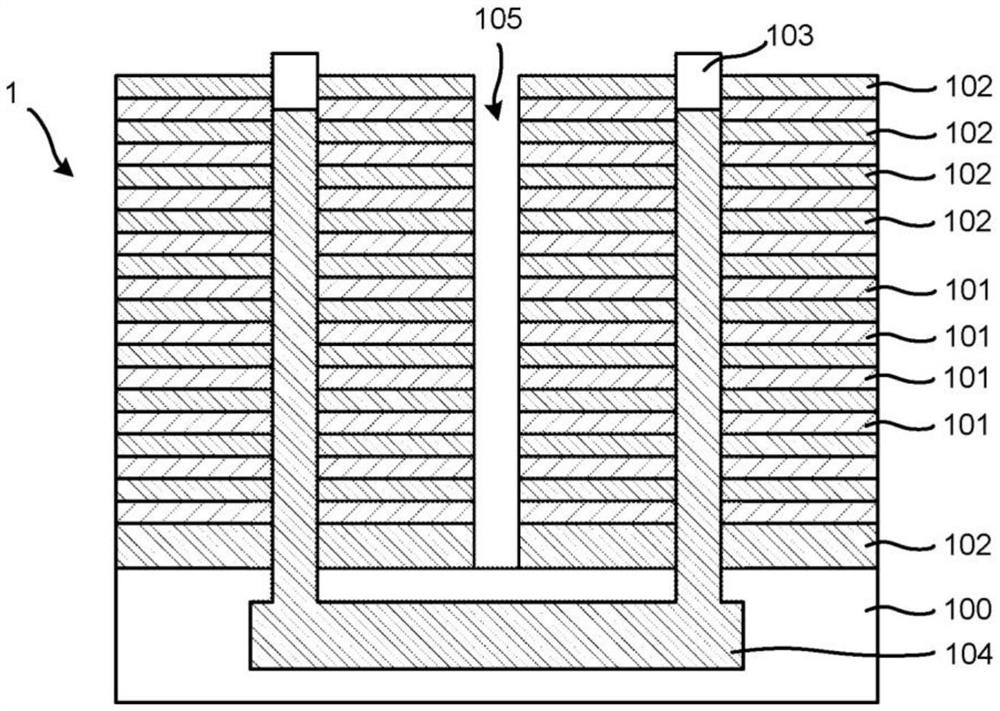

图1A和1B通过截面图示意性地示出制造3D NAND结构;

图2示出了作为根据本发明实施例的蚀刻时间的函数的微加工结构的沟槽中模拟的二氧化硅浓度对深度的关系;

图3示出了作为根据本发明实施例的蚀刻时间的函数的沟槽中模拟的二氧化硅浓度对深度的关系;

图4示出了作为根据本发明实施例的蚀刻时间的函数的沟槽中模拟的二氧化硅浓度对深度的关系;

图5示出了图2-4中包含不同数目的交替的SiN和SiO

图6示出了根据本发明实施例的包含不同数目的交替的SiN和SiO

具体实施方式

提供了一种用于蚀刻衬底的方法。该方法包括在蚀刻处理系统的槽中提供蚀刻溶液,其中该蚀刻处理系统被配置为控制蚀刻溶液的温度、蚀刻溶液的浓度以及蚀刻溶液在槽内的流动。该蚀刻处理系统可以被配置为容纳多个衬底(晶片)并使蚀刻溶液在槽中循环。该方法进一步包括将衬底浸入蚀刻溶液中,其中该衬底包含具有第一材料和第二材料的交替层的微加工结构,并且其中该蚀刻溶液包括蚀刻第一材料的酸。该方法进一步包括以第一蚀刻速率开始第一材料的蚀刻,其中该第一材料的蚀刻导致要从该衬底上移除的蚀刻产物。根据一个实施例,该方法包括监测蚀刻溶液内蚀刻产物的浓度;并响应于识别出蚀刻产物的浓度大于预定值,将第一蚀刻速率降低至第二蚀刻速率。

根据另一个实施例,该方法包括监测蚀刻溶液内蚀刻产物的浓度,并响应于识别出蚀刻产物的浓度下降至低于预定值,将第一蚀刻速率增加至第二蚀刻速率。

根据另一个实施例,该方法包括监测蚀刻溶液内蚀刻产物的浓度,其中该蚀刻溶液内蚀刻产物的浓度被维持在低于预定值,以防止蚀刻产物以阻碍通过蚀刻溶液蚀刻第一材料的量再沉积在第二材料上。

图1A示意性地示出了包含第一材料101和第二材料102的交替层的微加工结构1。通常,本发明的实施例可以应用于包含不同材料的交替层的简单或高级的微结构。根据一个实施例,微加工结构1包含部分制造的3D NAND装置。3D NAND通常通过交替层的总数目来量化。目前,3D NAND装置包含64层,但是未来的装置节点设想为包含多达96层、128层并且更多。根据一个实施例,第一材料101可以包含氮化硅(SiN)并且第二材料102可以包含氧化硅(SiO

图1B示出了在选择性地去除第一材料101的层的湿蚀刻工艺之后的微制造结构1。作为装置制造工艺的一部分,第一材料101被蚀刻掉,留下第二材料的鳍片附着在芯104上。由于在3D NAND装置中仅蚀刻SiN而保持SiO

随着在每个新的3D NAND装置节点中SiN和SiO

本发明的实施例解决了这个问题并提供了一种用于减少或消除3D NAND装置和包含不同材料的交替层的其他结构中SiO

图2示出了作为根据本发明实施例的蚀刻时间的函数的微加工结构的沟槽中模拟的二氧化硅浓度对深度的关系。晶片上的微加工结构与图1A中的结构类似,但是总共包含77个交替的SiN和SiO

图3示出了作为根据本发明实施例的蚀刻时间的函数的微加工结构的沟槽中模拟的二氧化硅浓度对深度的关系。晶片上的微加工结构与图1A中的结构类似,但是总共包含150个交替的SiN和SiO

图4示出了作为根据本发明实施例的蚀刻时间的函数的微加工结构的沟槽中模拟的二氧化硅浓度对深度的关系。晶片上的微加工结构与图1A中的结构类似,但是总共包含200个交替的SiN和SiO

图5示出了图2-4中包含不同数目的交替的SiN和SiO

在H

SiN的刻蚀速率取决于H

根据一个实施例,可以使用主动反馈控制或多个H

已经描述了用于蚀刻具有不同材料的交替层的微加工结构的方法的多个实施例。为了说明和描述的目的,已经呈现了对本发明实施例的前述描述。并不旨在穷举或将本发明限制于所披露的确切形式。本说明书和所附权利要求包括仅用于描述目的并且不应解释为进行限制的术语。相关领域的技术人员可以理解,根据以上教导,许多修改和变化是可能的。因此,意图是本发明的范围不受该详细描述限制,而是由在此所附的权利要求限制。

- 3D NAND结构中氮化硅的蚀刻和二氧化硅的沉积控制

- 在HDP-CVD沉积/蚀刻/沉积工艺中的杂质控制