连接器处理方法、装置、处理模块及电子设备

文献发布时间:2023-06-19 09:55:50

技术领域

本发明涉及数字信号处理技术领域,具体而言,涉及一种连接器处理方法、装置、处理模块及电子设备。

背景技术

在计算机领域中,存在各类连接器,用于连接其他设备或模块。对于可以兼容连接不同型号的硬件模块的连接器,若连接器同时存在长引脚与短引脚,在连接器上插或拔硬件模块期间,容易因长短脚而导致误触发热插拔中断以增加处理流程,从而影响设备的正常运行。

发明内容

本申请提供一种连接器处理方法、装置、处理模块及电子设备,能够在判断所插或所拔的硬件模块的类型时简化处理流程,有利于提高检测硬件模块类型的准确性。

为了实现上述目的,本申请实施例所提供的技术方案如下所示:

第一方面,本申请实施例提供一种连接器处理方法,应用于处理模块,所述处理模块用于与连接器连接,所述连接器包括第一类引脚及第二类引脚,所述第一类引脚的长度大于所述第二类引脚,所述方法包括:

获取所述第一类引脚的第一引脚信号及所述第二类引脚的第二引脚信号;

在当前检测时段中,当所述第一引脚信号、所述第二引脚信号中的任意引脚信号首先发生变化时,根据所述第一类引脚及所述第二类引脚在目标时刻的引脚信号,对在所述首先发生变化后的第一指定时长内的所述第一引脚信号及所述第二引脚信号进行更新,得到更新后的第一引脚信号及第二引脚信号,所述目标时刻包括在所述首先发生变化的时刻之前且与所述首先发生变化的时刻间隔第二指定时长的时刻。

在上述的实施方式中,第一指定时长通常为略大于插或拔硬件模块的时长,引脚信号首先发生变化后的第一指定时长通常包括插或拔动作所用时长。通过将引脚信号首先发生变化后的第一指定时长内第一类引脚及第二类引脚的引脚信号,重新置为在发生变化前的间隔第二指定时长时的引脚信号,可以避免在插或拔硬件模块时造成的引脚信号的波动而误触发热插拔中断,避免因热插拔中断而触发后续的误报校正处理流程,从而简化处理流程,从而有利于提高检测硬件模块类型的准确性。

结合第一方面,在一些可选的实施方式中,根据所述第一类引脚及所述第二类引脚在目标时刻的引脚信号,对在所述首先发生变化后的第一指定时长内的所述第一引脚信号及所述第二引脚信号进行更新,得到更新后的第一引脚信号及第二引脚信号,包括:

将在所述首先发生变化后的所述第一指定时长内的所述第一引脚信号更新为所述第一类引脚在所述目标时刻的引脚信号,以及将在所述首先发生变化后的所述第一指定时长内的所述第二引脚信号更新为所述第二类引脚在所述目标时刻的引脚信号。

在上述的实施方式中,在当前检测时段中,首先发生变化后的第一指定时长内包括插入或拔出硬件模块期间的时长。因此,可以将插入或拔出硬件模块期间的第一引脚信号、第二引脚信号分别更新为在插入或拔出之前的一个时刻对应的引脚信号,从而避免在插入或拔出连接器的动作期间,第一类引脚与第二类引脚的信号存在波动而造成误判,进而有利于提高判断的准确性。

结合第一方面,在一些可选的实施方式中,所述连接器用于连接硬盘,所述硬盘的类型包括SATA、U.2、SAS中的至少一种,将在所述首先发生变化后的所述第一指定时长内的所述第一引脚信号更新为所述第一类引脚在所述目标时刻的引脚信号,以及将在所述首先发生变化后的所述第一指定时长内的所述第二引脚信号更新为所述第二类引脚在所述目标时刻的引脚信号,包括:

当在所述目标时刻时所述第一类引脚和所述第二类引脚的引脚信号均为高电平信号时,将在所述首先发生变化后的所述第一指定时长内的所述第一引脚信号及所述第二引脚信号均更新为所述高电平信号;

当在所述目标时刻时所述第一类引脚和所述第二类引脚的引脚信号均为低电平信号时,将在所述首先发生变化后的所述第一指定时长内的所述第一引脚信号及所述第二引脚信号均更新为所述低电平信号;

当在所述目标时刻时所述第一类引脚的引脚信号为低电平信号,在所述目标时刻时所述第二类引脚的引脚信号为高电平信号时,将在所述首先发生变化后的所述第一指定时长内的所述第一引脚信号更新为所述低电平信号,以及将在所述首先发生变化后的所述第一指定时长内的所述第二引脚信号更新为所述高电平信号。

在上述的实施方式中,无需检测引脚信号的边沿信号属于上升沿或下降沿,可以通过简洁的逻辑运算,便可以对插入或拔出期间的引脚信号进行更新,以提高硬件模块类型检测的准确性。

结合第一方面,在一些可选的实施方式中,所述方法还包括:

根据在所述第一指定时长结束后的第一引脚信号及第二引脚信号,确定所述连接器的状态或所连接的硬件模块的类型。

在上述的实施方式中,在对插入或拔出期间的引脚信号进行更新后,再利用后期的引脚信号进行检测判断,可以提高硬件模块类型判断的准确性。

结合第一方面,在一些可选的实施方式中,所述连接器用于连接硬盘,所述硬盘的类型包括SATA、U.2、SAS中的至少一种,所述方法还包括:

在所述第一指定时长结束后,若所述第一类引脚的第一引脚信号为低电平信号,且所述第二类引脚的第二引脚信号为高电平信号,输出表示热插拔中断的中断信号。

在上述的实施方式中,若连接器接入的硬盘的类型为U.2,在第一指定时长结束后,第一类引脚的第一引脚信号便为低电平信号,且第二类引脚的第二引脚信号为高电平信号。如此,可以准确判断连接器所连接的硬盘是否为U.2SSD,从而有利于通过热插拔中断的中断信号实现U.2SSD的热插拔,避免在SATA硬盘插入时上报热插拔中断而误触发PCIe热插拔处理流程。

结合第一方面,在一些可选的实施方式中,在得到更新后的第一引脚信号及第二引脚信号之前,所述方法还包括:

判断所述第一引脚信号为第一预设信号,且第二引脚信号为第二预设信号的持续时长是否小于或等于第一指定时长;

当所述持续时长小于或等于所述第一指定时长时,在所述持续时长中确定参考时刻,所述目标时刻为在所述第一引脚信号或所述第二引脚信号发生变化的时刻之前且间隔所述第二指定时长的时刻,或者为在所述参考时刻之前且间隔第三指定时长的时刻,所述第三指定时长大于所述第一指定时长。

在上述的实施方式中,通过判断第一引脚信号为第一预设信号,且第二引脚信号为第二预设信号的持续时长是否小于或等于第一指定时长,有利于判断连接器上插或拔的硬件模块的类型。例如,若连接器用于插接U.2SSD或SATA硬盘,若第一引脚信号为低电平信号,且第二引脚信号为高电平信号的持续时长小于或等于指定时长,则可以确定所插或拔的硬盘为SATA硬盘,以便于针对SATA硬盘在插拔期间的引脚信号进行更新。

结合第一方面,在一些可选的实施方式中,当所述持续时长小于或等于所述第一指定时长时,在所述持续时长中确定参考时刻,包括:

当所述持续时长小于或等于所述第一指定时长时,将所述持续时长的开始时刻确定为所述参考时刻,或者将所述持续时长的结束时刻确定为所述参考时刻。

第二方面,本申请实施例还提供一种连接器处理装置,应用于处理模块,所述处理模块用于与连接器连接,所述连接器包括第一类引脚及第二类引脚,所述第一类引脚的长度大于所述第二类引脚,所述装置包括:

获取单元,用于获取所述第一类引脚的第一引脚信号及所述第二类引脚的第二引脚信号;

更新单元,用于在当前检测时段中,当所述第一引脚信号、所述第二引脚信号中的任意引脚信号首先发生变化时,根据所述第一类引脚及所述第二类引脚在目标时刻的引脚信号,对在所述首先发生变化后的第一指定时长内的所述第一引脚信号及所述第二引脚信号进行更新,得到更新后的第一引脚信号及第二引脚信号,所述目标时刻包括在所述首先发生变化的时刻之前且与所述首先发生变化的时刻间隔第二指定时长的时刻。

第三方面,本申请实施例还提供一种处理模块,所述处理模块包括相互耦合的存储器、处理器,所述存储器内存储计算机程序,当所述计算机程序被所述处理器执行时,使得所述处理模块执行上述的方法。

第四方面,本申请实施例还提供一种电子设备,所述电子设备包括主板模块及上述的处理模块。

第五方面,本申请实施例还提供一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机程序,当所述计算机程序在计算机上运行时,使得所述计算机执行上述的方法。

附图说明

为了更清楚地说明本申请实施例的技术方案,下面将对实施例中所需要使用的附图作简单地介绍。应当理解,以下附图仅示出了本申请的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

图1为本申请实施例提供的处理模块与连接器的示意图。

图2为本申请实施例提供的电子设备的结构示意图。

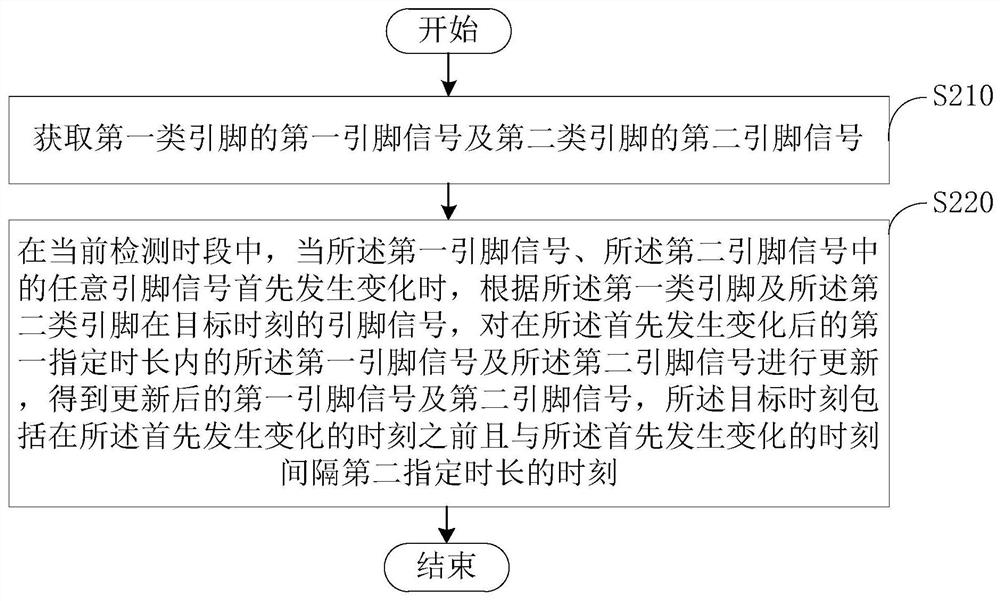

图3为本申请实施例提供的连接器处理方法的流程示意图。

图4为本申请实施例提供的第一引脚信号、第二引脚信号在更新前后的时序信号示意图。

图5为本申请实施例提供的连接器处理装置的框图。

图标:10-处理模块;11-处理器;12-存储器;20-电子设备;21-主板模块;30-连接器;100-连接器处理装置;110-获取单元;120-更新单元。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行描述。需要说明的是,术语“第一”、“第二”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

申请人发现,在服务器或计算机设备中,SFF-8639型号的硬盘连接器可以兼容连接的硬盘类型(或硬盘的接口类型)包括但不限于SATA(Serial Advanced TechnologyAttachment,串行高级技术附件,一种基于行业标准的串行硬件驱动器接口)接口、U.2接口、SAS(Serial Attached SCSI,串行SCSI)接口等,SCSI指小型计算机系统接口,英文全称为Small Computer System Interface。U.2接口的固态硬盘(Solid State Disk,SSD)可以支持热插拔,即,服务器或计算机设备在检测到连接器接入的硬盘为U.2SSD时,可以通过触发PCIe热插拔中断,以实现U.2SSD的热插拔。由于SFF-8639连接器存在的接口存在长短引脚,当在插入SATA硬盘时,在插入或拔出期间,引脚的电平信号与U.2SSD的电平信号相同,从而会触发误报U.2SSD的中断,进而误触发PCIe的热插拔流程。

鉴于上述问题,本发明申请人提出以下实施例以解决上述问题。下面结合附图,对本申请实施例作详细说明。在不冲突的情况下,下述的实施例及实施例中的特征可以相互组合。

请参照图1,本申请实施例提供一种处理模块10,可以用于与连接器30的长短引脚连接,用于对连接器30插拔硬盘期间的引脚信号进行校正,以避免因插拔硬盘过程中的引脚信号的波动误触发PCIe热插拔处理流程。

其中,处理模块10可以包括处理器11及存储器12。存储器12中存储有计算机程序。当计算机程序被处理模块10执行时,可以使得处理模块10执行下述的连接器处理方法中的各步骤。

其中,存储器12与处理器11可以集成一体,或者独立存在。例如,处理模块10可以为CPLD(Complex Programming Logic Device,复杂可编程逻辑器件)模块,可以同时包括处理器11及存储器12。

处理模块10可以与连接器30的第一类引脚(比如,图1中的“IFDET#”引脚)、第二类引脚(比如,图1中的“PRSNT#”引脚)连接,用于采集并校正第一类引脚的引脚信号、第二类引脚的引脚信号。其中,第一类引脚为连接器30的接口中较长引脚,第二类引脚为连接器30的接口中较短的引脚。

可理解地,本实施例中的连接器30的接口同时具有长短脚(或称为长短探针),连接器30的接口可以连接相应的硬件模块,所连接的硬件模块可以根据连接器30的实际种类进行确定。例如,对于SFF-8639连接器,所连接的硬件模块为硬盘。SFF-8639连接器可以兼容连接SATA硬盘、U.2SSD、SAS等硬盘。

在SFF-8639连接器中,第一类引脚为P4引脚,P4引脚的引脚信号可以称为IFDET信号,可以用“IFDET#”表示IFDET信号;第二类引脚为P10引脚,P10引脚的引脚信号可以称为PRSNT信号,可以用“PRSNT#”表示PRSNT信号,可以参见图4。P4引脚的长度大于P10引脚,为本领域技术人员所熟知。

在本实施例中,存储器12中可以固化或存储有连接器处理装置100,连接器处理装置100可以为软件功能模块,用于实现连接器处理方法中的各步骤。

请参照图2,本申请实施例还提供一种电子设备20,可以包括但不限于主板模块21及上述的处理模块10。主板模块21与处理模块10连接,可以用于与处理模块10进行数据交互。电子设备20可以是但不限于服务器、个人电脑等。其中,主板模块21可以为本领域技术人员所熟知,这里不再赘述。

请参照图3,本申请实施例还提供一种连接器处理方法,可以应用于上述的处理模块10,由处理模块10执行或实现方法的各步骤。方法可以包括以下步骤:

步骤S210,获取所述第一类引脚的第一引脚信号及所述第二类引脚的第二引脚信号;

步骤S220,在当前检测时段中,当所述第一引脚信号、所述第二引脚信号中的任意引脚信号首先发生变化时,根据所述第一类引脚及所述第二类引脚在目标时刻的引脚信号,对在所述首先发生变化后的第一指定时长内的所述第一引脚信号及所述第二引脚信号进行更新,得到更新后的第一引脚信号及第二引脚信号,所述目标时刻包括在所述首先发生变化的时刻之前且与所述首先发生变化的时刻间隔第二指定时长的时刻。

在上述的实施方式中,第一指定时长通常为略大于插或拔硬件模块的时长,引脚信号首先发生变化后的第一指定时长通常包括插或拔动作所用时长。通过将引脚信号首先发生变化后的第一指定时长内第一类引脚及第二类引脚的引脚信号,重新置为在发生变化前的间隔第二指定时长时的引脚信号,可以避免在插或拔硬件模块时造成的引脚信号的波动而误触发热插拔中断,避免因热插拔中断而触发后续的误报校正处理流程,从而简化处理流程,从而有利于提高检测硬件模块类型的准确性。

下面将对方法的各步骤进行详细阐述,如下:

在步骤S210中,处理模块可以实时接收连接器第一类引脚的引脚信号,以及实时接收第二类引脚的引脚信号。其中,第一类引脚的引脚信号即为第一引脚信号,第二类引脚的引脚信号即为第二引脚信号。第一引脚信号可以为第一类引脚中的任意一个引脚的电平信号,第二引脚信号可以为第二类引脚中任意一个引脚的电平信号。

可理解地,获取第一引脚信号及第二引脚信号的方式可以根据实际情况进行确定。例如,处理模块可以以设定的检测周期,采集第一类引脚的第一引脚信号,以及采集第二类引脚的第二引脚信号。检测周期可以根据实际情况进行确定,这里不做具体限定。

在步骤S220中,引脚信号发生变化,可理解为:引脚信号由高电平信号变为低电平信号,或者由低电平信号变为高电平信号。当前检测时段的时长通常为一个预设时长,可以根据实际情况进行确定。例如,当前检测时段可以在第一引脚信号、第二引脚信号中的任一引脚信号发生变化时触发。比如,第一引脚信号发生变化,则可以将第一引脚信号发生变化前后的预设时长作为当前检测时段。预设时长通常为较短的时长,且大于第一指定时长、第二指定时长。第一指定时长、第二指定时长通常不超过1秒,可以根据实际情况进行确定。

例如,第一指定时长可以为10毫秒、50毫秒、100毫秒等。第一指定时长可以用于表示在连接器上插/拔硬件模块时,连接器的长短引脚(第一类引脚、第二类引脚)先后与硬件模块中的探针连接的间隔时长,或者为长短引脚先后与硬件模块中的探针断开的间隔时长;或者,第一指定时长可以略大于前述的间隔时长。第二指定时长可以略大于第一指定时长。预设时长(当前检测时段)可以为1秒、2秒等时长。

示例性地,在本实施例中,可以将第一脚信号发生变化前后各1秒时段作为当前检测时段,或者,将第二脚信号发生变化前后各1秒时段作为当前检测时段,如此,可以将一个插入或拔出硬件模块的时段包括在一个检测时段中。

在当前检测时段中,第一引脚信号、第二引脚信号中的任意引脚信号首先发生变化,可理解为:在当前检测时段中,第一引脚信号、第二引脚信号可能均会发生变化,此时,首先发生变化的时刻即为第一引脚信号、第二引脚信号中最先发生变化的时刻;或者第一引脚信号与第二引脚信号中,仅有一个发生变化,此时,首先发生变化的时刻即为单个引脚信号发生变化的时刻。

作为一种可选的实施方式,步骤S120可以包括:将在所述首先发生变化后的所述第一指定时长内的所述第一引脚信号更新为所述第一类引脚在所述目标时刻的引脚信号,以及将在所述首先发生变化后的所述第一指定时长内的所述第二引脚信号更新为所述第二类引脚在所述目标时刻的引脚信号。

可理解地,硬件模块在插入连接器时,对于不同类型的硬件模块,由于连接器的高低引脚的影响,在插入或拔出连接器的动作期间,第一类引脚与第二类引脚的信号存在波动,并不可靠,插入或拔出期间的引脚信号不能作为判断硬件类型的引脚信号。在现有的处理方式中,若处理模块在插入或拔出期间,采集到第一引脚信号及第二引脚信号,此时便可能存在误判断。比如,当在插入SATA硬盘时,在插入或拔出期间,存在误触发U.2SSD中断的情况,此时会误触发PCIe热插拔流程,从而增加了处理流程。

在本申请实施例中,在当前检测时段中,引脚信号首先发生变化后的第一指定时长内包括插入或拔出硬件模块期间的时长。因此,可以将插入或拔出硬件模块期间的第一引脚信号、第二引脚信号,分别更新为在插入或拔出之前的一个时刻对应的引脚信号,从而避免在插入或拔出连接器的动作期间,第一类引脚与第二类引脚的信号存在波动。在对引脚信号进行更新矫正后,在插入或拔出连接器的动作期间,便可以提高校正后的第一类引脚与第二类引脚的引脚信号的可靠性,避免信号波动造成误判断,也就不会误触发PCIe热插拔流程,以简化引脚信号的处理流程。

作为一种可选的实施方式,所述连接器用于连接硬盘,所述硬盘的类型包括SATA、U.2、SAS中的至少一种,步骤S120可以包括:

当在所述目标时刻时所述第一类引脚和所述第二类引脚的引脚信号均为高电平信号时,将在所述首先发生变化后的所述第一指定时长内的所述第一引脚信号及所述第二引脚信号均更新为所述高电平信号;

当在所述目标时刻时所述第一类引脚和所述第二类引脚的引脚信号均为低电平信号时,将在所述首先发生变化后的所述第一指定时长内的所述第一引脚信号及所述第二引脚信号均更新为所述低电平信号;

当在所述目标时刻时所述第一类引脚的引脚信号为低电平信号,在所述目标时刻时所述第二类引脚的引脚信号为高电平信号时,将在所述首先发生变化后的所述第一指定时长内的所述第一引脚信号更新为所述低电平信号,以及将在所述首先发生变化后的所述第一指定时长内的所述第二引脚信号更新为所述高电平信号。

示例性地,请参照图4,以连接器为SFF-8639连接器,硬盘为SATA硬盘、U.2SSD为例,举例阐述步骤S120的实现过程,如下:

在图4中,A虚线对应的时刻可理解为目标时刻,即可以为在首先发生变化的时刻之前且间隔第二指定时长的时刻。B虚线对应的时刻可理解为引脚信号首先发生变化后,且与发生变化时间隔第一指定时长的时刻,图4中所示的第一指定时长即为T1或T2。在其他实施方式中,第一指定时长可以略长于T1或T2。例如,第一指定时长的起始时刻可以为F1,终止时刻可以为E线对应的时刻,E线的时刻晚于B线的时刻。F1为插入硬件模块期间引脚信号首先发生变化的时刻,F2为拔出硬件模块期间引脚信号首先发生变化的时刻。T0可以为上述的第二指定时长。T1可以为:在插入硬件模块的过程中,连接器的长引脚接触硬件模块的探针至短引脚接触硬件模块的探针期间的时长。T2可以为:在拔出硬件模块的过程中,连接器的短引脚离开硬件模块的探针至长引脚离开硬件模块的探针期间的时长。

在SATA硬盘或U.2SSD插入连接器后,处理模块可以根据连接器的P4引脚(第一类引脚)的IFDET#(第一引脚信号)和P10引脚(第二类引脚)的PRSNT#(第二引脚信号),来确定所连接的硬盘类型。若IFDET#为低电平信号(可以用数字“0”表示),PRSNT#为高电平信号(可以用数字“1”表示),则表示所接硬盘通常为U.2SSD。即,处理模块可以确定当前插入的硬盘为U.2SSD。若IFDET#和PRSNT#均为低电平信号,则表示连接器所连接的硬盘为SATA硬盘,即,处理模块可以确定当前插入的硬盘为SATA硬盘。

请再次参照图4,在对引脚信号进行更新前,若是SATA硬盘插入连接器,则在T1和T2期间,IFDET#和PRSNT#分别为0、1,此时,处理模块便会误将SATA硬盘判断为U.2SSD,从而会误触发U.2SSD的热插拔中断,进而影响SATA硬盘或电子设备的正常运行。

在对引脚信号进行更新时,对于插入动作,可以将T1期间的IFDET#和PRSNT#分别更新为在A虚线的目标时刻下的IFDET#和PRSNT#,均为1(高电平信号),从而得到更新后的IFDET#和PRSNT#,均为高电平信号,如图4中更新后的图区所示。

对于拔出动作,电子设备无需判断所拔出的硬盘的类型,可以直接将T2期间的IFDET#和PRSNT#分别更新为在C虚线的目标时刻下的IFDET#和PRSNT。例如,若C虚线的目标时刻下,IFDET#和PRSNT#均为0,则将T2期间的IFDET#和PRSNT#均更新为0。若在C虚线的目标时刻下,IFDET#为0,PRSNT#为1,则将T2期间的IFDET#更新为0,将T2期间的PRSNT#更新为1,如图4中更新后的图区所示。如此,可以通过简洁的逻辑运算,便可以对插入或拔出期间的引脚信号进行更新。在对引脚信号进行更新后,便不会出现误报U.2SSD的中断以及后期校正的情况,从而简化引脚信号的处理流程,有利于提高硬盘类型的检测的准确性。

作为一种可选的实施方式,在步骤S120中,更新首先发生变化后的第一指定时长内的第一引脚信号及第二引脚信号的方式,可以是对首先发生变化之前的第一引脚信号及第二引脚进行延迟,延迟时间为第一指定时长。即,步骤S120可以为:

将在所述首先发生变化前的所述第一引脚信号延迟第一指定时长,以及将在所述首先发生变化前的所述第二引脚信号延迟所述第一指定时长。

示例性地,请再次参照图4,在插入期间,对于SATA硬盘,可以将F1时刻的IFDET#为1,PRSNT#为1的引脚信号进行延迟,延迟时间即为第一指定时长。第一指定时长可以为T1,或者为略长于T1的时长,如此,可以确保在插入的T1期间内IFDET#为1,且PRSNT#为1,而不会出现如图4中SATA硬盘更新前的IFDET#为0,且PRSNT#为1的情况,避免因IFDET#为0,且PRSNT#为1而出现误报热插拔中断的问题。

同样地,在拔出期间,对于SATA硬盘,可以将F2时刻的IFDET#为0,PRSNT#为0的引脚信号进行延迟,延迟时间即为第一指定时长。第一指定时长可以为T2,或者为略长于T2的时长,如此,可以确保在拔出的T2期间内IFDET#为0,且PRSNT#为0,而不会出现如图4中SATA硬盘更新前的IFDET#为0,且PRSNT#为1的情况。

需要说明的是,电子设备在处理其他类型的硬盘的引脚信号时,处理过程与上述的对SATA硬盘的引脚信号的处理方式相类似,这里不再赘述。

作为一种可选的实施方式,方法还可以包括:

根据在所述第一指定时长结束后的第一引脚信号及第二引脚信号,确定所述连接器的状态或所连接的硬件模块的类型。

请再次参照图4,在本实施例中,在第一指定时长结束后,可理解为:在第一指定时长结束时至下一检测时段的第一指定时长结束时期间的任意时刻,即,可以为图4中更新后的B至D期间中的任意时刻。可以通过更新后的B至D期间中任意时刻的IFDET#(第一引脚信号)和PRSNT#(第二引脚信号),来确定当前连接器所插入的硬件模块的类型或硬盘的类型。

比如,在B至D期间,若IFDET#和PRSNT#均为0,则处理模块可以判断连接器当前插入的硬盘为SATA硬盘。

又比如,在B至D期间,若IFDET#为0,PRSNT#为1,则处理模块可以判断连接器当前插入的硬盘为U.2SSD。

若IFDET#和PRSNT#均为1,通常表示连接器未插入硬盘。

在上述的实施方式中,在对插入或拔出期间的引脚信号进行更新后,再利用后期时刻的引脚信号进行检测判断,可以提高硬件模块类型判断的准确性。

作为一种可选的实施方式,方法还可以包括:

在所述第一指定时长结束后,若所述第一类引脚的第一引脚信号为低电平信号,且所述第二类引脚的第二引脚信号为高电平信号,输出表示热插拔中断的中断信号。

可理解地,若连接器接入的硬盘的类型为U.2,在第一指定时长结束后,第一类引脚的第一引脚信号便为低电平信号,且第二类引脚的第二引脚信号为高电平信号,此时,需要向系统(比如电子设备的主板模块)上报插拔中断的中断信号,以供系统进行热插拔的中断,以使U.2SSD可以实现热插拔操作。

若处理模块确定连接器所连接的硬盘为SATA硬盘,即,在B至D期间,若IFDET#和PRSNT#均为0,此时,处理模块可以无需上报热插拔中断。

在上述的实施方式中,可以准确判断连接器所连接的硬盘是否为U.2SSD,从而有利于通过热插拔中断的中断信号实现U.2SSD的热插拔,避免在SATA硬盘插入时上报热插拔中断而影响SATA硬盘的正常运行。

在本实施例中,处理模块可以通过上述的步骤S120,实时地对第一指定时长内的第一引脚信号及第二引脚信号进行更新;或者以延迟处理的方式,对第一指定时长内的第一引脚信号及第二引脚信号进行更新,然后,再进行热插拔中断的上报处理。

例如,在实时处理时,直接将在当前检测时段中,信号发生变化后的第一指定时长内的第一引脚信号及第二引脚信号,分别更新为目标时刻的第一引脚信号及第二引脚信号,以实现引脚信号的实时更新处理。

又例如,在进行延时处理时,存储器先缓存所采集的未经处理的第一引脚信号及第二引脚信号,然后由处理模块对当前所缓存的信号发生变化后的第一指定时长内的第一引脚信号及第二引脚信号进行校正更新(即,将缓存的信号发生变化后的第一指定时长内的第一引脚信号及第二引脚信号,分别更新为目标时刻的第一引脚信号及第二引脚信号)。最后将更新后的第一引脚信号及第二引脚信号,作为是否输出表示热插拔中断的中断信号的依据。

例如,在步骤S220之前,方法还可以包括:

判断所述第一引脚信号为第一预设信号,且第二引脚信号为第二预设信号的持续时长是否小于或等于第一指定时长;

当所述持续时长小于或等于所述第一指定时长时,在所述持续时长中确定参考时刻,所述目标时刻为在所述第一引脚信号或所述第二引脚信号发生变化的时刻之前且间隔所述第二指定时长的时刻,或者为在所述参考时刻之前且间隔第三指定时长的时刻,所述第三指定时长大于所述第一指定时长。

在本实施例中,处理模块可以以较短的采集周期,采集第一类引脚的第一引脚信号及第二类引脚的第二引脚信号,以便于确定第一引脚信号为第一预设信号,且第二引脚信号为第二预设信号的持续时长。

可理解地,处理模块中的存储器或处理模块外接的存储器,可以缓存所采集的未经处理的第一类引脚的第一引脚信号及第二类引脚的第二引脚信号。缓存第一引脚信息及第二引脚信号的时长可以为上述的当前检测时段的时长。即,处理模块可以每间隔预设时长,清空存储器中之前缓存的第一引脚信号及第二引脚信号,然后将当前最近周期采集的第一引脚信号、第二引脚信号缓存于存储器中。此后,处理模块可以对当前缓存的第一引脚信号、第二引脚信号,进行分析处理。

比如:判断第一引脚信号为第一预设信号,且第二引脚信号为第二预设信号的持续时长是否小于或等于第一指定时长;当持续时长小于或等于第一指定时长时,表示当前引起信号波动的操作为插入或拔出操作(因为插拔操作引起的信号波动的时长较短);然后,将持续时长内(如图4更新前的T1或T2期间)的第一引脚信号,更新为目标时刻(如图4更新前的A时刻)的第一引脚信号;以及将持续时长内(如图4更新前的T1或T2期间)的第二引脚信号,更新为目标时刻(如图4更新前的A时刻)的第二引脚信号。最后,处理模块可以根据更新后的第一引脚信号及第二引脚信号的电平,进行分析判断。比如,更新后的第一引脚信号为低电平信号,且更新后的第二引脚信号为高电平信号,则输出表示热插拔中断的中断信号。另外,处理模块可以根据更新后的第一引脚信号和第二引脚信号的电平值,确定连接器所连接的硬件模块的类型。

在本实施例中,第一预设信号、第二预设信号可以根据实际情况进行确定。例如,对于用于连接SATA硬盘或U.2SSD的连接器,第一预设信号可以为低电平信号,第二预设信号可以为高电平信号。如此,可以检测如图4中更新前的T1或T2的时长,即为第一引脚信号为低电平信号,且第二引脚为高电平信号的持续时长。

由于在连接器上插或拔硬件模块时,若为SATA硬盘,第一引脚信号为低电平信号,且第二引脚为高电平信号的持续时长(如图4中的T1、T2)的时间较短,通常为几毫秒或几十毫秒。而若为SATA硬盘,第一引脚信号为低电平信号,且第二引脚为高电平信号的持续时长相对较长,通常超过1秒。因此,可以通过该持续时长的长短,来对插入或拔出的硬盘类型(或硬件模块类型)进行区分。其中,第一指定时长小于1秒,且大于T1和T2中的任意值,比如可以为500毫秒。

示例性地,请参照图4,若确定第一引脚信号为低电平信号,且第二引脚信号为高电平信号的持续时长小于或等于第一指定时长时,参考时刻可以为T1或T2中的任意时刻。例如,对于更新前T1期间的第一引脚信号及第二引脚信号,参考时刻可以为T1的开始时刻,或者为T1的结束时刻。目标时刻可以为在参考时刻之前且间隔第三指定时长的时刻,且第三指定时长大于第一指定时长,即,第三指定时长可以大于T1和T2中的任意值。

当需要检测持续时长时,采集周期的时长需要小于上述的第一指定时长,或者采集周期小于连接器的长短引脚先后与硬件模块中的探针连接的间隔时长,或者小于长短引脚先后与硬件模块中的探针断开的间隔时长。例如,第一指定时长为100毫秒,采集周期可以为1毫秒,处理模块可以每间隔1毫秒采集一次第一类引脚的第一引脚信号及第二类引脚的第二引脚信号。

对于第一引脚信号为低电平信号,且第二引脚信号为高电平信号的持续时长小于或等于第一指定时长时,步骤S220中,实现引脚信号的更新方式可以为前述的实现方式,即为:将在所述首先发生变化后的所述第一指定时长内的所述第一引脚信号更新为所述第一类引脚在所述目标时刻的引脚信号,以及将在所述首先发生变化后的所述第一指定时长内的所述第二引脚信号更新为所述第二类引脚在所述目标时刻的引脚信号。

或者,实现引脚信号的更新方式可以为:对于持续时长小于第一指定时长的第一引脚信号及第二引脚信号,可以利用第一类引脚在目标时刻时的引脚信号的反电平信号,更新该持续时长内的第一引脚信号;以及利用第二类引脚在目标时刻时的引脚信号的反电平信号,更新该持续时长内的第二引脚信号,无需对其他时段中的第一引脚信号、第二引脚信号进行更新。

其中,引脚信号的反电平信号可理解为:与引脚信号的电平相反的电平信号。比如,若引脚信号为高电平信号,引脚信号的反电平信号即为低电平信号;若引脚信号为低电平信号,引脚信号的反电平信号即为高电平信号。

请参照图5,本申请实施例还提供一种连接器处理装置100,可以应用于上述的处理模块中,用于执行或实现连接器处理方法中的各步骤。连接器处理装置100包括至少一个可以软件或固件(Firmware)的形式存储于存储器中或固化在处理模块操作系统(Operating System,OS)中的软件功能模块。处理模块中的处理器用于执行存储器中存储的可执行模块,例如连接器处理装置100所包括的软件功能模块及计算机程序等。

连接器处理装置100可以包括获取单元110及更新单元120,执行的操作内容可以如下:

获取单元110,用于获取所述第一类引脚的第一引脚信号及所述第二类引脚的第二引脚信号;

更新单元120,用于在当前检测时段中,当所述第一引脚信号、所述第二引脚信号中的任意引脚信号首先发生变化时,根据所述第一类引脚及所述第二类引脚在目标时刻的引脚信号,对在所述首先发生变化后的第一指定时长内的所述第一引脚信号及所述第二引脚信号进行更新,得到更新后的第一引脚信号及第二引脚信号,所述目标时刻包括在所述首先发生变化的时刻之前且与所述首先发生变化的时刻间隔第二指定时长的时刻。

可选地,更新单元120还可以用于:将在所述首先发生变化后的所述第一指定时长内的所述第一引脚信号更新为所述第一类引脚在所述目标时刻的引脚信号,以及将在所述首先发生变化后的所述第一指定时长内的所述第二引脚信号更新为所述第二类引脚在所述目标时刻的引脚信号。

可选地,所述连接器用于连接硬盘,所述硬盘的类型包括SATA、U.2、SAS中的至少一种,更新单元120还可以用于:

当在所述目标时刻时所述第一类引脚和所述第二类引脚的引脚信号均为高电平信号时,将在所述首先发生变化后的所述第一指定时长内的所述第一引脚信号及所述第二引脚信号均更新为所述高电平信号;

当在所述目标时刻时所述第一类引脚和所述第二类引脚的引脚信号均为低电平信号时,将在所述首先发生变化后的所述第一指定时长内的所述第一引脚信号及所述第二引脚信号均更新为所述低电平信号;

当在所述目标时刻时所述第一类引脚的引脚信号为低电平信号,在所述目标时刻时所述第二类引脚的引脚信号为高电平信号时,将在所述首先发生变化后的所述第一指定时长内的所述第一引脚信号更新为所述低电平信号,以及将在所述首先发生变化后的所述第一指定时长内的所述第二引脚信号更新为所述高电平信号。

可选地,连接器处理装置100还可以包括类型确定单元,用于根据在所述第一指定时长结束后的第一引脚信号及第二引脚信号,确定所述连接器的状态或所连接的硬件模块的类型。

可选地,所述硬盘的类型包括SATA、U.2、SAS中的至少一种,连接器处理装置100还可以包括中断上报单元,用于在所述第一指定时长结束后,若所述第一类引脚的第一引脚信号为低电平信号,且所述第二类引脚的第二引脚信号为高电平信号,输出表示热插拔中断的中断信号。

可选地,连接器处理装置100还可以包括判断单元及参考时刻确定单元。在更新单元120执行步骤S220之前,判断单元用于:判断所述第一引脚信号为第一预设信号,且第二引脚为第二预设信号的持续时长是否小于或等于第一指定时长。参考时刻确定单元用于:当所述持续时长小于或等于所述第一指定时长时,在所述持续时长中确定参考时刻,所述目标时刻为在所述首先发生变化的时刻之前且间隔所述第二指定时长的时刻,或者为在所述参考时刻之前且间隔第三指定时长的时刻,所述第三指定时长大于所述第一指定时长。

可选地,参考时刻确定单元还用于:当所述持续时长小于或等于所述第一指定时长时,将所述持续时长的开始时刻确定为所述参考时刻,或者将所述持续时长的结束时刻确定为所述参考时刻。

在本实施例中,处理器可以是一种集成电路芯片,具有信号的处理能力。上述处理器可以是通用处理器。例如,该处理器可以是中央处理器(Central Processing Unit,CPU)、数字信号处理器(Digital Signal Processing,DSP)、专用集成电路(ApplicationSpecific Integrated Circuit,ASIC)、现场可编程门阵列(Field-Programmable GateArray,FPGA)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件,可以实现或者执行本申请实施例中的公开的各方法、步骤及逻辑框图。

存储器可以是,但不限于,随机存取存储器,只读存储器,可编程只读存储器,可擦除可编程只读存储器,电可擦除可编程只读存储器等。在本实施例中,存储器可以用于存储第一引脚信号、第二引脚信号与硬件模块类型的对应关系、第一指定时长、第二指定时长等。当然,存储器还可以用于存储程序,处理器在接收到执行指令后,执行该程序。

可以理解的是,图1所示的结构仅为处理模块的一种结构示意图,处理模块还可以包括比图1所示更多的组件。图1中所示的各组件可以采用硬件、软件或其组合实现。

需要说明的是,所属领域的技术人员可以清楚地了解到,为描述的方便和简洁,上述描述的处理模块、电子设备、连接器处理装置100的具体工作过程,可以参考前述方法中的各步骤对应过程,在此不再过多赘述。

本申请实施例还提供一种计算机可读存储介质。可读存储介质中存储有计算机程序,当计算机程序在计算机上运行时,使得计算机执行如上述实施例中所述的连接器处理方法。

通过以上的实施方式的描述,本领域的技术人员可以清楚地了解到本申请可以通过硬件实现,也可以借助软件加必要的通用硬件平台的方式来实现,基于这样的理解,本申请的技术方案可以以软件产品的形式体现出来,该软件产品可以存储在一个非易失性存储介质(可以是CD-ROM,U盘,移动硬盘等)中,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行本申请各个实施场景所述的方法。

综上所述,本申请提供一种连接器处理方法、装置、处理模块及电子设备。方法包括:获取第一类引脚的第一引脚信号及第二类引脚的第二引脚信号;在当前检测时段中,当第一引脚信号、第二引脚信号中的任意引脚信号首先发生变化时,根据第一类引脚及第二类引脚在目标时刻的引脚信号,对在首先发生变化后的第一指定时长内的第一引脚信号及第二引脚信号进行更新,得到更新后的第一引脚信号及第二引脚信号,目标时刻包括在首先发生变化的时刻之前且间隔第二指定时长的时刻。在本方案中,第一指定时长通常为略大于插或拔硬件模块的时长,引脚信号首先发生变化后的第一指定时长通常包括插或拔动作所用时长。通过将引脚信号首先发生变化后的第一指定时长内第一类引脚及第二类引脚的引脚信号重新置为在发生变化前的第二指定时长的引脚信号,可以避免在插或拔硬件模块时造成的引脚信号的波动而误触发热插拔中断,避免因热插拔中断而触发后续的误报校正处理流程,从而简化处理流程,从而有利于提高检测硬件模块类型的准确性。

在本申请所提供的实施例中,应该理解到,所揭露的装置、系统和方法,也可以通过其它的方式实现。以上所描述的装置、系统和方法实施例仅仅是示意性的,例如,附图中的流程图和框图显示了根据本申请的多个实施例的系统、方法和计算机程序产品的可能实现的体系架构、功能和操作。在这点上,流程图或框图中的每个方框可以代表一个模块、程序段或代码的一部分,所述模块、程序段或代码的一部分包含一个或多个用于实现规定的逻辑功能的可执行指令。也要注意的是,框图和/或流程图中的每个方框、以及框图和/或流程图中的方框的组合,可以用执行规定的功能或动作的专用的基于硬件的系统来实现,或者可以用专用硬件与计算机指令的组合来实现。另外,在本申请各个实施例中的各功能模块可以集成在一起形成一个独立的部分,也可以是各个模块单独存在,也可以两个或两个以上模块集成形成一个独立的部分。

以上所述仅为本申请的优选实施例而已,并不用于限制本申请,对于本领域的技术人员来说,本申请可以有各种更改和变化。凡在本申请的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本申请的保护范围之内。

- 连接器处理方法、装置、处理模块及电子设备

- 应用程序的隐私模块处理方法、装置、电子设备及介质