以太网接口和相关系统、方法和设备

文献发布时间:2023-06-19 10:00:31

技术领域

公开的实施方案总体涉及以太网,并且更具体地,一些实施方案涉及以太网接口。

背景技术

互连件被广泛用于促进网络的设备之间的通信。一般来说,电信号在物理介质(例如,总线、同轴电缆或双绞线-但通常简称为“线路”)上通过被耦接到物理介质的设备传输。

根据开放式系统互连模型(OSI模型),基于以太网的计算机联网技术使用基带传输(即,电信号为离散的电脉冲)来传输数据包以及最终传送在网络设备之间传送的消息。根据OSI模型,称为物理层(PHY)设备的专用电路或控制器用于在线路的模拟域与数据链路层(本文中也仅称为“链路层”)的根据分组信令操作的数字域之间进行交互。虽然数据链路层可包括一个或多个子层,但在基于以太网的计算机网络中,数据链路层通常包括至少介质访问控制(MAC)层,所述介质访问控制(MAC)层提供物理层的控制抽象。以举例的方式,当将数据传输至网络上的另一设备时,MAC控制器可为物理介质准备帧、添加纠错元素并实现避免冲突。此外,当从另一个设备接收数据时,MAC控制器可确保所接收数据的完整性,并为较高层准备帧。

存在各种网络拓扑,所述网络拓扑实现物理层和链路层(并且可包括不限于其他层)。自九十年代初期以来,外围部件互连(PCI)标准和并行高级技术附件(并行ATA)均可以实现多站总线拓扑。自2000年代初以来的趋势是使用点对点总线拓扑,例如PCI Express标准和串行ATA(SATA)标准实施点到点拓扑。

典型的点到点总线拓扑可实现每个设备之间的线路(例如,专用点到点)或设备与交换机之间的线路(例如,不限于切换的点对点)。在多站拓扑中,物理介质是共享总线,并且每个网络设备例如经由基于物理介质类型(例如不限于同轴电缆或双绞线)而选择的电路耦接到共享总线。

点到点总线拓扑(诸如专用的点到点拓扑或交换点到点拓扑)需要比多站拓扑更多的电线和更昂贵的材料,这部分是由于设备之间的链路数较多。在某些应用(诸如汽车)中,可能存在使得难以直接连接设备的物理约束,因此在网络或子网络中不需要或不需要尽可能多的直接连接(例如,不限于多站拓扑)的拓扑可能不太容易受到此类约束的影响。

基带网络上的设备(例如,不限于多站网络)共享相同的物理传输介质,并且通常使用该介质的整个带宽进行传输(换句话说,用于基带传输的数字信号占用介质的整个带宽)。因此,在给定的时刻,仅基带网络上的一个设备可传输。因此,介质访问控制方法用于处理共享传输介质的争用。

附图说明

为了容易地识别对任何特定元素或行为的讨论,参考标记中最重要的一个或多个数字是指首次引入该元素的图号。

图1示出了根据一个或多个实施方案的网络段。

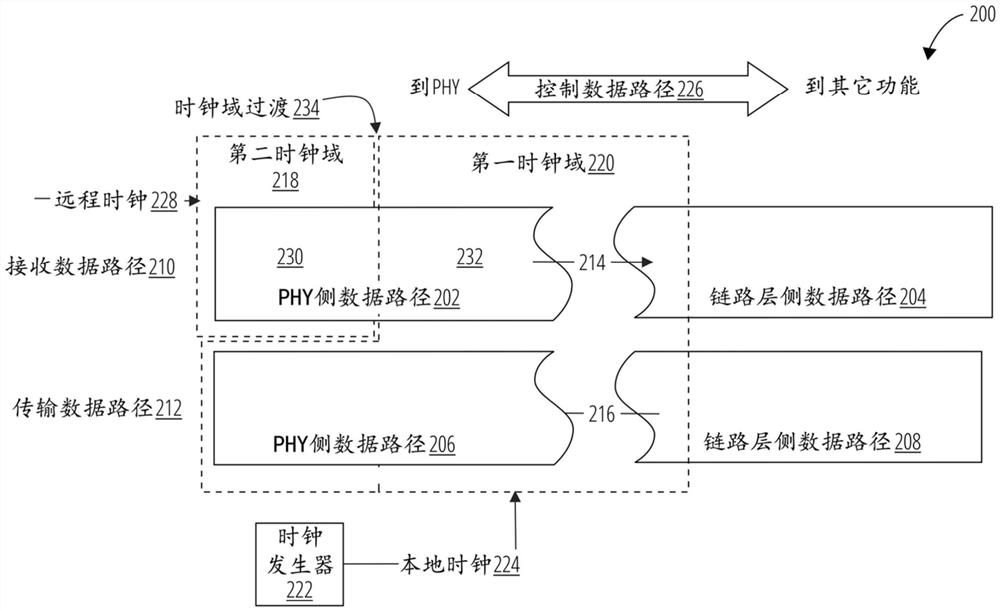

图2示出了根据一个或多个实施方案的实现公共时钟接口的系统的框图。

图3示出了用于实现通用时钟接口系统(诸如图2所示的系统)的系统的实施方案的框图。

图4示出了根据一个或多个实施方案的过程的流程图。

具体实施方式

在以下详细说明中,参考了形成本公开的一部分的附图,并且在附图中以举例说明的方式示出了可实践本公开的具体示例性实施方案。充分详细地描述了这些实施方案,以使本领域的普通技术人员能够实践本公开。然而,可利用其他实施方案,并且可在不脱离本公开的范围的情况下进行结构、材料和工艺变化。

本文所呈现的图示并不旨在为任何特定方法、系统、设备或结构的实际视图,而仅仅是用于描述本公开的实施方案的理想化表示。本文所呈现的附图未必按比例绘制。为了读者的方便,各附图中的类似结构或部件可保持相同或相似的编号;然而,编号的相似性并不意味着所述结构或部件在尺寸、组成、配置或任何其它特性方面必须是相同的。

应当容易理解,如本文一般所述并且在附图中示出的实施方案的部件可被布置和设计成多种不同的配置。因此,以下对各种实施方案的描述并不旨在限制本公开的范围,而是仅代表各种实施方案。

以下描述可包括示例,以帮助本领域的普通技术人员实践所公开的实施方案。术语“示例性的”、“通过举例”和“例如”的使用是指相关的描述是说明性的,虽然本公开的范围旨在涵盖示例和法律等同形式,但使用此类术语并不旨在将实施方案或本公开的范围限制于指定的部件、步骤、特征或功能等。

因此,所示出和描述的具体实现方式仅为示例,并且不应理解为实施本公开的唯一方式,除非本文另外指明。元件、电路和功能可以框图形式示出,以便以不必要的细节模糊本公开。相反,所示出和描述的具体实现方式仅为示例性的,并且不应理解为实施本公开的唯一方式,除非本文另外指明。另外,块定义和各个块之间逻辑的分区是示例性特定实现方式。对于本领域的普通技术人员将显而易见的是,本公开可通过许多其他分区解决方案来实践。在大多数情况下,省略了关于定时考虑等的细节,其中不需要此类细节来获得本公开的完全理解,并且是在相关领域的普通技术人员的能力范围内。

本文所述的信息和信号可使用多种不同技术和技法中的任一种来表示。例如,可在整个说明书中引用的数据、指令、命令、信息、信号、位和符号可由电压、电流、电磁波、磁场或粒子、光学场或粒子或它们的任何组合表示。为了清晰地呈现和描述,一些附图可以将信号示出为单个信号。本领域的普通技术人员应当理解,信号可表示信号总线,其中总线可具有多种位宽度,并且本公开可对包括单个数据信号在内的任意数量的数据信号实现。

如本文所用,涉及给定参数、特性或条件的术语“基本上”和“大约”是指并且包括在本领域的普通技术人员将理解给定参数、特性或条件满足一定程度的方差(诸如在可接受的制造公差内)的程度。例如,基本上或约为指定值的参数可是指定值的至少约90%,指定值的至少约95%、指定值的至少约99%或指定值的甚至至少约99.9%。

应当理解,除非明确说明此类限制,否则使用诸如“第一”、“第二”等的名称对本文中的元件的任何引用并不因此限制那些元件的数量或顺序。相反,本文将这些命名用作两个或更多个元件或元件的实例进行区分的便利方法。因此,引用的第一元件和第二元件并不意味着只能使用两个元件,或者第一元件必须以某种方式在第二元件之前。另外,除非另有说明,一组元件可包括一个或多个元件。同样,有时单数形式所指的元件也可包括该元件的一个或多个实例。

结合本文所公开的实施方案描述的各种示例性逻辑块、模块和电路可使用通用处理器、专用处理器、数字信号处理器(DSP)、专用集成电路(ASIC)、现场可编程门阵列(FPGA)或其他可编程逻辑设备、离散栅极或晶体管逻辑、离散硬件部件或它们的任何组合来实现或实施,以执行本文所描述的功能。通用处理器(在本文中也可称为主机处理器或简单地称为主机)可以是微处理器,但另外地,处理器可以是任何常规处理器、控制器、微控制器或状态机。处理器也可实现为计算设备的组合,诸如DSP和微处理器的组合、多个微处理器、与DSP核心结合的一个或多个微处理器或任何其他此类配置。包括处理器的通用计算机被认为是专用计算机,而通用计算机被配置为执行与本公开的实施方案相关的计算指令(例如,软件代码)。

另外,应当指出的是,可根据被描绘为流程图、流程示意图、结构图或框图的过程来描述实施方案。虽然流程图可将操作行为描述为顺序过程,但是这些动作中的许多可在另一序列中、并行地或基本上同时地执行。此外,可重新安排行为的顺序。过程可不受限制地对应于方法、线程、函数、过程、子例程或子程序。此外,本文所公开的方法可以在硬件、软件或两者中实现。如果在软件中实现,所述功能可作为一个或多个指令或代码存储或传输到计算机可读介质上。计算机可读介质包括计算机存储介质和通信介质,所述通信介质包括有利于将计算机程序从一个位置传输到另一个位置的任何介质。

在所公开的实施方案中,除非另外指明,否则冲突应被理解为是指逻辑冲突(即,预测实际冲突,但两个或更多个节点实际上不同时在共享传输介质上传输信号)。

可以在物理层处执行协议以进行介质访问调整。例如,10SPE(即,10Mbps单对以太网)是当前由电气和电子工程师学会(IEEE)开发为IEEE802.3cg

可在PHY中实现其他介质访问调谐协议,包括时间感知协议和流量整形协议。一般来说,时间感知协议是一种协议,其中根据计划表或使用调度的调度器在一段时间内授予或抑制介质访问。一般来说,流量整形协议是至少部分地基于性能水平、服务质量或投资回报而授予或抑制介质访问(另外地或除了冲突避免和/或时间感知协议之外)的协议。作为非限制性示例,流量整形可涉及将流量类型或流量流的类型(例如,不限于时间敏感数据、最佳努力数据、低优先级或无优先级数据)划分优先级。

一般来说,PHY与MAC(例如,不限于介质独立接口(MII)或减少的介质独立接口(RMII))之间的接口指定在设备之间发送的特定信号。为了符合这些规范,实现PHY或MAC的设备(例如,不限于微芯片和微控制器)将通常包括引脚,所述引脚被分配给指定信号。例如,除了用于接收数据的数据线(RXD)之外,MII PHY还可包括用于信令有效接收数据(RXDV)、用于信令载波活动(CRS)、用于信令有效传输数据(TX_EN)、接收参考时钟(RX_CLK)、传输参考时钟(TX_CLK)的引脚、以及用于信令管理数据(MDIO)的引脚,并传输数据(TXD)。根据实现方式,可指定PHY和MAC的相应输入引脚和输出引脚以用于对这些信号中的一个信号进行独占信令,或不完全地信令这些信号中的两个或更多个。

本公开的发明人认识到在MAC与PHY之间、控制器与PHY之间或仅在网络协议栈和PHY中的其他设备之间进行信令的需要。虽然可将更多的引脚添加到芯片,但成本(例如,不限于以货币、时间和物理空间中的一者或多者)与设备之间的一些引脚和/或互连件成比例地增加,并且期望限制成本。还可以更改信令,但应小心执行此类更改,因为符合接口规范是提高以太网设备(包括PHY设备和链路层设备)互操作性和可预测性的重要方式。

就用于连接链路层和共享总线的典型PHY而言,接收数据路径(用于将接收数据从共享总线移动到链路层的电路)通常在与传输数据路径(用于将传输数据从链路层至链路层移动至共享总线的电路)和接口不同的时钟域中操作,所述接口可操作地耦接PHY和链路层。作为非限制性示例,在10SPE PHY的情况下,接收数据路径在远程时钟域中,即,发送接收数据的远程设备的远程时钟的时钟域。远程时钟从接收数据中恢复,并跨越具有接收数据的接口提供给MAC。在将接收数据跨越接口发送到与MAC的时钟域同步的链路层之前,不会使接收数据与新的时钟域同步。同时,传输数据路径和接口在本地时钟域中操作,即PHY的本地时钟的时钟域。

如上所述,为了针对传输数据路径和接收数据路径实现不同时钟域,PHY提供两个参考时钟、链路层、用于接收数据路径的时钟域的接收参考时钟(例如,RX_CLK)以及用于传输数据路径的时钟域的传输参考时钟(例如,TX_CLK)。例如,MAC可使用接收参考时钟将接收数据帧同步到其时钟域,并使用传输参考时钟将传输数据帧同步到PHY的本地时钟域。

在希望在PHY处实现介质访问调谐之前,对于具有在不同时钟域中操作的接收数据路径和传输数据路径的缺点(如果有的话)通常不超过将用于域跨的电路添加到接收路径的缺点(例如,不限于成本、功率、与定时相关的设计问题)。然而,本公开的发明人认识到,具有用于PHY侧接收数据路径和PHY侧传输数据路径的公共时钟域将释放用于信令的一个或多个引脚,包括但不限于介质访问调谐或附加控制数据路径。

一个或多个实施方案通常涉及在同一时钟域中操作PHY侧接收数据路径和PHY侧发射数据路径。在一个实施方案中,PHY侧接收数据路径可包括同步电路,并且同步电路可被配置为在接收数据路径处启用从第二时钟域(例如,远程时钟域)到第一时钟域(例如,本地时钟域)的域跨。将PHY可操作地耦接到链路层的传输数据路径和接口也可在同一时钟域(例如,第一时钟域)中操作。

一个或多个实施方案通常涉及多站网络段的节点的网络协议栈,所述网络协议栈在设备之间实现控制数据路径和/或网络协议栈和PHY的功能。在一个实施方案中,PHY可包括一个或多个引脚,用于通过控制数据路径发送和/或接收控制数据。在一个实施方案中,控制数据可用于在PHY处实现介质访问调谐的方面。在另一个实施方案中,控制数据可用于过滤以太网数据包的类型(例如,不限于使用标准以太网数据包的类型字段中的信息)。

图1示出了网络段100的功能框图,所述网络段100包括链路层设备、MAC 104和物理层(PHY)设备以及PHY 102。作为非限制性示例,网络段100可以是多站网络的段、多站子网络的段、是混合介质网络的段的多站总线、或它们的组合或子组合。作为非限制性示例,网络段100可为、部分可为或包括以下中的一者或多者:微控制器类型嵌入式系统,用户类型计算机,计算机服务器,笔记本计算机,平板电脑,手持设备,移动设备,无线耳塞设备或耳机设备,有线耳塞或耳机设备,设备子系统,照明子系统,音响子系统,建筑物控制系统,住宅监测系统(例如,不限于用于安全或公用事业),电梯系统或子系统,公共交通控制系统(例如,不限于用于地上火车,地下火车,小车或公共汽车),汽车系统或汽车子系统,或工业控制系统。

PHY 102通常被配置为与MAC 104接口。作为非限制性示例,PHY102和/或MAC 104可为芯片包装,所述芯片包装包括存储器和/或逻辑,所述存储器和/或逻辑被配置用于执行本文所述的实施方案的全部或一部分。作为非限制性示例,PHY 102和MAC 104可分别在单个芯片包装(例如,包装中的系统(SIP))中实现为单独的芯片封装或电路(例如,集成电路)。

PHY 102通常被配置为与共享传输介质108和物理介质接口,该物理介质为用于节点的通信路径,所述节点为例如网络段100的一部分或该网络段100为其一部分的网络,包括具有相应PHY 102和MAC 104的节点。作为一个非限制性示例,共享传输介质108可以是单双绞线,诸如用于单对以太网。

在一个或多个实施方案中,PHY 102被配置为执行介质访问调谐。在一个或多个实施方案中,MAC 104被配置为流量感知的,并且更具体地,被配置为实现冲突检测和/或避免协议。在一个实施方案中,MAC 104被配置为执行载波感测多重存取(CSMA)。更具体地,MAC104被配置为检查共享传输介质108上的载波,并且如果其检测到载波,则其在开始数据传输之前等待直到没有载波(即,信道是空闲)检测到。

在图1所示的实施方案中,网络段100还包括一个或多个其他功能106。作为非限制性示例,其他功能106可是网络协议栈的链路层或其他层、实现网络协议栈的一个或多个层的设备、或作为子系统的一部分的设备的功能。

图2为根据一个或多个实施方案的实现用于接收数据路径和传输数据路径的公共时钟的系统200的框图。系统200可包括接收数据路径210和传输数据路径212。

在图2的实施方案中,系统200包括至少两个时钟域即第一时钟域220和第二时钟域218。第一时钟域220对应于在图1的PHY 102处生成的本地时钟224的时钟速率。第二时钟域218对应于远程时钟228的时钟速率,例如,除包括系统200的节点之外的节点的时钟速率。

对于接收数据路径210,数据路径202的PHY侧和PHY侧数据路径206的第二部分232在同一时钟域中,此处为第一时钟域220。第一接口214可操作地将数据路径202的PHY侧耦接到链路层侧数据路径204,并且第二接口216可操作地将链路层侧数据路径208耦接到PHY侧数据路径206。第一接口214和第二接口216也在第一时钟域220中。

数据路径202的PHY侧的第一部分230在第二时钟域218中。在图2的实施方案中,第二时钟域218可以是与远程时钟228相关联的远程时钟域。作为非限制性示例,远程时钟228表示在远程节点的远程PHY处使用的时钟,该远程节点发送接收数据路径210上的接收数据。如本文所讨论,远程时钟228不一定在系统200或系统300处恢复。

时钟域过渡234存在于数据路径202的PHY侧的第一部分230与第二部分232之间,并且是在数据路径202的PHY侧处从第二时钟域218到第一时钟域220的时钟域跨。

在各种实施方案中,链路层侧数据路径204和链路层侧数据路径208可在与第一时钟域220相同或不同的时钟域中。

如上所述,在一个或多个实施方案中,系统200可包括时钟发生器222。在一个实施方案中,时钟发生器222被配置为将本地时钟224提供给第一时钟域202,并且更具体地讲,提供给数据路径202的PHY侧和数据路径206的PHY侧。

在一个或多个实施方案中,系统200可包括可在第三数据路径,这里,未示出可在第一时钟域220或另一个时钟域中操作的控制数据路径226。控制数据路径226可被配置为将控制数据在物理层之间往返移动,例如在PHY 102和图1的其他功能106之间移动。在一个实施方案中,可在系统200处执行一个或多个控制循环时使用控制数据路径226。

在所公开的实施方案的预期使用情况下,第一时钟域220和第二时钟域218的相应时钟速率可是相同或不同的时钟速率。

图3示出了用于在例如图2的系统200中实现同一时钟域中的接收数据路径和传输数据路径的系统300的实施方案的框图。

在一个或多个实施方案中,系统300可包括PHY 302和链路层308。PHY 302和链路层308通过接收接口336和传输接口338可操作地耦接。在一个实施方案中,接收接口336和传输接口338可包括用于实现指定接口中的一些或全部接口的PHY 302和链路层308的引脚、互连件和相应电路。

在一个实施方案中,指定接口可指定从PHY 302到链路层308(例如,不限于MII接口)的独占冲突避免信令。独占信令是用于一个特殊目的的信令(例如,不限于用于指示具体条件),并且独占冲突避免信令是用于专用指示在可操作地耦接到接口电路328的共享传输介质处检测到的冲突的信令。在该实施方案中,接收接口336的PHY侧和MAC侧可各自包括相应引脚,所述相应引脚分配用于独占冲突避免信令(在PHY的情况下是输出端并且在MAC的情况下是输入端)。PHY 302还可包括被配置用于独占冲突避免信令的电路,并且链路层308可包括用于使用独占冲突避免信令来执行避免冲突的电路。在图3的实施方案中,PHY包括用于冲突避免信号的独占性信令的输出360。更具体地,PHY 302可被配置为生成独占的避免冲突信号,并通过输出端360和冲突信令线362向链路层308提供信号。

在一个或多个实施方案中,PHY 302可包括接收数据路径304、传输数据路径306、参考时钟发生器334和接口电路328。接口电路328被配置为将PHY 302可操作地耦接到共享传输介质(例如,共享传输介质108),并且更具体地,被配置为可操作地将相应的接收数据路径304和传输数据路径306耦接至共享传输介质。作为一个非限制性示例,接口电路328可以是介质相关接口(MDI),所述介质相关接口(MDI)被配置为可操作地耦接到单对以太网型电缆。

接收数据路径304通常可被配置为将接收数据从共享传输介质移动到链路层,并且可包括用于在PHY 302处朝向链路层308移动接收数据的电路。传输数据路径306通常可被配置为将传输数据从链路层移动到共享传输介质,并且可包括用于将PHY 302处的传输数据移动远离链路层308的电路。

在一个或多个实施方案中,接收数据路径304可包括接收器310、过采样件314、数字时钟和数据恢复(DCDR)与同步(sync)件(即,DCDR与sync件316)、对准和解码件318、以及接收缓冲器320。

在数据接收的情况下,在接收器310处接收模拟输入数据流,然后通过过采样件314对其进行过采样。过采样件314的采样率可至少部分地基于本地参考时钟342(例如,不限于使用响应于本地参考时钟342而生成的正交分量)。在大多数情况下,输入数据流的近似速率将是已知的,因此在一些实施方案中,振荡器344的频率可被选择为输入数据流的频率的倍数(即,偶数或奇数倍)。

向DCDR与sync件316提供过采样的数据,该DCDR与sync件316执行数字时钟和数据恢复,并且将恢复的数据(即,接收数据)同步到本地时钟340。本地时钟340由时钟分频器330生成,时钟分频器330被配置为接收本地参考时钟342,并响应于本地参考时钟342生成分路时钟。因此,本地参考时钟342的频率是本地时钟340的频率的整数倍(偶数或奇数)。因此,当在DCDR与sync件316处接收到本地时钟342时,过量采样的数据立即与本地时钟340同步(实际上其可被认为通过同步到本地参考时钟342和本地时钟340的采样率而被呈现为同步的),并且本地时钟340可用作由DCDR与sync件316的DCDR接收从过采样数据恢复的数据的恢复时钟。提供未对准的接收数据至对准&解码件318,该对准&解码件被配置为通过在DCDR与sync件316提供的未对准接收数据上执行符号对齐来提供恢复的数据。恢复的数据(即,接收数据)存储在接收缓冲器320处,以等待通过接收接口336被发送到链路层308。

在一个或多个实施方案中,参考时钟发生器334被配置为基于晶体振荡器(此处为晶体振荡器344)来生成本地参考时钟342。在一个实施方案中,可将晶体振荡器344的频率选择为与耦接到接口电路328的共享传输介质相关联的预期频率的倍数(偶数或奇数倍)。作为非限制性示例,对于在10SPE以太网中使用的绞线单对型电缆,传输频率可为12.5兆赫,晶体振荡器344的频率可为25兆赫,本地参考时钟342的频率可为5兆赫,并且本地时钟340的频率可为2.5兆赫。

本地参考时钟342被提供给过采样件314,该过采样件314被配置为使用本地参考时钟342对包括来自共享传输介质的接收数据的信号进行过采样。在图3所示的实施方案中,任选地提供本地参考时钟342,以传输用于向共享传输介质发送传输数据的数据路径306。

如上所述,时钟分频器330被配置为响应于本地参考时钟342来生成本地时钟340。在一个实施方案中,时钟分频器330被配置为响应于一个或多个控制位(未示出)来划分本地参考时钟342。在一个实施方案中,控制位可以是设置整数除数的一个或多个位,该整数除数限定本地参考时钟342与本地时钟340之间的关系。在一个实施方案中,控制位可由用户设置(例如,不限于使用设计界面编程)和/或控制位可由控制器设置,即实现网络协议栈(作为非限制性示例,链路层)的一个或多个部分的微控制器。

在一个或多个实施方案中,在其他线路中,接收接口336可包括输出端350、接收参考时钟线322、接收数据行312和接收时钟输入端354。此外,传输接口338可包括传输参考时钟线326和传输参考传输时钟输入端356。本地时钟340通过参考时钟线324和接收接口336的输出端350被提供至接收参考时钟线322和传输参考时钟线336。此外,本地时钟340分别在接收接口336和传输接口338处被提供至接收时钟输入端354和传输时钟输入端354(链路层308的每个输入端)。作为非限制性示例,在各种实施方案中,参考时钟线324可包括一条或多条粘结线或集成导体。

值得注意的是,接收接口336处的数据的比特率和在传输接口338处的比特率可相同。此外,接收接口336和传输接口338的相应比特率可与由接收接口336和传输接口336实现的接口定义中所指定的比特率相同或较慢。

在预期的使用例中,由接收接口336和传输接口338实现的接口可指定PHY 302应为传输数据路径和接收数据路径中的每一者提供时钟。由于在所公开的实施方案中,接收接口336和传输接口338在公共时钟即本地时钟340上操作,因此接收参考时钟线322和传输参考时钟线326可由同一条线路,即参考时钟线324来驱动。在该示例中,此类布置在PHY302处释放输入端—在此处是输入端348和输入端358。

在一些实施方案中,输入端348可用于实现PHY 302与功能(例如,图1的其他功能106)之间的控制数据路径(例如,用于控制信令),所述功能在链路层308之外的某个位置定位(例如,不限于在设备和/或子层中实现)。换句话讲,输入端348可用于实现与接收接口336和传输接口338分开的控制数据路径。在一个实施方案中,可在PHY 302与功能之间实现控制数据路径,所述功能定位在网络协议栈(但不限于链路层)中的任何位置。在一个实施方案中,控制数据路径可在PHY 302与功能之间实现,并且作为非限制性示例,非网络协议栈的一部分的设备特别适用于一种应用(例如,不限于汽车网络、建筑物网络、运输控制网络、照明网络)。

在图3的实施方案中,输入端348可操作地耦接到时间同步332,时间同步332一起形成可用于与介质访问调谐相关的控制循环的控制数据路径352的一部分。另一个控制数据路径部分地由输入358和时间同步332形成。在图3中,输入358可为传输接口338或接收接口336的一部分。

在这种情况下,时间同步332被配置为生成用于介质访问调谐的时间同步的控制信号346。作为非限制性示例,控制信号346可包括与时间感知协议相关的事件,诸如指示预定传输机会开始的事件。作为另一个非限制性示例,控制信号346可包括与流量整形协议相关的事件,诸如时间敏感数据(其是规则的的流量(例如,不限于音频帧、传感器轮询)并且确定性的延迟是重要的)或最佳努力数据(不规则的数据(例如,不限于固件更新、音频控制信号)并且延迟不重要,但在匮乏待避免的地方)的传输机会的开始。这样,控制信号346可以是或涉及PHY 302的一个或多个控制循环,包括但不限于针对时间感知协议、流量整形协议和物理层冲突避免的控制循环。

本领域的普通技术人员将认识到本文所公开的实施方案的许多优点和益处。作为一个非限制性示例,可将控制数据路径添加至适用于指定接口但不添加附加输入和/或输出的PHY架构。作为非限制性示例,控制路径可用于PHY与链路层(PHY和网络协议栈内(而不是链路层)的其他位置)之间的通信以及PHY与系统或子系统中的其他设备之间的通信。

图4示出了根据一个或多个实施方案的数据接收过程400的流程图。在操作402中,过程400从共享传输介质开始数据接收。数据接收可在物理层设备诸如PHY 102和PHY 302处执行。在一个实施方案中,共享传输介质为双绞单对以太网电缆,并且物理层设备被配置用于通过共享传输介质进行10兆位/秒通信。在操作404中,过程400朝向接口移动接收数据,该接口被配置为将物理层设备可操作地耦接到链路层设备。在一个实施方案中,接口是使用独占冲突避免信令的接口。在一个实施方案中,链路层设备是介质访问控制设备。在操作404中移动接收数据时,在操作406中,过程400从物理层设备的远程时钟域跨越到本地时钟域。在一个实施方案中,接收数据在被恢复之后跨越至本地时钟域。在另一个实施方案中,接收数据在其被恢复时跨越本地时钟域。在操作408中,过程400将现在在本地时钟域中的接收数据提供给接口用于发送至链路层。

本公开中任何表征为“典型的”、“常规的”或“已知的”不一定是指其公开于现有技术中,或所讨论的方面在现有技术中得到理解。也不一定意味着,在相关领域中,它是众所周知的、被很好地理解或经常使用的。

用于本公开,尤其是所附权利要求中的术语(例如,所附权利要求的主体)通常旨在为“开放”术语(例如,术语“包括”应被解释为“包括但不限于”,术语“具有”应被理解为“具有至少”,术语“包括”应被理解为“包括但不限于”等)。

另外,如果预期具体数量的引入的权利要求详述,则在权利要求中将明确叙述此类意图,并且在不进行此类详述的情况下,不存在此类意图。例如,作为对理解的帮助,以下所附权利要求书可包含使用介绍性短语“至少一个”和“一个或多个”来引入权利要求详述。然而,使用此类短语不应理解为暗示由不定冠词“一个”或“一种”引入的权利要求详述将包含此类引入的权利要求此类的任何特定权利要求限定于仅包含一个此类详述的实施方案,即使当相同的权利要求包括介绍性短语“一个或多个”或“至少一个”和不定冠词诸如“一个”或“一种”(例如,“一个”和/或“一种”可被解释为指的是“至少一个”或“一个或多个”);使用用于引入权利要求详述的定冠词的使用也是如此。

此外,即使明确列举了所引入的权利要求详述的具体编号,本领域的技术人员也将认识到,此类详述应被解释为是指的是至少所列举的数目(例如,在没有其它修饰符的情况下,“两个详述”的裸露详述是指至少两个详述或两个或更多个详述)。此外,在使用类似于“A、B和C等中的至少一者”或“A、B和C等中的一者或多者”的常规的那些情况下,此类配置一般旨在包括单独A、单独B、单独C、A和B一起、A和C一起、B和C一起或A、B和C一起,等等。

此外,无论在说明书、权利要求书或附图中,呈现两个或更多个另外的术语的任何分离的词或短语应当理解为考虑包括术语中的一个、两个术语中的任意一个或两个术语两者的可能性。例如,短语“A或B”应理解为包括“A”或“B”或“A和B”的可能性。

本公开的附加非限制性实施方案包括:

实施方案1:一种系统,包括:物理层侧接收数据路径,其被配置为朝向链路层侧接收数据路径移动接收数据;和物理层侧传输数据路径,其被配置为朝向共享传输介质移动传输数据,其中接收数据路径和传输数据路径位于第一时钟域中。

实施方案2:根据实施方案1所述的系统,还包括控制数据路径。

实施方案3:根据实施方案1和2中任一项所述的系统,其中控制数据路径被配置为将控制数据移动到系统的物理层或从系统的物理层移动控制数据。

实施方案4:根据实施方案1至3中任一项所述的系统,其中控制数据路径被配置为在系统的物理层与网络协议栈的应用层之间移动控制数据。

实施方案5:根据实施方案1至4中任一项所述的系统,其中控制数据路径被配置为在系统的物理层和与网络协议栈分开的设备之间移动控制数据。

实施方案6:根据实施方案1至5中任一项所述的系统,其中控制数据路径能够用于一个或多个控制循环,所述控制循环包括将控制数据移动到物理层或从物理层移动控制数据。

实施方案7:根据实施方案1至6中任一项所述的系统,其中一个或多个控制循环中的一者与时间感知协议、流量整形协议和物理层冲突避免协议中的一者相关联。

实施方案8:根据实施方案1至7中任一项所述的系统,其中物理层侧接收数据路径包括:位于第二时钟域中的第一部分;位于第一时钟域中的第二部分;和过渡边界,其中由物理层侧接收数据路径移动的接收数据从第二时钟域跨越到第一时钟域。

实施方案9:一种物理层设备的电路,包括:被配置为生成本地时钟的本地时钟发生器;接收电路和发射电路,其中接收电路和发射电路中的每一者操作地耦接到本地时钟发生器的输出,并被配置用于由所述本地时钟进行时钟控制;和一个或多个输出端,其中一个或多个输出端包括第一输出端,所述第一输出端可操作地耦接到时钟发生器,并被配置为传播本地时钟。

实施方案10:根据实施方案9的电路,本地参考时钟发生器操作地耦接到本地时钟发生器的输出端,并被配置为响应于本地时钟生成本地参考时钟。另外,其中本地时钟发生器操作地耦接到本地参考时钟发生器的输出端,并被配置为响应于本地参考时钟生成本地时钟。

实施方案11:根据实施方案9和10中任一项所述的电路,还包括互连件,所述互连件被配置为将第一输出端可操作地耦接至链路层设备的接收时钟输入端和链路层设备的传输时钟输入端。

实施方案12:根据实施方案9至11中任一项所述的电路,其中一个或多个输出端包括第二输出端,所述第二输出端被分配到用于独占冲突信令的信号。

实施方案13:根据实施方案9至12中任一项所述的电路,还包括一个或多个输入端,其中所述一个或多个输入端包括操作地耦接到发射电路的第一输入端,其中第一输入端被分配到用于控制信令的信号。

实施方案14:根据实施方案9至13中任一项所述的电路,还包括互连件,所述互连件被配置为将所述第一输入可操作地耦接到网络协议栈的链路层上方的一个或多个设备。

实施方案15:根据实施方案9至14中任一项所述的电路,还包括用于可操作地耦接到共享传输介质的接口电路。

实施方案16:根据实施方案9至15中任一项所述的电路,其中一个或多个设备中的一者是时间同步电路。

实施方案17:根据实施方案9至16中任一项所述的电路,其中一个或多个输出端中的至少一个输出端被配置用于独占冲突信令。

实施方案18:根据实施方案9至17中任一项所述的电路,还包括互连件,所述互连件被配置为将用于独占冲突信令的至少一个输出端操作地耦接到链路层设备的用于独占冲突信令的输入端。

实施方案19:根据实施方案9至18中任一项所述的电路,还包括第二时钟发生器,所述第二时钟发生器被配置为生成本地参考时钟。

实施方案20:根据实施方案9至19中任一项所述的电路,其中本地时钟发生器被配置为响应于本地参考时钟生成本地时钟。

实施方案21:根据实施方案9至20中任一项所述的电路,其中接收电路包括:过采样电路,所述过采样电路被配置为接收本地参考时钟;和同步电路,所述同步电路被配置为接收本地时钟。

实施方案22:一种方法,包括:从共享传输介质开始数据接收;朝向接口移动接收数据用于操作地耦接到链路层,其中所述移动接收数据包括将接收数据从远程时钟域跨越至物理层设备的本地时钟域。

实施方案23:根据实施方案22所述的方法,其中所述移动接收数据还包括:对从共享传输介质接收的数据进行过采样。

实施方案24:根据实施方案22和23中任一项所述的方法,其中所述移动接收数据还包括:使用过采样数据执行数字时钟和数据恢复。

实施方案25:根据实施方案22至24中任一项所述的方法,还包括:向接口提供接收数据用于发送至链路层。

虽然本文结合某些图示实施方案描述了本公开,但本领域的普通技术人员将认识到并理解本发明不受此限制。相反,在不脱离下文所要求保护的本发明的范围及其法律等同形式的情况下,可对图示实施方案和所述实施方案进行许多添加、删除和修改。此外,来自一个实施方案的特性可与另一个实施方案的特性组合,同时仍被包括在发明人所设想的本发明的范围内。

- 以太网接口和相关系统、方法和设备

- 设备间通过以太网接口传递额外数据的系统及方法