一种采样保持电路以及包含其的模数转换器

文献发布时间:2023-06-19 10:03:37

技术领域

本发明涉及读出电路领域,特别涉及一种采样保持电路以及包含其的模数转换器。

背景技术

CMOS图像传感器(CMOS Image Sensor,CIS)在消费类电子产品中的应用日益广泛,对CIS的面积和功耗要求也越来越苛刻。随着集成电路工艺的不断进步,CMOS图像传感器可以在片内将模拟信号数字化,即在像素阵列中使用模数转换器(ADC)。在CMOS图像传感器中,模数转换器(Analog to Digital Converter,ADC)的集成方式主要有三种,即像素级ADC、列级ADC以及芯片级ADC。其中,参考图1所示,芯片级ADC,顾名思义,就是整个芯片只采用一个ADC对整个像素阵列所采集的模拟信号进行量化,因而,要求ADC具有较高的转换速度。对于百万像素的CMOS图像传感器来讲,为保证较高的图像质量,除了保证每秒较高的帧频外,还要求全局ADC满足精度(8-12位)与动态性能的要求。目前,全局ADC多采用流水线ADC,这种ADC的通道一致性较好,控制更简单。

在流水线ADC中,采样保持电路(Sample-and-Hold Amplifier,SHA)是最前端的模块,用来采样输入的模拟信号,并将采样的结果保持一定的时间后传递给第一级进行量化,以避免信号传输时的孔径误差,因此,采样保持电路的性能优劣对整个ADC的精度影响最大,所以,采样保持电路的速度和精度是整个ADC设计的关键。

然而,对于典型的CIS读出电路,采样保持电路的输入范围是(0,V

发明内容

本发明的目的是提供一种采样保持电路以及包含其的模数转换器,使得该采样保持电路既能实现1倍增益,又能实现2倍增益,并且可以将输出信号拓展到(-V

为达到上述目的,本发明实施例提供一种采样保持电路,包括:

第一电容组与第二电容组,每个电容组包括电容C1,电容C2以及电容C3;

四个采样开关,每个采样开关的第一端与一个电容C1或电容C2的第一端连接,所述采样开关的第二端用于接收差分输入信号V

两个第一开关,每个第一开关的第一端与一个电容C3的第一端连接;

运算跨导放大器,所述运算跨导放大器的正相输入端与所述第一电容组的第一端相连,反相输入端与所述第二电容组的第一端相连;所述电容组的第一端由电容组中各个电容的第二端相连得到;

两个第二开关,每个第二开关的第一端与一个电容C1的第一端相连;

一个第三开关,连接于两个电容C3的第一端之间;

两个第四开关,其中一个第四开关连接于所述第一电容组中的电容C2的第一端与所述运算跨导放大器的反相输出端之间,另一个第四开关连接于所述第二电容组中的电容C2的第一端与所述运算跨导放大器的正相输出端之间;

两个第五开关,其中一个第五开关连接于所述正相输入端与反相输出端之间,另一个第五开关连接于所述反相输入端与正相输出端之间。

在一实施例中,所述第三开关以及与电容C1相连的采样开关由时钟信号CK1控制,与电容C2相连的采样开关由时钟信号CK1_2X控制,所述第一开关与所述第二开关由时钟信号CK2控制,所述第四开关由时钟信号CK2_2X控制,所述第五开关由时钟信号CK1P控制;

其中,所述时钟信号CK1与CK2为两相不交叠时钟;

所述时钟信号CK1与CK1P的上升沿对齐,所述时钟信号CK1P的下降沿早于所述时钟信号CK1的下降沿;

所述时钟信号CK1与控制信号P输入与非门G1,所述与非门G1的输出信号再输入非门G2,所述非门G2的输出信号为所述时钟信号CK1_2X;

所述控制信号P输入非门G3,所述非门G3的输出信号与所述时钟信号CK2输入或非门G4,所述或非门G4的输出信号输入非门G5,所述非门G5的输出信号为所述时钟信号CK2_2X。

在一实施例中,两个第一开关的第二端用于接收差分调节信号V

在一实施例中,两个第二开关的第二端用于接收差分参考信号V

在一实施例中,在所述控制信号P为低电平的情况下,所述采样保持电路实现1倍增益,在所述控制信号P为高电平的情况下,所述采样保持电路实现2倍增益。

在一实施例中,所述运算跨导放大器为带增益自举的套筒式放大电路结构。

本发明实施例还提供一种模数转换器,所述模数转换器包含上述任一实施例所述采样保持电路。

由以上本发明实施例提供的技术方案可见,本发明提供的采样保持电路为全差分结构,可以对范围为(0,V

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明中记载的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

图1是采用全局读出方式的图像传感器;

图2是现有的电容翻转型的采样保持电路;

图3是现有的电荷重分布型的采样保持电路;

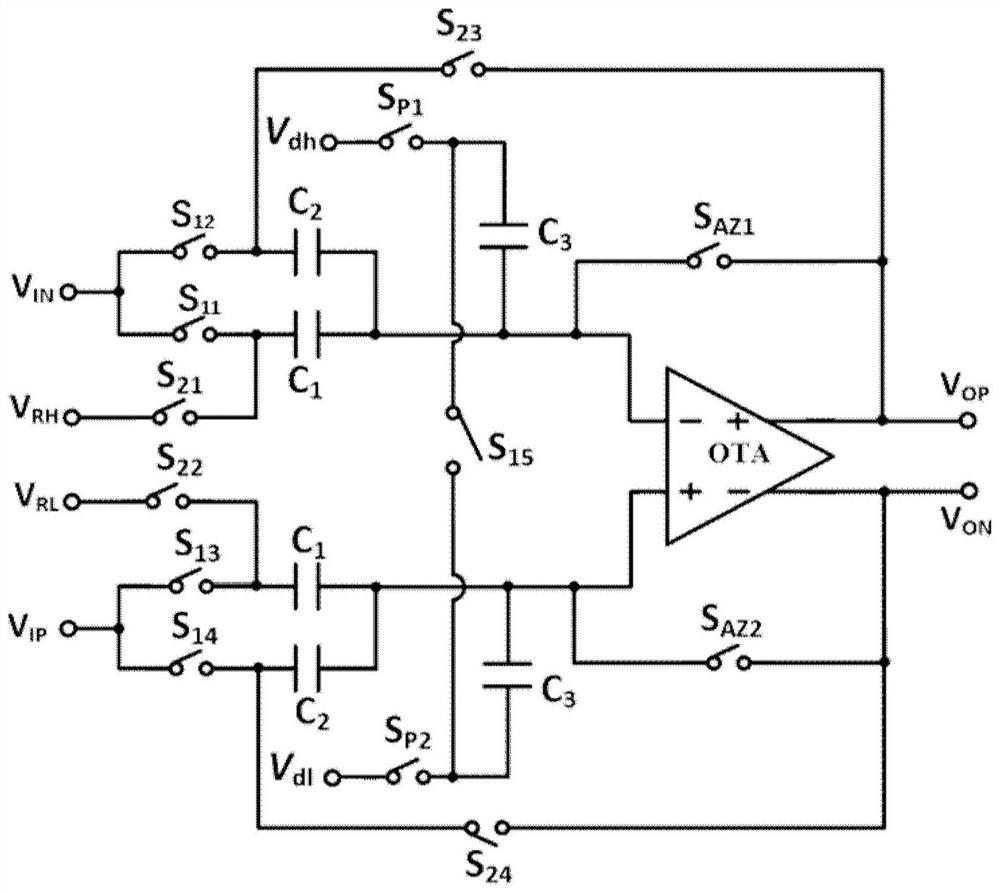

图4是本发明实施例提供的采样保持电路的电路结构图;

图5是本发明实施例中的时钟信号CK1、CK1P以及CK2的时序图;

图6是本发明实施例中的得到时钟信号CK1_2X与CK2_2X的逻辑门电路;

图7是图4所示的采样保持电路在控制信号P为低电平时的电路结构图;

图8中(a)是图4所示的采样保持电路在控制信号P为低电平且处于采样相时的电路结构图;图8中(b)图4所示的采样保持电路在控制信号P为低电平且处于保持相时的电路结构图;

图9是图4所示的采样保持电路在控制信号P为高电平时的电路结构图;

图10是图4所示的采样保持电路中的运算跨导放大器的电路结构图;

图11是利用图4所示的采样保持电路得到的瞬态响应图。

具体实施方式

传统的采样保持电路结构通常有两种,分别为电容翻转型和电荷重分布型。具体的,参考图2所示为电容翻转型的采样保持电路,参考图3所示为电荷重分布型的采样保持电路。可以看出,传统的采样保持电路实现的都是1倍增益,对输入信号的运算方法比较单一,并且采样保持电路的输入接的是相关双采样电路的输出,由于相关双采样电路的输出在(0,V

下面将结合附图和具体实施方式,对本发明的技术方案作详细说明,应理解这些实施方式仅用于说明本发明而不用于限制本发明的范围,在阅读了本发明之后,本领域技术人员对本发明的各种等价形式的修改均落入本发明所附权利要求所限定的范围内。

除非另有定义,本文所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。本文中在本发明的说明书中所使用的术语只是为了描述具体的实施方式的目的,不是旨在于限制本发明。

参考图4所示,为本发明实施例提供的一种采样保持电路的电路结构图,包括:

第一电容组与第二电容组,每个电容组包括电容C1,电容C2以及电容C3;

四个采样开关(开关S

两个第一开关(开关S

运算跨导放大器(Operational Transconductance Amplifier,OTA),所述运算跨导放大器的正相输入端与所述第一电容组的第一端相连,反相输入端与所述第二电容组的第一端相连;所述电容组的第一端由电容组中各个电容的第二端相连得到;

两个第二开关(开关S

一个第三开关(开关S

两个第四开关(开关S

两个第五开关(开关S

具体的,两个第一开关的第二端用于接收差分调节信号V

具体的,两个第二开关的第二端用于接收差分参考信号V

具体的,所述第三开关以及与电容C1相连的采样开关由时钟信号CK1控制,与电容C2相连的采样开关由时钟信号CK1_2X控制,所述第一开关与所述第二开关由时钟信号CK2控制,所述第四开关由时钟信号CK2_2X控制,所述第五开关由时钟信号CK1P控制;

其中,

参考图5所示,可以看出时钟信号CK1与CK2为两相不交叠时钟;时钟信号CK1P与CK1的上升沿对齐,时钟信号CK1P的下降沿早于时钟信号CK1的下降沿,从而可以消除采样开关的电荷注入。

参考图6所示,可以看出,采用1比特的控制位,生成控制信号P,所述时钟信号CK1与控制信号P输入与非门G1,所述与非门G1的输出信号再输入非门G2,所述非门G2的输出信号为所述时钟信号CK1_2X;所述控制信号P输入非门G3,所述非门G3的输出信号与所述时钟信号CK2输入或非门G4,所述或非门G4的输出信号输入非门G5,所述非门G5的输出信号为所述时钟信号CK2_2X。

具体的,在所述控制信号P为低电平的情况下,所述采样保持电路实现1倍增益,在所述控制信号P为高电平的情况下,所述采样保持电路实现2倍增益。

下面利用电荷守恒原理,详细分析控制信号P为低电平和高电平两种控制输入时,采样保持电路的输出关系式。

具体的,参考图7所示,为采样保持电路在控制信号P为低电平时的电路结构图。可以看出,时钟信号CK1_2X始终为低电平,时钟信号CK2_2X始终为高电平。参考图8中(a)所示,在采样相时,两个电容C

公式(1)中的V

V

从公式(2)可以看出,当控制信号P为低电平时,采样保持电路的差分输出信号为差分输入信号的1倍增益减去差分参考信号,再减去差分调节信号。

具体的,参考图9所示,为采样保持电路在控制信号P为高电平时的电路结构图。可以看出,此时,时钟信号CK1_2X与时钟信号CK1等效,时钟信号CK2_2X与时钟信号CK2等效。同样利用电荷守恒原理可以得到以下公式(3)。

V

从公式(3)可以看出,当控制信号P为高电平时,采样保持电路的差分输出信号为差分输入信号的2倍增益减去差分参考信号,再减去差分调节信号。

通过以上分析可知,当控制信号P为不同逻辑电平时,采样保持电路的增益也会不同。上述推导假设了运算跨导放大器在采样相和保持相时都能正常工作,且采样相时运算跨导放大器的输入输出短接,运算跨导放大器的输出共模电平会为V

具体的,从图10可以看出,本发明所用的运算跨导放大器为带增益自举的套筒式放大电路结构。在NMOS共栅管M3和M4的栅极,引入了增益自举运放,增益自举的作用是提高内部节点的输出阻抗而不增加更多的共源共栅器件,从而提高运算跨导放大器的直流增益。由于运算跨导放大器本身近似为一个单极点系统,它的次主极点的频率较大,所以具有很宽的带宽;此外,由于这种结构只有两条电流支路,因此在各种放大器中功耗最低。此外,为了进一步提高运算跨导放大器的能效,本发明采用工艺中低阈值NMOS管作为运放的输入对(M1和M2)和尾电流源(M9),低阈值管的使用可以提高输入对的跨导,从而降低运放的电流消耗。

本发明还提供一种模数转换器,所述模数转换器包含上述任一实施例所述的采样保持电路。

下面通过一个具体的实施例,进一步说明本发明的技术方案。

参考图11所示,给出了采样保持电路的输入信号和输出信号。输入为一个(0mV,800mV)的周期性方波信号,当设置控制信号P为高,DAC的输出为零时,可以看到,采样保持电路的输出变为(-800mV,800mV)的方波,完成了对输入的电平移位,其建立精度也达到了预期要求,图中输出方波的峰值约799.9mV,误差仅为0.1mV,满足10bitADC的精度要求。

本说明书中的上述各个实施方式均采用递进的方式描述,各个实施方式之间相同相似部分相互参照即可,每个实施方式重点说明的都是与其他实施方式不同之处。

以上所述仅为本发明的几个实施方式,虽然本发明所揭露的实施方式如上,但所述内容只是为了便于理解本发明的技术方案而采用的实施方式,并非用于限定本发明。任何本发明所属技术领域的技术人员,在不脱离本发明所揭露的精神和范围的前提下,可以在实施方式的形式上及细节上作任何的修改与变化,但本发明的专利保护范围,仍须以所附权利要求书所界定的范围为准。

- 一种采样保持电路以及包含其的模数转换器

- 一种用于流水线模数转换器的高中频采样保持电路