栅极驱动电路

文献发布时间:2023-06-19 10:03:37

相关申请:

本申请享受以日本专利申请2019-153989号(申请日:2019年8月26日)以及日本专利申请2019-203445号(申请日:2019年11月8日)为基础申请的优先权。本申请通过参照这些基础申请而包含基础申请的所有内容。

技术领域

本发明的实施方式涉及栅极驱动电路。

背景技术

作为对高电流进行开关的功率半导体元件,广泛使用了功率MOSFET(Metal-Oxide-Semiconductor Field-Effect-Transistor:金属氧化物半导体场效应晶体管)。功率MOSFET作为一个例子呈DMOS(Double-Diffused MOSFET:双扩散MOSFET)的构造,例如通过对N沟道以及P沟道的DMOS(以下,分别记载为NDMOS、PDMOS)的栅极施加电压来进行开关。作为对外部所具备的NDMOS、PDMOS的栅极施加电压的电路,有时分别配备CMOS(Complementary MOS:互补MOS)。例如外置的NDMOS所对应的CMOS的输出与外置的NDMOS的栅极连接,外置的PDMOS所对应的CMOS的输出与外置的PDMOS的栅极连接。在构成NDMOS侧的CMOS的、PMOS的源极和构成PDMOS侧的CMOS的、NMOS的源极被共享连接的情况下,有时在该共用阻抗(例如布局布线、接合线)中流过大电流,PDMOS侧的源极-栅极被较弱地偏压,流过漏电电流,从而进行误动作。

发明内容

一个实施方式提供一种使功率晶体管的栅极驱动稳定的栅极驱动电路。

根据一个实施方式,栅极驱动电路具备第一驱动电路,该第一驱动电路具备n型的第一晶体管、p型的第二晶体管、电平上升电路(level up circuit)以及电平下降电路(level down circuit)。第二晶体管与所述第一晶体管之间,彼此的漏极相连接,以比所述第一晶体管高的基准电压动作。电平上升电路使向所述第一晶体管的栅极施加的电压向高电平移位,并向所述第二晶体管的栅极反馈。电平下降电路使向所述第二晶体管的栅极施加的电压向低电平移位,并向所述第一晶体管的栅极反馈。第一驱动电路从所述第一晶体管以及所述第二晶体管的漏极输出第一功率晶体管的驱动电压。

附图说明

图1是表示栅极驱动电路的一个使用例的图。

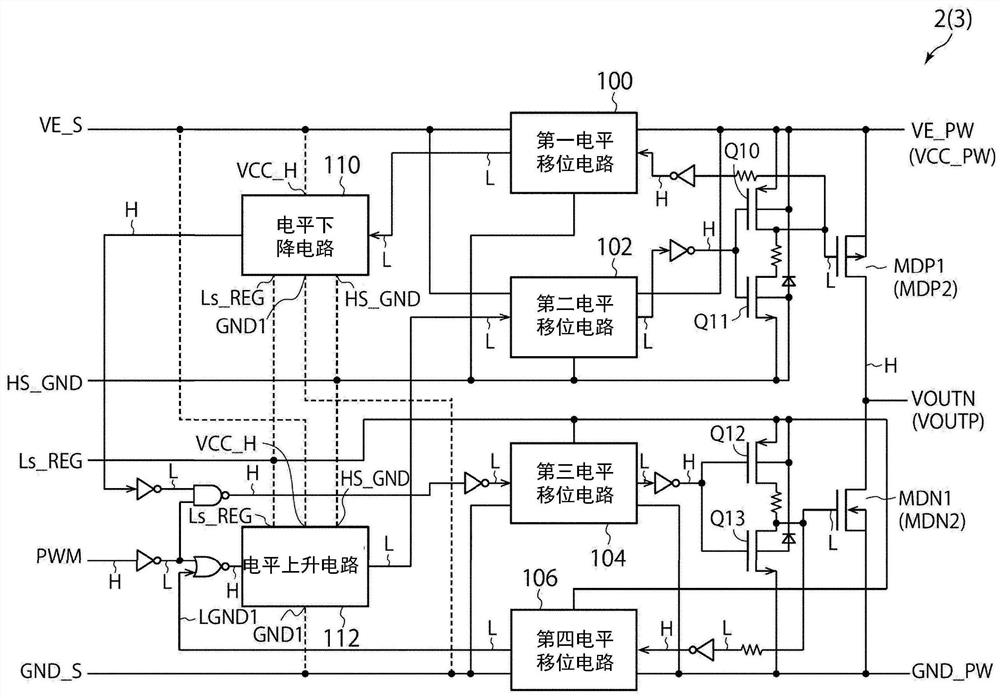

图2是一个实施方式的栅极驱动电路的电路图。

图3是一个实施方式的驱动电路的电路图。

图4是一个实施方式的第一电平移位电路的电路图。

图5是一个实施方式的第二电平移位电路的电路图。

图6是一个实施方式的第三电平移位电路的电路图。

图7是一个实施方式的第四电平移位电路的电路图。

图8是一个实施方式的电平下降电路的电路图。

图9是一个实施方式的电平上升电路的电路图。

图10是表示一个实施方式的栅极驱动电路的一个使用例的图。

图11是表示一个实施方式的栅极驱动电路的一个使用例的图。

图12是一个实施方式的栅极驱动电路的输出例。

图13是一个实施方式的栅极驱动电路的输出例。

具体实施方式

以下,参照附图对实施方式进行说明。由于提取了本实施方式的本质部分,因此并不限定于排除具备其他电路元件的情况。另外,除了CMOS与电平移位电路等配置以外而适当地变更者也不脱离本实施方式的范围。另外,由于图会变得繁琐,因此例如未在缓冲电路等中描绘VCC、GND等的全部连接,而设为适当地与电源电压等连接。另外,说明中使用的电压等数值只是作为一个例子来表示,并不局限于此,也可以根据需要而适当地变更。

(第一实施方式)

图1是表示本实施方式的栅极驱动电路1的使用例的图。若PWM等开关信号被输入到死区时间控制电路4,则执行死区时间控制。该输出经由电平上升电路5而直接地向栅极驱动电路1输入。被进行了死区时间控制的PWM信号例如直接地输入到第一驱动电路2,生成向NDMOS Q1的栅极施加的驱动电压,并且被进行了死区时间控制的PWM信号经由电平上升电路5输入到第二驱动电路3,生成向PDMOS Q2的栅极施加的驱动电压。第一驱动电路2与第二驱动电路3也可以在栅极驱动电路1内连接。另外,在以下的说明中,栅极驱动电路1由第一驱动电路2与第二驱动电路3构成,但并不限定于此,也可以将栅极驱动电路1设为广义上还具备死区时间控制电路4与电平上升电路5的构成。

本实施方式的栅极驱动电路1像这样具备第一驱动电路2与第二驱动电路3,分别进行位于外部的NDMOS Q1(第一功率晶体管)与PDMOS Q2(第二功率晶体管)的驱动。通过经由死区时间控制电路4以及电平上升电路5,从而防止短路,使导通·断开的切换定时具有足够的余量,并且适当地控制向各个DMOS的栅极施加的电压。

如后述那样,第二驱动电路3相比于第一驱动电路2,作为其基准的电位更高。例如第一驱动电路2在VCC为8V、GND为0V的情况下动作,第二驱动电路3在VCC为23V、GND为8V的情况下动作。在第二驱动电路3与PDMOS Q2之间,也可以根据PDMOS Q2的栅极的耐压性能而进一步具备电平下降电路。以下,有时将各电路中的正侧的电源电压简单记载为VCC。同样,有时将接地电位简单记载为GND。

图2示出本实施方式的栅极驱动电路1的电路图的一个例子。栅极驱动电路1具备第一驱动电路2、第二驱动电路3以及电压源V1、V2、V3、V4、V5、V6、V7、V8、V9、V10。电压源并不一定需要配备于栅极驱动电路1的内部,也可以在栅极驱动电路1的外部以附加各端子彼此的电位差的方式连接。例如也可以将虚线所示的构成要素配备于栅极驱动电路1的内部。在该情况下,电压源V2、V3、V6、V7、V9、V10在外部使端子彼此之间生成电位差。并不限定于此,也可以是一部分或者所有电压源位于栅极驱动电路1的外部。

第一驱动电路2被输入进行了死区时间控制的输入信号PWM,对向NDMOS Q1的栅极施加电压的输出端子VOUTN施加输出电压。作为其他端子,有HS_GND、VE_S、VE_PW、GND_S、Ls_REG、GND_PW端子,分别适当地与VCC、GND之间具有电位差地连接。之后叙述这些端子的内部的连接。

第二驱动电路3被输入进行了死区时间控制以及电平移位的输入信号PWM,对向PDMOS Q2的栅极施加电压的输出端子VOUTP施加输出电压。其他端子与第一驱动电路2相同。

在第一驱动电路2与第二驱动电路3中,作为输出侧的电路元件,分别具备互补型MOSFET(以下,记载为CMOS)。栅极驱动电路1的端子VCC_PW与构成第二驱动电路3的CMOS的PMOS的源极连接。端子VE_PW与构成第二驱动电路3的CMOS的NMOS的源极以及构成第一驱动电路2的CMOS的PMOS的源极连接。端子GND_PW与构成第一驱动电路2的CMOS的NMOS的源极连接。如此,利用VCC_PW与VE_PW、VE_PW与GND_PW施加各个驱动电路中的CMOS的源极间的电压。

另外,端子VCC_S是VCC传感端子,例如与电源电压VCC连接。端子GND_S是GND传感端子,例如与接地电压GND连接。利用连接于这些传感端子的电源电压,供给栅极驱动电路1的电压。

例如在该图2中,端子GND_PW与外置NDMOS Q1的源极连接,VOUTN被施加到NDMOSQ1的栅极。端子VCC_PW与外置PDMOS Q2的源极连接,VOUTP被施加到PDMOS Q2的栅极。NDMOSQ1与PDMOS Q2的漏极彼此连接而构成CMOS,从该共享连接的漏极输出开关信号。如后述那样,V2、V9是表示与传感电压之差的电压。这些电压例如示出了布局布线、接合线等的高电阻中流过大电流而短路的情况下的与传感电压的电位差。理想情况下,期望NDMOS Q1、PDMOS Q2的源极分别与GND_S、VCC_S连接,但设想短路而考虑如上述那样连接。本实施方式在存在该短路的情况下也抑制误动作。

图3示出第一驱动电路2(或者实质上与第二驱动电路3同等)的电路图的一个例子。在该例子中,作为PWM示出了被输入High的信号的情况下。图中的H与L分别表示High(高)与Low(低)。在输入了Low的信号的情况下,成为替换了图中的H与L后的状态。

第一驱动电路2具备第一电平移位电路100、第二电平移位电路102、第三电平移位电路104、第四电平移位电路106、电平下降电路110以及电平上升电路112。另外,作为向第一功率晶体管NDMOS Q1的栅极施加电压的CMOS,具备NMOS MDN1(第一晶体管)和PMOS MDP1(第二晶体管),从这些晶体管的漏极输出向NDMOS的栅极施加的驱动电压VOUTN。

在作为驱动PDMOS Q2的电路的第二驱动电路3的情况下,最后级的CMOS构成为MDN2(第三晶体管)、MDP2(第四晶体管)。第二驱动电路3中,从这些晶体管的漏极输出向第二功率晶体管PDMOS Q2的栅极施加的驱动电压VOUTP。

使用图2与图3对栅极驱动电路1的动作进行说明。栅极驱动电路1例如被施加VCC=23V、GND=0V作为电源电压。即,端子VCC_S与23V连接,端子GND_S与0V连接。

电压源V1是用于设置端子GND_S与第一驱动电路2的端子Ls_REG间的电位差的电压源。电压源V4是用于设置端子VE_S与第一驱动电路2的端子HS_GND间的电位差的电压源。电压源V5是用于设置端子VE_S与第二驱动电路3的端子Ls_REG间的电位差的电压源。电压源V8是用于设置端子VCC_S与第二驱动电路3的端子HS_GND间的电位差的电压源。这些电压源V1、V4、V5、V8定义第一驱动电路2或者第二驱动电路3内的晶体管的输入输出端子间(漏极-源极间、或者CMOS中的PMOS的源极与NMOS的源极间)的电压,例如施加5V的电压。

电压源V3、V7、V10是使各个端子的电位从接地电压提高的电压源,例如电压源V3施加0V的电压,电压源V7施加8V的电压,电压源V10施加23V的电压。

电压源V2是虚拟表示第一驱动电路2的端子GND_S、GND_PW之间的电位差的电压源。电压源V6是虚拟表示第一驱动电路2的端子VE_PW、VE_S之间的电位差以及第二驱动电路3的端子GND_S、GND_PW之间的电位差的电压源。电压源V9是虚拟表示第二驱动电路3的端子VCC_PW、VCC_S之间的电位差的电压源。

这些虚拟的电压源的输出例如理想的是0V。然而,在采用封装等的情况下,有时经由高电阻的路径而短路。虚拟地安装有这种经由高电阻的短路。在本实施方式中,利用第一驱动电路2以及第二驱动电路3,即使该V2、V6、V9的值是某种程度的大小,也能够稳定地进行NDMOS Q1、PDMOS Q2或作为它们的组合的互补型DMOS(CDMOS)的驱动。

第一驱动电路2通过具备PMOS MDP1以及NMOS MDN1的CMOS输出VOUTN。该CMOS通过向各个晶体管的栅极施加的电压来切换向图1所示的NDMOS Q1的栅极施加的电压。

第一电平移位电路100是替换输入输出的“高”/“低”并使VE_PW与HS_GND间的振幅向VE_S与HS_GND间的振幅电平移位的电路。第二电平移位电路102是在保持输入输出的“高”/“低”的状态下使VE_S与HS_GND间的振幅向VE_PW与HS_GND间的振幅电平移位的电路。

第三电平移位电路104是在保持输入输出的“高”/“低”的状态下使Ls_REG与GND_S间的振幅向Ls_REG与GND_PW间的振幅电平移位的电路。第四电平移位电路106是替换输入输出的“高”/“低”并使Ls_REG与GND_PW间的振幅向Ls_REG与GND_S间的振幅电平移位的电路。

图3示出了在作为PWM信号而输入了“高”的信号的情况下稳定的状态。虚线所示的路径是从VCC以及GND向电平下降电路110以及电平上升电路112的连接,为了容易观察而标注虚线。电平下降电路110是使输入输出的信号反转并使VCC_H(VE_S)与HS_GND间的振幅向Ls_REG与GND1(GND_S)间的振幅电平下降的电路。电平上升电路112是使输入输出的信号反转并使Ls_REG与GND1(GND_S)间的振幅向VCC_H(VE_S)与HS_GND间的振幅电平上升的电路。换言之,电平下降电路110是将VCC基准的信号向GND基准的信号转换的电路,电平上升电路112是将GND基准的信号向VCC基准的信号转换的电路。

作为输入信号的PWM是“高”,通过否定电路而变为“低”。该“低”的信号与第四电平移位电路106的输出一起被输入到或非电路。在第四电平移位电路106的输出为“低”的情况下,或非电路的输出成为“高”。具有该Ls_REG与GND_S间的振幅的“低”的信号向电平上升电路112输入。在电平上升电路112中,被转换为具有“高”的VE_S与HS_GND间的振幅的信号。

该信号在第二电平移位电路102中被转换为VE_PW与HS_GND间的“低”的信号。“低”的信号在否定电路中被转换为“高”的信号,向构成CMOS的PMOS Q10、NMOS Q11的栅极施加。被施加了“高”的信号的CMOS从其漏极输出“低”的信号。并且,该VE_PW与HS_GND间的“低”的信号被施加到PMOS MDP1的栅极。

施加到该栅极的电压反馈到对构成CMOS的NMOS MDN1的栅极施加的信号。首先,利用否定电路向“高”的信号转换,并输入到第一电平移位电路100。第一电平移位电路100将该输入的信号向VE_S与HS_GND间的“低”信号电平移位。该“低”信号输入到电平下降电路110,向Ls_REG与GND_S间的“高”的信号转换。电平下降电路110的输出经由否定电路而与PWM信号的否定一起输入到与非电路,从而输出“高”的信号。与非电路的输出经由否定电路转换为“低”信号之后,被输入到第三电平移位电路104。

第三电平移位电路104将输入的Ls_REG与GND_S间的“低”信号向Ls_REG与GND_PW间的“低”信号转换。在第三电平移位电路104中转换后的信号经由否定电路向构成CMOS的PMOS Q12、NMOS Q13的栅极施加。被施加了“高”的信号的CMOS从其漏极输出“低”的信号。并且,该Ls_REG与GND_PW间的“低”的信号向NMOS MDN1的栅极施加。

施加到该栅极的电压经由否定电路以及第四电平移位电路106而向电平上升电路112反馈。如此,在第一电平移位电路100以及第四电平移位电路106中,将电平向作为输入PWM信号的电平的Ls_REG与GND_S间的信号转换并反馈。

如此,向构成CMOS的PMOS MDP1的栅极以及NMOS MDN1的栅极施加“低”的信号,因此向图1所示的NDMOS Q1的栅极输出“高”的信号。

关于第二驱动电路3也进行相同的动作。但是,在第二驱动电路3中,如图2所示,在VE_PW端子连接有VCC_PW,在VE_S端子连接有VCC_S,在HS_GND连接有利用电压源V8降低了电压的VCC_S,在Ls_REG端子连接有利用电压源V5施加了电压的VE_S,在GND_PW端子连接有VE_PW,在GND_S端子连接有VE_S。在如上述那样连接的状态下,构成CMOS的PMOS MDP2以及NMOS MDN2的栅极被施加“高”或者“低”的信号,并将“低”或者“高”的信号向图1所示的PDMOS Q2的栅极输出。

根据图2以及图3可知,第二驱动电路3的GND_PW端子与第一驱动电路2的VE_PW端子、即第二驱动电路3的NMOS MDN2的源极与第一驱动电路2的PMOS MDP1的源极相连接。例如在使第一驱动电路2以及第二驱动电路3的输出为“高”(希望使功率开关为“关”)的情况下,在第一驱动电路2的VE_PW端子以及第二驱动电路3的GND_PW端子间使大电流流过布局布线与接合线的合成电阻Rpara。

在这种情况下,也基于第二驱动电路3的GND_PW端子、即NMOS MDN2的源极的电压,进行由第二驱动电路3的第四电平移位电路106转换后的NMOS MDN2的栅极电压的反馈。利用第四电平移位电路106转换GND电平并反馈的电压经由第二电平移位电路102、第一电平移位电路100向第三电平移位电路104输入。在该第三电平移位电路104中,GND的基准从GND_S转换为GND_PW。

据此,能够适当地控制向NMOS MDN2的栅极施加的电压的基准电平,将栅极-源极间的电压保持为小于NMOS MDN2的阈值电压|Vth|,并能够抑制NMOS MDN2中的泄漏电流的产生。

同样,在使第一驱动电路2以及第二驱动电路3的输出为“低”(希望使功率开关为“开”)的情况下,使大电流流过合成电阻Rpara。

在这种情况下,也基于第一驱动电路2的VE_PW端子、即PMOS MDP1的源极的电压,进行由第一驱动电路2的第一电平移位电路100转换后的PMOS MDP1的栅极电压的反馈。利用第一电平移位电路100转换VCC电平并反馈的电压经由第三电平移位电路104、第四电平移位电路106向第二电平移位电路102输入。在该第二电平移位电路102中,VCC的基准从VE_S转换到VE_PW。

据此,能够适当地控制向PMOS MDP1的栅极施加的电压的基准电平,将栅极-源极间的电压保持为小于PMOS MDP1的阈值电压|Vth|,并能够抑制PMOS MDP1中的泄漏电流的产生。

如以上那样,根据本实施方式,在构成CMOS的功率MOSFET的驱动中,即使在生成向各个栅极施加的电压的前级的CMOS的源极间产生电位差的情况下,也能够抑制前级的CMOS间的泄漏电流。

以下,列举一个例子简单地说明包含电平下降电路110以及电平上升电路112的各电平移位电路。另外,关于以下的各电平移位电路,在输入信号的“高”与“低”相反的情况下,成为“高”与“低”反转的动作。

第一电平移位电路100、第二电平移位电路102、第三电平移位电路104、第四电平移位电路106分别是小信号的CMOS逻辑电路。这些电路的逻辑振幅设为5V左右,但也可以是能够配合栅极驱动电路1的设计而进行变更的电路。

图4是表示第一电平移位电路100的一个例子的电路图。第一电平移位电路100例如具备晶体管Q100、Q101、Q102、Q103、Q104、Q105、Q106、Q107和两个否定电路。例如晶体管Q100、Q101、Q104、Q105是P型的MOSFET,晶体管Q102、Q103、Q106、Q107是N型的MOSFET。

设为向第一电平移位电路100输入以VE_PW为VCC基准的“高”的信号。在该情况下,晶体管Q100的栅极被施加“高”的信号,漏极侧成为“低”。晶体管Q101的栅极以及晶体管Q103的栅极被施加“低”的信号,漏极侧成为“高”。同样,晶体管Q102的栅极被施加“高”的信号,与晶体管Q100共享的漏极侧成为“低”。

这些漏极侧的信号分别向NMOS的栅极施加。晶体管Q107的栅极被施加“高”的信号,因此从晶体管Q105的漏极经由晶体管Q107的漏极向源极地使电流流向HS_GND,晶体管Q105、Q107的漏极间成为“低”。因此,晶体管Q104的栅极被施加“低”的信号,与同样是栅极被施加“低”的信号的晶体管Q106之间,彼此漏极间成为“高”。这里,由于VCC的基准成为晶体管Q104的VCC基准,因此转换为VE_S的电平的信号经由否定电路而输出。在图中的情况下,从第一电平移位电路100经由否定电路输出“低”的信号。

如此,第一电平移位电路100将VCC基准从VE_PW转换到VE_S,使输入输出向相反的状态转换并输出。

图5是表示第二电平移位电路102的一个例子的电路图。第二电平移位电路102具备例如作为PMOS的晶体管Q108、Q109、Q112、Q113和例如作为NMOS的晶体管Q110、Q111、Q114、Q115。

设为向第二电平移位电路102输入以VE_S为VCC基准的“低”的信号。在该情况下,晶体管Q108的栅极经由否定电路被施加“高”的信号,晶体管Q109的栅极进而经由否定电路被施加“低”的信号。并且,晶体管Q110的栅极被施加“高”的信号,晶体管Q111的栅极被施加“低”的信号。

与这些漏极连接的晶体管Q114、Q115的栅极分别被施加“低”、“高”的信号,晶体管Q112、Q113的栅极被施加“低”的信号。因此,晶体管Q112、Q114的漏极成为VCC基准转换为VE_PW后的“高”的状态。其结果,从第二电平移位电路102经由否定电路输出“低”的信号。

如此,第二电平移位电路102将VCC基准从VE_S转换为VE_PW,保持输入输出的状态并输出。

图6是表示第三电平移位电路104的一个例子的电路图。第三电平移位电路104具备例如作为PMOS的晶体管Q116、Q117、Q120、Q121和例如作为NMOS的晶体管Q118、Q119、Q122、Q123。

设为向第三电平移位电路104输入以GND_S为GND基准的“低”的信号。在该情况下,晶体管Q118的栅极经由否定电路被施加“高”的信号,晶体管Q119的栅极被施加“低”的信号。并且,晶体管Q116的栅极被施加“高”的信号,晶体管Q117的栅极被施加“低”的信号。

与这些漏极连接的晶体管Q120、Q121的栅极分别被施加“高”、“低”的信号,晶体管Q122、Q123的栅极被施加“低”的信号。因此,晶体管Q121、Q123的漏极成为GND基准转换为GND_PW后的“高”的状态。其结果,从第三电平移位电路104经由否定电路输出“低”的信号。

如此,第三电平移位电路104将GND基准从GND_S转换为GND_PW,保持输入输出的状态并输出。

图7是表示第四电平移位电路106的一个例子的电路图。第四电平移位电路106具备例如作为PMOS的晶体管Q124、Q125、Q128、Q129和例如作为NMOS的晶体管Q126、Q127、Q130、Q131。

设为向第四电平移位电路106输入以GND_PW为GND基准的“高”的信号。在该情况下,晶体管Q131的栅极经由否定电路被施加“低”的信号,晶体管Q130的栅极被施加“高”的信号。并且,晶体管Q128的栅极被施加“高”的信号,晶体管Q129的栅极被施加“低”的信号。

与这些漏极连接的晶体管Q124、Q125的栅极分别被施加“低”、“高”的信号,晶体管Q126、Q127的栅极被施加“低”的信号。因此,晶体管Q124、Q126的漏极成为GND基准转换为GND_S后的“高”的状态。其结果,从第四电平移位电路106经由否定电路输出“低”的信号。

如此,第四电平移位电路106将GND基准从GND_PW转换为GND_S,使输入输出的状态相反并输出。

接下来,说明晶体管MDP1、MDN1、MDP2、MDN2的栅极、即对从第一电平移位电路100、第四电平移位电路106反馈的信号的电压电平进行转换的电平下降电路110与电平上升电路112。电平下降电路110与电平上升电路112是高耐压的电平移位电路。

图8是表示电平下降电路110的一个例子的电路图。根据图3,电平下降电路110被输入以VE_S、HS_GND为基准的信号HS_sig。图8中如括号所示,VCC_H端子被施加VE_S的电压,GND1端子被施加GND_S的电压。另外,说明电平下降电路110被输入“高”的信号的情况。

电平下降电路110例如具备作为PMOS的晶体管Q200、Q201、Q204、Q205、Q208、Q209、Q212、Q213和例如作为NMOS的晶体管Q202、Q203、Q206、Q207、Q210、Q211、Q214、Q215。

晶体管Q200、Q202的栅极经由否定电路被施加“低”的信号,从而漏极成为“高”,晶体管Q201、Q203的栅极被施加“高”的信号,从而漏极成为“低”。

由于晶体管Q204的源极被施加“高”,栅极被施加HS_GND,因此漏极输出用HS_GND抑制了“低”电平后的“高”的信号。晶体管Q205的源极被施加“低”,栅极被施加HS_GND,因此漏极输出用HS_GND抑制了“低”电平后的“低”的信号。晶体管Q206的漏极被施加“高”,栅极被施加Ls_REG,因此源极输出用Ls_REG抑制了“高”电平后的“高”的信号。晶体管Q207的漏极被施加“低”,栅极被施加Ls_REG,因此源极输出用Ls_REG抑制了“高”电平后的“低”的信号。

晶体管Q208、Q210的栅极被输入“高”的信号,从漏极输出GND基准被转换为GND_S后的“低”的信号。晶体管Q209、Q211的栅极被施加“低”的信号,从漏极输出GND基准被转换为GND_S后的“高”的信号。

晶体管Q214的栅极被施加“高”的信号,因此源极成为“低”电平,晶体管Q213的栅极成为“低”。另外,由于晶体管Q213的栅极为“低”,因此从栅极被施加“低”的信号的晶体管Q215的漏极输出“高”的信号。另外,晶体管Q212的栅极被施加该“高”的信号,使晶体管Q212、Q214的漏极为“低”。

其结果,输出的信号LS_sig成为其基准被转换为Ls_REG与GND_S后的“低”的信号。如此,电平下降电路110使输入的“高”/“低”反转,将以VE_S、HS_GND为基准的信号转换为以Ls_REG,GND_S为基准的信号并输出。

图9是表示图3的电平上升电路112的一个例子的电路图。根据图3,电平上升电路112被输入以Ls_REG、GND_S为基准的信号LS_sig。图9中如括号所示,VCC_H端子被施加VE_S的电压,GND1端子被施加GND_S的电压。另外,说明电平上升电路112被输入“高”的信号的情况。

电平上升电路112具备例如作为NMOS的晶体管Q220、Q221、Q224、Q225、Q228、Q229、Q232、Q233和例如作为PMOS的晶体管Q222、Q223、Q226、Q227、Q230、Q231、Q234、Q235。

晶体管Q220、Q222的栅极被施加“高”的信号,从而漏极成为“低”,晶体管Q221、Q223的栅极经由否定电路被施加“低”的信号,从而漏极成为“高”。

晶体管Q225的栅极被施加“高”的信号,晶体管Q227的栅极被施加“低”的信号,因此该两个晶体管导通。并且,晶体管Q225的源极连接于GND_S,因此晶体管Q225的漏极、晶体管Q227的漏极以及源极成为“低”。

晶体管Q229、Q231的栅极成为“低”,因此它们的漏极成为“高”。其结果,晶体管Q226的源极成为“高”。晶体管Q226的栅极被施加HS_GND(低),晶体管Q224的栅极被施加“低”,因此晶体管Q226、Q224的漏极成为“高”。

晶体管Q228、Q230的栅极被施加以VE_S与HS_GND为基准后的“高”的信号,漏极成为“低”。同样,在上级的晶体管中,成为基准的电压被转换为VE_S与HS_GND。

通过这些,晶体管Q234的栅极被施加“低”的信号,晶体管Q235的栅极被施加“高”的信号,晶体管Q232的栅极被施加“低”的电压,晶体管Q233的栅极被施加“高”的电压。这些信号的基准成为VE_S与HS_GND。

其结果,从电平上升电路112输出以VCC_H与HS_GND为基准后的“低”的信号。如此,电平上升电路112使输入的“高”/“低”反转,将以Ls_REG、GND_S为基准的信号转换为以VE_S、HS_GND为基准的信号并输出。

图1等所示的电平上升电路5可以与该电平上升电路112同等为适当地调整了输出的“高”/“低”的电路,也可以是另一构成的电路。

另外,各电平移位电路并不限定于图4至图9所示,只要适当地转换输入输出的信号的状态“高”/“低”并转换VCC或者GND的电平基准即可。

另外,在本实施方式中,具备第一驱动电路2与第二驱动电路3这两方,但例如在功率晶体管仅为NDMOS的情况下,也可以构成为仅具备第一驱动电路2。如此,通过具备第一驱动电路2,也能够同样对输出目的地的功率晶体管抑制开关为断开状态下的泄漏电流。

(第二实施方式)

也可以对前述的实施方式的输出进行监视并进一步进行反馈。在本实施方式中,将第一驱动电路2以及第二驱动电路3的输出信号向死区时间控制进行反馈。

图10示出本实施方式的栅极驱动电路的安装例。栅极驱动电路1的输出信号经由比较电路CMP1、CMP2向死区时间控制电路4反馈。

比较器CMP1监视作为第一驱动电路2的输出的外置的NDMOS Q1侧的输出信号。比较器CMP1将作为输出信号的VOUTN与接地电位(端子GND_PW的电位)进行比较,例如在输出信号VOUTN比接地电位GND_PW高出约外置的NDMOS Q1的阈值电压Vth(例如1.5V左右)以上的情况下,输出“高”的信号,除此以外的情况下,输出“低”的信号。如此进行监视,作为该结果的控制,避免外置的NDMOS Q1短路。

通过将该比较器CMP1的输出与输入信号PWM的输入的否定之间的、逻辑和的否定作为第二驱动电路3的输入,使得第一驱动电路2的输出从“高”转变为“低”之后,第二驱动电路3的输出从“高”转变为“低”。即,在输入信号从“低”转变为“高”的情况下,在使第二驱动电路3的输出转变为“低”之前,第一驱动电路2的输出先转变为“低”。

比较器CMP2监视作为第二驱动电路3的输出的外置的PDMOS Q2侧的输出信号。比较器CMP2对作为输出信号的VOUTP和电源电位(例如VCC_PW的电位)进行比较,例如在输出信号VOUTP比电源电压VCC_PW低出约外置的PDMOS Q2的阈值电压Vth的绝对值(例如1.5V左右)以上的情况下,输出“高”的信号,除此以外的情况下,输出“低”的信号。如此进行监视,作为该结果的控制,避免外置的PDMOS Q2短路。

通过将该比较器CMP2的输出与输入信号PWM的输入之间的、逻辑和的否定作为第一驱动电路2的输入,使得第二驱动电路3的输出从“低”转变为“高”之后,使第一驱动电路2的输出从“低”转变为“高”。即,在输入信号从“高”转变为“低”的情况下,在使第一驱动电路2的输出转变为“高”之前,第二驱动电路3的输出先转变为“高”。

与图2相同,端子GND_PW与外置NDMOS Q1的源极连接,VOUTN被施加到NDMOS Q1的栅极。端子VCC_PW与外置PDMOS Q2的源极连接,VOUTP被施加到PDMOS Q2的栅极。NDMOS Q1与PDMOS Q2的、漏极彼此连接而构成CMOS,从该共享连接的漏极输出开关信号。

如以上那样,根据本实施方式,在构成CMOS的功率MOSFET的驱动中,即使在生成向各个栅极施加的电压的前级的CMOS的源极间产生电位差的情况下,也能够抑制前级的CMOS间的泄漏电流。而且,通过反馈各驱动电路的输出,能够在将DMOS的一方设为“关”之后使另一方为“开”,能够抑制两个DMOS的双方同时成为“开”的情况,从而提高功率MOS开关的稳定性以及安全性。

本实施方式也可以如图11那样变形。即,比较器CMP1的反转端子连接于端子GND_S,比较器CMP2的非反转端子连接于端子VCC_S。即使如此连接,也能够与上述相同地监视外置的NDMOS Q1、PDMOS Q2的各端子的电位。其结果,能够将比较结果向栅极驱动电路1反馈,避免外置的NDMOS Q1、PDMOS Q2短路。

图12以及图13示出:在第一实施方式的栅极驱动电路1中的VCC_S、VCC_PW间、VE_PW、VE_S间、GND_PW、GND_S间经由1Ω的电阻而短路的情况下的各信号。例如以5us为基准,在5us处将输入PWM设为“低”,在10us处将输入PWM设为“高”。死区时间在各个定时设计为0.125us。

在这些图中,从上起依次示出来自VOUTP、VOUTN、VE_PW、VE_S、PDMOS Q2以及NDMOSQ1的漏极的输出GATE、MDP2的源极-栅极电压MDP2_SG、MDN2的栅极-源极电压MDN2_GS、MDP1的源极-栅极电压MDP1_SG、MDN1的栅极-源极电压MDN1_GS、MDP2的漏极电流I_MDP2、MDN2的漏极电流I_MDN2、MDP1的漏极电流I_MDP1、MDN1的漏极电流I_MDN1。

图12是表示在5us处将输入PWM设为“低”的状态的图。在0.125us后的定时,VOUTN成为“低”。在0.25us后,VOUTP成为“低”,GATE成为“高”,即开关成为导通,另一方面,漏极电流I_MDP1几乎不变化。如此,在PDMOS Q2导通的定时,不流过漏极电流I_MDP1,因此能够抑制误动作。

图13是表示在10us处将输入PWM设为“高”的状态的图。在0.125us后的定时,VOUTP成为“高”。在0.25us后,VOUTN成为“高”,GATE成为“低”,即开关成为断开,另一方面,漏极电流I_MDN2几乎不变化。如此,在NDMOS Q1导通的定时,不流过漏极电流I_MDN2,因此能够抑制误动作。

如前述那样,若考虑将VCC偏压为23V、将VOUTP与VOUTN的输出端子的中间偏压为8V、将GND偏压为0V的情况,则能够如图12、图13那样获得结果。

根据以上的各实施方式,利用第一电平移位电路100以及第三电平移位电路104,能够防止PW布线与传感布线之间的限制电阻Rs(例如基于IC内的布线+接合线的电阻)中的IR_Drop的电压下降引起的误动作。

而且,能够避免VCC_PW与VCC_S间的寄生电感(例如IC内的布线+接合线)、GND_PW与GND_S间的寄生电感中的断开的定时下的逆基电压V=-Ls×dI/dt所引起的MDP2与MDN1的误导通。

虽然说明了本发明的几个实施方式,但这些实施方式是作为例子而提出的,并不意图限定发明的范围。这些新的实施方式能够以其他各种方式实施,在不脱离发明的主旨的范围内能够进行各种省略、替换、变更。这些实施方式及其变形包含在发明的范围及主旨中,并且包含在权利要求书所记载的发明与其等效的范围内。

例如第一驱动电路的输出目的地设为n型的DMOS,但并不限定于此。作为另一例,也可以与绝缘栅双极晶体管(IGBT:Insulated Gate Bipolar Transistor)连接并进行该IGBT的控制。即,在使用第一驱动电路的情况下,也可以设为第一驱动电路的输出目的地的n沟道的IGBT。如此,将适当的功率晶体管设为驱动电路的输出目的地也能够作为前述的各实施方式的范围。另外,关于该其他MOSFET也是只要性能、工序的容易程度等适当即可,例如也能够置换为双极晶体管等。

- 栅极驱动电路、级联栅极驱动电路以及级联栅极驱动电路的驱动方法

- 栅极驱动电路、栅极驱动电路的控制方法和栅极驱动器