一种利用扩展I2C协议调试芯片的方法、存储介质、电子设备

文献发布时间:2023-06-19 10:11:51

技术领域

本发明涉及芯片调试技术领域,特别涉及一种利用扩展I2C协议调试芯片的方法、存储介质、电子设备。

背景技术

在芯片开发阶段需要利用I2C接口对芯片进行调试设置,但在使用的时候I2C需要被隔离。如果隔离不好,在热拔插的应用中,芯片有可能进入非预想的状态,需要多次插拔来使得芯片正常工作。

为了避免插拔误触发I2C接口,通常会使用一个额外管脚作为选项输入来隔离I2C接口。例如,用一个上拉电阻来设置这个管脚为“1”,作为实际应用时隔离I2C的条件。如果需要调试就把这个管脚设置为“0”。这种方法的缺点就是多一个管脚,尤其在芯片面积有限的情况下,这个缺点尤其突出。

发明内容

本发明要解决的技术问题是提供一种可以实现隔离I2C的需求而不需要额外增加管脚的调试芯片方法。其采用如下技术方案:

为了解决上述问题,本发明提供了一种利用扩展I2C协议调试芯片的方法,其包括:

扩展I2C协议至通信时隙外,定义一个调试状态:开始和停止调试的条件是保持SDA高电平,且SCL分别为高-低电平切换和低-高电平切换,在调试状态下对芯片进行调试;

在I2C接口空闲时利用SCL处于高电平的特性作为输入,结合逻辑电路隔离I2C接口。

作为本发明的进一步改进,芯片内部信号线通过逻辑电路与SCL连接,使得当SCL处于高电平时,信号线的输出端均为低电平,实现I2C接口和被调试芯片的隔离。

作为本发明的进一步改进,所述信号线包括overwrite_mode_o和test_mode_o,两个信号线overwrite_mode_o和test_mode_o通过逻辑电路与SCL连接;当SCL处于高电平时,overwrite_mode_o和test_mode_o均为低电平,实现I2C接口和被调试芯片的隔离;当I2C接口通信时,overwrite_mode_o和test_mode_o随着I2C的通信改变,但不会影响最终写入或读出的寄存器数据;当处于调试状态时,SCL处于低电平,overwrite_mode_o和test_mode_o不受SCL控制,而是直接或间接受寄存器数据控制。

本发明还公开了一种计算机可读存储介质,所述存储介质包括存储的程序,其中,所述程序执行上述任意一项所述的调试方法。

本发明还公开了一种电子设备,其包括:一个或多个处理器,存储器以及一个或多个程序,其中,所述一个或多个程序被存储在所述存储器中,并且被配置为由所述一个或多个处理器执行,所述一个或多个程序包括用于执行上述任意一项所述的调试方法。

本发明的有益效果:

本发明利用扩展I2C协议调试芯片的方法通过扩展I2C协议至通信时隙外,定义一个调试状态,在该调试状态下可以进行芯片调试而不影响I2C已经写入寄存器的值,同时,利用I2C接口本身的上拉电阻,不需要额外管脚,完成芯片使用时隔离I2C接口的要求,降低了设计复杂度和系统成本。

上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其他目的、特征和优点能够更明显易懂,以下特举较佳实施例,并配合附图,详细说明如下。

附图说明

图1是I2C协议在开始和停止时的波形图;

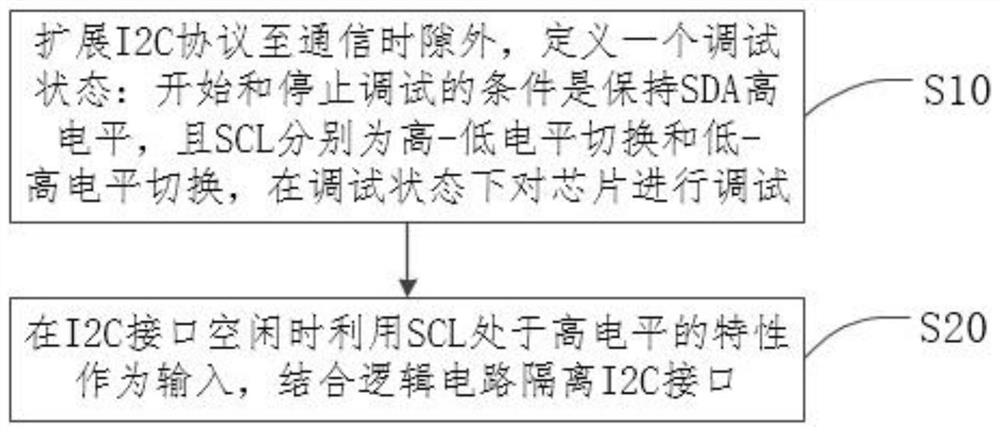

图2是本发明优选实施例中利用扩展I2C协议调试芯片的方法的流程图;

图3是本发明优选实施例中扩展后的I2C协议在开始和停止时的波形图;

图4是I2C协议在实际应用情况下的波形图;

图5是本发明优选实施例中芯片内部信号线通过逻辑电路与SCL连接结构图。

具体实施方式

下面结合附图和具体实施例对本发明作进一步说明,以使本领域的技术人员可以更好地理解本发明并能予以实施,但所举实施例不作为对本发明的限定。

如图1所示,I2C协议规定了开始和停止I2C条件是保持SCL高电平,且SDA分别为高-低和低-高切换。

如图2所示,本发明优选实施例中的利用扩展I2C协议调试芯片的方法,包括以下步骤:

S10、扩展I2C协议至通信时隙外,定义一个调试状态:开始和停止调试的条件是保持SDA高电平,且SCL分别为高-低电平切换和低-高电平切换,在调试状态下对芯片进行调试;参照图3。

在实际应用的情况下,由于I2C接口有上拉电阻,所以SCL始终处于高电平,是一个硬件产生的条件,如图4所示,可以利用SCL这个特性来作为输入隔离I2C接口。

S20、在I2C接口空闲时利用SCL处于高电平的特性作为输入,结合逻辑电路隔离I2C接口。

其中,芯片内部信号线通过逻辑电路与SCL连接,使得当SCL处于高电平时,信号线的输出端均为低电平,实现I2C接口和被调试芯片的隔离。

如图5所示,在其中一实施例中,信号线包括overwrite_mode_o和test_mode_o,两个信号线overwrite_mode_o和test_mode_o通过逻辑电路与SCL连接;当SCL处于高电平时,overwrite_mode_o和test_mode_o均为低电平,实现I2C接口和被调试芯片的隔离;当I2C接口通信时,overwrite_mode_o和test_mode_o随着I2C的通信改变,但不会影响最终写入或读出的寄存器数据;当处于调试状态时,SCL处于低电平,overwrite_mode_o和test_mode_o不受SCL控制,而是直接或间接受寄存器数据控制,实现调试目的。

本发明优选实施例还公开了一种计算机可读存储介质,所述存储介质包括存储的程序,其中,所述程序执行上述任意一项所述的调试方法。

本发明优选实施例还公开了一种电子设备,其包括:一个或多个处理器,存储器以及一个或多个程序,其中,所述一个或多个程序被存储在所述存储器中,并且被配置为由所述一个或多个处理器执行,所述一个或多个程序包括用于执行上述任意一项所述的调试方法。

本发明利用扩展I2C协议调试芯片的方法通过扩展I2C协议至通信时隙外,定义一个调试状态,在该调试状态下可以进行芯片调试而不影响I2C已经写入寄存器的值,同时,利用I2C接口本身的上拉电阻,不需要额外管脚,完成芯片使用时隔离I2C接口的要求,防止误触发,降低了设计复杂度和系统成本。利用SCL本身的上拉电阻特点作为硬件产生的条件也可以供给其它需要硬件条件的电路,例如上电复位(POR)电路来确保芯片成功启动。

以上实施例仅是为充分说明本发明而所举的较佳的实施例,本发明的保护范围不限于此。本技术领域的技术人员在本发明基础上所作的等同替代或变换,均在本发明的保护范围之内。本发明的保护范围以权利要求书为准。

- 一种利用扩展I2C协议调试芯片的方法、存储介质、电子设备

- 一种I2C从设备的调试方法、I2C主设备及存储介质