一种反熔丝一次性可编程存储单元

文献发布时间:2023-06-19 10:32:14

本申请要求于2020年3月12日提交美国专利局、申请号为16816537、发明名称为“Antifuse OTP structures with hybrid low-voltage devices具有混合低压器件的反熔丝OTP结构”的美国专利申请的优先权,其全部内容通过引用结合在本申请中。

技术领域

本发明涉及半导体存储器技术领域,具体涉及一种一次性可编程otp存储器。

背景技术

嵌入式非易失性存储器(envm)技术已经用于许多应用中,诸如后硅调谐,存储器修复,在线现场测试和安全id存储。Envm也是用于自愈应用的关键组件,其中关于时间相关故障机制(诸如电路老化)的信息必须在系统断电周期期间被保留。反熔丝一次可编程(af-otp)nvm存储器已被广泛用于标准逻辑过程中的存储器修复。

反熔丝在本机未编程状态下是不导电的,并且在被编程时变得导电,因此名称反熔丝。在集成电路中,反熔丝通常由夹在两个导体之间的薄介电层构成。为了编程反熔丝,在两个导体之间施加高电压。这导致薄介电层的物理和永久击穿以及两个导体之间的电流传导路径的形成。因此,反熔丝可以用作存储器元件。反熔丝的编程状态表示数据"1"和未编程状态"0",反之亦然。一旦被编程,反熔丝存储器就不能恢复到未编程状态,即,它是一次性可编程存储器。即使在电源被关闭之后,反熔丝也保持导电或不导电状态,从而使数据非易失性。因此,反熔丝存储器是非易失性otp存储器。

为了提供高电压来编程反熔丝电容器,选择晶体管通常在器件中具有厚栅极介电层,并且具有高电压结。然而,由于需要更宽的沟道长度和宽度,具有高电压结的高压晶体管器件将花费更多的硅面积,并且更多的硅面积将直接与更高的成本和更低的积分密度相关。另一方面,反熔丝电容器通常用较薄的栅极介电层构建以用于更容易的编程,并且低电压结通常与其低压器件一起应用。

因此需要具有高结构简单性和高集成密度的反熔丝otp存储器单元。

发明内容

鉴于上文,本发明提供一种反熔丝otp存储器位单元,其包括反熔丝电容器和金属氧化物半导体场效应晶体管(mosfet)。Mosfet是被实现为编程或访问反熔丝电容器的选择晶体管。一种新颖的存储单元包括混合结构:用于较小硅脚印刷的低电压栅极介电层和高电压结或混合高电压和低电压结。新颖的选择晶体管包括低电压栅极介电层和低电压结或混合高电压和低电压结,或高电压结,用于高电压编程和较小硅面积两者。

在一个一般方面,本发明涉及一种反熔丝一次性可编程存储单元,其包括基板;混合选择晶体管,所述混合选择晶体管形成在所述基板上,所述混合选择晶体管包括:形成在所述基板上的第一栅极介电层,其中所述第一栅极介电层薄于40nm,所述第一栅极介电层启用低电压选择晶体管装置;形成在所述栅极介电层上的第一栅极;在所述基板中形成的第一高压结;以及形成于所述基板中的低电压结,其中所述选择晶体管的源极和漏极由所述第一高电压结和所述低电压结形成;以及在所述基板上形成的混合反熔丝电容器,所述混合反熔丝电容器包括形成在所述基板上的第二栅极电介质层,其中所述第二栅极电介质层薄于40nm,这使得能够实现低电压反熔丝电容器器件;形成在所述栅极介电层上的第二栅极;形成于所述基板中的第二高压结;以及形成于所述基板中的第三高压结,其中所述反熔丝电容器的源极和漏极分别由所述第二高电压结和所述第三高电压结形成。

系统的实施方式可以包括以下中的一个或多个。反熔丝电容器的第二高电压结和第三高电压结可以由基板中的沟道分开。反熔丝电容器的第二高压结和第三高电压结可以电连接。第一栅极介电层或第二栅极介电层可薄于 30nm。混合选择晶体管可以是在3.3v或以下操作的低电压器件。混合反熔丝电容器可以是在3.3v或以下操作的低电压器件。第一高压结或第二高压结或第三高电压结可以具有高于3.3伏的阈值结击穿电压。第一高压结或第二高压结或第三高电压结可以具有高于5伏的阈值结击穿电压。第二高压结和第三高电压结可以电连接。低电压结可以包括在比远离第一栅极介电层的第二掺杂区更低的掺杂水平下与第一栅极介电层相邻的第一掺杂区。第一高电压结可以包括在比远离第一栅极介电层的第二掺杂区更低的掺杂水平下与第一栅极介电层相邻的第一掺杂区。第一高电压结还可以具有基本上均匀的掺杂水平。第二高电压结或第三高电压结可以包括与第二栅极介电层相邻的位于比远离第二栅极介电层的第二掺杂区更低的掺杂水平的第一掺杂区。第二高电压结或第三高电压结可以具有基本上均匀的掺杂水平。

在另一个一般方面,本发明涉及一种反熔丝一次性可编程存储单元,其包括:基板;低电压选择晶体管,形成在所述基板上,所述低电压选择晶体管包括:形成在所述基板上的第一栅极介电层,其中所述第一栅极介电层薄于40nm,所述第一栅极介电层启用低电压选择晶体管装置;形成在所述栅极介电层上的第一栅极;在所述基板中形成的第一低电压结;以及形成于所述基板中的第二低电压结,其中所述选择晶体管的源极和漏极由所述第一低电压结和所述第二低电压结形成;以及在所述基板上形成的混合反熔丝电容器,所述混合反熔丝电容器包括:形成在所述基板上的第二栅极电介质层,其中所述第二栅极电介质层薄于40nm,这使得能够实现低电压反熔丝电容器器件;形成在所述栅极介电层上的第二栅极;形成在所述基板中的第一高压结;以及形成在所述基板中的第二高压结,其中所述反熔丝电容器的源极和漏极分别由所述第一高压结和所述第二高压结形成。

反熔丝一次性可编程存储单元的实现可以包括以下中的一个或多个。反熔丝电容器的第一高压结和第二高压结可以由基板中的沟道隔开。所述反熔丝电容器的所述第一高压结和所述第二高压结电连接。第一栅极介电层或第二栅极介电层可薄于30nm。混合选择晶体管可以是在3.3v或以下操作的低电压器件。混合反熔丝电容器可以是在3.3v或以下操作的低电压器件。第一高压结或第二高压结可以具有高于3.3伏的阈值结击穿电压。第二低压结和第一高压结可以电连接。所述第一低电压结或所述第二低电压结可以包括与所述第一栅极介电层在比远离所述第一栅极介电层的第二掺杂区更低的掺杂水平下的第一掺杂区。第一高电压结或第二高电压结可以包括与第二栅极介电层相邻的第一掺杂区,该第一掺杂区在比远离第二栅极介电层的第二掺杂区低的掺杂水平下与第二栅极介电层相邻。

附图说明

为了说明本发明的技术方案,附图中简要描述的实施例需要用于描述实施例。显然,以下附图仅描述了本发明的示例。对于本领域的技术人员,也可以根据这些附图获得其它附图,而没有任何创造性的工作。

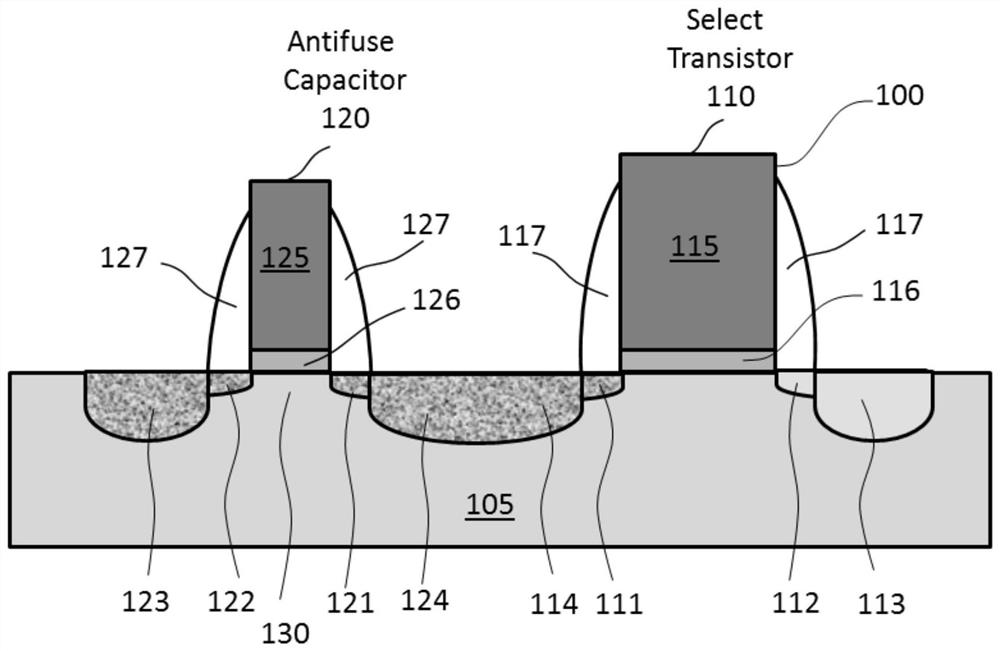

图1a是根据本发明的一些实施例的具有混合低电压反熔丝电容器和混合低电压选择晶体管的反熔丝otp存储器单元的截面图;

图1b是图1a中所示的反熔丝otp存储器单元的示意性平面图;

图1c是根据本发明的一些实施例的具有混合低电压反熔丝电容器和混合低电压选择晶体管的另一反熔丝otp存储器单元的截面图;

图2是与图1a中的反熔丝otp存储器单元相关的反熔丝otp存储器单元的截面图;

图3是根据本发明的一些实施例的具有混合低电压反熔丝电容器和低电压选择晶体管的又一反熔丝otp存储器单元的截面图;

图4是与图3中的反熔丝otp存储器单元相关的反熔丝otp存储器单元的截面图;

图5是根据本发明的一些实施例的具有混合低电压反熔丝电容器和混合低电压选择晶体管的再一反熔丝otp存储器单元的截面图;

图6是与图5中的反熔丝otp存储器单元相关的反熔丝otp存储器单元的截面图;

图7是根据本发明的一些实施例的具有混合低电压反熔丝电容器和混合低电压选择晶体管的一可选反熔丝otp存储器单元的截面图;

图8是构建图1-7所示的反熔丝otp存储器单元的过程流程图;

图9是具有混合低电压反熔丝电容器和与图1a和1b相关的混合低电压选择晶体管的另一可选反熔丝otp存储器单元的截面图;

图10是具有混合低电压反熔丝电容器和与图2相关的混合低电压选择晶体管的又一可选反熔丝otp存储器单元的截面图;

图11是构建图9-10所示的反熔丝otp存储单元的工艺流程图。

具体实施方式

在本发明的实施例中参照附图描述本发明的实施例中的技术方案。

在一些实施例中,反熔丝otp存储器使用金属氧化物半导体(mos)电容器作为反熔丝元件。Mos电容器连接到称为选择晶体管(通常为金属氧化物半导体场效应晶体管(mosfet))的存取装置以形成反熔丝存储器位单元。参考图1a-1c,反熔丝otp存储单元100包括选择晶体管110和反熔丝电容器120,选择晶体管110包括在基板105上的栅极电介质116上的栅极115,栅极电介质116 包括薄介电层,其使得选择晶体管110成为低压器件。对于氧化硅,薄介电层通常低于40埃,且可进一步薄于30埃。反熔丝电容器120包括位于基板105上的栅极电介质126上的栅极125,栅极电介质126包括薄电介质层。对于氧化硅,薄介电层通常低于40埃,并且可以进一步薄于30埃,这使得反熔丝电容器120 也是低电压器件。低电压装置可在3.3v或以下操作,或进一步在2.5v或以下操作。

通过轻掺杂区111,112和深掺杂区113,114分别形成选择晶体管110的结 (例如,源极或漏极)。

反熔丝电容器120的结(例如源极或漏极)分别由轻掺杂区121,122和深掺杂区123,124形成。反熔丝电容器120的结(分别由掺杂区122,123和掺杂区121,124形成)被沟道130隔开,并且不连接在基板105中(与下面的图2中描述的示例相反))。

通过在两个掺杂工艺之间施加间隔结构117,127,在沟道的两侧上形成轻掺杂区111,112和121,122和深掺杂区113,114和123,124的组合。

选择晶体管110和反熔丝电容器120的源极/漏极和栅极115,125具有相同的导电类型。晶体管沟道区(即,栅极电介质下方的硅基板105)具有相反的导电类型。在选择晶体管110中,例如,如果由掺杂区域111,114和掺杂区域 112,113分别形成的栅极115和源极/漏极是n型,则栅极电介质116下方的基板 105的区域是p型。因此,源极/漏极区与反向掺杂硅基板105形成pn结。类似地,对于反熔丝电容器120,如果由掺杂区121,124和122,123分别形成的栅极125 和源极/漏极是n型,则栅极电介质126下面的基板105的区域是p型。

掺杂区111,112和121,122是轻掺杂的,其中掺杂剂水平的电活性浓度可以在1x10

掺杂区113,112连接,并且它们是导电的。类似地,掺杂区111,114, 124和121被连接,并且它们是导电的。掺杂区122,123也连接。在反熔丝编程期间,在栅极115上施加电压以导通选择晶体管110,即,在栅极电介质116 下方的基板105中形成导电沟道,同时,将编程电压施加到掺杂区域113。通过栅极电介质116下方的导电路径,编程电压实际上被施加在栅极电介质126 上以引起电介质击穿。将在栅极125与掺杂区124或掺杂区123之间测量低电阻。

为了使晶体管正常工作,结偏置需要低于结击穿电压。对于低电压晶体管,可以使用更浅和更陡的结而不引起击穿。因此,设备可以具有更好的短信道行为。这种结的形成需要较浅的注入,较低的温度和较短的退火。对于高压晶体管,避免可能导致击穿的峰值结电场是关键的;因此必须相应地调整结轮廓。为了避免在结处引入非常高的峰值场,优选更渐进的结掺杂分布。这通常意味着更深的注入,更长的(可能是多个)退火步骤。因此,这种结可以处理较高的偏置电压。

选择晶体管110中的栅极115和栅极电介质116支持用于高编程良率的低电压器件。掺杂区111/114形成高压(hv)结,而掺杂区112/113与用于选择晶体管110的基板105形成低压(lv)结,hv结的击穿阈值电压可以高于3.3v或高于5v,这取决于器件的技术节点。Lv结的击穿阈值电压可以低于3.2v,或者低于3.3v,这取决于设备的技术节点。

反熔丝otp存储单元100的一个重要方面是反熔丝电容器120中的栅极125 和栅极电介质126以及选择晶体管110中的栅极115和栅极电介质116都支持低电压器件,这降低了硅脚印刷。此外,选择晶体管110包括由掺杂区112/113 形成的低电压(lv)结,其也减少了硅脚印刷。由掺杂区111/114形成的另一高电压结使得选择晶体管110能够具有改进的编程良率。

在反熔丝电容器120中,掺杂区122/123和121/124与基板105形成hv结,hv 结的结击穿阈值电压可以高于3.3v或高于5v,这取决于器件的技术节点。低电压栅极介电层(即,lv器件)和高电压结的组合提供低硅脚印刷和高编程良率。

由于针对反熔丝电容器120和选择晶体管110两者形成hv结,所以可以组合深掺杂区域114和124以简化结构和过程。因此,由用于选择晶体管110的掺杂区111,114和由用于反熔丝电容器120的掺杂区121,124形成的hv结形成的 hv结导电连接。

在一些实施例中,参考图2,反熔丝otp存储器单元200包括选择晶体管110 和反熔丝电容器120以及相关联的组件,类似于如上所述的反熔丝otp存储器单元100。反熔丝otp存储单元100的差异在于,反熔丝otp存储单元200中的轻掺杂区域121,122被电连接,而不是被通道分隔开。

反熔丝在本机未编程状态下是不导电的,并且在被编程时变得导电。通常,在反熔丝电容器上,例如在深掺杂区域123与栅极125之间施加电压,测量电流以确定反熔丝存储器单元是否被编程。然而,如果轻掺杂区121和122 未连接在栅极氧化物126下方的基板105中(即,由图1a中的沟道130分开),则部分电流将通过图1a中所示的沟道130泄漏到基板105中,并且电流可能不稳定。通过合并掺杂区域121和122,阻挡到基板105中的电流泄漏路径,并且可以有效地减小电流测量噪声。

在一些实施例中,参考图3,反熔丝otp存储器单元300包括选择晶体管310 和反熔丝电容器320。选择晶体管310包括在基板305上的栅极电介质316上的栅极315。栅极电介质316包括薄电介质层,其使得选择晶体管310成为低压器件。对于氧化硅,薄介电层可以是40埃或更薄,或者还可以进一步薄于30埃。反熔丝电容器320包括在基板305上的栅极电介质326上的栅极325。栅极电介质326包括薄电介质层,其使得反熔丝电容器320也是低电压器件。

通过轻掺杂区311,312和深掺杂区313,314分别形成选择晶体管310的结 (例如,源极或漏极),两个结在基板305中分离。

反熔丝电容器320的结(例如源极或漏极)分别由轻掺杂区321,322和深掺杂区323,324形成。反熔丝电容器320的结(分别由掺杂区322,323和掺杂区321,324形成)被沟道330隔开,并且不连接在基板305中(与下面的图4中描述的示例相反)。

通过在两个掺杂工艺之间施加间隔结构317,327,在沟道的两侧上形成轻掺杂区311,312和321,322和深掺杂区313,314和323,324的组合。

选择晶体管310和反熔丝电容器320的源极/漏极和栅极315,325具有相同的导电类型。晶体管沟道区(即,栅极电介质下方的硅基板305)具有相反的导电类型。在选择晶体管310中,例如,如果由掺杂区域311,314和掺杂区域 312,313分别形成的栅极315和源极/漏极是n型,则栅极电介质316下方的基板 305的区域是p型。因此,源极/漏极区域与反向掺杂的硅基板305形成pn结。类似地,对于反熔丝电容器320,如果由掺杂区域321,324和322,323分别形成的栅极325和源极/漏极是n型,则栅极电介质326下方的基板305的区域是p型。

掺杂区311,312和321,322是轻掺杂的,其中掺杂剂水平的电活性浓度可以在1x10

掺杂区313,312连接,并且它们是导电的。类似地,掺杂区域311,314, 324和321被连接,并且它们是导电的。掺杂区322,323也连接。在反熔丝编程期间,在栅极315上施加电压以接通选择晶体管310,即,在栅极电介质316 下方的基板305中形成导电沟道。同时,将编程电压施加到掺杂区域3132。通过栅极电介质316下方的导电路径,将编程电压实际施加在栅极电介质326上以引起电介质击穿。将在栅极325与掺杂区324之间或在栅极325与掺杂区3235 之间测量低电阻。

选择晶体管310中的栅极315和栅极电介质316支持用于区域缩放的低压器件。掺杂区311/314和掺杂区312/313形成与选择晶体管310的基板305的低压 (lv)结,hv结的击穿阈值电压可以高于3.3v或高于5v,这取决于器件的技术节点。Lv结的击穿阈值电压可以低于3.2v,或者低于3.3v,这取决于设备的技术节点。

反熔丝otp存储单元300的一个重要方面是,反熔丝电容器320中的栅极325 和栅极电介质326以及选择晶体管310中的栅极315和栅极电介质316都支持低电压器件,这降低了硅脚印刷。此外,选择晶体管310包括由掺杂区312/313 和311/314形成的低电压(lv)结,这也减少了硅脚印刷。

在一些实施例中,参考图4,反熔丝otp存储器单元400包括选择晶体管310 和反熔丝电容器320以及相关联的组件,类似于上面关于图3所描述的反熔丝 otp存储器单元300。反熔丝otp存储器单元300的差异在于反熔丝otp存储器单元 400中的轻掺杂区域321,322被电连接而不是被通道分开。

反熔丝在本机未编程状态下是不导电的,并且在被编程时变得导电。通常,在反熔丝电容器上施加电压,例如,在深掺杂区域323与栅极325之间或在深掺杂区域324与栅极325之间施加电流以确定反熔丝存储器单元是否被编程。然而,如果轻掺杂区321和322未连接在栅极氧化物326下方的基板305中 (即,由图3中所示的沟道330分开),则部分电流将通过沟道330泄漏到基板 305中(图3);电流测量将不稳定。通过合并掺杂区域321和322,阻挡到基板305中的电流泄漏路径,并且可以有效地减小电流测量噪声。

在一些实施例中,参考图5,反熔丝otp存储器单元500包括选择晶体管510 和反熔丝电容器520。选择晶体管510包括在基板505上的栅极电介质516上的栅极515。栅极电介质516包括薄电介质层,其使得选择晶体管510成为低压器件。对于氧化硅,薄介电层可以是40埃或更薄,或者还可以进一步薄于30埃。反熔丝电容器520包括在基板505上的栅极电介质526上的栅极525。栅极电介质526包括薄电介质层,其使得反熔丝电容器520也是低电压器件。

选择晶体管510的结(例如,源极或漏极)分别由轻掺杂区511,512和深掺杂区513,514形成,两个结在基板505中分离。

反熔丝电容器520的结(例如源极或漏极)分别由轻掺杂区521,522和深掺杂区523,524形成。反熔丝电容器520的结(分别由掺杂区522,523和掺杂区521,524形成)被沟道530隔开,并且不连接在基板505中(与下面的图6中描述的示例相反)。

通过在两个掺杂工艺之间施加间隔结构517,527,在沟道的两侧上形成轻掺杂区511,512和521,522和深掺杂区513,514和523,524的组合。

选择晶体管510和反熔丝电容器520的源极/漏极和栅极515,525具有相同的导电类型。晶体管沟道区(即,栅极电介质下方的硅基板505)具有相反的导电类型。在选择晶体管510中,例如,如果由掺杂区域511,514和掺杂区域 512,513分别形成的栅极515和源极/漏极是n型,则栅极电介质516下面的基板 505的区域是p型。因此,源极/漏极区域与反向掺杂的硅基板505形成pn结。类似地,对于反熔丝电容器520,如果由掺杂区域521,524和522,523分别形成的栅极525和源极/漏极是n型,则栅极电介质526下方的基板505的区域是p型。

掺杂区511,512和521,522是轻掺杂的,其中掺杂剂水平的电活性浓度可以在1x10

掺杂区域513,512被连接,并且它们是导电的。类似地,掺杂区域511, 514,524和521被连接,并且它们是导电的。掺杂区522,523也连接。在反熔丝编程期间,在栅极515上施加电压以接通选择晶体管510,即,在栅极电介质516下面的基板505中形成导电沟道。同时,将编程电压施加到掺杂区域 5132。通过栅极电介质516下方的导电路径,将编程电压实际施加在栅极电介质526上以引起电介质击穿。将在栅极525与掺杂区524之间或在栅极525与掺杂区5233之间测量低电阻。

选择晶体管510中的栅极515和栅极电介质516支持用于高编程良率的低电压器件。掺杂区511/514和掺杂区512/513与基板505形成高压(hv)结,用于选择晶体管510。hv结的击穿阈值电压可以高于3.3v或高于5v,这取决于器件的技术节点。Lv结的击穿阈值电压可以低于3.2v,或者低于3.3v,这取决于设备的技术节点。

反熔丝otp存储单元500的一个重要方面是,反熔丝电容器520中的栅极525 和栅极电介质526以及选择晶体管510中的栅极515和栅极电介质516都支持低电压器件,这降低了硅脚印刷。此外,选择晶体管510中的高电压结可以提供增加的编程良率。

在一些实施例中,参考图6,反熔丝otp存储器单元600包括选择晶体管510 和反熔丝电容器520以及相关联的组件,类似于上面关于图5所描述的反熔丝 otp存储器单元500。反熔丝otp存储器单元500的差异在于反熔丝otp存储器单元 600中的轻掺杂区域521,522被电连接,而不是被通道分开。

反熔丝在本机未编程状态下是不导电的,并且在被编程时变得导电。通常,在反熔丝电容器上施加电压,例如,在深掺杂区域523与栅极525之间或在深掺杂区域524与栅极525之间施加电流以确定反熔丝存储器单元是否被编程。然而,如果轻掺杂区521和522未连接在栅极氧化物526下方的基板505中 (即,由图5中所示的沟道530分开),则部分电流将通过沟道530泄漏到基板 505中(图5);电流测量将不稳定。通过合并掺杂区域521和522,阻挡到基板505中的电流泄漏路径,并且可以有效地减小电流测量噪声。

在一些实施例中,参考图7,反熔丝otp存储器单元700包括选择晶体管710 和反熔丝电容器720。选择晶体管710包括在基板705上的栅极电介质716上的栅极715。栅极电介质716包括薄电介质层,其使得选择晶体管710成为低压器件。对于氧化硅,薄介电层可以是40埃或更薄,或者还可以进一步薄于30埃。反熔丝电容器720包括在基板705上的栅极电介质726上的栅极725。栅极电介质726包括薄电介质层,这使得反熔丝电容器720也是低电压器件。

选择晶体管710的结(例如,源极或漏极)分别由轻掺杂区711,712和深掺杂区713,714形成

反熔丝电容器720的结(例如,源极或漏极)分别由轻掺杂区721,722和深掺杂区723,7246形成。反熔丝电容器720的结(分别由掺杂区722,723和掺杂区721,724形成)由沟道730分开并且不连接在基板705中。

通过在两个掺杂工艺之间施加间隔结构717,727,在沟道的两侧上形成轻掺杂区711,712和721,722和深掺杂区713,714和723,724的组合。

选择晶体管710和反熔丝电容器720的源极/漏极和栅极715,725具有相同的导电类型。晶体管沟道区(即,栅极电介质下方的硅基板705)具有相反的导电类型。在选择晶体管710中,例如,如果由掺杂区域711,714和掺杂区域 712,713分别形成的栅极715和源极/漏极是n型,则在栅极电介质716下方的基板705的区域是p型。因此,源极/漏极区域与反向掺杂的硅基板705形成pn结。类似地,对于反熔丝电容器720,如果由掺杂区域721,724和722,723分别形成的栅极725和源极/漏极是n型,则在栅极电介质726下面的基板705的区域是p 型。

掺杂区711,712和721,722是轻掺杂的,其中掺杂剂水平的电活性浓度可以在1x10

掺杂区域713,712被连接,并且它们是导电的。类似地,掺杂区711,714,724和721连接,并且它们是导电的。掺杂区722,723也连接。在反熔丝编程期间,在栅极715上施加电压以导通选择晶体管710,即,在栅极电介质716下方的基板705中形成导电沟道。同时,将编程电压施加到掺杂区域7136。通过栅极电介质716下方的导电路径,将编程电压实际施加在栅极电介质726上以引起电介质击穿。将在栅极725与掺杂区724或掺杂区7235之间测量低电阻。

为了使晶体管正常工作,结偏置需要低于结击穿电压。对于低电压晶体管,可以使用更浅和更陡的结而不引起击穿。因此,设备可以具有更好的短信道行为。这种结的形成需要较浅的注入,较低的温度和较短的退火。对于高压晶体管,避免可能导致击穿的峰值结电场是关键的;因此必须相应地调整结轮廓。为了避免在结处引入非常高的峰值场,优选更渐进的结掺杂分布。这通常意味着更深的注入,更长的(可能是多个)退火步骤。因此,这种结可以处理较高的偏置电压。

在选择晶体管710中,栅极715和栅极电介质716支持用于高编程良率的低电压器件。掺杂区711/714形成高压(hv)结,而掺杂区712/713与基板705形成低电压(lv)结以用于选择晶体管710。hv结的击穿阈值电压可高于3.3v或高于5v,这取决于器件的技术节点。Lv结的击穿阈值电压可以低于3.2v,或者低于3.3v,这取决于设备的技术节点。

反熔丝otp存储单元700的一个重要方面是反熔丝电容器720中的栅极725 和栅极电介质726以及选择晶体管710中的栅极715和栅极电介质716都支持低电压器件,这降低了硅脚印刷。此外,选择晶体管710包括由掺杂区712/713 形成的低电压(lv)结,其也减少了硅脚印刷。由掺杂区711/714形成的另一高电压结使得选择晶体管710能够具有改进的编程良率。

在反熔丝电容器720中,掺杂区721/724与基板705形成hv结,而掺杂区 722/723与基板705形成lv结。取决于器件的技术节点,hv结的击穿阈值电压可以高于3.3v或高于5v。Lv结的击穿阈值电压可以低于3.2v,或者低于3.3v,这取决于设备的技术节点。低电压栅极介电层(即,lv器件),低电压结提供低硅脚印刷,而高电压结实现高编程良率。

由于针对反熔丝电容器720和选择晶体管710两者形成hv结,所以可以组合深掺杂区域714和724以简化结构和过程。因此,由用于选择晶体管710的掺杂区711,714和由用于反熔丝电容器720的掺杂区721,724形成的hv结形成的 hv结导电连接。

参考图8,构建上述反熔丝otp存储器单元的过程可以包括以下步骤。使用反熔丝otp存储单元100作为示例,首先,在衬底上为反熔丝电容器和选择晶体管形成薄栅介质层(步骤180),然后在基板上为反熔丝电容器和选择晶体管形成栅极电介质和栅极堆叠图案(步骤182)。为反熔丝电容器结形成轻掺杂区,并为选择晶体管结形成轻掺杂区(步骤184),在反熔丝电容器和选择晶体管栅极叠层周围建立间隔件(步骤186)。最后,使用掩模,为反熔丝电容器结形成深掺杂区,并为选择晶体管结形成深掺杂区(步骤188)。

在本申请的其他实施例中,构建上述反熔丝otp存储器单元的过程还可以包括以下步骤。首先,在基板上形成栅极介电层(步骤180)。然后为反熔丝电容器和基板上的选择晶体管产生栅极电介质和栅极图案(步骤182)。这些可以使用掩模和蚀刻技术来实现。在基板上形成用于反熔丝电容器的薄栅极电介质层,并且在基板上分别形成用于选择晶体管的较厚栅极电介质层。然后,在栅极介电层的顶部上形成栅极堆叠。反熔丝电容器和选择晶体管通过掩蔽和蚀刻来定义。通过在两个掺杂工艺之间施加间隔件结构117,127来形成轻掺杂区和深掺杂区的组合。

用于反熔丝电容器120的相对浅的掺杂区域(例如,图1a和1b中的121, 122)和用于选择晶体管110的相对浅的掺杂区域(例如,图1a和1b中的112, 112)通过单个掩模和离子注入或单独的掩模和离子注入形成(步骤184)。此外,可以在掺杂剂注入工艺之后添加退火步骤。

接着,在反熔丝电容器堆叠和选择晶体管栅极堆叠周围建立间隔件(步骤186)。用于选择晶体管110的深掺杂区113,114(图1a和1b)以及用于反熔丝电容器120的深掺杂区123,124(图1a和1b)在掩蔽工艺和离子注入中形成(步骤188)。

上述仅用作用于构建图1a-1b中所示的反熔丝otp存储单元的关键工艺步骤的示例,可以在上述处理步骤之间包括附加的处理步骤,并且在上述用于构建整个装置的处理步骤之前和之后需要其他处理步骤。例如,在步骤182-188 中,可以通过离子注入形成源极和漏极结。

在一些实施例中,反熔丝otp存储单元的高压结可以通过基板中的深掺杂区而不使用轻掺杂区形成。参考图9,otp存储器单元900包括混合低电压反熔丝电容器和混合低电压选择晶体管,类似于图1a和1b中的otp存储器单元100,不同之处在于没有形成轻掺杂区(图1a和图1b中的111,121,122),并且在这些区域中消除了抗冲穿离子注入。保持轻掺杂区112。

栅极电介质116包括薄介电层,其使选择晶体管110成为低压器件。反熔丝电容器120包括在基板105上的栅极电介质126上的栅极125。栅极电介质126 包括薄电介质层,其使得反熔丝电容器120也是低电压器件。对于氧化硅,薄介电层通常低于40埃,且可进一步薄于30埃。低电压装置可在3.3v或以下操作,或进一步在2.5v或以下操作。

选择晶体管110的结(例如,源极或漏极)分别由掺杂区112/113(低压结) 和掺杂区114(高压结)形成。两个结在基板105中分离,反熔丝电容器120的高压结(例如源极或漏极)分别由深掺杂区123,124形成。反熔丝电容器120 的高压结(分别由深掺杂区123和深掺杂区124形成)被沟道130隔开,并且不连接在基板105中(与下面的图10中描述的示例相反)。深掺杂区114,123, 124各自具有基本上均匀的掺杂水平。

在一些实施例中,参考图10,otp存储器单元1000包括混合低电压反熔丝电容器和混合低电压选择晶体管,类似于图2中的otp存储器单元200,除了未形成轻掺杂区域(图2中的111,121,122)。保持轻掺杂区112。

栅极电介质116包括薄介电层,其使选择晶体管110成为低压器件。反熔丝电容器120包括在基板105上的栅极电介质126上的栅极125。栅极电介质126 包括薄电介质层,其使得反熔丝电容器120也是低电压器件。对于氧化硅,薄介电层通常低于40埃,且可进一步薄于30埃。低电压装置可在3.3v或以下操作,或进一步在2.5v或以下操作。

选择晶体管110的结(例如,源极或漏极)分别由掺杂区112/113(低压结) 和掺杂区114(高压结)形成。两个结在基板105中分离,反熔丝电容器120的结(例如源极或漏极)分别由深掺杂区123,124形成。反熔丝电容器120的高电压结(分别由深掺杂区123和深掺杂区124形成)连接在基板105中以阻挡到基板105中的电流泄漏路径,这可以有效地减小电流测量噪声,如上所述。

图9-10所示的用于构建反熔丝otp存储单元900,1000的工艺可以包括与上面关于图8所述的步骤类似的步骤,通过在两个掺杂工艺之间施加间隔结构 117,127来形成轻掺杂区(112)和深掺杂区(113,113,123,134)的组合。

参考图11,使用反熔丝otp存储器单元900/1000作为示例,首先在基板上为反熔丝电容器和选择晶体管形成薄栅介质层(步骤1180)。然后在基板上为反熔丝电容器和选择晶体管形成栅极电介质和栅极堆叠图案(步骤1182)。通过掩蔽反熔丝电容器区域和选择晶体管结区域的另一侧,在选择晶体管结的一侧形成轻掺杂区(步骤1184)。在反熔丝电容器和选择晶体管栅极叠层周围建立间隔件(步骤1186)。使用掩模,为反熔丝电容器形成结的深掺杂区,并为选择晶体管形成结的深掺杂区(步骤1188)。最后退火以使深掺杂区域位于栅极电介质下方(步骤1190)。

在本申请的其他实施例中,上述过程还可包括:首先,在基板上形成栅极介电层(步骤1180)。然后为反熔丝电容器和基板上的选择晶体管产生栅极电介质和栅极图案(步骤1182)。这些可以使用掩模和蚀刻技术来实现。在基板上分别形成用于反熔丝电容器和用于选择晶体管的薄栅极介电层。然后,在栅极介电层的顶部上形成栅极堆叠。反熔丝电容器和选择晶体管通过掩蔽和蚀刻来定义。通过在两个掺杂工艺之间施加间隔件结构117,127来形成轻掺杂区和深掺杂区的组合。

通过掩蔽反熔丝电容器120和选择晶体管的另一侧,在选择晶体管的一侧上形成相对浅的掺杂区域(图9和10中的112)(步骤1184)。为反熔丝电容器和具有相同掩蔽处理的选择晶体管的另一侧消除了抗冲穿离子注入。此外,可以在掺杂剂注入工艺之后添加退火步骤。

接着,在反熔丝电容器堆叠和选择晶体管栅极堆叠周围建立间隔件(步骤1186)。在选择晶体管110的另一侧上的深掺杂区(图9和10中的114),以及反熔丝电容器120的深掺杂区(图9和10中的123,124)在掩蔽工艺和离子注入中形成(步骤1188)。随后可进行后续退火以驱动深掺杂区在栅极电介质下方。可以控制退火程度以允许深掺杂区123和124彼此电连接(图10)。因此形成用于选择晶体管和反熔丝电容器(1190)的结。

以上对所公开的实施例的描述使得本领域技术人员能够实现或使用本发明。对这些实施例的各种修改对于本领域技术人员而言将是显而易见的,并且在不脱离本发明的精神或范围的情况下,本文中定义的一般原理可以应用于其他实施例。因此,本发明将不限于本文中所展示的实施例,而是将符合与本文中所揭示的原理及新颖特征一致的最广范围。

- 一种反熔丝一次性可编程存储单元

- 一种反熔丝一次性可编程存储单元