半导体装置和制造方法

文献发布时间:2023-06-19 10:40:10

本申请是申请日为2016年2月22日、发明名称为“半导体装置和制造方法以及电子设备”的申请号为201680005481.2专利申请的分案申请。

相关申请的交叉参考

本申请要求享有于2015年3月5日提交的日本在先专利申请JP2015-043553的权益,其全部内容以引用的方式并入本文。

技术领域

本公开涉及一种半导体装置和制造方法以及电子设备,具体地,涉及一种使得可以容易地进行半导体芯片的接合的半导体装置和制造方法以及电子设备。

背景技术

设计了一种使半导体芯片电连接的技术,其通过使用凸块的倒装芯片接合而允许连接部分具有多个引脚和较低的电容,并且与现有技术中使用引线接合的连接相比,提高了半导体芯片之间的数据交换速度(例如,参见PTL 1)。

作为该技术的应用,有一项通过倒装芯片接合将外围电路堆叠在表面型固态成像装置的光收集面侧的技术。在表面型固态成像装置的光收集面侧进行倒装芯片接合需要在光收集面上形成凸块。然而,称为片上透镜的光收集结构形成在光收集面上,并且形成这些片上透镜的有机物质等透镜材料堆叠在包括外围电路区域以及像素区域的整个光收集面上。因此,为了将凸块连接到形成于半导体基板上的凸块连接用电极焊盘,在透镜材料上形成了开口,并且在开口上形成凸块。

在这种情况下,开口的深度增大了透镜材料的厚度的量,这使得难以形成高精度的凸块。这不仅适用于固态成像装置,而且也适用于使用聚酰亚胺等树脂作为保护膜的元件。

如上所述,在其中在形成有凸块的区域中存在透镜材料的情况下,不能容易地进行半导体芯片的接合。

另一方面,存在一种其中通过使第一半导体芯片和第二半导体芯片制成彼此面对并且通过凸块彼此接合而堆叠的固态成像装置,其中,在第一半导体芯片中形成有光电转换元件和连接用电极等,在第二半导体芯片中形成有A/D转换电路、信号处理电路、逻辑运算电路等以及收集用电极。

用于相机等的固态成像装置的像素数通常为数百万到数千万,因此需要大量的连接用电极;连接用电极以几十微米的间距的高密度进行配置。

为了精确地连接以高密度配置的连接用电极,需要在第一半导体芯片和第二半导体芯片的每个上都配置对准标记,并且在基于对准标记进行精确对准的同时进行凸块接合。

凸块接合方法包括芯片上芯片接合(chip-on-chip bonding)方法(例如,参见PTL2)和晶片上芯片接合(chip-on-wafer bonding)方法(例如,参见PTL 3)。芯片上芯片接合方法是一种以半导体芯片为单位使半导体芯片接合的方法,该方法接合效率低并且不适于批量生产。

晶片上芯片接合方法是一种将多个第二半导体芯片接合到半导体晶片上的方法,其中,第一半导体芯片在半导体晶片上配置成矩阵形式。虽然这种方法与芯片上芯片接合方法相比提高了接合效率,但是在将第二半导体芯片逐个接合到半导体晶片上的情况下,每个半导体晶片接合所花费的时间与待接合的第二半导体芯片的数量成比例地延长。这不仅导致了生产量的下降,而且还延长了凸块接合所需的热处理的时间,进而增大了半导体晶片上的热负荷。

在将多个第二半导体芯片共同接合到半导体晶片上的情况下,虽然每个半导体晶片的接合次数减少了,并因而使得接合所花费的时间缩短了,但是需要提前通过镜面反转来使半导体芯片具有对称轴的设计限制(例如,见PTL 4和5)。然而,由于固态成像装置从投射于第一半导体芯片上的透镜图像获得图像信号,所以不能容易地改变如东、南、西、北等的物理配置。也就是说,很难施加如镜面反转等设计限制。因此,不能容易地进行半导体芯片的接合。

[引用文献列表]

[专利文献]

PTL 1:JP 2006-49361A

PTL 2:JP 2011-243612A

PTL 3:JP 2001-196528A

PTL 4:JP 2001-168383A

PTL 5:JP 2012-503884T

发明内容

[技术问题]

如上所述,半导体芯片的接合不能够容易地进行。

鉴于这种情况完成的本公开使得可以容易地进行半导体芯片的接合。

[解决问题的方案]

根据本公开的第一实施方案,提供了一种半导体装置,包括:在第一半导体基板上的多个凸块;和在第一半导体基板上的所述多个凸块之外的区域中的透镜材料,其中,离所述透镜材料最近的凸块的离所述透镜材料最近的一侧与所述透镜材料的离所述凸块最近的一侧之间的距离大于离所述透镜材料最近的凸块的直径的两倍,以及其中,离所述透镜材料最近的凸块的离所述透镜材料最近的一侧与所述透镜材料的离所述凸块最近的一侧之间的距离大于所述凸块的最小间距。

本公开第一实施方案的电子设备对应于本公开第一实施方案的半导体装置。

根据本公开的第二实施方案,提供了一种半导体装置的制造方法,包括:在第一半导体基板上形成多个凸块,和在第一半导体基板上的所述多个凸块之外的区域中形成透镜材料,其中,离所述透镜材料最近的凸块的离所述透镜材料最近的一侧与所述透镜材料的离所述凸块最近的一侧之间的距离大于离所述透镜材料最近的凸块的直径的两倍,以及其中,离所述透镜材料最近的凸块的离所述透镜材料最近的一侧与所述透镜材料的离所述凸块最近的一侧之间的距离大于所述凸块的最小间距。

根据本公开的第三实施方案,提供了一种半导体装置,包括:具有矩形形状的第一半导体基板;具有矩形形状的第二半导体基板,其中,第二半导体基板的面积小于第一半导体基板的面积,并且第二半导体基板的第一边缘的至少部分区域与第一半导体基板的第一边缘的至少部分区域平齐;和具有矩形形状的第三半导体基板。第三半导体基板的面积小于第一半导体基板的面积,并且第三半导体基板的第一边缘的至少部分区域与第一半导体基板的第二边缘的至少部分区域平齐。

本公开第三实施方案的电子设备对应于本公开第三实施方案的半导体装置。

在本公开的第三实施方案中,第一半导体基板包括像素阵列,第二半导体基板和第三半导体基板各自包括至少一个逻辑电路。第一半导体基板的第一边缘和第二半导体基板的第一边缘中的每个对应于形成堆叠的半导体装置的第一边缘的划线。第一半导体基板的第二边缘和第三半导体基板的第一边缘中的每个对应于形成堆叠的半导体装置的第二边缘的划线。

根据本公开的第四实施方案,提供了一种半导体装置的制造方法,所述方法包括:将包括多个逻辑电路的第一半导体基板接合到在半导体晶片中配置成阵列的第二半导体基板和第三半导体基板上,其中第二半导体基板和第三半导体基板中的每个都包括像素阵列。第一半导体基板跨越第二半导体基板和第三半导体基板。所述方法还包括对第一半导体基板的第一边缘和第二半导体基板的第一边缘进行切割,以使得第一半导体基板的第一边缘和第二半导体基板的第一边缘彼此平齐。

在本公开的第四实施方案中,可以将包括多个逻辑电路的第四半导体基板接合到第二半导体基板和第五半导体基板上,其中,第四半导体基板跨越第二半导体基板和第五半导体基板。所述方法还可以包括对第二半导体基板的第二边缘和第四半导体基板的第一边缘进行切割,以使得第二半导体基板的第二边缘和第四半导体基板的第一边缘彼此平齐。在这个实施方案中,形成了其中第一半导体基板的第一边缘和第二半导体基板的第一边缘彼此平齐的半导体装置。此外,第二半导体基板的第二边缘和第四半导体基板的第一边缘可以彼此平齐。

[发明的有益效果]

根据本公开的第一和第三实施方案,可以容易进行半导体芯片的接合。

根据本公开的第二实施方案,可以制造允许半导体芯片容易地接合的半导体装置。

需要指出的是,这里描述的效果不一定是限制性的,并且可以表现出期望在本公开中描述的任意效果。

附图说明

图1是示出了作为本公开适用的半导体装置的CMOS图像传感器的第一实施方案的示例配置的框图;

图2是示出了图1的CMOS图像传感器的第一示例结构的图;

图3是描述图2的CMOS图像传感器的制造方法的概述图;

图4是描述凸块的形成方法的细节的图;

图5是示出了当透镜材料堆叠在半导体芯片的光照射侧的整个表面上时凸块的示例结构的图;

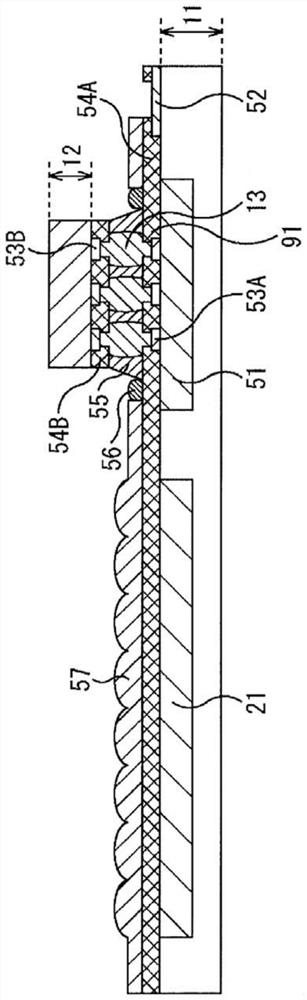

图6是示出了图1的CMOS图像传感器的第二示例结构的断面图;

图7是示意性地示出了图1的CMOS图像传感器的第三示例结构的断面图;

图8是示意性地示出了图1的CMOS图像传感器的第四示例结构的断面图;

图9是描述开口区域的一个例子的图;

图10是描述开口区域的另一个例子的图;

图11是示出了图7的区域的形状的一个例子的图;

图12是示出了图7的区域的形状的另一个例子的图;

图13是示出了图7的区域的形状的再一个例子的图;

图14是示出了本公开适用的CMOS图像传感器的第二实施方案的示例配置的概述图;

图15是示出了图14的CMOS图像传感器在划片之前的示例配置的立体图;

图16是沿着图15中的A-A的断面图;

图17是示出了其中北芯片和南芯片分别形成的CMOS图像传感器的示例结构的图;

图18是描述图14的CMOS图像传感器的制造方法的立体图;

图19是示出了作为本公开实施方案适用的电子设备的成像装置的示例配置的框图;

图20是示出了上述CMOS图像传感器的应用例的图。

具体实施方式

在下文中,将说明用于实施本公开的方式(以下称实施方案)。按以下顺序进行说明。

1.第一实施方案:CMOS图像传感器(图1-13)

2.第二实施方案:CMOS图像传感器(图14-18)

3.第三实施方案:成像装置(图19)

4.CMOS图像传感器的应用例(图20)

<第一实施方案>

(CMOS图像传感器的第一实施方案的示例配置)

图1是示出了作为本公开适用的半导体装置的互补金属氧化物半导体(CMOS)图像传感器的第一实施方案的示例配置的框图

CMOS图像传感器10包括经由凸块13连接的半导体芯片11和半导体芯片12。半导体芯片11和半导体芯片12各自包括半导体基板(例如,硅基板)和Cu、Al等的金属布线层。

在半导体芯片11上形成有像素区域21、像素驱动线22、垂直信号线23、垂直驱动单元24、列处理单元25-1以及系统控制单元27。在半导体芯片12上形成有列处理单元25-2,水平驱动单元26以及存储器和信号处理单元28。

在像素区域21中,像素配置成二维矩阵形式以进行成像,每个像素都包括产生电荷量与入射光的光量相当的电荷并将电荷蓄积在内部的光电转换元件。此外,像素驱动线22形成在像素区域21中的矩阵中的每个像素行中并且垂直信号线23形成在每个像素列中。

垂直驱动单元24包括移位寄存器和地址解码器等,并且例如以行为单位驱动像素区域21中的像素。像素驱动线22的一个端子与未示出的输出端子连接,该输出端子对应于垂直驱动单元24的每一行。虽然垂直驱动单元24的具体结构没有示出,但是垂直驱动单元24包括两个扫描系统、读出扫描系统和清除扫描系统。

读出扫描系统顺序选择每一行,从而以行为单位顺序读出来自像素的像素信号,并且从与选定行的像素驱动线22连接的输出端子输出选择信号等。因此,将来自由读出扫描系统选择的行中的像素的光电转换元件中蓄积的电荷的电信号作为像素信号读出并提供给垂直信号线23。

清除扫描系统在比由读出扫描系统进行的扫描早与快门速度对应的时间段时从与每一行的像素驱动线22连接的输出端子输出复位信号,以便从光电转换元件清除(复位)不必要的电荷。通过由清除扫描系统进行的这种扫描,逐行顺序进行所谓的电子快门操作。这里,电子快门操作是指使光电转换元件的电荷放电并且重新开始曝光(开始蓄积电荷)的操作。

列处理单元25-1是针对像素区域21的各列设置的信号处理电路的一部分,列处理单元25-2是另一部分。列处理单元25-1和列处理单元25-2经由凸块13彼此连接以形成针对像素区域21的各列设置的信号处理电路。每个信号处理电路对通过垂直信号线23从选定行的像素输出的像素信号进行诸如A/D转换处理和相关双采样(CDS)处理等信号处理。每个信号处理电路暂时保留信号处理之后的像素信号。

水平驱动单元26包括移位寄存器和地址解码器等,并且顺序选择每列的信号处理电路。通过由水平驱动单元26进行的这种选择扫描,将已经经受过各信号处理电路进行的信号处理的像素信号顺序输出到存储器和信号处理单元28。

系统控制单元27包括生成各种时序信号的时序发生器等。系统控制单元27基于由时序发生器生成的各种时序信号生成用于控制垂直驱动单元24、列处理单元25-1、列处理单元25-2和水平驱动单元26的控制信号。

系统控制单元27将用于控制垂直驱动单元24的控制信号提供给垂直驱动单元24,并将用于控制列处理单元25-1的控制信号提供给列处理单元25-1。此外,系统控制单元27经由凸块13将用于控制列处理单元25-2的控制信号提供给列处理单元25-2,以及经由凸块13将用于控制水平驱动单元26的控制信号提供给水平驱动单元26。

存储器和信号处理单元28对从水平驱动单元26输出的像素信号进行各种信号处理。此时,存储器和信号处理单元28必要时在例如内部存储器中储存信号处理的中间结果,或者在必要的时序时引用中间结果。例如,存储器配置有动态随机存取存储器(DRAM)和静态随机存取存储器(SRAM)等。存储器和信号处理单元28输出信号处理之后的像素信号。

(CMOS图像传感器的第一示例结构)

图2A是示出了图1的CMOS图像传感器10的第一示例结构的断面图。图2B是从光照射侧看到的CMOS图像传感器10的第一示例结构的图。

如图2A和图2B所示,在半导体芯片11上形成有像素区域21等。此外,在半导体芯片11的与半导体芯片12对应的区域中形成有包括列处理单元25-1和系统控制单元27的外围电路单元51。此外,在半导体芯片11上还形成有引线接合用电极焊盘52。

在外围电路单元51中形成有凸块连接用电极焊盘53A。在半导体芯片11的光照射侧,SiN等的钝化层54A形成为在与凸块连接用电极焊盘53A和引线接合用电极焊盘52对应的部分区域中具有开口。凸块(微凸块)13经由钝化层54A的开口连接到凸块连接用电极焊盘53A。

另一方面,在半导体芯片12(的列处理单元25-2)上形成有凸块连接用电极焊盘53B。此外,在与半导体芯片12的光照射侧相反的一侧,SiN等的钝化层54B形成为在与凸块连接用电极焊盘53B对应的部分区域中具有开口。凸块13经由钝化层54B的开口连接到凸块连接用电极焊盘53B。因此,半导体芯片12经由半导体芯片12上的凸块13和半导体芯片11上的凸块13接合到半导体芯片11的光照射侧。也就是说,半导体芯片12倒装芯片接合到半导体芯片11的光照射侧。

为了保持机械强度,半导体芯片11和半导体芯片12之间的空间填充有底部填充树脂55。在半导体芯片11上的与半导体芯片12接合的区域周围形成有坝56,在用底部填充树脂55填充空间时,该坝防止底部填充树脂55泄漏到接合区域之外的区域中。因此,底部填充树脂55仅在坝56内侧扩散。

此外,在半导体芯片11的光照射侧,在像素区域21中形成有有机物质等的透镜材料57,其中,该像素区域为凸块13之外的区域。透镜材料57可以包括一种有机物质,或者可以包括堆叠的两种以上有机物质。SiO

透镜材料57充当像素区域21中的片上透镜,并且收集像素区域21上的照射光。透镜材料57没有在半导体芯片11上的像素区域21之外的区域58中形成。也就是说,透镜材料57在像素区域21之外的区域中具有开口。

需要指出的是,尽管没有示出,但是在透镜材料57和像素区域21之间实际上形成有滤色片等。

(CMOS图像传感器的制造方法的说明)

图3是描述图2的CMOS图像传感器的制造方法的概述图。

首先,如图3A所示,在其中形成有像素区域21、外围电路单元51和引线接合用电极焊盘52的半导体芯片11的光照射侧的整个表面上堆叠钝化层54A和透镜材料57。

接着,如图3B所示,对透镜材料57的像素区域21之外的区域58进行蚀刻并制成开口。然后,如图3C所示,为了将凸块13和凸块连接用电极焊盘53A进行连接,对钝化层54A的与凸块连接用电极焊盘53A对应的部分区域进行蚀刻并且形成凸块用开口部分71。此外,为了将引线接合件与引线接合用电极焊盘52进行连接,对与引线接合用电极焊盘52对应的部分区域进行蚀刻并且形成引线接合用开口部分72。然后,如图3D所示,在外围电路单元51中的凸块连接用电极焊盘53A上形成凸块13,并且在外围电路51上半导体芯片12的接合区域周围形成坝56。

然后,如图3E所示,将其中形成有与凸块13连接的凸块连接用电极焊盘53B的半导体芯片12接合到半导体芯片11的外围电路单元51上,以便使半导体芯片11的凸块13和半导体芯片12连接。然后,用底部填充树脂55填充半导体芯片11和半导体芯片12之间的空间。

图4是描述半导体芯片11的凸块13的形成方法的细节的外围电路单元51附近的放大图。

首先,如图4A所示,沉积种子金属73。然后,如图4B所示,进行光刻,并且在形成有凸块13的区域之外的区域中形成抗蚀剂74。

接着,如图4C所示,通过使用抗蚀剂74作为掩模来进行焊料的电镀生长,因而形成焊料75。然后,如图4D所示,除去抗蚀剂74。然后,如图4E所示,对焊料75之外的区域中的种子金属73进行蚀刻。最后,如图4F所示,进行回流并形成凸块13。

相比之下,在其中透镜材料57堆叠在半导体芯片11的光照射侧的整个表面上的情况下,在凸块连接用电极焊盘53A的光照射侧除了钝化层54A之外还存在透镜材料57,如图5所示。因而,需要在钝化层54A和透镜材料57中制作开口以形成开口部分81。如此,开口部分81的深度和开口宽度之间的深宽比很大。

因此,在形成凸块13时,焊料和种子金属73的嵌入性降低,并且很可能发生由于光刻时的曝光不足以及显影不足导致的抗蚀剂残留。因此,出现凸块13畸形等。

此外,由于透镜材料57包括有机物质,所以会从钝化层54A的开口部分81周围的透镜材料57产生气体,并且该气体在进行用于形成钝化层54A的开口部分81的蚀刻时通过与蚀刻气体发生反应而产生反应产物。此外,在其中透镜材料57是比钝化层54A更脆的材料的情况下,在进行用于形成钝化层54A的开口部分81的蚀刻时,对透镜材料57进行物理蚀刻以使其散开,并且散开的透镜材料57抑制用于形成钝化层54A的开口部分81的蚀刻的进行。因此,出现钝化层54A的开口部分81的异常,并且出现凸块13畸形以及连接电阻劣化等。

随着凸块13越来越小型化并且凸块13的间距越来越窄,开口部分81的深宽比进一步增大并且上述在形成凸块13时的问题也变得更加显著。然而,在其中列处理单元25-2形成在与半导体芯片11不同的半导体芯片12上并且进行倒装芯片接合的CMOS图像传感器10中,凸块13的数量的增多使得能够实现高速运行。因此,希望在有限尺寸的半导体芯片12中配置尽可能多的凸块13,并且凸块13的小型化以及缩窄凸块13的间距是必要的。另外,在其中透镜材料57较厚的情况下,开口部分81的深宽比也增大,并且上述在形成凸块13时的问题也会更加显著。

由于引线接合用电极焊盘52足够大,所以在用于形成在引线接合用电极焊盘52上形成的引线接合用开口部分72的蚀刻中,在引线接合用开口部分72周围的透镜材料57的影响较小。此外,丝球不是通过光刻形成,而是通过使用超声波和压力机械地形成合金并进行压接来形成;因此,不会发生像形成凸块13时一样的问题。

另一方面,在CMOS图像传感器10中,在其中形成有凸块13和引线接合用电极焊盘52的至少部分区域中制作开口;因此,如图4E所示,凸块用开口部分71的深宽比小于图5所示的开口部分81的深宽比。因此,可以提高形成凸块13时焊料和种子金属73的嵌入性。此外,在湿法处理(例如显影)时不会阻塞液体的流动。因此,可以防止由于在光刻时的曝光不足以及显影不足导致的抗蚀剂74残留等的发生。此外,在用于形成钝化层54A的凸块用开口部分71的蚀刻时,可以防止凸块用开口部分71周围的透镜材料57对蚀刻的抑制。

(像素区域和外围电路的第二示例结构)

图6是示出了图1的CMOS图像传感器10的第二示例结构的断面图。

图6的CMOS图像传感器10的结构与图2的结构基本相同,不同之处在于在图6中,透镜材料57形成在区域91以及引线接合用电极焊盘52的部分区域之外的区域中,区域91与半导体芯片12对应并且是半导体芯片11上的坝56内侧(包括坝56)的全部区域。

也就是说,在图6的示例中,透镜材料57形成为在半导体芯片11上的区域91以及引线接合用电极焊盘52的部分区域中具有开口,其中,区域91与半导体芯片12对应并且比半导体芯片12大。

例如,当在距离半导体芯片12的边缘大约200μm的位置形成坝56时,在距离半导体芯片12接合在半导体芯片11上的区域的边缘200μm左右的透镜材料57中制作开口。

(像素区域和外围电路的第三示例结构)

图7是示意性地示出了图1的CMOS图像传感器10的第三示例结构的断面图。

图7的CMOS图像传感器10的结构与图2的结构基本相同,不同之处在于在图7中,透镜材料57形成为仅在区域92以及引线接合用电极焊盘52的部分区域中具有开口,区域92是半导体芯片11上的坝56内侧(包括坝56)的一部分并且大于半导体芯片12的尺寸。

也就是说,在图7的示例中,透镜材料57形成为在半导体芯片11上的与半导体芯片12对应、大于半导体芯片12的尺寸并比坝56内侧(包括坝56)的区域小的区域以及引线接合用电极焊盘52的部分区域中具有开口。

如上所述,在图6和图7的示例中,透镜材料57也在像素区域21之外的区域中形成;因此,透镜材料57也可以保护像素区域21之外的区域。此外,当透镜材料57包括防止光的反射的滤色片时,可以防止像素区域21之外的区域的光的反射。

尽管透镜材料57没有在外围电路单元51上的部分区域中形成,但是由于该部分填充有底部填充树脂55,所以其也可以受到保护。此外,通过选择合适的树脂作为底部填充树脂55,可以防止坝56内侧(不包括坝56)的光的反射。

(像素区域和外围电路的第四示例结构)

图8是示意性地示出了图1的CMOS图像传感器10的第四示例结构的断面图。

图8的CMOS图像传感器10的结构与图2中的结构基本相同,不同之处在于在图8中,透镜材料57形成为仅在半导体芯片11上的坝56内侧的区域93以及引线接合用电极焊盘52的部分区域中具有开口,区域93的尺寸与半导体芯片12的尺寸相同。

也就是说,在图8的示例中,透镜材料57形成为在半导体芯片11上的与半导体芯片12对应且尺寸与半导体芯片12的尺寸相同的区域93以及引线接合用电极焊盘52的部分区域中具有开口。

考虑到半导体芯片12的未对准,透镜材料57可能在比区域93靠近内侧未对准量并小于半导体芯片12的尺寸的区域中具有开口。需要指出的是,当透镜材料57的开口区域太小时,在形成凸块13时会出现与在其中透镜材料57形成在半导体芯片11的整个表面上的情况下一样的问题。

因此,例如,如图9所示,透镜材料57的引线接合用电极焊盘52之外的开口区域94形成为使得从离透镜材料57最近的凸块13的离透镜材料57最近的一侧到透镜材料57的离该凸块13最近的一侧的距离101大于在光刻时的开口尺寸(即,凸块13的直径102)的两倍和凸块13的间距的最小值103中较大的一个。

可选择地,如图9和图10所示,开口区域94形成为使得从引线接合用开口部分72的离透镜材料57最近的一侧到透镜材料57的离引线接合用开口部分72最近的一侧的距离124与引线接合用开口部分72在其中透镜材料57和引线接合件120对准的方向上的尺寸123的比值(下文中称为引线接合比值)小于从离透镜材料57最近的凸块用开口部分71的离透镜材料57最近的一侧到透镜材料57的离该凸块用开口部分71最近的一侧的距离105与凸块用开口部分71在其中透镜材料57和凸块13对准的方向上的尺寸104的比值(下文中称为凸块比值)。

也就是说,开口区域94形成为使得凸块比值等于或大于在形成引线接合件120时不会引起问题的引线接合比值。

如上所述,在图8到图10的示例中,与图6和图7中的情况一样,透镜材料57也在像素区域21之外的区域中形成。因此,像素区域21之外的区域也可以受到保护,并且可以防止像素区域21之外的区域的光的反射。

透镜材料57的引线接合用电极焊盘52之外的开口区域(区域93或开口区域94)的尺寸等于或小于半导体芯片12的尺寸。因此,半导体芯片12和底部填充树脂55可以保护外围电路单元51上的透镜材料57的开口区域,并且防止开口区域的光的反射。

(区域92的形状的例子)

图11~13是从光照射侧看到的半导体芯片11的一部分的图,其示出了图7的区域92的形状的例子。

如图11所示,例如,区域92包括包围在半导体芯片11上形成的所有凸块13的一个区域。在这种情况下,减小了半导体芯片11的光照射侧的表面上由透镜材料57形成的高度差,并且在如显影等湿法处理时,液体的流动不太可能被阻塞。

需要指出的是,如图12所示,区域92可以包括两个以上的区域,这些区域把凸块13划分为两个以上的组并且分别包围每个组中的凸块13。此外,区域92的形状不限于矩形形状,并且例如,可以是如图13所示的圆形形状。

尽管使用图11到图13描述了区域92,但是这同样适用于区域93和开口区域94。

在第一实施方案中,说明了其中本公开的实施方案应用于CMOS图像传感器的情况;然而,本公开的实施方案也可以应用于CMOS图像传感器以外的固态成像装置,例如电荷耦合器件(CCD)图像传感器等。此外,本公开的实施方案可以应用于其中代替透镜材料57而将如聚酰亚胺等树脂用作保护膜并形成凸块的元器件。此外,将CMOS图像传感器10的部件分配到半导体芯片11和半导体芯片12的方法不限于上述方法。此外,通过凸块连接的单元不限于列处理单元25-1和25-2、水平驱动单元26和系统控制单元27。此外,半导体芯片12可以由多个半导体芯片形成。多个半导体芯片上形成的单元可以相同或不同。

<第二实施方案>

(CMOS图像传感器的第二实施方案的示例配置的概述)

图14是示出了本公开适用的CMOS图像传感器的第二实施方案的示例配置的概述图。

在图14的CMOS图像传感器140中,下部芯片141是图中下侧的半导体芯片,上部芯片142是图中上侧的半导体芯片,二者彼此进行倒装芯片接合。

下部芯片141包括半导体基板和Cu、Al等的金属布线层,并且在下部芯片141上形成有像素区域141A和外围电路141B。像素区域141A的配置与图1的像素区域21的配置类似。其配置与垂直驱动单元24、列处理单元25-1和25-2、水平驱动单元26和系统控制单元27的配置类似的外围电路141B形成在形成有像素区域141A的同一下部芯片141上,并且包括用于接合到上部芯片142上的未示出的凸块。

在下部芯片141上形成的未示出的透镜材料形成为在与上部芯片142的接合区域对应的区域中具有开口。因此,与第一实施方案中一样,可以防止在形成外围电路141B中包含的未示出的凸块时出现的问题。

上部芯片142包括半导体基板和Cu、Al等的金属布线层,并且在上部芯片142上形成有信号处理电路142A。信号处理电路142A的配置与图1的存储器和信号处理单元28的配置类似。

(划片前的CMOS图像传感器示例配置)

图15是示出了划片前的图14的CMOS图像传感器140的示例配置的立体图,图16是沿着图15的A-A方向的断面图。

如图15所示,划片前的CMOS图像传感器140包括下部芯片141在其中配置成阵列的半导体晶片150和横跨并接合在两个下部芯片141上的上部芯片142。需要指出的是,图15仅示出了其中形成有2(横向)×3(纵向)个下部芯片141的半导体晶片150的一部分。

下部芯片141(第一半导体芯片)和上部芯片142中的各者的外形都是具有预定厚度的矩形形状。在下部芯片141之间设有划线区域151。两个下部芯片141之间的划线区域151中形成有测试元件组(test element group:TEG)图案161和标记162,其中上部芯片142横跨并存在于该两个下部芯片上。

TEG图案161是用于评价将下部芯片141和上部芯片142彼此接合的未示出的凸块的图案。标记162是在使下部芯片141和上部芯片142接合时对准用的标记。使下部芯片141和上部芯片142彼此接合,以使得标记162与上部芯片142上形成的未示出的标记重合。

此外,用于评价将下部芯片141和上部芯片142接合的未示出的凸块的电极163在划线区域151中形成以与TEG图案161连接。在下部芯片141上的与上部芯片142接合的区域周围形成有坝164,其中该坝防止在将下部芯片141和上部芯片142彼此接合时填充下部芯片141和上部芯片142之间的空间的底部填充树脂泄漏。

上部芯片142由在图上侧(北侧)形成的北芯片171和图下侧(南侧)形成的南芯片172形成,其中,北芯片171和南芯片172之间夹有划线区域173。北芯片171(第二半导体芯片)和南芯片172(第三半导体芯片)中的各者的外形均为具有预定厚度的矩形形状。在将下部芯片141和上部芯片142彼此接合时对准用的未示出的标记形成在划线区域173中。

在上部芯片142上,信号处理电路142A被分为五个电路181到185,并且在这些电路中,两个电路181和182形成在北芯片171上,并且三个电路183~185形成在南芯片172上。

划片前的CMOS图像传感器140通过对下部芯片141周围的划线区域151进行划片(切割)来分离,如图16所示。

因此,在分离后的CMOS图像传感器140中,形成划线区域151添加到其上的下部芯片141的轮廓线的划线外的图15的左右方向(水平方向)上的侧面(第一侧面)191的整个区域与形成划线区域173添加到其上的北芯片171的轮廓线的划线外的图15的左右方向上的侧面(第二侧面)192的整个区域彼此平齐。

此外,形成划线区域151添加到其上的下部芯片141的轮廓线的划线外的面对侧面191的侧面(第三侧面)193的整个区域与形成划线区域173添加到其上的南芯片172的轮廓线的划线外的图15的左右方向上的侧面(第四侧面)194的整个区域彼此平齐。

需要指出的是,尽管在第二实施方案中,侧面191和侧面192的整个区域彼此平齐,并且侧面193和侧面194的整个区域彼此平齐,但是只要至少部分区域彼此平齐,那么不必整个区域都彼此平齐。

如上所述,在CMOS图像传感器140中,北芯片171和南芯片172形成在一个上部芯片142上。因此,北芯片171和南芯片172可以同时接合到下部芯片141上。此外,下部芯片141可以以相同的取向形成在半导体晶片150上,并且下部芯片141不需要对称轴。此外,北芯片171和南芯片172不需要对称轴。

此外,仅在制造时使用的TEG图案161、标记162和电极163配置在划线区域151中,并且在将CMOS图像传感器140分离时将其除去。因此,与TEG图案161、标记162和电极163配置在CMOS图像传感器140中的情况相比,可以增大下部芯片141的有效区域。

相比之下,如图17所示,在北芯片203和南芯片204在形成在半导体晶片201上的下部芯片202上分别形成的情况下,北芯片203和南芯片204逐个地接合到下部芯片202上。

因此,需要形成在将北芯片203和南芯片204接合时对准用的标记205和标记206。因而,如图17所示,当在半导体晶片201上的下部芯片202上形成标记205和标记206时,下部芯片202的尺寸会增大,而且制造成本也会增加。

此外,需要在下部芯片202上的北芯片203和南芯片204的接合区域附近形成防止底部填充树脂泄漏的坝207和208,该底部填充树脂填充下部芯片202与北芯片203和南芯片204中的各者之间的空间。

(CMOS图像传感器的制造方法的说明)

图18是描述CMOS图像传感器140的制造方法的立体图。

首先,如图18A所示,在半导体晶片150上形成下部芯片141。在下部芯片141之间的划线区域151中形成TEG图案161和标记162,并且在划线区域151的下部芯片141之间的区域之外的区域中形成电极163。在下部芯片141上的与上部芯片142接合的区域附近形成坝164。

在下部芯片141上的坝164内侧的外围电路141B中,通过诸如电镀、无电镀、转印或压接等方法形成诸如球或柱等凸块221以连接到形成于下部芯片141中的未示出的用于凸块的电极。例如,凸块221配置成具有几十微米的窄间距。为了确保凸块221的电特性和可靠性,该凸块包括通常使用诸如Ni、Pd、Au、Sn、Ag、Pb、Bi、Cu和In等金属材料的阻挡层、种子层、接合用金属层等。

接着,如图18B所示,其中形成有电路181和182的北芯片171与其中形成有电路183~185的南芯片172配置成划线区域173夹在其间,因而形成上部芯片142。在北芯片171和南芯片172上形成凸块222。在划线区域173中形成标记231和TEG图案232。

然后,如图18C所示,上部芯片142顺序配置在待接合的半导体晶片150上,使得标记162与标记231重合。因而,北芯片171上的凸块222接合到一个下部芯片141的南侧的凸块221上,并且南芯片172上的凸块222接合到与该下部芯片141不同的另一个下部芯片141的北侧的凸块221上。

以这种方式,下部芯片141和上部芯片142基于标记162和标记231彼此接合;因此,即使在其中凸块221和凸块222以高密度进行配置的情况下,凸块221和凸块222也可以精确的进行连接。

需要指出的是,在其中北芯片171配置在其南侧的下部芯片141的北侧,配置有与具有该北芯片171的上部芯片142不同的上部芯片142的南芯片172。此外,在其中南芯片172配置在其北侧的下部芯片141的南侧,配置有与具有该南芯片172的上部芯片142不同的上部芯片142的北芯片171。

接着,从南向和北向中的一个方向或两个方向往下部芯片141和上部芯片142之间注入底部填充树脂。在其中从南向和北向两个方向注入底部填充树脂的情况下,从南向和北向之间的左右相反方向通过线施加(line application)注入底部填充树脂。这样,下部芯片141和上部芯片142被固定。

最后,如图18D所示,对下部芯片141周围的划线区域151进行划片并且将CMOS图像传感器140分离。

如上所述,北芯片171和南芯片172共同接合到下部芯片141上,因此,与图17所示的其中北芯片203和南芯片204分别接合到下部芯片202上的情况相比,可以极大的减少接合次数。也就是说,北芯片171和南芯片172可以容易地接合到下部芯片141上。

因此,缩短了接合周转时间(turn-around time:TAT),并且可以降低制造成本。此外,缩短了凸块连接所需的热处理时间,因而减小了半导体晶片150上的热负荷,并且可以使热处理对CMOS图像传感器140的特性的影响最小化。

此外,由于北芯片171和南芯片172共同接合到下部芯片141上,所以北芯片171和南芯片172接合时对准用的标记和用于评价凸块的TEG图案可以共享。

此外,CMOS图像传感器140不存在例如镜面反转和对称轴等布局限制;因此,不需要改变CMOS图像传感器140的物理配置。

尽管在第二实施方案中,接合到一个上部芯片142上的下部芯片141的数量是两个,但是该数量也可以大于两个。例如,上部芯片142可以横跨并接合在2(横向)×2(纵向)个下部芯片141(即,4个下部芯片141)上,或者可以横跨并接合在3(横向)×2(纵向)个下部芯片141(即,6个下部芯片141)上。需要指出的是,接合到一个上部芯片142上的下部芯片141的数量与产量之间具有折衷关系。

尽管在第二实施方案中形成信号处理电路142A的电路数量是五个,但也可以是大于1的任意数量。

另外,尽管在第二实施方案中像第一实施方案中一样透镜材料没有形成在下部芯片141上的与上部芯片142的接合区域对应的区域中,但是透镜材料可以形成在该区域中。

尽管在第二实施方案中,像素区域141A和外围电路141B形成在同一下部芯片141上,但是它们也可以形成在不同的半导体芯片上。在这种情况下,半导体芯片间的接合也以与下部芯片141和上部芯片142类似的方式进行。

此外,CMOS图像传感器10和CMOS图像传感器140可以是背侧照射CMOS图像传感器或前侧照射CMOS图像传感器。需要指出的是,在其中CMOS图像传感器10和CMOS图像传感器140是前侧照射CMOS图像传感器的情况下,凸块连接用电极焊盘可以在金属布线层上方形成。因此,凸块连接用电极焊盘的形成步骤可以与普通的用于引线接合连接的电极焊盘的形成步骤类似。此外,与背侧照射CMOS图像传感器的情况不同,不需要进行将背侧的金属布线层的配线带到前侧的背侧重新布线步骤。因此,可以降低制造成本。

<第三实施方案>

(成像装置的实施方案的示例配置)

图19是示出了作为本公开适用的电子设备的成像装置的实施方案的示例配置的框图。

图19的成像装置1000是摄像机或数位相机等。成像装置1000包括透镜组1001、固态图像传感器1002、DSP电路1003、帧存储器1004、显示单元1005、记录单元1006、操作单元1007和电源单元1008。DSP电路1003、帧存储器1004、显示单元1005、记录单元1006、操作单元1007和电源单元1008经由总线1009相互连接。

透镜组1001接收来自被摄体的入射光(图像光),并在固态图像传感器1002的成像面上形成图像。固态图像传感器1002包括上述的CMOS图像传感器10(140)。固态图像传感器1002将其图像由透镜组1001形成在成像面上的入射光量转换成以像素为单位的电信号,并将电信号作为像素信号提供给DSP电路1003。

DSP电路1003对从固态图像传感器1002提供的像素信号进行预定的图像处理,并且将图像处理之后的像素信号以帧为单位提供给帧存储器1004,以便暂时储存像素信号。

例如,显示单元1005配置有诸如液晶面板或有机电致发光(EL)面板等面板式显示装置,并且基于暂时储存在帧存储器1004中的以帧为单位的像素信号来显示图像。

记录单元1006配置有数字通用光盘(DVD)、闪速存储器等,并且读出和记录暂时储存在帧存储器1004中的以帧为单位的像素信号。

操作单元1007在使用者的控制下发出关于成像装置1000的各种功能的操作命令。电源单元1008向DSP电路1003、帧存储器1004、显示单元1005、记录单元1006和操作单元1007适当地供电。

本技术实施方案适用的电子设备可以是在图像捕获单元(光电转换单元)中使用CMOS图像传感器的任何设备,除了成像装置1000之外,这些设备的例子还包括具有成像功能的便携式终端装置和在图像读出单元中使用CMOS图像传感器的复印机。

图20是示出了上述CMOS图像传感器10(140)的应用例的图。

例如,上述CMOS图像传感器10(140)可以用于如下所述的感测诸如可见光、红外光、紫外线和X射线等光的各种情况。

-用于欣赏的拍摄图像的装置,如数位相机和具有相机功能的便携式设备。

-用于交通工具的装置,例如拍摄汽车的前方和后方、周围以及汽车内部等的图像的车载传感器,监视行驶的车辆和道路的监控摄像机,以及测量车辆等之间的距离以用于安全驾驶(例如,自动停止)和识别驾驶员的状况等的距离传感器。

-用于家用电器(例如电视机、冰箱和空调)的装置,拍摄使用者的手势的图像并根据手势执行电器的操作。

-用于医疗和保健的装置,例如内窥镜和通过接收红外光进行血管造影的设备。

-用于安保的装置,例如用于预防犯罪的监控摄像机和用于个人认证的摄像机。

-用于美容的装置,例如拍摄皮肤图像的皮肤测量设备和拍摄头皮图像的显微镜。

-用于运动的装置,例如动作相机和用于运动等的可穿戴相机。

-用于农业的装置,例如用于监测田地和作物状况的相机。

需要指出的是,本说明书中描述的效果仅仅是示例性的,而不是限制性的;也可以表现出其它的效果。

此外,本公开的实施方案不限于上述实施方案,并且在本公开的范围内可以出现各种改变。

例如,本技术的实施方案也可以应用于CMOS图像传感器之外的其中多个半导体芯片彼此进行倒装芯片接合的半导体装置。

另外,本技术也可以具有如下构成。

(1)一种半导体装置,包括:

在第一半导体基板上的多个凸块;和

在第一半导体基板上的所述多个凸块之外的区域中的透镜材料,其中,离所述透镜材料最近的凸块的离所述透镜材料最近的一侧与所述透镜材料的离所述凸块最近的一侧之间的距离大于离所述透镜材料最近的凸块的直径的两倍,以及其中,离所述透镜材料最近的凸块的离所述透镜材料最近的一侧与所述透镜材料的离所述凸块最近的一侧之间的距离大于所述凸块的最小间距。

(2)根据(1)所述的半导体装置,

其中,所述透镜材料仅在第一半导体基板上的像素区域中形成。

(3)根据(1)所述的半导体装置,

其中,所述透镜材料仅在第一半导体基板上的与第二半导体基板对应的区域之外的区域中形成,第二半导体基板配置成经由所述凸块接合到第一半导体基板上。

(4)根据(3)所述的半导体装置,

其中,所述透镜材料形成为在第一半导体基板上的区域中具有开口,所述开口大于第二半导体基板。

(5)根据(4)所述的半导体装置,还包括:

在第二半导体基板和第一半导体基板之间形成的底部填充树脂;和

坝,所述坝形成在第一半导体基板上并且防止所述底部填充树脂泄漏到第一半导体基板上的与第二半导体基板接合的区域之外的区域,

其中,所述透镜材料形成为在第一半导体基板上的所述坝内侧的整个区域中具有开口。

(6)根据(3)所述的半导体装置,还包括:

在第二半导体基板和第一半导体基板之间形成的底部填充树脂;和

坝,所述坝形成在第一半导体基板上并且防止所述底部填充树脂泄漏到第一半导体基板上的与第二半导体基板接合的区域之外的区域;

其中,所述透镜材料形成为仅在第一半导体基板上的所述坝内侧的部分区域中具有开口。

(7)根据(3)所述的半导体装置,

其中,所述透镜材料形成为在第一半导体基板上的区域中具有开口,所述开口小于第二半导体基板。

(8)根据(1)所述的半导体装置,

其中,所述透镜材料的离所述凸块最近的一侧是片上透镜的一侧。

(9)根据(1)所述的半导体装置,还包括:

在第一半导体基板上形成并且配置成连接到所述凸块的凸块连接用电极焊盘;和

在第一半导体基板上形成并且配置成连接到引线接合件的引线接合用电极焊盘,

其中,引线接合用开口部分的离所述透镜材料最近的一侧与所述透镜材料的离所述引线接合用开口部分最近的一侧之间的距离和所述引线接合用开口部分的尺寸的比值小于离所述透镜材料最近的凸块用开口部分的离所述透镜材料最近的一侧与所述透镜材料的离所述凸块用开口部分最近的一侧之间的距离和所述凸块用开口部分的尺寸的比值。

(10)一种半导体装置的制造方法,所述方法包括:

在第一半导体基板上形成多个凸块,和

在第一半导体基板上的所述多个凸块之外的区域中形成透镜材料,其中,离所述透镜材料最近的凸块的离所述透镜材料最近的一侧与所述透镜材料的离所述凸块最近的一侧之间的距离大于离所述透镜材料最近的凸块的直径的两倍,以及其中,离所述透镜材料最近的凸块的离所述透镜材料最近的一侧与所述透镜材料的离所述凸块最近的一侧之间的距离大于所述凸块的最小间距。

(11)一种电子设备,包括:

在第一半导体基板上的多个凸块;和

在第一半导体基板上的所述多个凸块之外的区域中的透镜材料,其中,离所述透镜材料最近的凸块的离所述透镜材料最近的一侧与所述透镜材料的离所述凸块最近的一侧之间的距离大于离所述透镜材料最近的凸块的直径的两倍,以及其中,离所述透镜材料最近的凸块的离所述透镜材料最近的一侧与所述透镜材料的离所述凸块最近的一侧之间的距离大于所述凸块的最小间距。

(12)一种半导体装置,包括:

具有矩形形状的第一半导体基板;

具有矩形形状的第二半导体基板,其中,第二半导体基板的面积小于第一半导体基板的面积,并且第二半导体基板的第一边缘的至少部分区域与第一半导体基板的第一边缘的至少部分区域平齐;和

具有矩形形状的第三半导体基板,其中,第三半导体基板的面积小于第一半导体基板的面积,并且第三半导体基板的第一边缘的至少部分区域与第一半导体基板的第二边缘的至少部分区域平齐。

(13)根据(12)所述的半导体装置,

其中,第一半导体基板包括像素阵列,

其中,第二半导体基板和第三半导体基板各自包括至少一个逻辑电路,

其中,第一半导体基板的第一边缘和第二半导体基板的第一边缘中的每个对应于形成堆叠的半导体装置的第一边缘的划线,以及

其中,第一半导体基板的第二边缘和第三半导体基板的第一边缘中的每个对应于形成堆叠的半导体装置的第二边缘的划线。

(14)一种半导体装置的制造方法,所述方法包括:

将包括多个逻辑电路的第一半导体基板接合到在半导体晶片中配置成阵列的第二半导体基板和第三半导体基板上,其中第二半导体基板和第三半导体基板中的每个都包括像素阵列,以及其中,第一半导体基板跨越第二半导体基板和第三半导体基板;和

对第一半导体基板的第一边缘和第二半导体基板的第一边缘进行切割,以使得第一半导体基板的第一边缘和第二半导体基板的第一边缘彼此平齐。

(15)根据(14)所述的半导体装置的制造方法,还包括:

将包括多个逻辑电路的第四半导体基板接合到第二半导体基板和第五半导体基板上,其中,第四半导体基板跨越第二半导体基板和第五半导体基板;和,

对第二半导体基板的第二边缘和第四半导体基板的第一边缘进行切割,以使得第二半导体基板的第二边缘和第四半导体基板的第一边缘彼此平齐。

(16)一种电子设备,包括:

具有矩形形状的第一半导体基板;

具有矩形形状的第二半导体基板,其中,第二半导体基板的面积小于第一半导体基板的面积,并且第二半导体基板的第一边缘的至少部分区域与第一半导体基板的第一边缘的至少部分区域平齐;和

具有矩形形状的第三半导体基板,其中,第三半导体基板的面积小于第一半导体基板的面积,并且第三半导体基板的第一边缘的至少部分区域与第一半导体基板的第二边缘的至少部分区域平齐。

(17)一种半导体装置,包括:

包括与多个像素对应的多个片上透镜的第一半导体基板;和

经由一个或多个焊料凸块安装到第一半导体基板的光入射侧的第二半导体基板,其中,第一半导体基板的尺寸大于第二半导体基板的尺寸,以及其中,第二半导体基板配置成接收来自第一半导体基板的一个或多个像素信号,处理所述一个或多个像素信号,以及输出经过处理的一个或多个像素信号。

[附图标记列表]

10 CMOS图像传感器

11,12 半导体芯片

13 凸块

21 像素区域

52 引线接合用电极焊盘

53 凸块连接用电极焊盘

55 底部填充树脂

56 坝

57 透镜材料

71 凸块用开口部分

72 引线接合用开口部分

91~93 区域

94 开口区域

101 距离

102 直径

103 最小值

104 尺寸

105 距离

120 引线接合件

123 尺寸

124 距离

140 CMOS图像传感器

141 下部芯片

171 北芯片

172 南芯片

191~194 侧面

- 半导体光发射装置的制造方法、半导体光发射装置、半导体装置的制造方法、半导体装置、一种装置的制造方法、以及一种装置

- 半导体装置的制造方法、显示装置的制造方法、半导体装置、半导体元件的制造方法以及半导体元件