半导体结构

文献发布时间:2023-06-19 10:43:23

技术领域

本发明有关于一种半导体结构,特别是有关于一种具有条状掺杂区的半导体结构。

背景技术

在一般包含高压元件的电路系统中,若因功能性考量,欲额外增加高压二极管(HVdiode)元件时,会在该高压二极管元件下方设置一N井区,用来形成该高压二极管元件与基板之间的隔离结构。然而,此N井区的设置会造成该高压二极管元件的结击穿电压(junction breakdown voltage)的下降,导致该高压二极管元件无法满足元件运作时的需求。

目前,调降此N井区的浓度,是改善结击穿电压的方法之一。然而,虽此方法可适度提升高压二极管元件的结击穿电压,但却会造成同一电路系统中其他高压元件的击穿电压的下降,而影响该些元件的电性稳定。

因此,开发一种可提升高压二极管元件的结击穿电压并维持同一电路系统中其他高压元件的电性稳定的半导体结构是众所期待的。

发明内容

根据本发明的一实施例,提供一种半导体结构,包括:一基板;多个条状第一掺杂区,形成于该基板中;多个条状第二掺杂区,形成于该基板中,分别位于所述多个条状第一掺杂区之间,其中所述多个条状第一掺杂区的掺杂型式与所述多个条状第二掺杂区的掺杂型式相反;一第三掺杂区,形成于该基板中,包围所述多个条状第一掺杂区与所述多个条状第二掺杂区,其中该第三掺杂区的掺杂型式与所述多个条状第二掺杂区的掺杂型式相同;以及一第四掺杂区,形成于该基板中,位于所述多个条状第一掺杂区、所述多个条状第二掺杂区与该第三掺杂区下方,其中该第四掺杂区的掺杂型式与所述多个条状第二掺杂区的掺杂型式相同。

在部分实施例中,该基板为P型或N型基板。在部分实施例中,当该基板为P型基板时,所述多个条状第一掺杂区的掺杂型式为P型、所述多个条状第二掺杂区的掺杂型式为N型,该第三掺杂区的掺杂型式为N型,以及该第四掺杂区的掺杂型式为N型。在部分实施例中,当该基板为N型基板时,所述多个条状第一掺杂区的掺杂型式为N型、所述多个条状第二掺杂区的掺杂型式为P型,该第三掺杂区的掺杂型式为P型,以及该第四掺杂区的掺杂型式为P型。在部分实施例中,所述多个条状第一掺杂区与所述多个条状第二掺杂区的宽度相同。在部分实施例中,所述多个条状第一掺杂区与所述多个条状第二掺杂区于该基板中的深度相同。在部分实施例中,该第三掺杂区于该基板中的深度大于所述多个条状第一掺杂区与所述多个条状第二掺杂区于该基板中的深度。在部分实施例中,所述多个条状第一掺杂区、所述多个条状第二掺杂区与该第三掺杂区的掺杂浓度相同。在部分实施例中,该第四掺杂区的掺杂浓度低于所述多个条状第一掺杂区、所述多个条状第二掺杂区与该第三掺杂区的掺杂浓度。在部分实施例中,该第四掺杂区为一连续掺杂区域。在部分实施例中,所述多个条状第一掺杂区为高压P井区,以及所述多个条状第二掺杂区与该第三掺杂区为高压N井区。在部分实施例中,所述多个条状第一掺杂区、所述多个条状第二掺杂区与该第三掺杂区构成多个高压二极管。

根据本发明的一实施例,提供一种半导体结构,包括:一基板;一第一掺杂区,形成于该基板中;一第二掺杂区,形成于该基板中,包围该第一掺杂区,其中该第一掺杂区的掺杂型式与该第二掺杂区的掺杂型式相反;以及多个条状第三掺杂区,形成于该基板中,位于该第一掺杂区与该第二掺杂区下方,其中所述多个条状第三掺杂区的掺杂型式与该第二掺杂区的掺杂型式相同。

在部分实施例中,该基板为P型或N型基板。在部分实施例中,当该基板为P型基板时,该第一掺杂区的掺杂型式为P型,该第二掺杂区的掺杂型式为N型,以及所述多个条状第三掺杂区的掺杂型式为N型。在部分实施例中,当该基板为N型基板时,该第一掺杂区的掺杂型式为N型,该第二掺杂区的掺杂型式为P型,以及所述多个条状第三掺杂区的掺杂型式为P型。在部分实施例中,该第一掺杂区与该第二掺杂区于该基板中的深度相同。在部分实施例中,该第一掺杂区与该第二掺杂区的掺杂浓度相同。在部分实施例中,所述多个条状第三掺杂区的掺杂浓度低于该第一掺杂区与该第二掺杂区的掺杂浓度。在部分实施例中,所述多个条状第三掺杂区的宽度相同。在部分实施例中,所述多个条状第三掺杂区彼此分离。在部分实施例中,该第一掺杂区为高压P井区,以及该第二掺杂区为高压N井区。在部分实施例中,该第一掺杂区与第二掺杂区构成多个高压二极管(HV diode)。

本发明通过调整掺杂区间将传统整面延伸掺杂的高压P井区(HVPW)置换形成多个条状(strip)形式的掺杂区,并与多个高压N井区(HVNW)彼此间隔排列形成特殊的高压二极管(HV diode)结构。由于本发明多个条状掺杂区的设置,大幅增加了PN的结面积,促使高压二极管在运作时,得以有效分散所产生的电场,即便在深N井区(DNW)存在下,仍能大幅提升其击穿电压(BV)达80%以上。此外,本发明在不更动MOS制造工艺、注入条件、掩膜组合的情况下,可直接导入上述高压二极管结构,且不影响与上述高压二极管结构设置于同一电路系统中的其他高压元件的击穿电压(BV),确保该些高压元件的电性稳定,进而维持了整体电路的稳定与效能。

附图说明

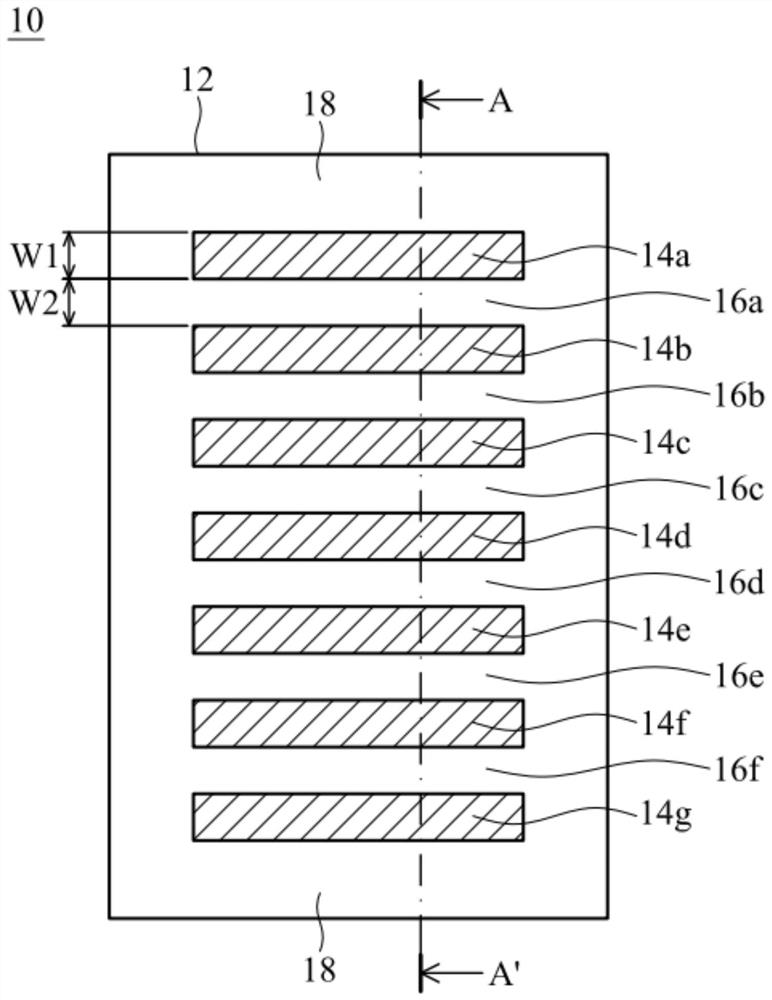

图1为根据本发明的一实施例,一种半导体结构的上视图;

图2为图1所示的半导体结构沿A-A’剖面线所得的剖面示意图;

图3为根据本发明的一实施例,一种半导体结构的上视图;

图4为图3所示的半导体结构沿B-B’剖面线所得的剖面示意图;

图5为根据本发明的一实施例,一种半导体结构的击穿电压(BV)值。

符号说明

10、100 半导体结构

12、120 基板

14a、14b、14c、14d、14e、14f、14g 条状第一掺杂区

16a、16b、16c、16d、16e、16f 条状第二掺杂区

18 第三掺杂区

20 第四掺杂区

140 第一掺杂区

160 第二掺杂区

180a、180b、180c、180d、180e、180f、180g 条状第三掺杂区

H1 条状第一掺杂区的深度(第一掺杂区的深度)

H2 条状第二掺杂区的深度(第二掺杂区的深度)

H3 第三掺杂区的深度

W1 条状第一掺杂区的宽度

W2 条状第二掺杂区的宽度

W

具体实施方式

请参阅图1以及图2,根据本发明的一实施例,提供一种半导体结构10。图1为半导体结构10的上视图。图2为图2沿A-A’剖面线所得的剖面示意图。

如图1以及图2所示,半导体结构10包括基板12、多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)、第三掺杂区18、以及第四掺杂区20。多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)形成于基板12中。多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)形成于基板12中,分别位于多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)之间。例如,多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)与多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)彼此间隔排列。在图1以及图2中,多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)与多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)间隔排列的两端均为条状第一掺杂区(14a、14g)。第三掺杂区18形成于基板12中,包围多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)与多个条状第二掺杂区(16a、16b、16c、16d、16e、16f),并与多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)以及多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)实质接触。第四掺杂区20形成于基板12中,位于多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)与第三掺杂区18下方,并与多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)、以及第三掺杂区18实质接触。在部分实施例中,多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)的掺杂型式与多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)的掺杂型式相反。第三掺杂区18的掺杂型式与多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)的掺杂型式相同。第四掺杂区20的掺杂型式与多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)的掺杂型式相同。

在图1以及图2中,基板12、多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)、第三掺杂区18、以及第四掺杂区20的掺杂型式如下,基板12为P型半导体基板,多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)的掺杂型式为P型,多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)的掺杂型式为N型,第三掺杂区18的掺杂型式为N型,以及第四掺杂区20的掺杂型式为N型。在部分实施例中,基板12、多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)、第三掺杂区18、以及第四掺杂区20可通过任何适当的P型掺质或N型掺质掺杂而成。

在图1以及图2中,条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)的宽度W1与条状第二掺杂区(16a、16b、16c、16d、16e、16f)的宽度W2相同。条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)于基板12中的深度H1与条状第二掺杂区(16a、16b、16c、16d、16e、16f)于基板12中的深度H2相同,而第三掺杂区18于基板12中的深度H3大于条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)于基板12中的深度H1以及条状第二掺杂区(16a、16b、16c、16d、16e、16f)于基板12中的深度H2。在部分实施例中,第三掺杂区18于基板12中的深度H3与条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)于基板12中的深度H1以及条状第二掺杂区(16a、16b、16c、16d、16e、16f)于基板12中的深度H2相同。

在图1以及图2中,多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)与第三掺杂区18的掺杂浓度相同,而第四掺杂区20的掺杂浓度低于多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)与第三掺杂区18的掺杂浓度。在部分实施例中,多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)、第三掺杂区18、以及第四掺杂区20可根据产品需求施予适当的掺杂浓度。

在图1以及图2中,第四掺杂区20为一连续掺杂区域,也就是位于多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)与第三掺杂区18下方的第四掺杂区20呈现一连续掺杂态样。多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)为高压P井区(HVPW),而多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)与第三掺杂区18为高压N井区(HVNW)。多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)与第三掺杂区18构成多个高压二极管(HV diode),而第四掺杂区20作为上述高压二极管与基板12之间的隔离结构。

仍请参阅图1以及图2,根据本发明的另一实施例,提供一种半导体结构10。图1为半导体结构10的上视图。图2为图1沿A-A’剖面线所得的剖面示意图。

如图1以及图2所示,半导体结构10包括基板12、多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)、第三掺杂区18、以及第四掺杂区20。多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)形成于基板12中。多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)形成于基板12中,分别位于多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)之间。例如,多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)与多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)彼此间隔排列。在图1以及图2中,多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)与多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)间隔排列的两端均为条状第一掺杂区(14a、14g)。第三掺杂区18形成于基板12中,包围多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)与多个条状第二掺杂区(16a、16b、16c、16d、16e、16f),并与多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)以及多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)实质接触。第四掺杂区20形成于基板12中,位于多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)与第三掺杂区18下方,并与多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)、以及第三掺杂区18实质接触。在部分实施例中,多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)的掺杂型式与多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)的掺杂型式相反。第三掺杂区18的掺杂型式与多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)的掺杂型式相同。第四掺杂区20的掺杂型式与多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)的掺杂型式相同。

在图1以及图2中,基板12、多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)、第三掺杂区18、以及第四掺杂区20的掺杂型式如下,基板12为N型半导体基板,多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)的掺杂型式为N型,多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)的掺杂型式为P型,第三掺杂区18的掺杂型式为P型,以及第四掺杂区20的掺杂型式为P型。在部分实施例中,基板12、多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)、第三掺杂区18、以及第四掺杂区20可通过任何适当的P型掺质或N型掺质掺杂而成。

在图1以及图2中,条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)的宽度W1与条状第二掺杂区(16a、16b、16c、16d、16e、16f)的宽度W2相同。条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)于基板12中的深度H1与条状第二掺杂区(16a、16b、16c、16d、16e、16f)于基板12中的深度H2相同,而第三掺杂区18于基板12中的深度H3大于条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)于基板12中的深度H1以及条状第二掺杂区(16a、16b、16c、16d、16e、16f)于基板12中的深度H2。在部分实施例中,第三掺杂区18于基板12中的深度H3与条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)于基板12中的深度H1以及条状第二掺杂区(16a、16b、16c、16d、16e、16f)于基板12中的深度H2相同。

在图1以及图2中,多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)与第三掺杂区18的掺杂浓度相同,而第四掺杂区20的掺杂浓度低于多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)与第三掺杂区18的掺杂浓度。在部分实施例中,多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)、第三掺杂区18、以及第四掺杂区20可根据产品需求施予适当的掺杂浓度。

在图1以及图2中,第四掺杂区20为一连续掺杂区域,也就是位于多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)与第三掺杂区18下方的第四掺杂区20呈现一连续掺杂态样。多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)为高压N井区(HVNW),而多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)与第三掺杂区18为高压P井区(HVPW)。多个条状第一掺杂区(14a、14b、14c、14d、14e、14f、14g)、多个条状第二掺杂区(16a、16b、16c、16d、16e、16f)与第三掺杂区18构成多个高压二极管(HV diode),而第四掺杂区20作为上述高压二极管与基板12之间的隔离结构。

请参阅图3以及图4,根据本发明的一实施例,提供一种半导体结构100。图3为半导体结构100的上视图。图4为图3沿B-B’剖面线所得的剖面示意图。

如图3以及图4所示,半导体结构100包括基板120、第一掺杂区140、第二掺杂区160、以及多个条状第三掺杂区(180a、180b、180c、180d、180e、180f、180g)。第一掺杂区140形成于基板120中。第二掺杂区160形成于基板120中,包围第一掺杂区140,并与第一掺杂区140实质接触。多个条状第三掺杂区(180a、180b、180c、180d、180e、180f、180g)形成于基板120中,位于第一掺杂区140与第二掺杂区160下方,并与第一掺杂区140与第二掺杂区160实质接触。在部分实施例中,第一掺杂区140的掺杂型式与第二掺杂区160的掺杂型式相反。多个条状第三掺杂区(180a、180b、180c、180d、180e、180f、180g)的掺杂型式与第二掺杂区160的掺杂型式相同。

在图3以及图4中,基板120、第一掺杂区140、第二掺杂区160、以及多个条状第三掺杂区(180a、180b、180c、180d、180e、180f、180g)的掺杂型式如下,基板120为P型半导体基板,第一掺杂区140的掺杂型式为P型,第二掺杂区160的掺杂型式为N型,以及多个条状第三掺杂区(180a、180b、180c、180d、180e、180f、180g)的掺杂型式为N型。在部分实施例中,基板120、第一掺杂区140、第二掺杂区160、以及多个条状第三掺杂区(180a、180b、180c、180d、180e、180f、180g)可通过任何适当的P型掺质或N型掺质掺杂而成。

在图3以及图4中,第一掺杂区140于基板120中的深度H1与第二掺杂区160于基板120中的深度H2相同。在部分实施例中,第一掺杂区140于基板120中的深度H1与第二掺杂区160于基板120中的深度H2不同,例如,第二掺杂区160于基板120中的深度H2大于第一掺杂区140于基板120中的深度H1。

在图3以及图4中,第一掺杂区140与第二掺杂区160的掺杂浓度相同,而多个条状第三掺杂区(180a、180b、180c、180d、180e、180f、180g)的掺杂浓度低于第一掺杂区140与第二掺杂区160的掺杂浓度。在部分实施例中,第一掺杂区140、第二掺杂区160、以及多个条状第三掺杂区(180a、180b、180c、180d、180e、180f、180g)可根据产品需求施予适当的掺杂浓度。

在图3以及图4中,多个条状第三掺杂区(180a、180b、180c、180d、180e、180f、180g)的宽度W

仍请参阅图3以及图4,根据本发明的另一实施例,提供一种半导体结构100。图3为半导体结构100的上视图。图4为图3沿B-B’剖面线所得的剖面示意图。

如图3以及图4所示,半导体结构100包括基板120、第一掺杂区140、第二掺杂区160、以及多个条状第三掺杂区(180a、180b、180c、180d、180e、180f、180g)。第一掺杂区140形成于基板120中。第二掺杂区160形成于基板120中,包围第一掺杂区140,并与第一掺杂区140实质接触。多个条状第三掺杂区(180a、180b、180c、180d、180e、180f、180g)形成于基板120中,位于第一掺杂区140与第二掺杂区160下方,并与第一掺杂区140与第二掺杂区160实质接触。在部分实施例中,第一掺杂区140的掺杂型式与第二掺杂区160的掺杂型式相反。多个条状第三掺杂区(180a、180b、180c、180d、180e、180f、180g)的掺杂型式与第二掺杂区160的掺杂型式相同。

在图3以及图4中,基板120、第一掺杂区140、第二掺杂区160、以及多个条状第三掺杂区(180a、180b、180c、180d、180e、180f、180g)的掺杂型式如下,基板120为N型半导体基板,第一掺杂区140的掺杂型式为N型,第二掺杂区160的掺杂型式为P型,以及多个条状第三掺杂区(180a、180b、180c、180d、180e、180f、180g)的掺杂型式为P型。在部分实施例中,基板120、第一掺杂区140、第二掺杂区160、以及多个条状第三掺杂区(180a、180b、180c、180d、180e、180f、180g)可通过任何适当的P型掺质或N型掺质掺杂而成。

在图3以及图4中,第一掺杂区140于基板120中的深度H1与第二掺杂区160于基板120中的深度H2相同。在部分实施例中,第一掺杂区140于基板120中的深度H1与第二掺杂区160于基板120中的深度H2不同,例如,第二掺杂区160于基板120中的深度H2大于第一掺杂区140于基板120中的深度H1。

在图3以及图4中,第一掺杂区140与第二掺杂区160的掺杂浓度相同,而多个条状第三掺杂区(180a、180b、180c、180d、180e、180f、180g)的掺杂浓度低于第一掺杂区140与第二掺杂区160的掺杂浓度。在部分实施例中,第一掺杂区140、第二掺杂区160、以及多个条状第三掺杂区(180a、180b、180c、180d、180e、180f、180g)可根据产品需求施予适当的掺杂浓度。

在图3以及图4中,多个条状第三掺杂区(180a、180b、180c、180d、180e、180f、180g)的宽度W

实施例1

高压二极管的击穿电压(BV)的测试

请参阅图5,在本实施例中,同时进行传统高压二极管与本发明高压二极管(HVdiode)两者击穿电压(breakdown voltage,BV)的测试。此处的传统高压二极管结构包括高压P井区(HVPW)、高压N井区(HVNW)、以及深N井区(DNW),其中高压P井区(HVPW)为整面延伸的连续掺杂区,高压N井区(HVNW)包围高压P井区(HVPW),以及深N井区(DNW)位于高压P井区(HVPW)与高压N井区(HVNW)下方。本发明高压二极管结构包括多个条状高压P井区(HVPW)、多个条状高压N井区(HVNW)、高压N井区(HVNW)、以及深N井区(DNW),其中多个条状高压P井区(HVPW)与多个条状高压N井区(HVNW)彼此间隔排列,高压N井区(HVNW)包围多个条状高压P井区(HVPW)与多个条状高压N井区(HVNW),以及深N井区(DNW)位于多个条状高压P井区(HVPW)、多个条状高压N井区(HVNW)与高压N井区(HVNW)下方,如图1以及图2所示。上述元件经测试后所测得的击穿电压(BV)变化如曲线A(传统高压二极管)及曲线B(本发明高压二极管)所示。

由图5可看出,传统高压二极管的击穿电压(BV)(曲线A)未能达到40伏(V),此与一般高压元件运作时所需求的击穿电压(BV)数值相差甚远。而本发明高压二极管由于将高压P井区(HVPW)与高压N井区(HVNW)分别设计成多个条状形式的掺杂区,彼此间隔排列,因而大幅增加了PN的结面积,使得该高压二极管在运作时,得以有效分散所产生的电场,进而提升其击穿电压(BV)(曲线B)的数值至高达60伏(V)以上,而本发明具有如此足够大的击穿电压(BV)的高压二极管已可广泛应用于包含各式高压元件的电路系统。

本发明通过调整掺杂区间将传统整面延伸掺杂的高压P井区(HVPW)置换形成多个条状(strip)形式的掺杂区,并与多个高压N井区(HVNW)彼此间隔排列形成特殊的高压二极管(HV diode)结构。由于本发明多个条状掺杂区的设置,大幅增加了PN的结面积,促使高压二极管在运作时,得以有效分散所产生的电场,即便在深N井区(DNW)存在下,仍能大幅提升其击穿电压(BV)达80%以上。此外,本发明在不更动MOS制造工艺、注入条件、掩膜组合的情况下,可直接导入上述高压二极管结构,且不影响与上述高压二极管结构设置于同一电路系统中的其他高压元件的击穿电压(BV),确保该些高压元件的电性稳定,进而维持了整体电路的稳定与效能。

上述实施例的特征有利于本技术领域中技术人员理解本发明。本技术领域中技术人员应理解可采用本发明作基础,设计并变化其他制造工艺与结构以完成上述实施例的相同目的及/或相同优点。本技术领域中技术人员亦应理解,这些等效置换并未脱离本发明精神与范畴,并可在未脱离本发明的精神与范畴的前提下进行改变、替换、或更动。

- 氮化物半导体结构、氮化物半导体发光元件、氮化物半导体晶体管元件、氮化物半导体结构的制造方法以及氮化物半导体元件的制造方法

- 衬底结构、包含衬底结构的半导体封装结构,以及制造半导体封装结构的半导体工艺