一种沟槽终端结构及其制备方法

文献发布时间:2023-06-19 10:54:12

技术领域

本发明属于半导体器件领域,特别涉及了一种沟槽终端结构。

背景技术

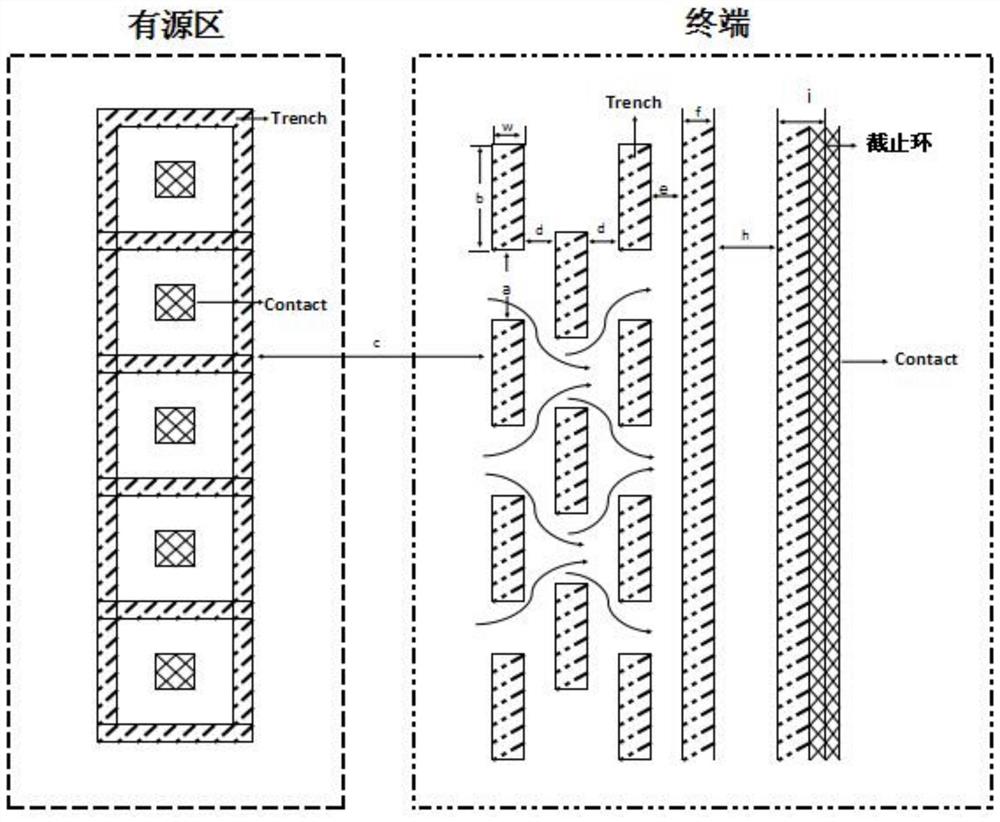

图1给出了一种现有的普通沟槽终端结构,终端由几条沟槽按一定间距排列,通常沟槽的宽度w相同,间距d也相同,并且最外面一圈为截止环,截止环与其他沟槽的间距h比d大。沟槽呈环状分布于有源区外围,主要由靠近有源区的第一根沟槽侧壁的栅氧来承担压降,由于终端位置的沟槽宽度比有源区宽,在沟槽刻蚀时,其沟槽深度更深,沟槽侧壁的栅氧化层更薄,导致终端位置的击穿电压低于有源区,限制了器件性能。

发明内容

为了解决上述背景技术提到的技术问题,本发明提出了一种沟槽终端结构及其制备方法,使终端位置的电势分布更均匀,并减小终端宽度,提升器件性能。

为了实现上述技术目的,本发明的技术方案为:

一种沟槽终端结构,沟槽呈环状分布于有源区的外围,在沟槽的外围设有截止环,所述沟槽包括若干条间断沟槽和一条连续沟槽,所述连续沟槽位于间断沟槽与截止环之间,每条间断沟槽包括若干条等间距设置的间断子沟槽,且相邻间断沟槽的间断子沟槽交错分布。

进一步地,连续沟槽与间断沟槽的间距为e,连续沟槽与截止环的间距为h,相邻间断沟槽的间距为d,则h的取值大于e和d的取值。

进一步地,间断沟槽的宽度为w,连续沟槽的宽度为f,截止环的宽度为i,则i的取值大于w和f的取值。

如上述沟槽终端结构的制备方法,包括如下步骤:

(1)衬底采用N型<100>晶向,并掺杂砷元素或磷元素,在衬底做外延生长,所生长的外延电阻率和厚度根据器件的耐压要求确定;

(2)在衬底表面沉积一层SiO

(3)在沟槽侧壁通过干法氧化形成一层氧化层,然后湿法漂洗去除所有氧化层,修复沟槽刻蚀损伤,使沟槽底部圆滑;

(4)在沟槽侧壁生长一层氧化层作为栅介质层;

(5)通过多晶沉积、光刻、刻蚀,形成多晶栅;

(6)在芯片表面注入硼元素,高温退火形成P阱;通过光刻、注入、退火形成N+区,注入元素为砷元素;

(7)在N+区上淀积一层氧化层作为介质层,并在介质层上通过孔光刻、刻蚀,形成接触孔;

(8)通过注入、退火,降低接触孔的接触电阻,注入的元素为B或BF

(9)在P阱和介质层上淀积金属铝,通过刻蚀金属铝形成各功能区;

(10)沉积钝化层并光刻腐蚀,形成栅极和源极的开口区;

(11)减薄衬底背面,并在衬底背面蒸镀Ti-Ni-Ag合金。

进一步地,在步骤(2)中,SiO

在步骤(3)中,干法氧化形成的氧化层的厚度为500-2000埃,氧化温度为1000-1100℃;在步骤(4)中,在沟槽侧壁生长的氧化层的厚度为500-1000埃,生长温度为950℃-1050℃;在步骤(5)中,多晶的厚度为0.8-1.2um,多晶的掺杂浓度为1E19-6E19,掺杂元素为磷。

进一步地,在步骤(6)中,硼元素的注入能量为60KeV ~120KeV,注入剂量根据电压阈值确定,形成P阱的退火条件为1100℃/60min,采用双注入提高P阱掺杂浓度的均匀性;形成N+区的注入元素为砷,注入能量为60KeV,退火条件为950℃/60min。

进一步地,在步骤(7)中,介质层的厚度为8000-12000埃,在介质层中掺杂硼元素和磷元素,接触孔的深度为0.3-0.45um。

进一步地,在步骤(8)中,注入的能量为30-40KeV,注入的剂量为2E14-5E14,退火条件为950℃/30s。

进一步地,在步骤(9)中,金属铝的厚度为4um,在金属铝中掺杂SiCu。

进一步地,在步骤(10)中,钝化层为氮化硅,钝化层的厚度为7000-12000埃。

采用上述技术方案带来的有益效果:

与普通沟槽终端相比,本发明采用分段沟槽结构,可显著降低第一根沟槽侧氧的电场强度,降低电势密度,将电势场引流到第二根和第三根等,从而使终端位置的电势分布更均匀,更容易向终端外围耗尽;终端沟槽和有源区沟槽的间距更短,沟槽环数更少,终端宽度可降低30%以上。而且本发明无需调整工艺流程,工艺实现简单且工艺窗口足够。

附图说明

图1为一种现有的普通沟槽终端结构示意图;

图2为本发明设计的沟槽终端结构示意图。

具体实施方式

以下将结合附图,对本发明的技术方案进行详细说明。

本发明设计了一种沟槽终端结构,如图2所示,沟槽呈环状分布于有源区的外围,在沟槽的外围设有截止环,所述沟槽包括若干条间断沟槽和一条连续沟槽,所述连续沟槽位于间断沟槽与截止环之间,每条间断沟槽包括若干条等间距设置的间断子沟槽,且相邻间断沟槽的间断子沟槽交错分布。

在本实施例中,连续沟槽与间断沟槽的间距为e,连续沟槽与截止环的间距为h,相邻间断沟槽的间距为d,则h的取值大于e和d的取值。间断沟槽的宽度为w,连续沟槽的宽度为f,截止环的宽度为i,则i的取值大于w和f的取值。

对比图1与图2,可以明显看出图2中沟槽的环数少于图1中的沟槽环数,且图2中终端沟槽与有源区沟槽的间距小于图1中终端沟槽与有源区沟槽的间距,所以图2中整个终端的宽度小于图1中整个终端的宽度。

本发明还提出了针对上述沟槽终端结构的制备方法,步骤如下:

1、衬底材料准备:外延片的衬底采用N型(100)晶向, 砷元素或磷元素掺杂,电阻率通常在0.001-0.05Ω.cm. 在衬底做外延生长,所生长的外延电阻率和厚度,由不同的器件耐压决定。通常外延厚度:3-15um,外延电阻率:0.1-3Ω.cm,器件耐压可以达到20V-200V。

2、沟槽(Trench)刻蚀:圆片表面淀积一层SiO

3、牺牲氧化生长:在沟槽侧壁通过干法氧化形成一层厚度500-2000埃的氧化层,氧化温度1000-1100℃,湿法漂洗去除所有氧化层,修复Trench刻蚀损伤,并使Trench底部圆滑。

4、栅介质层形成:在沟槽侧壁生长一层厚度500-1000埃的氧化层,生长温度950℃-1050℃,氧化层厚度越厚,需要更高的温度生长。

5、多晶栅形成:多晶淀积、光刻、刻蚀,多晶厚度0.8-1.2um,多晶掺杂浓度1E19-6E19,掺杂元素:磷。

6、P阱和N+区形成:在芯片表面注入B元素,能量60KeV ~120KeV,剂量根据VTH参数的需求调整,通常在5E12-1.8E13左右,高温退火形成P阱,退火条件:1100℃/60min,也可以采用双注入提高P阱掺杂浓度的均匀性;N+区光刻、注入、退火,注入元素:As元素,能量60KeV,退火条件:950℃/60min。

7、介质层淀积、孔刻蚀:淀积一层厚度8000-12000埃的氧化层,可在氧化层中掺入一定比例的B元素和P元素,吸收可动Na、K离子,提高器件可靠性。孔光刻、刻蚀,孔深度一般为0.3-0.45um。

8、孔注入、填充:孔注入、退火,降低接触电阻,注入元素为BF2/B,剂量:2E14-5E14,能量:30-40KeV,快速退火:950℃/30s;Ti/TiN层淀积和钨金属填充,形成欧姆接触孔。

9、金属淀积、刻蚀:沉积厚度为4um金属铝,铝中可掺杂一定比例的SiCu,防止铝硅互溶,然后光刻腐蚀铝。

10、钝化层沉积,钝化层光刻,腐蚀:沉积钝化层氮化硅 7000-12000埃,然后光刻腐蚀,形成Gate和Source的开口区,可降低芯片表面可动离子引起的器件漏电。

11、背面蒸镀Ti-Ni-Ag:减薄圆片背面到150um左右,在背面蒸镀Ti-Ni-Ag(钛-镍-银)。

实施例仅为说明本发明的技术思想,不能以此限定本发明的保护范围,凡是按照本发明提出的技术思想,在技术方案基础上所做的任何改动,均落入本发明保护范围之内。

- 一种沟槽MOSFET终端结构和沟槽MOSFET器件及其制备方法

- 具有可变角度沟槽结终端扩展终端结构及其制备方法