用于校正裸片放置误差的自适应布线

文献发布时间:2023-06-19 11:00:24

技术领域

本发明大体上涉及制造电子模块且特定来说,涉及用于电子模块的衬底上的电子装置的自适应布线互连的方法及系统。

背景技术

电子模块及系统通常包括使用电互连件电连接到衬底的一或多个电子装置。所属领域中已知图案化电互连件的各种技术。

例如,美国专利7,508,515描述用于制造电路的系统及方法,其中通过不均匀地修改电路的表示而产生数字控制图像,使得使用数字控制图像在衬底上记录的电路图案精确地符合已经形成的电路部分。

美国专利8,799,845描述用于制造基于面板的封装结构的自适应图案化方法及系统。个别装置单元在面板或网状晶片中的未对准可通过测量各个别装置单元的位置且在各个别装置单元上方形成单元特定图案而调整。

美国专利9,040,316描述用于使用动态通孔截割的框组封装(panelizedpackaging)的自适应图案化的半导体装置及方法。形成包括安置于多个半导体裸片周围的囊封材料之面板。测量面板内的多个半导体裸片中的每一者的实际位置。形成包括与多个半导体裸片中的每一者的实际位置对准的第一捕获垫的导电重布层(RDL)。形成至少部分安置于第一捕获垫上方且与多个半导体封装中的每一者的封装轮廓对准的多个第二捕获垫。调整多个导电通孔的标称占据面积以考虑每一半导体裸片与其对应封装轮廓之间的未对准。

发明内容

本文中描述的本发明的实施例提供一种方法,其包含接收电子模块的至少部分的布局设计,所述设计至少指定(i)耦合到至少一衬底的电子装置及(ii)连接到所述电子装置且具有经设计布线的电迹线。接收数字输入,所述数字输入表示根据所述布局设计制造但无所述电迹线的至少一部分的实际电子模块的至少部分。基于所述数字输入估计在将所述电子装置耦合到所述衬底时相对于所述布局设计的误差。针对所述电迹线的至少所述部分计算校正所述经估计误差的实际布线。在所述实际电子模块的所述衬底上沿着所述实际布线而非所述经设计布线形成所述电迹线的至少所述部分。

在一些实施例中,计算所述实际布线包含针对所述实际电子模块定义:(i)第一框架,其包围所述电子装置且保持所述电子装置周围的第一裕度;及(ii)第二框架,其包围所述第一框架且保持所述电子装置周围的大于所述第一裕度的第二裕度。在所述第一框架与所述第二框架之间计算所述实际布线。在其它实施例中,定义所述第二框架包含基于在将所述电子装置耦合到所述衬底时的所述经估计误差设置所述第二裕度。在又其它实施例中,接收所述数字输入包含接收选自由以下项组成的列表的至少一个输入:(a)至少布置于所述第一框架及所述第二框架内的所述实际电子模块的图像及(b)至少布置于所述第一框架与所述第二框架之间的所述电迹线的至少所述部分的宽度的测量。

在实施例中,所述方法包含基于所述数字输入,当所述电子装置的至少部分或所述第一框架超出所述第二框架时,使所述实际电子模块不合格。在另一实施例中,估计所述误差包含估计选自由以下项组成的列表的一或多个误差类型:(a)所述电子装置从所述布局设计中指定的第一位置到在所述数字输入中接收的第二位置的移位、(b)所述电子装置在所述数字输入中相对于所述布局设计的旋转及(c)所述电子装置与所述衬底之间的缩放误差。在又一实施例中,所述经设计布线包含布置于所述经设计布线的第一边缘上的第一位置处的至少一点,且计算所述实际布线包含基于所述数字输入估计所述点从所述第一位置到第二不同位置的位移及基于所述第二位置计算所述实际布线上的第一经计算边缘,使得所述第二位置布置于所述第一经计算边缘上。

在一些实施例中,计算所述实际布线包含检查所述实际布线是否违反所述布局设计的一或多个设计规则及调整所述实际布线以遵守所述设计规则。在其它实施例中,形成所述电迹线包含使用直接成像系统沿着所述实际布线产生所述电迹线。

在实施例中,所述衬底包含印刷电路板(PCB)且所述电子装置包含安装于所述PCB上的集成电路(IC)。在另一实施例中,使用嵌入式裸片封装过程将所述电子装置耦合到所述衬底。

根据本发明的实施例,另外提供一种系统,其包含处理器及直接成像子系统。所述处理器经配置以:(a)接收电子模块的至少部分的布局设计,所述设计至少指定(i)耦合到至少一衬底的电子装置及(ii)连接到所述电子装置且具有经设计布线的电迹线;(b)接收数字输入,所述数字输入表示根据所述布局设计制造但无所述电迹线的至少一部分的实际电子模块的至少部分;(c)基于所述数字输入,估计在将所述电子装置耦合到所述衬底时相对于所述布局设计的误差;及(d)针对所述电迹线的至少所述部分,计算校正所述经估计误差的实际布线。所述直接成像子系统经配置以基于所述实际布线,在所述实际电子模块的所述衬底上沿着所述实际布线而非所述经设计布线形成所述电迹线的至少所述部分。

从与图式一起进行的本发明的实施例的以下详细描述将更完全理解本发明,其中:

附图说明

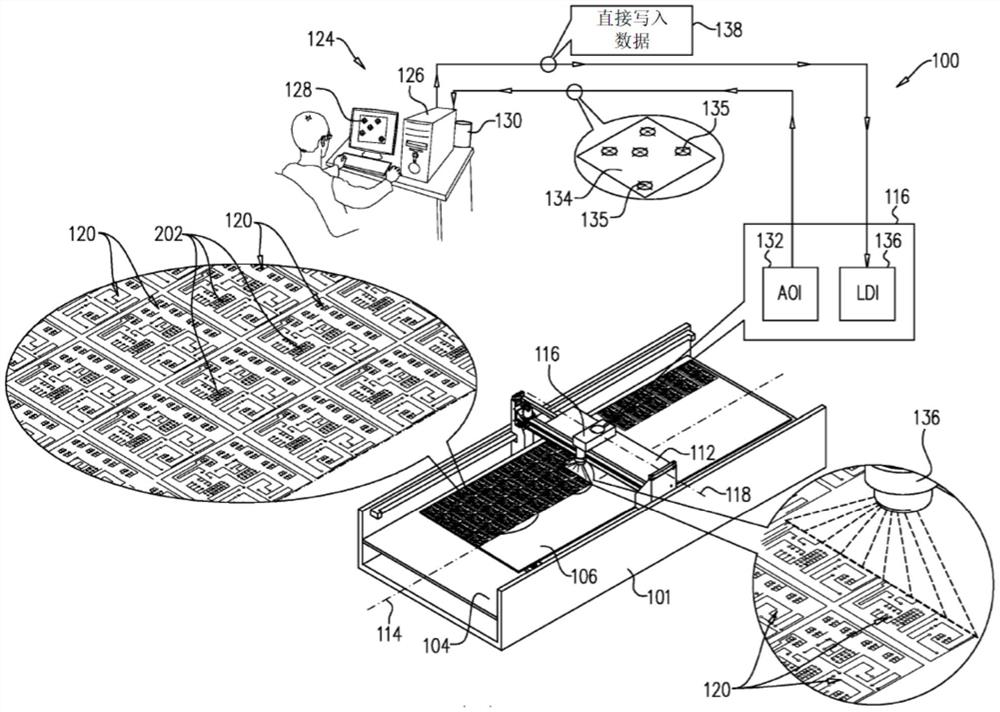

图1是根据本发明的实施例的用于在衬底上印刷导体的直接成像(DI)系统的示意性说明图;

图2A是根据本发明的实施例的电子模块的布局设计的示意性说明图;

图2B是根据本发明的实施例的用于校正在将电子装置耦合到衬底时的误差的布局的示意性说明图;

图3是示意性地说明根据本发明的实施例的用于校正在将电子装置耦合到衬底时的经估计误差的方法的流程图;

图4是根据本发明的实施例的电子模块的区段的布局设计的示意性说明图;

图5是根据本发明的实施例的用于计算校正在将电子装置耦合到衬底时的经估计误差的电迹线的实际布线的过程序列的示意性说明图;

图6是根据本发明的实施例的用于产生给定电子模块的布局设计与给定电子模块的实际产生组件的图像之间的变换矩阵的过程序列的示意性说明图;及

图7是根据本发明的实施例的用于校正两个电子装置之间经由衬底电耦合的误差的布局的示意性说明图。

具体实施方式

概述

产生电子模块通常包括(例如)通过从经切割晶片挑选电子装置作为裸片且将裸片放置于衬底上而将至少一个电子装置耦合到衬底。电子装置通常使用电迹线连接到衬底上的其它组件。

在一些情况中,在放置裸片时发生误差,其可引起电子装置与衬底上的电迹线之间的未对准,从而导致电子模块的不良功能性或不合格。

下文描述的本发明的实施例提供用于通过自适应地布线衬底上的电迹线而估计并校正电子装置的放置误差的系统及方法。

在一些实施例中,系统包括处理器,所述处理器经配置以接收电子模块的至少部分的布局设计。经接收布局设计包括至少耦合到衬底的电子装置及连接到电子装置且具有经设计布线的电迹线。

在一些实施例中,处理器进一步接收根据布局设计制造但无一或多个电迹线的至少一区段的实际电子模块的至少部分的数字输入(例如图像及测量)。在一些实施例中,处理器经配置以基于数字输入估计电子装置在衬底上的位置相对于布局设计的误差。处理器进一步经配置以针对一或多个电迹线的至少所述区段计算校正经估计误差的实际布线。

在一些实施例中,基于布局设计及经指定误差,处理器经配置以计算包围电子装置的内部框架及外部框架。内部框架(例如)以预定义裕度同轴地包围电子装置,且外部框架包围内部框架且具有等于或大于经指定误差的裕度。内部框架与外部框架之间的裕度在本文中还被称为“校正区”。

在一些实施例中,处理器经配置以沿着区段的经设计布线的给定边缘选择一或多个点。针对每一所选择的点,处理器经配置以沿着区段的面对给定边缘的相对边缘寻找定位于距所选择的点的最小距离处(在本文中被称为经设计宽度)的点。

在一些实施例中,基于数字输入,处理器经配置以通过变换经设计布线的至少所选择的点以遵守数字输入而在校正区内计算区段的经计算布线。处理器进一步通过寻找定位于区段的相对边缘处的与相应所选择的点相距最小距离的对应点而针对所选择的点中的每一者计算宽度。

在一些实施例中,处理器经配置以(例如)通过在所选择的点中的一或多者处在对应经设计及经计算宽度之间进行比较而检查经计算布线是否遵守区段的设计规则,且当需要时,通过调整经计算布线以遵守设计规则而计算实际布线。

在一些实施例中,系统进一步包括直接成像子系统,所述直接成像子系统经配置以基于实际布线而在实际电子模块的衬底上沿着实际布线而非经设计布线产生电迹线的至少所述区段。

所揭示技术通过调整装置与衬底之间的布线以便补偿电子模块的取放过程中的变化而改进集成于(例如)PCB或嵌入式裸片封装中的电子模块的质量。此外,所揭示技术通过改进生产良率且通过实现在衬底的给定面积(real estate)上产生的电子模块的较高密度而改进此类电子模块的生产效率。

系统描述

图1是根据本发明的实施例的用于在衬底106上印刷图案的直接成像(DI)系统100的示意性说明图。

在一些实施例中,系统100包括安装于光学支撑台(未展示)上的机壳101。机架101包括经配置以固持衬底106以便由系统100在其上印刷图案的衬底支撑表面104。在一些实施例中,衬底106可包括适用于待在其上执行的计算机化直接写入的任何衬底且图案化通常通过将上覆相应表面的光致抗蚀剂暴露到激光而定义衬底106的一或多个表面上的对象。在其它实施例中,图案化可通过将上覆相应表面的任何其它适合光敏材料暴露到激光而定义衬底106的一或多个表面上的对象。在一些实施例中,系统100经配置以将直接写入过程应用到衬底以便在其上印刷多个对象的设计。

在本发明的上下文中,术语对象是指可通过在衬底106上进行计算机化直接写入而图案化的任何单元(例如电子模块)的特征,每一单元通常与定位于衬底106上的其它相邻单元隔开。在一些实施例中,系统100经配置以处理各种类型的模块,例如(但不限于)经配置以与安装于印刷电路板(PCB)上的一或多个装置电连接的电子电路及经封装为任何适合衬底中的嵌入式裸片的一或多个装置(例如集成电路(IC)装置)。嵌入式裸片封装可包括(例如)各种类型的装置(例如处理器、控制器、存储器装置)、各种类型的一或多个传感器及各种类型的一或多个光源的扇入及/或扇出封装。

在一些实施例中,衬底106可包括:面板,其包括编织玻璃纤维、聚酰亚胺、环氧树脂化合物或任何其它类型的刚性或柔性聚合物中的至少一者;或晶片,其由半导体材料(例如,聚硅氧、聚硅氧-锗或化合物半导体)、玻璃、塑料模具或任何其它适合材料制成。此外,衬底106可为在生产期间接合到刚性支撑层(例如玻璃)且随后在完成生产过程之后从其移除的柔性衬底。

在一些实施例中,系统100包括经布置用于沿着平行于相对于机壳101定义的第一轴线114的轴线相对于衬底支撑表面104线性运动的桥112。在其它实施例(未展示)中,桥可位静态的且支撑表面连同放置于其上的衬底经配置以移动,或桥及支撑表面两者相对于彼此移动。

在一些实施例中,系统100包括沿着桥112安装的至少一个读取/写入组合件。在图1的实例中,单个读取/写入组合件116经布置用于沿着与第一轴线114正交的第二轴线118相对于桥112可选择定位。此配置使多个循序平行扫描能够在衬底106上方实行,每一扫描产生多个对象120。

在其它实施例中,系统100可包括可在桥112上沿着第二轴线118以并排配置布置的多个读取/写入组合件116。此配置使多个扫描能够由相应组合件116在衬底106上方同时或部分同时实行,每一扫描产生多个对象120。

在一些实施例中,对象120通常但未必彼此类似且可在平行于第一轴线114的方向上前后布置及平行于第二轴线118并排布置,如图1中说明。替代地,对象120可以任何其它适合图案(例如以非线性重复或非重复图案)布置。在一些实施例中,电子模块200包括装置202,例如集成电路(IC)或存储器装置或任何其它适合电子装置。

在一些实施例中,系统100包括操作控制台(在本文中还被称为控制组合件124),所述操作控制台包括计算机126(其包括各种装置,例如一或多个处理器及一或多个存储器装置(未展示))及用户接口128。计算机126进一步包括经配置以控制读取/写入组合件116、桥112及系统100的其它组件的操作的软件模块。

在本发明的上下文中,且在权利要求书中,为了简洁,术语“计算机126的处理器”在下文简称为“处理器”。

在一些实施例中,控制组合件124进一步包括写入指令数据库130,所述写入指令数据库130包括根据本发明的实施例用于在衬底106的至少一个表面上写入对象120的计算机辅助设计(CAD)指令。

在一些实施例中,至少一个读取/写入组合件116包括经配置以捕获由计算机126的处理器接收的衬底106的光学图像134的自动光学成像(AOI)子系统132。此类光学图像134可包括对象120的一或多个适合特征(例如,具有独有形状)的光学图像及/或衬底106上的通常用于系统100的配准及/或校准的任何适合基准点135。在一些实施例中,AOI子系统132进一步经配置以测量电子模块的特征的各种尺寸以及(例如)相邻特征之间的距离。

在一些实施例中,读取/写入组合件116进一步包括直接成像子系统(例如激光直接成像(LDI)子系统136),所述直接成像子系统包括经配置以响应于从计算机126的处理器接收的直接写入数据138而启用激光写入到衬底106上以产生对象120的光学扫描组合件。应注意,尽管AOI子系统132及LDI子系统136两者在本文中被称为成像子系统的类型,但由每一子系统执行的成像具有相互不同的性质。AOI子系统132至少为了在执行衬底106上的直接写入之前进行系统100的测量、检验、配准及校准的目的执行衬底106的光学成像以便获取其光学图像。相比之下,LDI子系统136通过将图案激光成像到衬底106上而执行衬底106上的直接写入。在本发明的上下文中,且在权利要求书中,为了简洁,术语“LDI子系统”在下文简称为“LDI”或“DI”。

在一些实施例中,LDI 136可包括在美国专利8,531,751中描述的类型的激光扫描仪,所述专利被让与与本发明相同的受让人。适合与本发明一起使用的直接成像系统的其它实例包括可购自日本东京的屏幕半导体(SCREEN Semiconductor)的型号编号为DW-3000的直接成像系统及可购自德国海德堡(Heidelberg)的德国海德堡仪器(HEIDELBERGInstruments)的模型编号为MLA150的无掩模对准器系统。

在实施例中,AOI子系统132经配置以用作用于改进LDI子系统136的直接成像过程的配准测试子系统。

在一些实施例中,计算机126的处理器经配置以从数据库130接收包括用于衬底106上的直接写入的电路设计数据的计算机辅助设计(CAD)文件,所述CAD文件包括待在衬底106上产生的多个对象120的CAD数据。

在一些实施例中,计算机126的处理器经配置以控制读取/写入组合件116以基于CAD数据引导一或多个激光束用于在多个平行扫描中在衬底106上直接写入数据。多个平行扫描可如图1中说明那样由单个可复位位读取/写入组合件顺序执行,或可使用多个读取/写入组合件同时或部分同时执行。

在一些实施例中,控制组合件124(其还被称为自动直接写入机器配置(ADWMC)单元)经配置以接收含有用于在衬底106的至少一个表面上直接写入的电路设计数据的CAD文件。控制组合件124进一步经配置以自动地配置包括至少一个读取/写入组合件116的直接写入机器以在多个扫描中基于CAD数据在衬底106上直接写入直接写入数据。

在实施例中,计算机126的处理器自动地配置直接写入数据以使多个对象120在多个扫描中的每一者中以并排方式被写入以便在扫描宽度内,使得无对象在多个扫描中被写入,借此避免对于在邻近扫描之间拼接直接写入数据的需要。

在一些实施例中,读取/写入组合件116由控制组合件124控制以通常在多个扫描遍次中在衬底106上产生多个对象120,其中邻近扫描遍次的接缝不定位于对象内,借此避免对于在邻近扫描之间拼接直接写入数据的需要。应注意,接缝经布置以在对象120之间且不上覆于对象120内。

在一些实施例中,归因于由LDI 136提供的最大扫描长度的固有限制,通常需要多个扫描遍次以便扫描衬底106的完整宽度。此多个扫描遍次可使用单个可复位位扫描头循序实行或通过同时操作的多个扫描头至少部分同时执行。扫描长度的此限制受必须在执行衬底表面上的直接写入的聚焦激光束的所需大小与LDI 136的扫描透镜的扫描长度之间维持的临界比率以及其它因素制约。

在一些实施例中,衬底106不限于是其上仅图案化单层对象120的单层衬底。确切来说,可以加成方式采用系统100以便选择性地逐层修改衬底层以便产生三维结构。因此,对象120可由多个层形成,所述多个层可由读取/写入组合件116循序地在彼此上方配准地写入。

通常来说,计算机126包括在软件中编程以实行本文中描述的功能的通用计算机。软件可例如经由网络以电子形式被下载到计算机,或其可替代地或另外被提供及/或存储于非暂时性有形媒体(例如磁性、光学或电子存储器)上。

图2A是根据本发明的实施例的电子模块200的布局设计的示意性说明图。电子模块200可替换(例如)上文的图1的对象120的电子模块。在一些实施例中,电子模块200包括在上文的图1中描绘的装置202。

在实施例中,装置202耦合到衬底255,所述衬底255可替换(例如)上文的图1的衬底106。在此实施例中,装置202及衬底255可使用任何适合配置彼此耦合。例如,装置202可安装于包括PCB的衬底255上。在另一实例中,装置202可使用任何适合嵌入式裸片封装技术(例如扇入(例如,在半导体衬底中)或扇出(例如,在塑料模具衬底中))嵌入衬底255中。在一些实施例中,衬底255包括连接到装置202的电迹线222,每一电迹线222具有(例如)装置202的垫204与衬底255的连接器206(在本文中还被称为连接垫)之间的经设计布线。

在一些实施例中,计算机126的处理器经配置以计算电子模块200中,包围装置202且具有距装置202的边缘的预定义裕度(在本文中被称为区233)的框架210。应注意,框架210遵循装置202的大小、位置及定向。例如,假使装置202按给定旋转角度相对于经设计布局旋转,那么框架210也按相同角度旋转。

处理器进一步经配置以计算在电子模块200中,包围框210的其之间具有另一裕度(在本文中被称为区211或校正区)的框架220。在下文的图2B中详细描绘用于计算框架220的大小及区211的宽度的方法。应注意,框架210及220是由处理器布置于电子模块200的设计上的虚拟框架。在一实施例中,框架210与220之间的校正区用于校正装置202在衬底255上的放置误差,如下文的图2B中将详细描述。

在一些实施例中,电子模块200的每一迹线222包括三个区段。内部区段(在本文中还被称为区段218)经布置于垫204与框架210之间。外部区段(在本文中还被称为区段216)经布置于框架22与连接器206之间,且中间区段(在本文中还被称为区段244)经布置于框架210与框架220之间且连接于区段216与218之间。

估计裸片到衬底的耦合误差及计算校正经估计误差的布线

图2B是根据本发明的实施例的电子模块260的示意性说明图。模块260可替换(例如)上文的图2A的模块200。在模块260的制造过程中,从衬底(例如,硅晶片)切割装置202作为裸片,且使用卷带或任何其它适合技术将装置202与相邻裸片分开。

随后,取放系统(未展示)从卷带拾取装置202,且将装置202耦合到衬底255上的预定义位置。取放系统可具有可导致装置202到衬底255的耦合过程中的误差的过程变化。例如,取放系统可按相对于(例如)上文的图2A中展示的经设计布局的预定义位置的偏移将装置202放置于衬底255上。此偏移误差在本文中还被称为“平移”或“移位”。

耦合过程可具有其它误差,例如由装置202相对于(例如)上文的图2A中展示的经设计布局中指定的定向的非所要旋转引起的旋转误差。此外,制造过程中的热循环可引起装置202及衬底255的大小及/或面积相对于上文的图2A中展示的布局设计之间的不同比率。例如,衬底255可包括具有大于通常由聚硅氧制成的装置202的热膨胀系数(CTE)的CTE的聚合物。此CTE差可导致(例如)上文描述的不同比率,在本文中还被称为装置202与衬底255之间的缩放误差。

如上文的图1中描绘,衬底可包括多个对象120,因此多个(例如,多于一千个)电子模块260(各自包括至少装置202)。在电子模块260的示范性制造过程中,多于一千个装置202耦合到衬底255且适合测量系统(例如配准测试系统或AOI子系统132)跨衬底255捕获多个电子模块260的图像(例如,对五个电子模块取样)。

在一些实施例中,处理器经配置以从数据库130仅提取类似于全部电子模块206的全部框架210的面积及位置(而非衬底的整个面积)且将此信息保存于计算机126的存储器中。在这些实施例中,处理器减少计算机126的存储器及通信资源上的负载,此还实现LDI子系统136的操作的经改进速度及可靠性。

在一些实施例中,处理器经配置以从配准测试系统及/或从AOI子系统132接收数字输入,例如从每一经取样电子模块260获取的一组图像及/或一组测量(例如,电子模块260的经设计特征与实际产生的特征之间的大小、定向及配准)。应注意,数字输入包括根据(例如)上文的图2A中展示的布局设计制造但无电迹线222的至少一部分(例如,区段244)的经产生电子模块260(在本文中还被称为实际电子模块260)的至少部分。

在一些实施例中,处理器经配置以基于数字输入的图像及测量估计在装置到衬底255的耦合中相对于布局设计(例如,上文的图2A中展示)的误差。应注意,经估计误差通常包括上文描述的移位、旋转及缩放误差的组合。

在替代实施例中,经估计误差可包括仅前述误差中的一者,或额外误差,或基于从配准测试系统或从任何其它成像及/或测量系统接收的数字输入估计的任何两个或两个以上误差的组合。

在一些实施例中,处理器经配置以基于装置202在衬底255上的最大放置误差设置区211的宽度(即,框架210与220之间的裕度)。最大误差通常是上文描述的移位及旋转及缩放误差的组合。在实施例中,处理器将因子(例如,5)应用到最大误差用于设置区211的宽度。例如,针对具有1mm大小(例如,长度及宽度)的装置202,经指定移位误差是30μm,经指定旋转误差是10毫弧度(mrad)(归因于旋转而导致高达10μm位移)且经指定缩放误差是1%(归因于装置202及衬底255中的至少一者的缩放误差而导致额外10μm误差)。在此实例中,经组合最大误差加总高达50μm,因此,将区211的所选择的宽度设置为250μm。

在其它实施例中,处理器可应用用于设置区211的宽度的任何其它适合计算。例如,应用到最大误差的因子可大于1但小于5。1.5的示范性因子通过将区211的宽度从250μm减小到75μm而减小框架220的占据面积。此因子允许在衬底255上并入更大数目个电子模块260,但假使总误差超过50μm的经指定值(例如,当总误差加总高达80μm时),那么可降低生产良率。在此实例中,相应电子模块260的装置202的至少一部分可超过框架220的面积且因此,计算机126的处理器将使此相应电子模块260不合格。

在替代实施例中,处理器可仅使用一个误差(例如,移位误差),或前述误差的所选择的两者的组合(例如,移位误差及旋转误差),或(例如)由AOI子系统132提供的另一测量的另一误差,或其组合,或区211的宽度的计算中的任何其它适合方法。

另外或替代地,假使给定电子模块中的经估计误差超过经指定值,那么处理器可发出使相应给定电子模块不合格的警报。在实施例中,AOI子系统132进一步经配置以检测(例如)特定电子模块260中的缺陷,使得即使在特定电子模块中,上文描述的经估计误差在规范内,处理器仍可归因于缺陷而使特定电子模块不合格。

在一些实施例中,处理器经配置以针对电迹线222的至少区段244计算校正上文描述的经估计误差的实际布线。如图2B中展示,迹线222的区段218及216如在上文的图2A中展示的经设计布局中般(例如)相对于装置202的垫204保持,使得区段244的实际布线通过连接于区段218及216的分别定位于框架210及220上的端之间而补偿误差。

应注意,尽管区段218经保持于相对于相应垫204的相同位置及定向处,但实际上,垫204归因于上文描述的误差而移位。在实施例中,处理器经配置以使用用于计算区段244的实际布线的相同方法计算每一区段218的实际布线。

换句话说,区段218的实际布线不同于区段218的经设计布线以便保持每一区段218相对于相应垫204的经设计位置及定向(其在装置202的位移内经移位)。区段244的实际布线不同于区段244的经设计布线以便补偿区段218的实际布线与经设计布线之间的相对位移。

随后,基于经计算实际布线,LDI子系统136如上文描述那样印刷迹线222的全部区段(例如,区段216、244及218)。

图2B的方法及布局为了清楚起见被简化且通过实例展示以便说明由本发明的实施例解决的某些问题且证实这些实施例在增强任何DI系统(例如DI系统100)的性能中的应用。

然而,本发明的实施例绝不限于此特定种类的示范性DI系统及/或方法及/或布局,且本文中描述的原理可类似地应用到任何其它种类的系统、方法及布局。

在替代实施例中,处理器可应用用于校正装置202到衬底255的耦合中的经估计误差的任何其它适合方法。例如,使用喷墨系统而非DI系统100,或任何其它适合类型的加成制造技术(例如金属打印机),或任何CAM站重布线解决方案,或用于校正装置202与衬底255之间的耦合中的经估计误差的任何其它适合方法。

图3是示意性地说明根据本发明的实施例的用于校正将装置202耦合到衬底255时的经估计误差的方法的流程图。方法以在设计接收步骤300处,处理器(例如)从数据库130接收布置于衬底255上的面板的设计开始。处理器进一步经配置以基于来自系统100的用户的输入及/或基于数据库130的一或多个文件定义所关注区域及每一所关注区域的相应大小。例如,用户输入可包括每一电子模块(例如,电子模块200)的位置,装置202的大小以及如上文描述的移位、旋转及缩放的经指定误差。

在面板学习步骤302(在本文中还被称为“脱机步骤”或“预处理步骤”)处,处理器在设计布局中(例如)沿着迹线222确定所关注点,且对紧密接近每一所关注点的点进行分类。在一些实施例中,处理器经配置以基于脱机步骤计算迹线222的经设计宽度,如在下文的图5中将详细描述。

实际上,面板学习步骤302可在后续阶段(例如,在(例如)从配准测试系统接收数字输入之后)实行,但步骤202的预处理改进系统100的速度及效率。

在数字输入接收步骤304处,处理器从配准测试系统(或从任何其它适合系统,例如AOI子系统132)接收根据上文的图2A中展示的布局设计制造但无电迹线222的至少区段244的实际电子模块(例如,电子模块260)的至少部分的数字输入(例如,在跨衬底255的多个位置处获取的图像及/或测量)。如上文的图2B中描述,处理器经配置以基于数字输入估计在将装置202耦合到衬底255的过程中引起的相对于(例如,电子模块200的)布局设计的(例如,移位、旋转及缩放的)经组合误差。应注意,步骤300及302被视为脱机步骤,且通过处理器在接收数字输入之后实行的全部其它操作被视为联机步骤。在下文的图4到6中更详细描绘脱机及联机步骤。

在变换步骤306处,处理器变换区段244及任选地,电子模块206的其它元件的经预处理数据(在步骤302处前文提及)以便形成遵守在步骤304处接收的数字输入的经计算布线。换句话说,处理器变换电迹线222的所关注特征的经设计图案以便遵守装置202相对于衬底255的经设计布局的实际位置。在下文的图5中详细描绘经计算变换。

在验证步骤308处,处理器将电子模块的一组设计规则(例如,迹线222的最小宽度、电子模块的邻近特征之间的最小距离、所关注特征的经允许形状及其它设计规则)应用到在上文的步骤306处获得的经计算布线。在一些实施例中,处理器可使用用于检查设计规则的软件,及/或可与任何适合市售设计规则检查站(未展示)介接。

在一些实施例中,在应用设计规则之后,处理器可识别违反(即,可不遵守)设计规则的一或多个电子模块。换句话说,在相应电子模块中,区段244的经计算布线将不能够校正在步骤304处估计的误差,或校正可未能遵守设计规则。在这些实施例中,处理器经配置以使这些电子模块不合格(在本文中还被称为“报废”)以便聚焦LDI子系统136在遵守设计规则的电子模块上的利用时间。

在其它实施例中,处理器经配置以针对可在过程的后续阶段实行的校正过程步骤标记这些电子模块。标记可为电子的(例如,使用具有相应一或多个电子模块的坐标的文件)及/或使用任何适合技术的物理标记。如上文提及,处理器可计算区段244及/或电迹线222的另一部分的新布线且可将一或多个指令文件发送到LDI子系统136用于校正迹线222中的经计算误差。

在调整步骤310处,处理器基于设计规则调整经计算布线,且针对至少区段244(及任选地针对电子模块的其它元件)计算校正经估计误差且还遵守电子模块的设计规则的实际布线。在一些实施例中,在获得实际布线之后,处理器将用于将实际布线应用到迹线222的区段244的一或多个指令文件发送到LDI子系统136(或到任何其它适合类型的图案化系统),借此终止方法的联机步骤。

在实例实施例中,基于给定点处的设计规则,电迹线222沿着区段216、218及244的经设计宽度是10μm。在变换步骤306之后,至少一个区段244的经计算宽度是8μm,从而导致2μm的误差,使得处理器必须增加区段244的宽度。在此实施例中,处理器在给定点处在远离区段244的中心的方向上将区段244的两个边缘中的每一者移位达误差的一半(例如,1μm),借此将区段244的宽度从8μm增加到10μm。

在另一实例实施例中,迹线222在给定位置处的经计算宽度是14μm,而迹线在所述给定位置处的经设计宽度是10μm,使得处理器必须将迹线的宽度减小达4μm。在此实施例中,处理器在给定位置处将迹线222的两个边缘中的每一者朝向中心移位达2μm。

在其它实施例中,处理器可应用两个边缘之间的不对称调整以便遵守其它设计规则,例如两个邻近线之间的最小距离。在区段244具有8μm的经计算宽度(而在设计规则中的经指定宽度是10μm)的实例中,处理器可(例如)远离区段244的中心将一个边缘移位达0.5μm且将另一边缘移位达1.5μm以便补偿经计算宽度与设计规则之间的2μm差。在又一实施例中,处理器可仅将一个边缘移位达2μm,而将不移动其它边缘。

在其它实施例中,处理器经配置以将任何其它适合调整应用到线及/或带线之间的空间及/或到沟槽及/或到对象120的其它特征及图案。

在图案化步骤312处,LDI子系统136执行一或多个脚本文件案以便基于实际布线在衬底255上形成至少区段244。应注意,LDI子系统136沿着实际布线而非经设计布线印刷区段244以便补偿装置202的放置误差且遵守设计规则。图案化步骤312结束图3的方法。

图4是根据本发明的实施例的电子模块200的中间区段的布局设计的示意性说明图。图4的布局设计详细说明上文描述的用于相对于电子模块200的布局设计估计装置202在衬底255上的放置误差的方法。

在一些实施例中,“p”表示布置于迹线222的边缘上的点。点p定位于区段244中,在距框架220的d

α的值具有在0与1之间的范围。如果点p经布置于点402处,那么d

在一些实施例中,处理器经配置以(在应用设计规则之前)通过将所关注点(例如点p)的位置变换为经计算位置(在本文中被称为“pcalc”)而计算区段244的经计算布线。使用方程式(2)实行pcalc的计算:

(2)p

其中T(p)是变换函数,例如,变换矩阵。应注意,方程式(2)基于点p与框架210及220的接近性而应用变换矩阵。因此,如果α等于1,那么pcalc等于p,此意味着无点p的变换。假使α等于0,那么pcalc等于T(p),此意味着点p处的完全变换。在下文的图5中示意性地展示所关注点(例如点p)的变换。如图2B中展示,区段244可具有(例如)安置于区段218及216的分别定位于框架210及220上的端之间的线性形状。因此,pcalc的位置取决于α,其表示点p距框架210及220的距离。

图5是根据本发明的实施例的用于计算区段244的实际布线的过程序列的示意性说明图。

现参考图5的脱机区段。在一些实施例中,处理器从数据库130接收可替换(例如)上文的图2A的经布置于衬底255上的经设计区段244的中间区段的经设计布线502。如面板学习步骤302处描述,处理器在设计布局中识别所关注点,例如在经预处理布线504(其是经设计布线502的经预处理版本)上展示的点pdesign、p1及p2。

在一些实施例中,处理器进一步识别(例如)定位于经预处理布线504的左边缘506上的点pdesign与定位于经预处理布线504的右边缘508上的最接近点(在本文中被称为qdesign)之间最小距离,以便计算经预处理布线504的经设计宽度(在本文中还被称为经预处理布线504中展示的“Wdesign”)。

应注意,脱机步骤系对电子模块的设计实行,但适用于具有相同设计且耦合到相应衬底(例如,衬底255)的全部电子模块。

现参考图5的联机区段。联机区段包括由处理器在脱机步骤计算的经预处理布线504的复本。如上文的图3的步骤304中描述,处理器从配准测试系统接收根据电子模块200的布局设计制造但无电迹线的至少中间区段的每一实际电子模块(例如,电子模块260)的数字输入。

应注意,归因于将装置耦合到相应衬底时的不同经估计误差,针对每一电子模块实行以下联机步骤。

在一些实施例中,处理器经配置以基于数字输入估计在将装置202放置于衬底255上的过程中引起的相对于布局设计的移位、旋转及缩放的经组合误差。基于经估计误差,处理器针对每一点p计算α及T(p),且基于经计算α及T(p),处理器变换布线504的经预处理数据以便形成遵守经接收数字输入的经计算布线510。

在图5的实例中,点p1calc可对应于中间区段上与上文的图2B的区段216的端与框架220之间的相交点紧密接近的点,且点p2calc可对应于中间区段上与上文的图2B的区段218的端与框架210之间的相交点紧密接近的点。

如图2B中展示,大多数误差发生在装置202的边缘处,且接近区段216的端与框架220之间的相交点,几乎未观察到误差。因此,点p1calc紧密接近p1定位。换句话说,点p1到点p1calc的变换中的位移距离几乎为零。

如在经计算布线510中展示,点p2在经计算布线510上最紧密接近装置202定位,因此,点p2到点p2calc的变换包括大位移。类似地,在此实例中,点pdesign到pcalc的变换包括大于点p1到p1calc的变换且小于点p2到p2calc的变换的位移。

在一些实施例中,处理器从变换接收表示中间区段的图案的一或多个多边形,且沿着相应多边形的边缘508搜索定位于距点pcalc的最小距离处的点qcalc。点pcalc与qcalc之间的距离在本文中被称为经计算宽度,还被称为在经计算布线510上展示的Wcalc。

处理器将相同方法应用到其它点(例如点p1calc及p2calc),以便产生在相应最小距离Wcalc1及Wcalc2处的相应点q1calc及q2calc,借此计算经计算布线510的完整图案。应注意,(例如,来自Wcalc、Wcalc1及Wcalc2当中的)经计算宽度的至少两者可彼此不同。

在一些实施例中,处理器将电子模块的一组设计规则应用到经计算布线510,以便验证与设计规则的合规性,且如果需要,那么调整经计算布线510的图案。在图5的实例中,处理器检查经计算布线510的宽度是否遵守设计规则的经指定宽度。在沿着布线504学习经设计宽度且将这些宽度应用到经计算布线510之后,处理器经配置以通过使用(例如)方程式(3)而确定校正的方向:

其中“dir”是在笛卡尔(Cartesian)坐标系的斜度中展示从pcalc到边缘508上的对应qcalc的校正的方向的单位向量。

在一些实施例中,处理器进一步经配置以使用(例如)方程式(4)计算校正的量:

其中X是沿着向量“dir”的校正的经计算量且|pcalc-qcalc|表示经计算宽度(在图5中展示为Wcalc)的绝对值。

应注意,将经设计宽度与经计算宽度之间的差除以2,这是因为在计算X时,两个边缘(即,边缘506及508)上的点经移位。在其它实施例中,处理器可通过仅移动一个点(例如,通过将506上的点设置为锚且仅移动508上的点,或相反)而计算X。在这些实施例中,将从方程式(4)省略除以2。

随后,处理器将方程式(3)及(4)应用到沿着经计算布线510的多个所选择的点(例如,点p1calc及p2calc),且通过验证或调整经计算布线510的至少一些点而产生实际布线520。

在图5的实例中,处理器设置分别对应于pcalc及qcalc的实际位置,在本文中被称为pact及qact。实际位置被设置为实际宽度(在本文中还被称为实际布线520中展示的Wact),其中Wact遵守相应电子模块的设计规则。

处理器还验证或调整额外对的点(例如对p1act及q1act以及对p2act及q2act)以便产生实际布线520。

上文描述的过程序列及方法是通过实例提供,且在替代实施例中,还可使用其它适合方法。例如,执行特定移位及旋转的经预计算确切解决方案之间的内插或外插,或沿着基于裸片的实际位置的经变形格栅变换迹线,或在设计规则下执行迹线路径的优化。

图6是根据本发明的实施例的用于产生给定电子模块的布局设计600与表示给定电子模块的实际产生组件的数字输入的图像620之间的变换矩阵的过程序列的示意性说明图。在一些实施例中,本文中描述的过程序列包括在上文的图3的步骤306处大体上描述的变换步骤的部分的详细描述。

在一些实施例中,处理器从数据库130接收布局设计600,所述布局设计600包括具有四个配准标记604的面板602及各自分别具有四个配准标记610及612的两个电子模块606及608。在其它实施例中,面板602以及每一电子模块606及608可具有可彼此不同的任何其它适合数目个配准标记。此外,电子模块606及608可具有彼此不同的配置,例如,不同数目及类型的装置及/或电迹线的不同图案。

在其它实施例中,布局设计600可具有包括两个裸片的单个电子模块而非电子模块606及608。下文的描述通过使用术语“裸片”替换术语“电子模块”而适用于这些实施例。

在一些实施例中,处理器从配准测试系统及/或从AOI子系统132接收数字输入的图像620,所述图像620包括对应于布局设计600的面板602的面板622。面板622包括对应于配准标记604的四个配准标记624,以及各自分别具有四个配准标记630及632的两个电子模块626及628。电子模块626及628分别对应于电子模块606及608,且配准标记630及632分别对应于布局设计600的配准标记610及612。

在一些实施例中,处理器基于布局设计600及图像620的前述特征计算变换矩阵以便产生中间区段(及任选地,相应电子模块的额外特征)的经计算布线。

在一些实施例中,处理器通过在电子模块606的坐标系中在配准标记610与630之间匹配而将初始变换矩阵“B”应用到配准标记610。类似地,处理器通过在电子模块608的坐标系中在配准标记612与632之间匹配而将初始变换矩阵“C”应用到配准标记612。

在一些实施例中,处理器通过在面板622的坐标系中在配准标记624与面板602的配准标记604的位置之间匹配而将变换矩阵“A”应用到图像620的面板622的配准标记624。

在一些实施例中,处理器应用变换矩阵“A”以调整初始变换矩阵“B”及“C”,从而导致用于产生电子模块606的所关注点的变换的变换组合物“AB”及用于产生电子模块608的所关注点的变换的变换组合物“AC”。

图7是根据本发明的实施例的用于校正电子装置702与712之间经由衬底777电耦合的误差的布局700的示意性说明图。衬底777可替换(例如)衬底255且装置702及712中的每一者可替换(例如)上文的图2B的装置202。应注意,装置702及712可彼此类似或可彼此不同。

在一些实施例中,布局700包括电子模块(其包括两个装置而非如(例如)上文的图2A中展示那样包括一个装置)的至少部分的布局。

在一些实施例中,布局700包括在装置702的垫704与衬底777的连接器706之间连接的电迹线708。类似地,电迹线718安置于装置712的垫714与衬底777的连接器716之间。在一些实施例中,布局700进一步包括在装置702的垫704与装置712的垫714之间连接的电迹线710。电迹线708、710及718通常类似,但可替代地(例如)在长度及/或宽度及/或材料组合物方面彼此不同。例如,电迹线710可不同于电迹线708。

如描述,例如在上文的图2B中,一或多个取放系统从一或多个相应卷带拾取装置702及712,且将装置702及712耦合到衬底777上的预定义相应位置。装置702及712到衬底777的耦合的放置误差通常类似于在图2B中的装置202到衬底255的耦合中描述的放置误差。又,装置702与712之间的紧密接近性可增加(例如,翻番)待通过布线电迹线710而校正的误差的量值。

在一些实施例中,处理器通常应用上文描述的相同方法以便估计误差且计算实际布线,但可将不同组经允许误差应用到(例如)电迹线708及电迹线710。

在其它实施例中,处理器可将用于计算实际布线的不同组变换矩阵及/或设计规则应用到(例如)电迹线708及电迹线710。

在替代实施例中,处理器可计算用于在垫704及714的至少一些处直接彼此电连接(例如)而非经由衬底777的类似或替代布线。在此等实施例中,直接布线可使用通过LDI子系统136实行的LDI过程或任何适合生产过程(例如打线接合)实行。

在电迹线710的实例中,处理器可将每一电迹线710划分成三个区段:第一区段,其在垫704与装置702的物理边缘703之间;第二区段,其在垫714与装置712的物理边缘713之间;及第三区段,还被称为区720,其连接于第一区段与第二区段之间。

在一些实施例中且根据上文描述的方法论,处理器可调整电迹线710在垫(例如,垫704及714)与区720之间的区段的实际图案以便相对于相应垫保持这些区段的经设计布线。处理器可计算在区720内,校正由装置702及712的放置中相对于布局设计的经组合误差引起的经估计误差的实际布线。随后,处理器可将包括至少经计算实际布线的一或多个执行文件发送到LDI子系统136以便产生电迹线710的实际布线。

应注意,实际上,处理器针对每一电迹线710的全部区段计算实际布线。如上文的图2B中描述,处理器计算迹线710的连接于区720与垫(例如,垫704及714)之间的区段的实际布线,使得这些区段相对于相应垫704及714的相对位置及定向如在设计布局中那样保持。换句话说,垫704及714相对于原始设计移位,因此,耦合到这些垫的区段相应地移位以便与垫704及714中的每一者稳固地连接。

尽管本文中描述的实施例主要解决基于PCB及/或嵌入式裸片程序制造电子模块,但本文中描述的方法及系统还可用于其它应用中,例如显示器或其它电子电路中。

因此,将了解,通过实例引述上文描述的实施例,且本发明不限于上文特定展示且描述的内容。确切来说,本发明的范围包含上文描述的各种特征的组合及子组合两者以及所属领域的技术人员在阅读前述描述之后将想到且在现有技术中未揭示的其变化及修改。以引用的方式并入本专利申请案中的档案应被视为申请案的整体部分,除了在任何术语在这些经并入档案中以与在本说明书中明确或隐含做出的定义冲突的方式定义的程度外,应仅考虑本说明书中的定义。

- 用于校正裸片放置误差的自适应布线

- 用于校正从目标裸片及参考裸片的比较所产生的差异图像的系统、方法及计算机程序产品