存储阵列及其制造方法

文献发布时间:2023-06-19 11:05:16

技术领域

本公开涉及半导体制造技术领域,具体而言,涉及一种具有更高存 储单元密度的存储阵列及其制造方法。

背景技术

针对存储容量扩展困难的问题,相关技术提出了一种增加净模量、 减小单元尺寸的新方法——4F

在上述三维结构中,为了使晶体管正常工作,栅极材料(字线)最 好环绕单晶硅柱,单晶硅柱附近的栅极间距十分小,这种狭小的控件使 得工艺窗口十分狭窄,增加了批量生产的难度。

需要说明的是,在上述背景技术部分公开的信息仅用于加强对本公 开的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现 有技术的信息。

发明内容

本公开的目的在于提供一种存储阵列及其制造方法,用于至少在一 定程度上克服由于相关技术的限制和缺陷而导致的工艺难度较大问题。

根据本公开的一个方面,提供一种存储阵列,包括:

呈m行n列排列的mn/2个单晶硅柱,所述单晶硅柱位于奇数行偶 数列和偶数行奇数列,或者位于奇数行奇数列和偶数行偶数列;

n列平行排列的位线,每条所述位线包裹一列所述单晶硅柱的下 部;

m/2行平行排列的字线,每条所述字线包裹相邻两行所述单晶硅柱 的中部,每条所述字线连接的所述单晶硅柱均不相同,所述字线为波浪 线;

mn/2个电容,所述电容的下极板分别与所述mn/2个单晶硅柱的上 部电连接。

在本公开的一种示例性实施例中,所述电容与所述单晶硅柱轴对齐。

在本公开的一种示例性实施例中,所述电容的轴心与所述单晶硅柱 的轴心沿所述位线具有第一位移,相邻列的所述第一位移的正负号相反, 相同列的所述第一位移的正负号相同。

在本公开的一种示例性实施例中,所述单晶硅柱的横截面为圆形。

在本公开的一种示例性实施例中,所述位线之间的间距相等,所述 字线之间的间距相等。

在本公开的一种示例性实施例中,所述字线之间的间距与所述位线 之间的间距相等。

在本公开的一种示例性实施例中,所述位线之间的间距为所述字线 之间的间距的

在本公开的一种示例性实施例中,所述位线和所述字线之间设置有 介质层,所述介质层的材质为氮化硅和/或氧化硅。

在本公开的一种示例性实施例中,所述位线为直线。

根据本公开的一个方面,提供一种存储阵列制造方法,包括:

提供SOI晶圆;

蚀刻所述SOI晶圆的器件层硅,以形成呈m行n列排列的mn/2个 单晶硅柱,所述单晶硅柱位于奇数行偶数列和偶数行奇数列,或者位于 奇数行奇数列和偶数行偶数列;

在所述器件层硅上制作n列平行排列的位线,每条所述位线包裹一 列所述单晶硅柱的下部;

在所述位线上沉积介质,以制造包裹所述位线和所述单晶硅柱下部 的介质层;

对所述单晶硅柱进行表面氧化后,在所述介质层上制造m/2行平行 排列的字线,每条所述字线包裹相邻两行所述单晶硅柱的中部,每条所 述字线包裹的所述单晶硅柱均不相同,所述字线为波浪线,所述字线的 上表面不高于所述单晶硅柱的上表面;

在所述单晶硅柱的上部上方制作电容。

在本公开的一种示例性实施例中,所述在所述器件层硅上制作n列 平行排列的位线包括:

对所述器件层硅向下蚀刻n列平行排列的所述位线。

在本公开的一种示例性实施例中,所述在所述器件层硅上制作n列 平行排列的位线包括:

在所述器件层硅上通过沉积工艺制作n列平行排列的所述位线。

在本公开的一种示例性实施例中,所述电容与所述单晶硅柱轴对齐。

在本公开的一种示例性实施例中,所述电容的轴心与所述单晶硅柱 的轴心沿所述位线具有第一位移,相邻列的所述第一位移的正负号相反, 相同列的所述第一位移的正负号相同。

在本公开的一种示例性实施例中,所述单晶硅柱的横截面为圆形。

在本公开的一种示例性实施例中,所述位线之间的间距相等,所述 字线之间的间距相等。

在本公开的一种示例性实施例中,所述字线之间的间距与所述位线 之间的间距相等。

在本公开的一种示例性实施例中,所述位线之间的间距为所述字线 之间的间距的

在本公开的一种示例性实施例中,所述介质层的材质为氮化硅和/ 或氧化硅。

在本公开的一种示例性实施例中,所述位线为直线。

在本公开的一种示例性实施例中,还包括:

在刻蚀所述单晶硅柱之前,对所述器件层硅注入第一离子。

在本公开的一种示例性实施例中,还包括:

在制作所述位线之前或之后,对所述位线对应的区域注入第二离子。

本公开实施例通过设置呈蜂窝形式排列的存储单元,并设置波浪形 的字线,可以在使字线包裹单晶硅柱的同时增加单晶硅柱附近的栅极间 距,有效降低工艺难度。

应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解 释性的,并不能限制本公开。

附图说明

此处的附图被并入说明书中并构成本说明书的一部分,示出了符合 本公开的实施例,并与说明书一起用于解释本公开的原理。显而易见地, 下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人 员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他 的附图。

图1是4F

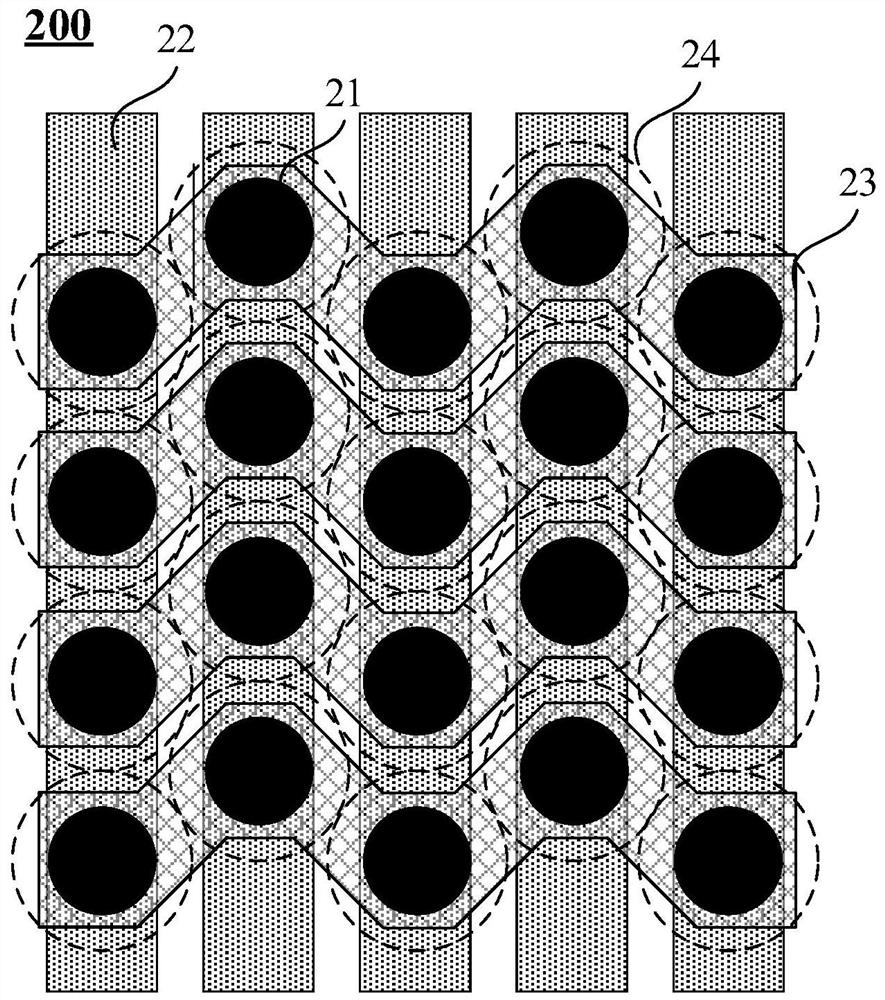

图2是本公开示例性实施例中存储阵列的结构示意图。

图3是本公开实施例中存储阵列的制造过程的流程图。

图4是图3中步骤S31的示意图。

图5A和图5B是图3中步骤S32的示意图。

图6A~图6D是图3中步骤S33的示意图。

图7是图3中步骤S34的示意图。

图8A和图8B是图3中步骤S35的示意图。

图9A~图9C是图3中步骤S36的示意图。

具体实施方式

现在将参考附图更全面地描述示例实施方式。然而,示例实施方式 能够以多种形式实施,且不应被理解为限于在此阐述的范例;相反,提 供这些实施方式使得本公开将更加全面和完整,并将示例实施方式的构 思全面地传达给本领域的技术人员。所描述的特征、结构或特性可以以 任何合适的方式结合在一个或更多实施方式中。在下面的描述中,提供 许多具体细节从而给出对本公开的实施方式的充分理解。然而,本领域 技术人员将意识到,可以实践本公开的技术方案而省略所述特定细节中 的一个或更多,或者可以采用其它的方法、组元、装置、步骤等。在其 它情况下,不详细示出或描述公知技术方案以避免喧宾夺主而使得本公 开的各方面变得模糊。

此外,附图仅为本公开的示意性图解,图中相同的附图标记表示相 同或类似的部分,因而将省略对它们的重复描述。

下面结合附图对本公开示例实施方式进行详细说明。

图2是本公开示例性实施例中存储阵列的结构示意图。

参考图2,存储阵列200可以包括:

呈m行n列排列的mn/2个单晶硅柱21,单晶硅柱位于奇数行偶数 列和偶数行奇数列,或者位于奇数行奇数列和偶数行偶数列;

n列平行排列的位线22,每条位线包裹一列单晶硅柱的下部;

m/2行平行排列的字线23,每条字线包裹相邻两行单晶硅柱的中部, 每条字线包裹的单晶硅柱均不相同,字线为波浪线;

mn/2个电容24,电容的下极板分别与mn/2个单晶硅柱的上部电连 接。

在图2所示实施例中,位线22为直线,单晶硅柱的横截面为圆形, 电容的横截面为圆形,电容与单晶硅柱轴对齐。从图中可以看出,相比 于图1中按照棋盘状排布的存储单元,本公开实施例的相邻存储单元之 间具有较大的栅极距离,在不降低存储单元分布密度的条件下降低了工 艺难度。

此外,在图2所示实施例中,位线22之间的间距相等,字线23之 间的间距相等(此处的间距指两条字线相邻直线部分的间距);在本公开 的其他实施例中,位线22之间的间距也可以具有两种或两种以上尺寸, 字线23之间的间距也可以具有两种或两种以上尺寸,本公开对此不作特 殊限制。

在位线22之间的间距相等且字线23之间的间距相等时,可以设置 字线23之间的间距与位线22之间的间距相等,可以理解,此时位于不 同列的单晶硅柱之间的间距大于同列相邻单晶硅柱之间的间距。在一些 实施例中,也可以设置不同列的单晶硅柱之间的间距等于同列相邻单晶 硅柱之间的间距,即设置位线22之间的间距为字线23之间的间距的

图3是本公开实施例中存储阵列的制造过程的流程图。

参考图3,存储阵列制造方法300可以包括:

步骤S31,提供SOI晶圆;

步骤S32,蚀刻所述SOI晶圆的器件层硅,以形成呈m行n列排列 的mn/2个单晶硅柱,所述单晶硅柱位于奇数行偶数列和偶数行奇数列, 或者位于奇数行奇数列和偶数行偶数列;

步骤S33,在所述器件层硅上制作n列平行排列的位线,每条所述 位线包裹一列所述单晶硅柱的下部;

步骤S34,在所述位线上沉积介质,以制造包裹所述位线和所述单 晶硅柱下部的介质层;

步骤S35,对所述单晶硅柱进行表面氧化后,在所述介质层上制造 m/2行平行排列的字线,每条所述字线包裹相邻两行所述单晶硅柱的中 部,每条所述字线包裹的所述单晶硅柱均不相同,所述字线为波浪线, 所述字线的上表面不高于所述单晶硅柱的上表面;

步骤S36,在所述单晶硅柱的上部上方制作电容。

图4~图9是图3所示流程的工艺过程示意图。

图4是图3中步骤S31的示意图。

在本公开实施例中,存储阵列是在SOI晶圆上制造的。SOI (Silicon-On-Insulator,绝缘衬底上的硅)是指在衬底层硅41和器件层 硅43之间引入了一层埋氧化层42(SiO

图5A和图5B是图3中步骤S32的示意图。

参考图5A,可以通过对柱孔进行掩模、曝光等制程,对器件层硅 43蚀刻呈m行n列排列的mn/2个单晶硅柱21(如图5B所示,m=10, n=5,单晶硅柱数量=25),使单晶硅柱21位于奇数行偶数列和偶数行 奇数列,或者单晶硅柱位于奇数行奇数列和偶数行偶数列。在本公开的 一个实施例中,柱孔(即单晶硅柱的横截面)为圆形,以在更小的周长 下提供更大的导电面积,在其他实施例中,柱孔(即单晶硅柱的横截面) 也可以为其他形状,本领域技术人员可以自行设置。

在一个实施例中,如需通过后续图6A所示的蚀刻工艺制造位线, 则在步骤S32中,无需控制单晶硅柱的蚀刻至氧化层42,保留一定厚度 的器件层硅以供蚀刻位线即可。在另一个实施例中,如需通过后续图6C 所示的沉积工艺制造位线,则为了保证单晶硅柱之间的绝缘,可以在形 成单晶硅柱时控制蚀刻深度氧化层42。

图5B是图5A所示制程的俯视效果图。从图5B可以看出,由于单 晶硅柱呈蜂巢状交错排列,相邻两行单晶硅柱之间的垂直距离得以增大, 为后续增加栅极间距提供了条件。

图6A~图6D是图3中步骤S33的示意图。

参考图6A,在一个实施例中,在器件层硅上制作n列平行排列的位 线的方法,例如可以通过蚀刻器件层硅实现,即对器件层硅向下蚀刻以 制造n列平行排列的位线22。

由于器件层硅的掺杂类型不同,且位线区域的掺杂类型需要与器件 层硅的掺杂类型不同,因此,在刻蚀单晶硅柱之前,需要对器件层硅注 入第一离子,在蚀刻位线前或蚀刻位线后,还需要对位线区域进行第二 离子注入,以改变位线区域的掺杂类型(如图6B所示),最后形成如图 6C所示的效果。

在另一个实施例中,在器件层硅上制作n列平行排列的位线22的方 法,例如可以通过在器件层硅上进行沉积工艺实现(实施效果如图6C 所示)。沉积工艺既可以应用于半导体材质的位线的制作,也可以应用于 金属材质的位线的制作。

图6D是图6C所示步骤的俯视效果图。

图7是图3中步骤S34的示意图。在步骤S34中,沉积形成的介质 层44的材质例如为二氧化硅(SiO

图8A和图8B是图3中步骤S35的示意图。在步骤S35中,制作连 接栅极的位线,首先可以对位线区域对应的单晶硅柱表面进行氧化,以 制造栅氧化层;然后,通过金属沉积、蚀刻(包括干法蚀刻或湿法蚀刻) 工艺制造m/2行平行排列的波浪形状的金属字线23。

在本公开实施例中,字线23为波浪形,以使每条字线包裹相邻两行 所述单晶硅柱21,且每条字线23包裹的单晶硅柱均不相同。通过制造 波浪形的字线23,可以在增加相邻两行单晶硅柱的垂直边距的情况下实 现栅极材料对单晶硅柱的包裹,同时利用更大的单晶硅柱的行间距实现 了更大的栅极间距,在保证更稳定的工作效果的同时降低了工艺难度。

图8B是图8A所示步骤的俯视示意图。

图9A~图9C是图3中步骤S36的示意图。

参考图9A,可以在单晶硅柱21的上部上方制造存储电容24,形成 如图2或图9B所示的存储阵列结构。由于本公开实施例中相邻两列的 单晶硅柱位于不同行,因此制造存储电容后,从图9A所在的侧视视角 看,存储电容之间互相遮挡。其中,存储电容24的结构例如为杯型。

从图9B可以看出,由于单晶硅柱交错排列,字线之间的垂直间距 得以增加,即相邻两行存储单元的栅极之间的间距得以增加,大大增加 了栅极之间的桥接裕度,降低了工艺难度。此外,由于存储单元呈蜂窝 状交错排布,存储电容24可以在直径不变的情况下实现更高密度的排布, 进而在单位面积内制造更多的存储单元,有效提高单位面积内存储阵列 的存储容量。在相同的存储单元数量下,图9B所示结构较图1所示结 构的占用面积缩小了13%,可以在不降低存储容量的前提下有效减小存 储芯片的体积。

图9C是本公开又一个实施例中存储电容24的制造效果图。

由于波浪形字线在造型上存在困难,在本公开实施例中,提出了将 存储电容24与单晶硅柱21非轴对称设置,进而减小字线的曲率,进一 步降低工艺难度。

参考图9C,在本公开的一个实施例中,存储电容24的横截面为圆 形,电容的轴心与单晶硅柱的轴心延位线具有第一位移,相邻列的第一 位移的正负号相反,相同列的第一位移的正负号相同。例如,如果一列 对应的第一位移为L(如图所示),则其相邻列对应的第一位移则为-L, L的值可以由本领域技术人员自行设置。

综上所述,本公开实施例提供的存储阵列制造方法通过设置交错排 布的单晶硅柱以及波浪形排列的字线,不但能够提高相邻字线之间的栅 极间距,增加工艺裕度,还能够提高单位面积内存储单元的排布密度, 增加存储阵列的存储容量。

本领域技术人员在考虑说明书及实践这里公开的发明后,将容易想 到本公开的其它实施方案。本申请旨在涵盖本公开的任何变型、用途或 者适应性变化,这些变型、用途或者适应性变化遵循本公开的一般性原 理并包括本公开未公开的本技术领域中的公知常识或惯用技术手段。说 明书和实施例仅被视为示例性的,本公开的真正范围和构思由权利要求 指出。

- 有控制栅隔片的浮栅存储单元的半导体存储阵列自对准方法及制造的存储阵列

- 存储阵列及其操作方法和制造方法