一种减小高压SiC模块位移电流的结构

文献发布时间:2023-06-19 11:17:41

技术领域

本发明属于功率器件封装技术领域,具体涉及一种减小高压SiC模块位移电流的结构。

背景技术

碳化硅(SiC)功率器件的应用可大幅提高电力电子变换器的性能,目前在工业变频、电动汽车、轨道牵引、再生能源发电等诸多场合中已获得初步应用。随着SiC材料和工艺技术的日趋成熟,SiC功率器件有望取代传统的Si基功率器件,在未来的电力电子变换器中获得更为广泛的应用与发展。

目前,以Si基IGBT为代表的商品化功率器件最高工作电压为6.5kV,SiC器件可应用于更高的电压,10kV SiC MOSFET、18kV SiC IGBT器件已经研制并进行测试。测试表明,Si基IGBT器件开关过程中dv/dt通常较小,在3kV/μs左右,10kV的SiC模块dv/dt可达到200kV/μs。

高压SiC模块使用焊接式方式进行封装,采用DBC(直接敷铜板)进行绝缘及电气连接,其结构为铜层-陶瓷-铜层,上铜层为了和芯片进行连接,中间陶瓷起绝缘作用,下铜层为了和底板进行连接。模块应用中输出点(out)电压变化,高压SiC模块开关时dv/dt和DBC铜层寄生电容(C

丹麦Aalborg大学研究团队在其发表的论文《Reduction of parasiticcapacitance in 10kV SiC MOSFET power modules using 3D FEM》中针对10kV等级SiCMOSFET模块提出采用减小输出侧DBC面积的方式减小寄生电容,减小位移电流。

如图2所示,通过改变图中粉红色DBC铜层的宽度改变输出侧(out)铜层的面积,改变寄生电容。有限元仿真表明,粉红色铜层宽度减小可有效降低寄生电容,降低位移电流。

现有技术在减小寄生电容方面存在的缺点如下:

减小铜层面积使得电流流通路径电阻增加,模块损耗增加;

铜层热导率高,面积减小使得芯片产生的热量通过铜层横向扩展小,芯片结温高。

发明内容

本发明的目的是提供一种减小高压SiC模块位移电流的结构,通过减小输出侧DBC寄生电容,降低模块位移电流。

本发明所采用的技术方案是,一种减小高压SiC模块位移电流的结构,包括高压SiC芯片下部电极通过焊接方式连接到下DBC层的DBC上铜层,高压SiC芯片上部电极通过键合方式连接到下DBC层的DBC上铜层,下DBC层的DBC下铜层通过焊接方式连接到底板,AC侧芯片以外进行双层DBC串联。

本发明的特点还在于,

AC侧芯片以外进行双层DBC串联具体为:包括串联连接固定在所述下DBC层的DBC上铜层上的上DBC层,上DBC层从上至下依次包括DBC上铜层、中间陶瓷层、DBC下铜层,DBC上铜层即为上覆铜层,DBC下铜层即为下覆铜层。

下DBC层从上至下依次包括DBC上铜层、中间陶瓷层、DBC下铜层,DBC上铜层即为上覆铜层,DBC下铜层即为下覆铜层。

上DBC层的DBC上铜层通过键合线与下DBC层的DBC上铜层键合连接。

下DBC层的DBC下铜层与底板之间通过DBC焊料层焊接固定。

高压SiC芯片下部电极与下DBC层的DBC上铜层之间通过芯片焊料层固定连接。

本发明的有益效果是,一种减小高压SiC模块位移电流的结构,该结构不减小AC侧导电铜层面积,不会增加回路电阻;该结构不需要更改原来有芯片及DBC布局设计,只需要在AC侧芯片以外面积焊接DBC及键合连接即可;上层DBC材料及厚度对电气性能无影响,可最大程度降低寄生电容;上层DBC可与芯片同时焊接及键合,不增加工艺流程。

附图说明

图1是半桥结构模块交流点与散热器之间形成位移电流的结构图;

图2是DBC优化方法结构图;

图3是既有高压SiC模块封装结构;

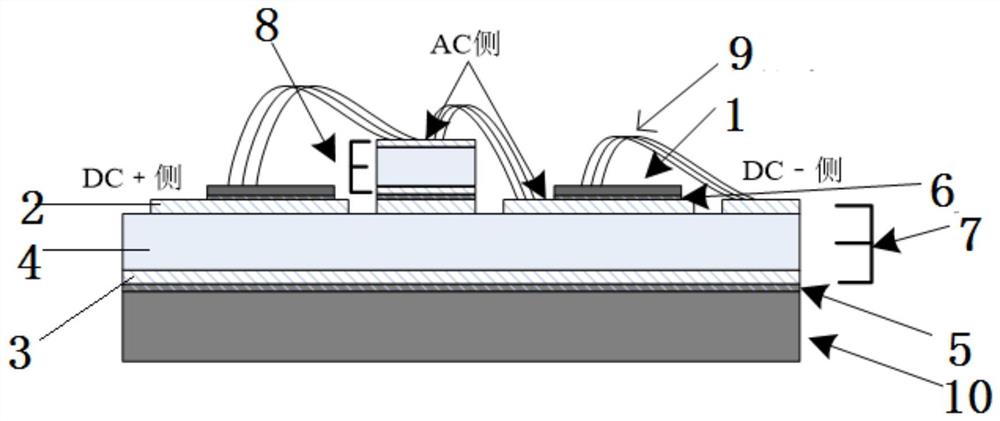

图4是本发明减小高压SiC模块位移电流的结构。

图中,1.高压SiC芯片,2.DBC上铜层,3.DBC下铜层,4.中间陶瓷层,5.DBC焊料层,6.芯片焊料层,7.下DBC层,8.上DBC层,9.键合线,10.底板。

具体实施方式

下面结合附图和具体实施方式对本发明进行详细说明。

高压(≥10kV)SiC模块是今后功率器件的发展趋势,高压SiC模块开关过程中会产生很高的dv/dt,结合模块封装绝缘材料DBC寄生电容会产生很大的位移电流,危害散热器及整个系统。

以目前常用的AlN陶瓷材料DBC计算,厚度d为0.63mm,介电常数ε

C

I

本发明一种减小高压SiC模块位移电流的结构,通过减小输出侧DBC寄生电容,降低模块位移电流。

本发明在模块设计时不考虑上层DBC设计,下层DBC布局确定后在AC侧芯片焊接以外的部分设计上层DBC岛,图形可与芯片焊接以外图形一致,也可以分开设计,要求上层DBC面积尽可能大。该发明不改变原有封装工艺,进行芯片焊接的同时实现上层DBC的焊接,进行芯片键合时同时实现上层DBC的键合。本发明可以采用所有AC侧双层DBC实现。同样可以通过在AC侧芯片以外的面积串联电容等方式降低整个AC侧寄生电容的思路实现,不仅限于DBC材料。

本发明一种减小高压SiC模块位移电流的结构,在传统图3的基础上改进,包括高压SiC芯片1下部电极通过焊接方式连接到下DBC层7的DBC上铜层2,高压SiC芯片1上部电极通过键合方式连接到下DBC层7的DBC上铜层2,下DBC层7的DBC下铜层3通过焊接方式连接到底板10,结构如图4所示,AC侧芯片以外进行双层DBC串联。

AC侧芯片以外进行双层DBC串联具体为:包括串联连接固定在所述下DBC层7的DBC上铜层2上的上DBC层8,上DBC层8从上至下依次包括DBC上铜层2、中间陶瓷层4、DBC下铜层3,DBC上铜层2即为上覆铜层,DBC下铜层3即为下覆铜层。

下DBC层7从上至下依次包括DBC上铜层2、中间陶瓷层4、DBC下铜层3,DBC上铜层2即为上覆铜层,DBC下铜层3即为下覆铜层。

上DBC层8的DBC上铜层2通过键合线9与下DBC层7的DBC上铜层2键合连接。

下DBC层7的DBC下铜层3与底板10之间通过DBC焊料层5焊接固定。

高压SiC芯片1下部电极与下DBC层7的DBC上铜层2之间通过芯片焊料层6固定连接。

既有高压SiC模块结构与现有焊接式Si基IGBT模块结构相同,高压SiC芯片下部电极通过焊接方式连接到DBC上铜层,上部电极通过键合方式连接到DBC上铜层,DBC下铜层通过焊接方式连接到底板。实际模块中,受模块尺寸、芯片并联数量、铜层通流能力要求,AC侧铜层面积较大且不容易减小,按照电容公式C

按照寄生电容计算方式,串联可减小寄生电容,因此采用双层DBC的方式可实现减小寄生电容的目的。然而实际应用中,双层DBC增加了芯片的热阻,提高了模块工作时芯片的结温。本发明提出在AC侧芯片以外DBC进行双层DBC设计,上层DBC通过焊接方式与下部DBC连接,键合方式实现电气连接,该方式可有效降低AC侧寄生电容,降低位移电流。

为最大程度的降低AC侧寄生电容,需增大上层DBC的电容,因此上层DBC面积应尽可能的大,厚度尽可能的小。

本发明一种减小高压SiC模块位移电流的结构,针对高压SiC模块开关过程中高dv/dt的问题,不需要改变原有芯片及DBC布局设计,在AC侧芯片以外的铜层采用双层DBC方式降低寄生电容,减小模块位移电流,与减小AC侧面积相比,本发明具有如下优势:

1.该方式不减小AC侧导电铜层面积,不会增加回路电阻;

2.该方式不需要更改原来有芯片及DBC布局设计,只需要在AC侧芯片以外面积焊接DBC及键合连接即可;

3.上层DBC材料及厚度对电气性能无影响,可最大程度降低寄生电容;上层DBC可与芯片同时焊接及键合,不增加工艺流程。

- 一种减小高压SiC模块位移电流的结构

- 薄膜电容组及适用于高压SiC MOSFET模块的低杂感母排