可测试性设计的适应性微电子电路的应用

文献发布时间:2023-06-19 11:26:00

技术领域

本发明大致上应用于微电子电路和电路组件的技术领域。特别地,本发明应用于可测试性设计的适应性微电子电路和电路组件。

背景技术

微电子电路(例如,微处理器、微控制器及类似者)藉由以由程序化指令所决定的特别方式,让大量的数字数值通过许多个处理路径,而基本地运作。处理路径典型地包含程序化逻辑的片段,在片段之间,有用于以由时钟信号所定义的速率暂时地储存数字数值的缓存器电路。微电子电路也可称为微电子系统,但微电子系统的概念也可用来指包含数个微电子电路的装置。

为了确保微电子电路或系统适当地运作,必须有可能测试其运作。DFT(DesignedFor Testability,或Design-For-Test)的概念已经变成多个实务或事实上的标准的经建立的集合性定义,其告诉微电子电路的设计者如何能确保可测试性。作为一范例,应可能选择性地将微电子电路内所含有的缓存器电路耦接进入主要地运作成移位寄存器的长链:一串数位数值可从一端点馈入,而从另一端点读出。使已知测试图案(test pattern)通过这种链的缓存器电路并且在输出核对其形状,告诉链中的所有缓存器电路是否正在如所希望的改变它们的状态、或是否有缓存器电路固定在一些特别数值(固定型故障测试(stuck-atfault test)。高速(at-speed)故障测试涉及以低时钟速度缓慢馈入测试图案,之后以全运作速度给出一个或更多个时钟脉波,以致于测试图案在链中以功能性逻辑速度进行与时钟脉波所具有一样多的步骤,并且最终再次以低时钟速度结束测试图案。高速测试可能会比预期慢给出关于缓存器电路的信息。

虽然DFT方法对于接受制造电路的测试和对于微电子系统的正确运作的一些运行时间监视是好的,但它的已知应用并没有给出关于电路和电路组件的性能优化或特性化的优化工具。

发明内容

本发明的目的是提出方法、微电子电路和微电子电路组件,其让使用DFT方法用于电路和电路组件的性能优化和特性化成为可能。

本发明的目的藉由微电子电路适应地配备适应性电路组件加以达成,以致于运作参数的数值的适应性可与DFT方法结合。

依据本发明的一个方面,提供用于运作适应性微电子电路的方法。它的效能可藉由让运作参数假定运作参数数值而加以配置。该方法包含选择性设定该微电子电路进入与该微电子电路的正常运作模式不同的测试模式、以及利用该测试模式以输入由测试输入数值所组成的测试输入信号进入该微电子电路内的一个或更多个适应性处理路径。适应性处理路径包含处理逻辑和缓存器电路,其被配置成从输入至它们的输入数值产生输出数值。这种适应性处理路径的效能可藉由让运作参数假定运作参数数值而加以配置。该方法包含让该一个或更多个适应性处理路径根据输入至它们的该个别测试输入数值形成测试输出数值、以及藉由收集由该一个或更多个适应性处理路径所给定的该测试输出数值形成一组测试输出信号。该方法包含检查该组测试输出信号、以及根据该检查形成测试结果、以及使用该测试结果选择和设定用于该运作参数的运作参数数值。

依据实施例,被设定的该运作参数数值被用来对该一个或更多个适应性处理路径的效能作出影响。这具有以下优点:可在许多情况下利用电路的适应性,甚至在运作期间也可动态地利用。

依据实施例,该方法包含藉由接续地设定用于该运作参数的至少第一和第二运作参数数值、根据检查于该运作参数具有该第一运作参数数值时所形成的第一组测试输出信号形成第一测试结果、根据检查于该运作参数具有该第二运作参数数值时所形成的第二组测试输出信号形成第二测试结果、以及形成指示该第一与第二测试结果之间的差异的特性化数值,以特性化该微电子电路。这具有以下优点:可验证并量化对于该微电子电路的运作和效能上的有利影响。

依据实施例,该方法包含藉由设定该第一和第二运作参数数值使得该第一运作参数数值在该适应性处理路径的性能上与该第二运作参数数值有不同的效应,而特性化该微电子电路内的适应性处理路径。这具有以下优点:可量化该运作参数数值的效应。

依据实施例,该方法包含根据该特性化数值而将该微电子电路分类至效能分类。这具有以下优点:可依据个别微电子电路满足它们的预期规格的程度而设定个别微电子电路的数值。

依据实施例,该效能分类是下列的至少一个:用于微电子电路的电压分类,对应的特性化数值针对该电压分类指示对于给定时钟速度的可接受最小运作电压;用于微电子电路的时钟速度分类,对应的特性化数值针对该时钟速度分类指示在给定运作电压下的可接受最大时钟速度;用于微电子电路的能量分类,对应的特性化数值针对该能量分类指示用于最小运作电压和最大时钟速度的结合的可接受能量消耗。这具有以下优点:电子装置的制造商可选择最适合特别种类的电子装置中的特别需求的微电子电路。

依据实施例,该适应性缓存器电路包含缓存器输入、时钟输入、缓存器输出和时序事件输出;该适应性缓存器电路包含在该缓存器输入与该缓存器输出之间的数据储存器,用于暂时地储存于与出现在该时钟输入处的时钟信号相关的可允许时间限制时出现在该缓存器输入处的数据数值;该适应性缓存器电路包含时序事件观察阶段,其配置成在该时序事件输出处输出时序事件观察信号,以响应该数据数值在该缓存器输入处的改变,该改变在与该时钟信号相关的该可允许时间限制之后发生;以及形成一组测试输出信号的该方法步骤包含收集由该时序事件观察阶段给定的输出数值。这具有以下优点:可依据DFT原理测试该时序事件观察阶段的运作。

依据实施例,该方法包含冻结该时序事件观察信号的数值比该时钟信号中的一个时钟周期更长周期,用于之后收集该时序事件观察信号的该冻结数值,以形成该组测试输出信号。这具有以下优点:在测试中收集时序事件观察信号不需要以完全时钟速度强制地运作。

依据实施例,该方法包含暂时地失能该时序事件观察阶段的运作、经由该缓存器输入将该测试输入数值输入进入该数据储存器、以及收集在该缓存器输出处给出的该测试输出数值;用于独立于该时序事件观察阶段的运作来测试该数据储存器的运作。这具有以下优点:该数据储存器的运作的测试可独立于该时序事件观察阶段的运作。

依据实施例,该测试模式包含至少一个标准化DFT测试模式,这其中包括但不限于固定型故障测试、实速故障测试。这具有以下优点:该方法可兼容于共同使用的DFT原理。

依据另一个方面,有提供包含处理路径的微电子电路。该处理路径包含电路组件,例如,处理逻辑和缓存器电路,而该处理路径适应地响应于可用于该电路组件的运作参数的数值。该微电子电路包含测试输入布置,其被配置成受控地馈入由测试输入数值所组成的测试输入信号进入该处理路径的多个电路组件。该微电子电路包含被配置成受控地收集来自该处理路径的该多个电路组件的测试输出数值的测试输出布置、以及被配置成根据该收集的测试输出数值选择该运作参数的该数值的运作参数数值选择器。

依据实施例,该电路组件的一者是缓存器电路,其包含沿着数据传播路径串接的第一子缓存器级和第二子缓存器级;该缓存器电路包含用于接收触发信号的触发事件输入,该触发信号的触发边缘定义可允许时间限制,在可允许时间限制前,数字数值必需出现在该第一子缓存器级的数据输入处,以变成暂时地储存的;并且该缓存器电路包含时序事件观察阶段,其与该数据传播路径耦接并且被配置成在该缓存器电路的输出处输出时序事件观察信号,作为该数字数值在该数据输入处的指示器,该数字数值已经在时间窗口内改变,该时间窗口从该可允许时间限制开始并且比该触发信号的一个周期短。这具有以下优点:可在这种缓存器电路中成功地完成时间借用并且所执行的时间借用的指示可用于进一步的处理和结论。

依据实施例,该测试输出布置是被配置成受控地收集来自该缓存器电路的数据输出的测试输出数值,该数据输出是该第二子缓存器级的输出。这具有以下优点:可依据DFT原理测试该缓存器电路的正确运作。

依据实施例,该测试输出布置是配置成受控地收集该时序事件观察信号的数值作为该测试输出数值。这具有以下优点:可依据DFT原理测试该时序事件观察阶段的正确运作。

依据实施例,该运作参数包含下列的至少一者:运作电压、时钟速度。这具有以下优点:可以各种方式适应该微电子电路的运作。

依据仍然另一个方面,提供一种缓存器电路,用于暂时地储存从微电子电路中的先前电路组件的输出所获得的数字数值。该缓存器电路包含用于接收数字数值用于暂时性储存的数据输入、以及用于输出该暂时储存的数字数值的数据输出。该缓存器电路包含用于接收触发信号的触发事件输入,该触发信号的触发边缘定义可允许时间限制,在可允许时间限制前,数字数值必需出现在该数据输入处,以变成暂时地储存的,并且在该数据输入与数据输出之间的数据传播路径上,有一序列的第一子缓存器级和第二子缓存器级。该第一子缓存器级是配置成相对于由该第二子缓存器级所接收的该触发信号而延迟的该触发信号,该延迟的长度为该触发信号的周期的片段。该缓存器电路包含时序事件观察逻辑,其被配置成在该缓存器电路的输出处输出时序事件观察信号,作为该数字数值在该数据输入处的指示器,该数字数值在时间窗口内已经改变,该时间窗口从该可允许时间限制开始并且比该触发信号的一个周期短。该缓存器电路是适应地响应于可用于该缓存器电路的运作参数的数值。

依据仍然另一个方面,提供一种监视器电路,用于侦测微电子电路的缓存器电路中的时序事件。该监视器电路包含用于接收触发信号的触发事件输入,该触发信号的触发边缘定义可允许时间限制,在该可允许时间限制前,数字数值必需出现在该缓存器电路的数据输入处,以变成暂时地储存在该缓存器电路。该监视器电路包含监视输入,其用于在该数字数值出现在该缓存器电路的该数据输入处的相同时间接收该数字数值的监视副本。该监视器电路包含时序事件观察输出、以及时序事件观察逻辑,该时序事件观察逻辑配置成在该时序事件观察输出处输出时序事件观察信号,作为该数字数值在该数据输入处的指示器,该数字数值在时间窗口内已经改变,该时间窗口从该可允许时间限制开始并且比该触发信号的一个周期短。该监视器电路包含输出管理单元,配置成致能收集该时序事件观察信号的数值,用于该监视器电路外部的进一步处理。该监视器电路适应地响应于可用于该监视器电路的运作参数的数值。

依据实施例,该输出管理单元包含用于接收输出冻结命令的控制输入,其中,该监视器电路是配置成藉由保持该时序事件观察信号的目前数值不变,而响应接收到的输出冻结命令。这具有以下优点:时序事件观察信号在测试中的收集不需要以完全时钟速度强制地运作。

依据实施例,该输出管理单元包含多任务器,其被配置成选择性导引该时序事件观察信号的数值至该监视器电路外部的扫描链,以取代该缓存器电路的数据输出数值。这具有以下优点:可利用单一扫描链用于两者目的。

附图说明

包括随附图式以提供本发明的进一步了解并构成此说明书的一部分,随附图式例示本发明的实施例,配合描述有助于了解本发明的原理。在该图式中:

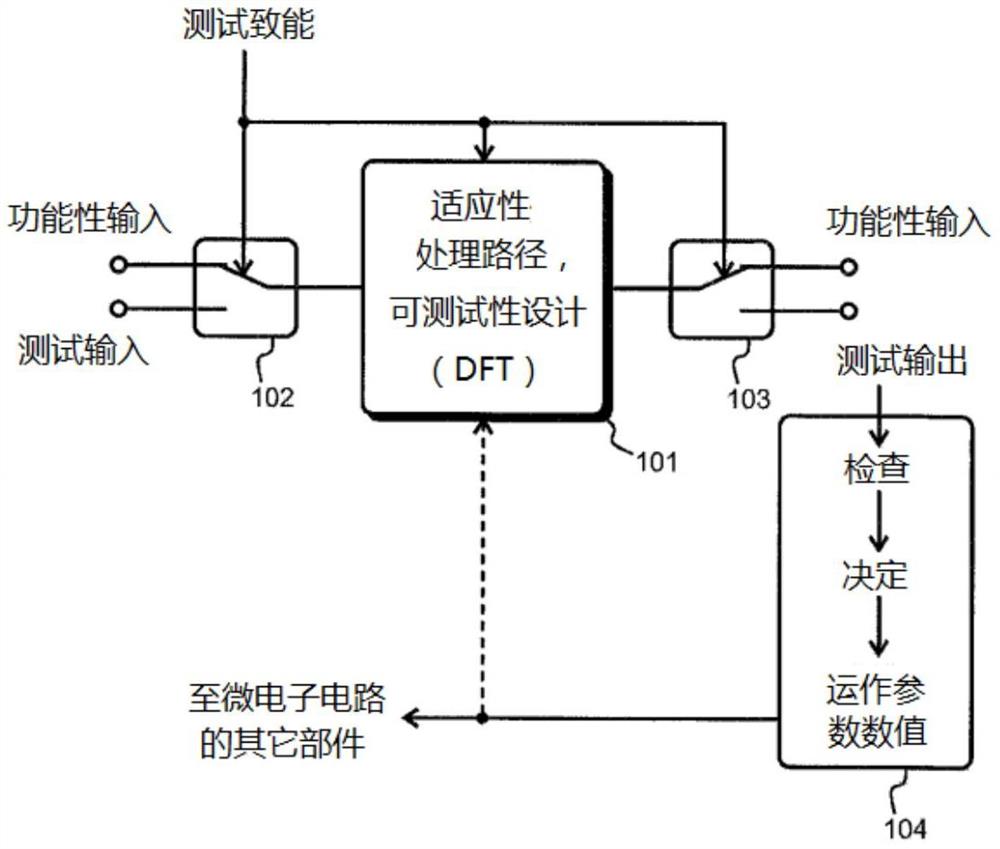

图1例示微电子电路中的适应性和DFT的概念,

图2示意地例示适应性监视器电路的使用,

图3示意地例示复制路径的使用,

图4例示适应性和DFT的一些有利使用,

图5例示适应性和DFT的一些有利使用,

图6示意地例示具有监视的缓存器电路,

图7示意地例示具有监视和TEO输出数值保持的缓存器电路,

图8例示具有监视器和DFT特性的适应性缓存器电路,

图9例示具有监视器和DFT特性的适应性缓存器电路,

图10例示具有监视器和DFT特性的适应性缓存器电路,

图11例示具有监视器和DFT特性的适应性缓存器电路,

图12例示具有监视器和DFT特性的适应性缓存器电路,

图13例示具有监视器和DFT特性的适应性缓存器电路,

图14例示具有监视器和DFT特性的适应性缓存器电路,

图15例示具有监视器和DFT特性的适应性缓存器电路,

图16例示具有监视器和DFT特性的适应性缓存器电路,

图17例示具有监视器和DFT特性的适应性缓存器电路,以及

图18例示具有监视器和DFT特性的适应性缓存器电路。

具体实施方式

适应性微电子电路或系统是其中的运作参数的数值在运作期间可以某种方式改变而优化效能的一种装置。最重要的运作参数为运作电压和时钟速度。最后提到的是确定出现在缓存器电路的输入处的数字数值会被储存并在该缓存器电路的输出处可用的速率。

为了最小化该微电子电路的能量消耗,让运作电压尽可能地低是有利的。但运作电压并不能作得任意地低,因为较低运作电压在电路组件中的状态之间引发较慢转换,其接着可能引发时序错误和不确定状态。然而,可以维持微电子电路的满意效能的运作电压的最小值不一定是恒定的,而是可随着例如系统的温度、将被处理的数据的重要性、应该实施的处理运作的本质、或类似者而加以变化。关于运作电压的适应性意指该运作电压的数值可动态地改变,但同时使用一些监视机制来确保特定测量或效能(像是处理错误或时序事件的发生)仍然在特定可接受的限制内。

可以许多方式使用适应性时钟速度,以优化效能。高时钟速度自然地让处理较快,因为处理后的数据通过微电子电路的处理路径而较快地移动。与此同时,高时钟速度已知增加能量消耗并让时序事件更频繁地发生。关于时钟速度的适应性可涉及需要快速处理时让时钟速度变高,并于最小化能量消耗时优先降低时钟速度。运作电压和时钟速度也可同时地适应,以发现最佳工作点,在该最佳工作点,该微电子电路的能量消耗相对于电路处理数据的速率是在最小值。

图1是适应性微电子电路的示意例示。该图式也被检查成用来运作适应性微电子电路的方法的示意例示。在此描述中,该微电子电路是适应性的事实意指该微电子电路的效能可藉由让运作参数假定为运作参数数值而加以配置。这些运作参数的范例包括、但不限于运作电压和时钟速度。

适应性微电子电路包含一个或更多个适应性处理路径101。处理路径大致上包含处理逻辑和缓存器电路,并且配置成从输入至它的输入数值产生输出数值。典型地在正常运作模式中,处理逻辑和缓存器电路以交错方式配置,使得暂时地储存在第一缓存器电路中的数字数值被馈入至第一片段的处理逻辑,所生成的处理数值被暂时地储存在第二缓存器中然后从该第二缓存器被馈入至第二片段的处理逻辑,以此类推。处理路径是适应性处理路径,如果它的电路组件的一者或更多者是适应性的,使得该处理路径变成适应地响应用于该一个或更多个电路组件的运作参数的数值。

图1的适应性微电子电路也是DFT,意指可测试性设计(Designed ForTestability)。此意指它的适应性处理路径101的一者或更多者可选择性地设定进入与正常运作模式不同的测试模式。设定适应性处理路径进入测试模式的范例包含耦接数个缓存器电路进入扫描链,使得它们一起运作像是在测试模式中的移位寄存器。

在图1的示意呈现中,藉由启动测试致能(Test Enable)信号而使设定进入测试模式。图1显示启动测试致能信号的三个可能效应。首先,它可影响输入信号被供应至适应性处理路径101的方式:取代在正常模式时输入所谓功能性输入信号,利用该测试模式输入由测试输入数值所组成的测试输入信号进入该微电子电路内的一个或更多个适应性处理路径101。其次,它可影响该测试输入数值在该适应性处理路径101内被管理(handled)的方式,让该一个或更多个适应性处理路径根据输入至它们的个别测试输入数值形成测试输出数值。第三,它可影响由该一个或更多个适应性处理路径所给定的该测试输出数值被收集和形成进入一组测试输出信号的方式。

适应性微电子电路包含测试输入布置,其配置成受控地馈入由测试输入数值所组成的测试输入信号进入适应性处理路径101的多个电路组件。第一开关102示意地例示启动测试致能信号是如何影响输入信号被提供的方式:不是像在正常运作模式时馈入功能信号,而是馈入测试输入信号。测试输入信号可举例来说是已知向量,也就是特别顺序的已知序列的数字数值(0和1)。

适应性微电子电路包含测试输出布置,其配置成受控地收集来自适应性处理路径101的多个电路组件的测试输出数值。第二开关103示意地例示启动测试致能信号是如何影响输出数值被管理的方式:不是将输出数值引导到进一步的处理或是以其他方式于正常运作模式时使用它,而是收集该测试输出数值以形成可被检查的测试输出信号。根据这种检查形成测试结果,以指示该测试如何进行,也就是该测试是否透露出适应性处理路径101的运作中的任何异状或错误。

启动测试致能信号如何影响测试输入数值在适应性处理路径101内被管理的方式的范例之后在此文本中会更详细地描述。应注意到,即使图1例示仅例示单一测试致能信号,此只是例示的简化。图1中有显示适应性微电子电路的不同部件的个别测试致能信号,并且这些可彼此独立或彼此仅有一些相关性而运作,视将作何种测试及将完成什么而定。

在图1中所显示的方案中,结合DFT和适应性的概念。此意指可使用测试结果以选择和设定用于适应性微电子电路的一个或更多个运作参数的一个或更多个新数值。图1示意地显示运作参数数值选择器104,其配置成根据所收集的测试输出数值选择运作参数的数值。可使选择和设定的运作参数数值直接地影响从中收集测试输出信号的一个或更多个适应性处理路径101的效能。此是以图1中的虚线例示。额外地或不同地,可使选择和设定的运作参数数值影响适应性微电子电路的其它部件的效能。

第2和3图例示一些稍微更详细的范例,在该范例中,DFT和适应性是组合在电路组件的阶层上。

图2示意地例示适应性缓存器电路,其可为适应性微电子电路中的适应性处理路径的部件。适合的缓存器电路,也就是用于数字数值的暂时储存,是显示为201。它具有用来接收数字数值以暂时储存的数据输入202、以及用来输出暂时储存的数字数值的数据输出203。适应性微电子电路的测试输入布置由第一开关204表示,其可用来选择性耦接功能性输入信号(在正常运作模式期间)或测试输入信号(在测试模式期间)至该数据输入202。适应性微电子电路的测试输出布置由第二开关205和第三开关206表示。这两者均配置成受控地收集来自适应性缓存器电路的测试输出数值,以形成测试输出信号。

适应性缓存器电路可包含其它输入,其为了图式简洁而没有显示在图2中。作为范例,适应性缓存器电路可包含触发事件输入和测试致能输入。在这些当中,触发事件输入允许缓存器电路接收触发信号,该触发信号的触发边缘定义可允许时间限制(allowabletime limit),在该可允许时间限制前,数字数值必需出现在该数据输入处,以变成暂时地储存的。触发信号通常是称为时钟信号。缓存器电路的类型可例如为在时钟信号的各个升缘处被触发的类型。在这种案例中,可允许时间限制意指在数据输入202处的数字数值必需在特定时间窗口内设定妥当,其相关于时钟信号的升缘而设定,以为了变成正确地暂时地储存在适应性缓存器电路中。

数据输入202处的数字数值改变过迟,也就是在可允许时间限制后才改变的情况称为时序事件。为了用于时序事件的监视,图2的适应性缓存器电路包含监视器电路207。它被描述成时序事件观察(TEO)逻辑,其配置成在缓存器电路的输出处输出时序事件观察(TEO)信号作为数字数值在数据输入202处改变过迟的指示器。“过迟”的更精确定义在此方面为“在一个时间窗口内,该时间窗口从该可允许时间限制开始并且比该触发信号的一个周期短”。如何实作监视器电路207并不重要,只要它能够实施此文本中所描述的运作即可。监视器电路如何实作的范例可例如先前提出的专利申请案第PCT/FI2017/050290号中发现的。

可使用在图2的适应性缓存器电路的输出处的下开关205来选择性地导引数据输出203处的数字数值至正常运作模式下的正规使用(“功能性输出”)或至测试数值的收集(“测试输出”)。类似地,可使用图2的适应性缓存器电路的输出处的上开关206来选择性地导引TEO输出处的数字数值至正常运作模式下的正规使用(“功能性TEO输出”)或至测试数值的收集(“测试TEO输出”)。

如图2的上部分中所例示的,可使用测试致能或其它对应输入信号来控制适应性缓存器电路的输入和输出连接(也就是开关204、205和206),并连同其内部运作。此意指适应性缓存器电路是DFT(Designed For Testability,或Design-For-Test)。如图2的下部分中所例示的,适应性微电子电路中的运作参数的选择和设定的数值可影响运作电压、时钟速度、以及也影响图2的适应性缓存器电路的其它运作参数数值。此解释它为何是“适应性”缓存器电路。

使用监视器(或者:“配置成在缓存器电路的输出处输出TEO信号的TEO逻辑,作为数字数值在数据输入处已经过迟改变的指示器”)并不是用来在电路组件的阶层上结合DFT和适应性的唯一可能性。图3示意地例示不同者,也就是复制路径的使用。

在图3中,适应性缓存器电路包含适合的缓存器电路,也就是暂时储存用于数字数值,是显示成301。它的数据输入和数据输出是分别显示成302和303。适应性微电子电路的测试输入布置由第一开关304表示,其可使用来选择性地耦接功能性输入信号(在正常运作模式期间)或测试输入信号(在测试模式期间)至数据输入302。适应性微电子电路的测试输出布置由第二开关305表示,配置成受控地收集来自适应性缓存器电路的数据输出303的测试输出数值,以形成测试输出信号。在正常运作模式中,第二开关305导引数据输出303处的数字数值,以正规使用。

复制路径311设置在相同适应性微电子电路内。复制路径311尽可能是适合的缓存器电路301的副本,除了它的数据输入312是耦接成接收预定测试输入数值并且它的数据输出313是固定地耦接成传送测试输出数值至测试输出信号的形成外。使用复制路径311的想法是它模仿真实部件的运作,以致于如果该复制路径的运作开始引发事件,则有可能事件也发生在该真实部件的运作中。复制路径的运作中的事件较容易侦测,因为至各个复制路径的输入数值是预定且已知的。由于没有两个电路组件是精确地相同的,因此,所谓的复制路径限度(margin)可添加至该复制路径311的运作。使用复制路径限度意指该复制路径311是故意地作得有一点较慢及/或相依于比真实部件有一点较高的运作电压,以致于当时钟速度增加及/或运作电压降低时,时序事件最可能在该复制路径311的运作中先变成看得见。

如图3的上部分中所例示的,可使用测试致能或其它对应输入信号来控制适应性缓存器电路的输入和输出连接(也就是开关304和305),并连同其内部运作,像是开启或关闭该复制路径311。此意指该适应性缓存器电路是DFT(Designed For Testability,或Design-For-Test)。如图3的下部分中所例示的,适应性微电子电路中的运作参数的选择和设定数值可影响运作电压、时钟速度、复制路径限度、以及也影响图3的该适应性缓存器电路的其它运作参数数值。此解释它为何是“适应性”缓存器电路。

可以许多方式利用DFT和适应性的结合。这种方式的范例例示在第4和5图中。

图4的左手侧例示用来动态地优化适应性微电子电路的性能的方法,首先没有利用其DFT特性。此处,额外地假定该适应性微电子电路是配备有上方参考图2所解释的类型的电路组件,以致于时序事件的发生可由监视TEO输出处所出现的数值而加以监视。此方法于该适应性微电子电路运作在其正常运作模式中时执行。如果观察到增加数目的时序事件,即使它意指增加能量消耗,则该适应性微电子电路的控制实体降低时钟速度、增加运作电压、及/或采取一些其它预警动作用来约束时序事件的增加。因此,如果观察到减少或零数目的时序事件,则该控制实体增加时钟速度、降低运作电压、及/或采取一些其它有益动作以用来降低能量消耗、增加处理速度、或完成一些其它有利效能目标,同时持续监视时序事件的数目没有增加至不可接受的程度。

图4的右手侧例示用来特性化相同适应性微电子电路的方法,利用其DFT特性。该适应性微电子电路是运作在测试模式中,靠它自己(如果它能够自己产生和分析测试信号)或与测试装置结合,举例来说,在制造线的末端,应该对制造线中刚制造的微电子电路予以特性化。

左分支代表时间借用失能的运作。换言之,即使适应性微电子电路的缓存器电路配备有像图2中的监视器,它们是暂时地关闭或它们的TEO输出没有使用。尝试用于运作参数的不同数值;更正式地它可说成至少第一和第二运作参数数值被接续地设定,以用于特别运作参数。根据检查于该运作参数具有该第一运作参数数值时所形成的第一组测试输出信号,形成第一测试结果。根据检查于该运作参数具有该第二运作参数数值时所形成的第二组测试输出信号,形成第二测试结果。可形成特性化数值,以指示该第一与第二测试结果之间的差异。

可重复此测试方式,变化运作参数数值,直到什么范围的运作参数数值分别导致可接受和不可接受效能变得清楚为止。举例来说,运作参数可为时钟速度,而测试可以各种时钟速度重复,直到发现第一效能限制为止:超过某些重要时钟速度,适应性微电子电路会在该测试中作出非常多错误,以致于它的效能变得不可接受。由于时间借用是失能的,因此,可将所发现的第一效能限制记录并文件化适应性微电子电路的“标准”或“正常”效能。

右分支代表时间借用致能的运作。现在缓存器电路的监视器开启,并且它们的TEO输出被使用。利用TEO输出典型地允许适应性微电子电路适当地实施在较高时钟速度及/或较低运作电压。因此,当重复相同测试时,有可能发现更有利的第二效能限制。此可记录和文件化适应性微电子电路的“改进”效能,该改进是有效地利用适当地配备的缓存器电路中的时间借用的结果。

在上方,考虑到的是整个微电子电路的特性化,但可使用类似方法以特性化较小部件,像是微电子电路内的个别适应性处理路径。可设定第一和第二运作参数数值,使得该第一运作参数数值在适应性处理路径的效应上具有与该第二运作参数数值的不同效果。可注意、记录和文件化效能中的差异作为适应性处理路径的DFT和时间借用能力改进了多少其效能的特性化。

可利用图4中所例示的方式所作出的特性化来实施所谓的分类(binning)。适应性微电子电路的制造商可能想要根据其以上述方式获得的电路特定的特性化数值将例如新制造的适应性微电子电路分类为效能分类。

效能分类可包含用于微电子电路的电压分类,其对应的特性化数值针对电压分类指示用于给定时钟速度的可接受最小运作电压。换言之,如果有指定微电子电路应该可接受的时钟速度,则个别微电子电路单元可依据展现需要的效能时的最小运作电压而放进电压分类。分类至最低电压分类的单元典型地为最有价值的。

效能分类可包含用于微电子电路的时钟速度分类,其对应的特性化数值针对时钟速度分类指示在给定运作电压下的可接受最大时钟速度。相较于电压分类,这是一种反向分类方法:如果有指定微电子电路应该可接受的特定运作电压,则个别微电子电路单元可依据仍然展现需要的效能时的最大时钟速度而被放进时钟速度分类。分类至最高时钟速度分类的单元典型地为最有价值的。

效能分类可包含用于微电子电路的能量分类,其对应的特性化数值针对能量分类指示用于最小运作电压和最大时钟速度的组合的可接受能量消耗。换言之,如果指定运作电压和时钟速度两者,则个别微电子电路单元可依据在运作参数的指定数值下展现的能量消耗而被放进能量分类。分类至最小能量分类的单元典型地为最有价值的。

图5显示当微电子电路已经被使用以建立较大电子装置时,即使在正常使用期间的运行时间中如何利用适应性微电子电路的DFT能力的比较。如图5的左手部分所例示的,电路可在正常运作模式中使用其时序事件观察能力,以监视观察的时序事件的平均数目。如果出现增加趋势,也就是如果看起来出现更多时序事件,则它可能意指某些环境情况可能具有增加地不利的影响:举例来说,周遭温度可能上升中、或正在进行的太阳风暴可能引发电磁扰动的暂时增加。适应性的电路可藉由降低时钟速度、藉由增加运作电压、或藉由采取一些其它预警措施,而作出反应。在对应的方式中,测试的时序事件中的减少趋势可能允许该电路增加时钟速度、降低运作电压、或以一些其它方式从先前所采取的预警中退出。

在右手侧中,是显示如何采取类似的动作,而不必要藉由观察时序事件、或至少不用在正常运作模式期间观察它们,而是藉由暂时地采用内建的测试模式。微电子电路可利用其内建的DFT能力,以实施运行时间测试(run-time test),其目的与上方所解释的时序事件的观察类似并引致类似的结果。内建的测试模式中的运作不需要花费很短的时间,因此,微电子电路具有内建DFT能力以及以此方式使用的事实可能会被使用者完全忽略。

图5的左方和右方所显示的实施可以结合,举例来说,以致于如果观察到时序事件的数目的改变,则会触发短暂(short excursion)进入内建测试模式,以便更精确地测量实际发生的情况。这样,微电子电路可能达成更精确的结论,并且采用更有效和专注的措施,来满足最初引发观察到的改变的环境或其它条件的改变。

此处所说的观察时序事件也可适用于观察可能由时序事件所引发的错误。

图6例示缓存器电路601的范例,该缓存器电路601具有DFT特性并且可为适应性的,但不是强制的。缓存器电路601的功能性方块为适合的缓存器电路602和监视器电路或时序事件观察阶段603。数据输入604、数据输出605和TEO输出606以与图2中的对应地命名的部件相同的方式运作。作为额外输入,有一个或更多个版本的触发(“时钟”)信号输入和与测试模式的使用有关的一个或更多个控制信号。触发或时钟信号的版本可包含举例来说真实时钟信号和延迟时钟信号,以致于该真实和延迟时钟信号中的升缘之间的时间中的差异定义TEO窗口。“TEO窗口”的概念是指早先已经参考图2而描述过的时间窗口:如果数据输入604处的数字数值在该TEO窗口期间改变,则时序事件观察阶段603会注意到此并且在TEO输出606处产生对应的TEO输出信号。

缓存器电路601的DFT特性包括导引数据输出605和TEO输出606至所谓扫描链的可能性。这种导引在测试模式中发生并且与DFT原理有关,其中,数个电路组件耦接在一起成为链,可从该链收集测试输出数值成为测试输出信号。可能有不同扫描链用来从数据和TEO输出收集测试输出数值,或者可能选择性地导引它们的任何一者至相同的扫描链。

图7例示另一个缓存器电路701的范例,该缓存器电路701具有DFT特性并且为适应性的(但不需要是)。缓存器电路701的功能性方块为适合的缓存器电路702和监视器电路或时序事件观察阶段703。数据输入704、数据输出705和TEO输出706基本上以与图2和6中对应命名的部件相同的方式运作。作为额外输入,有一个或更多个版本的触发(“时钟”)信号输入和与测试模式的使用有关的一个或更多个控制信号。

与图6的差异是在于,缓存器电路701包含脉波(pulsing)或维持TEO输出的数值的可能性。时序事件观察阶段703的输出耦接至可控制缓冲器707,其也接收控制信号的一者(在图7的顶部看到)。响应这种控制信号的数值,可控制缓冲器707不是让来自时序事件观察阶段的各个瞬时TE(时序事件)旗标以由时钟信号所决定的速率通过,就是冻结TEO信号的数值达长于时钟信号中的一个时钟周期的期间。后者可能地致能稍后收集TEO信号的冻结数值,以形成在此文本中早先所描述的该组测试输出信号。让TEO数值以由时钟信号所决定的速率通过是称为脉波(pulsing),而冻结TEO数值达长于一个时钟周期的期间则称为维持。

也有可能选择性地维持TEO输出的数值。上方所提到的控制信号的数值可具有以下效应:如果可控制缓冲器707变高,则只冻结TEO信号的数值。非选择性维持也可能涉及冻结TEO信号的低数值。

图8例示缓存器电路的范例,该缓存器电路用来暂时地储存从微电子电路中的先前电路组件的输出所获得的数字数值。图8的缓存器电路是DFT和适应性的。它包含用来接收数字数值用于暂时储存的数据输入:该数据输入配备有多任务器801,其藉由耦接功能性输入D或测试输入TI进入缓存器电路而响应TE(测试致能)信号。缓存器电路包含数据输出D,用来输出暂时地储存的数字数值。额外地,它包含两个触发事件输入CLK和CLKD,用来接收触发信号。CLKD输入配置成在CLK输入处接收延迟版本的信号。CLK信号中的触发边缘定义可允许时间限制,在该可允许时间限制前,数字数值必需出现在数据输入处,以变成暂时地储存的。在数据输入与数据输出之间的数据行进路径上,有一序列的第一子缓存器级L1和第二子缓存器级L2。这些较佳是脉波致能或位准致能的闩锁器。在下文中,术语闩锁器是用于子缓存器级的缩写。也可使用脉波致能的子缓存器级或位准致能的子缓存器级。

CLKD信号(或实际上:它的反向)行进进入第一闩锁器L1的致能输入。此意指第一闩锁器L1配置成接收与由第二闩锁器L2所接收的触发信号CLK有关而延迟的触发信号。该延迟的长度是触发信号CLK的周期的片段。

该缓存器电路包含时序事件观察逻辑802,其配置成在缓存器电路的上输出处输出TEO信号,以作为数字数值在数据输入处的指示器,该数字数值在以可允许时间限制开始的时间窗口内已经改变且比触发信号CLK的一个周期短。此所谓TEO窗口的长度是CLK信号中的升缘与CLKD信号中的立即接续的升缘之间的差异。由于CLK信号与CLKD信号的反向CLKDn行进进入AND闸803的输入,因此行进进入时序事件观察逻辑802的CP输入的致能信号tep_win_cp仅在该两个接续升缘期间是高的。

可以图8中所显示的那种缓存器电路所实施的测试的范例是TEO固定1故障测试(TEO-stuck-at-one test)。测试的目标是核对微电子电路中是否有任何监视器电路(也就是时序事件观察逻辑)会使它们的TEO输出固定在逻辑数值1。此可藉由启动TE信号并且馈入数字数值没有改变的测试图案,而加以测试。由于如果在数据输入处的数字数值过迟改变则监视器电路的TEO输出应该只会变高,并且由于此种类的测试图案涉及完全没有改变,因此所有TEO输出应该维持低。如果TEO输出的任何一者给出高数值,则它识别出至少一个监视器电路是错误的,并且它的输出是固定在高,也就是固定在逻辑数值“1”。

图8的缓存器电路可适应性响应用于它的运作参数的数值。举例来说,可改变CLK(和CLKD)信号的运作电压及/或时钟以及该CLKD信号中定义窗口的长度的延迟,在该窗口期间,时序事件观察逻辑802对迟来的数据作出反应。

图9例示稍微更精致的缓存器电路,其是适应性和DFT。至第一闩锁器L1的触发信号可为与触发第二闩锁器L2的时钟信号相同的时钟信号CP或其延迟版本的CPD(的反向),视控制触发信号多任务器901的信号TTBEN的数值而定。图8的TE信号现在以类似地工作的SE(扫描致能(Scan Enable))信号取代,其控制数据输入中的多任务器801。图8的TI信号在本处重新命名为SI(扫描输入(Scan Input))。

CP是图9中的正常触发(也就是时钟)信号,CPN是其反向,而CPD是其延迟版本。TTBEN信号选择时序事件观察是否在使用中,因为TTBEN的数值“1”引发第一和第二闩锁器L1和L2被精确地同时地触发,以致于没有作出时间借用。因此,使TTBEN的逻辑变为高,致能缓存器电路的运作的测试,彷佛它没有包括任何时间借用。

TMSE(测试监视器扫描致能(Test Monitor Scan Enable))信号在第二闩锁器L2的输入处控制多任务器902。它的效应是导引来自第一闩锁器L1的输出的中介数据数值q1或来自监视器电路802的输出的TEO信号至第二闩锁器L2。这使得能够仅用一个测试输出布置来实作微电子电路,该测试输出布置配置成受控地收集来自多个电路组件的测试输出数值:视TMSE的数值而定,不是数据输出、就是TEO输出被收集。

可使用TMTEOH(测试模式时序事件观察保持(Test Mode Timing EventObservation Hold))信号来冻结TEO信号的数值达比时钟信号CP中的一个时钟周期还长的期间。此致能的后收集的TEO信号的冻结数值,以形成所需组的测试输出信号。CDN信号是异步重置,其可用来重置第二闩锁器L2的输出。

固定1故障测试在图9中可以与图8中的上方相同方式作出。在图9中,有发现的额外可能性,缓存器电路使其监视器输出固定在高数值。也就是说,如果扫描链的缓存器电路中的所有监视器的TEO输出均只是行进至OR树(tree),则它们的输出在至少一个TEO输出变高的情况下会变高,但没有方式得知哪个会变高。在图9的布置中,设定TMTEOH为高会冻结各个TEO输出信号的数值,并且由于它们是经由多任务器902和第二闩锁器L2而被撷取,并且在具有高数值的一点处(也就是自从在扫描链中的那个缓存器电路)退出(clockedout),可从出来的测试信号而被计数。此也致能决定该问题是否在监视器或在用来结合该监视器的TEO输出的OR树中。

图9的布置也允许实施TEO固定0故障测试(TEO-stuck-at-zero test)。为了此目的,使用TCPDG(测试时钟脉波延迟闸(Test Clock Pulse Delay Gated))。通常,它的数值是零,因此,AND闸903的输出采用CPD信号的数值。使用AND闸903的输出和反向时钟信号CPN作为其输入的NOR闸904产生高脉波在CP信号的各个升缘和CPD脉波的立即地接续高缘之间,因此定义用于监视器电路802的TEO窗口。如果TCPDG信号假定高数值,则AND闸903的输出会保持固定低,而CKP信号主要是CPN信号的反向,也就是等于直接时钟信号CP。此接着意指当TCPDG为高时,由监视器电路802所应用的监视窗口是时钟周期的一半长,也就是与时钟信号CP中的各个高脉波一样长。视测试中所使用的时钟速率而定,此一半的时钟周期可比功能性模式中的时钟周期长。以只有一个位在高数值而所有其余位为低的方式传播测试向量应该现在在扫描链中一次触发各个监视器电路。如果它们的其中一者固定至零,则将在从扫描链所收集的测试输出信号中会注意到对应的异常。

图10例示图9的缓存器电路的变体,这次没有TMTEOH输入信号;如果对应的功能性不视为强制的,则它就不必要。图11例示出在其他方面类似的变体,但至监视器电路的数据输入是来自缓存器电路的功能性数据输入D,以取代如图9和10中的数据输入多任务器的输出。图12例示变体,其中,该第一闩锁器L1和该第二闩锁器L2两者均可以根据TTBEN信号的数值而用CP或CPD信号选择性地提供时钟。额外地在图12中,输出多任务器1201是放置在第二闩锁器L2之后,而不是像先前实施例放在该第二闩锁器L2之前。图13例示变体,其中,出现TMTEOH信号,但数据和TEO输出没有一起被多任务;两者均被导引至它们自己的扫描链。

图14例示变体,其中,没有使用TMTEOH信号,也没有输出多任务器。图15例示变体,其中,以简单方式产生至监视器电路802的时钟脉波信号,使得它只是CP和反向CPD信号的AND结果。图16例示相同,但没有TMTEOH信号,而图17例示变体,其中,使用SE信号以取代TTBEN信号来控制在输入处多任务的时钟信号。图18例示变体,其中,SE信号的此使用是相同,并且额外地,使用该SE信号作为至NAND闸1801的输入,TMSE信号是至NAND闸1801的另一输入。NAND闸1801的输出作为至最终形成CKP信号的逻辑中的AND闸903的一个输入;至该AND闸903的另一输入是CPD信号。

所有图9至18的共有的特征是它们揭露用于侦测微电子电路的缓存器电路中的时序事件的监视器电路。在各个案例中,监视器电路包含触发事件输入,用来接收触发信号,像是时钟信号或脉波式时钟信号。这种触发信号的触发边缘定义可允许时间限制,在可允许时间限制之前,数字数值必需出现在缓存器电路的数据输入处,以变成暂时地储存在该缓存器电路中。触发事件输入在图式中被标注为CP。也在各个案例中,监视器电路包含监视输入,用来于该数字数值出现在该缓存器电路的该数据输入处的同时接收讨论中的该数字数值的监视副本。该监视输入在该图式中被标注为D。

也在各个案例中,该监视器电路包含时序事件观察输出,被标注成TEO。该监视器电路内的时序事件观察逻辑配置成在该TEO输出处输出时序事件观察信号,作为该数字数值在该缓存器电路的该数据输入处已经过迟(too late)改变的指示器。此处,“过迟”的定义是“在从该可允许时间限制开始并且比该触发信号的一个周期短的时间窗口内”。

在各个案例中,该监视器电路包含输出管理单元,其配置成致能收集该时序事件观察信号的数值,用于该监视器电路外部的进一步处理。在各个案例中,该监视器电路也是适应性的,意指它是适应地响应于可用于该监视器电路的运作参数的数值。

图9至18中所显示的实施例在输出管理单元或输出管理功能的实作方式方面彼此之间有些微不同。在该监视器电路中的输入是用于TMTEOH信号的实施例中,该输出管理单元可说是包含用来接收输出冻结命令的控制输入,而该监视器电路可说是配置成藉由保持该时序事件观察信号的目前数值不变而响应接收到的输出冻结命令。在图9至12、17和18中,该输出管理单元包含多任务器,其配置成选择性地导引该时序事件观察信号的数值至该监视器电路外部的扫描链,以取代适合的缓存器电路的数据输出数值。

对于本领域中具有先进技术的已知技术人员而言明显的是,本发明的基本想法可以各种方式实施。本发明及其实施例因此不限定于所描述的范例,而是它们可在权利要求的范畴内变化。

- 可测试性设计的适应性微电子电路的应用

- 微电子导电路径和制作所述微电子导电路径的方法