一种3D NAND存储器件及其制造方法、半导体机台

文献发布时间:2023-06-19 11:32:36

技术领域

本发明涉及半导体技术领域,特别涉及一种3D NAND存储器件及其制造方法、半导体机台。

背景技术

3D NAND存储器的制备工艺中,首先在衬底上形成由氮化硅(SiN)层和氧化硅(SiO

目前常用多晶硅作为沟道层的材料,但是随着堆叠层数的增多,沟道孔的深度不断增大,采用多晶硅作为沟道层的材料时沟道电流越来越小,影响器件的性能。

发明内容

有鉴于此,本发明的目的在于提供一种3D NAND存储器件及其制造方法、半导体机台,以便于在沟道孔中形成高质量的硅锗层。

为实现上述目的,本发明有如下技术方案:

一种3D NAND存储器件的制造方法,包括:

提供衬底,所述衬底上形成有堆叠层,所述堆叠层中形成有沟道孔;

在所述沟道孔中依次形成存储功能层、种子层和沟道层,所述沟道层包括硅锗层。

可选的,所述种子层为硅层。

可选的,在所述沟道孔中形成种子层包括:

在温度范围为300~400℃时,利用二异丙胺硅烷作为气源形成硅层。

可选的,在所述沟道孔中形成沟道层包括:

在温度范围为500~600℃,压力小于1mTorr时,利用硅烷与锗烷作为气源形成硅锗层。

可选的,通过调节所述硅烷和/或所述锗烷的流量调整所述硅锗层中的硅和锗的比例。

可选的,所述存储功能层包括依次层叠的阻挡层、电荷存储层以及隧穿层,所述遂穿层的材料为氧化硅或掺氮氧化硅。

可选的,所述堆叠层包括交替层叠的绝缘层和牺牲层。

一种3D NAND存储器件,包括:

衬底,所述衬底上形成有堆叠层,所述堆叠层中形成有沟道孔;

所述沟道孔中依次形成有存储功能层、种子层和沟道层,所述沟道层包括硅锗层。

可选的,所述种子层为硅层。

可选的,所述存储功能层包括依次层叠的阻挡层、电荷存储层以及隧穿层,所述遂穿层的材料为氧化硅或掺氮氧化硅。

一种半导体机台,用于形成上述所述的存储器件,包括:

反应腔室,所述反应腔室用于形成所述种子层和所述沟道层;

第一输入管道,所述第一输入管道用于向所述反应腔室内通入形成所述种子层的气源;

第二输入管道,所述第二输入管道用于向所述反应腔室内通入形成所述沟道层的气源。

本发明实施例提供的一种3D NAND存储器件的制造方法,包括:提供衬底,衬底上形成有堆叠层,堆叠层中形成有沟道孔;在沟道孔中依次形成存储功能层、种子层和沟道层,沟道层包括硅锗层。这样,在存储功能层上形成种子层,之后在种子层上生长硅锗层,由于种子层为单原子层,从而能够在种子层上外延生长高质量的硅锗层,且由于硅锗层具有较高的载流子迁移率,能够提高3D NAND存储器件的电学性能。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图。

图1示出了一种3D NAND存储器件的结构示意图;

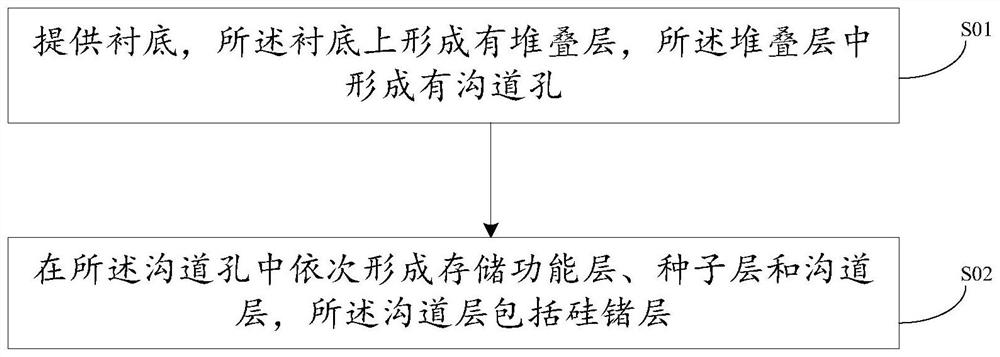

图2示出了根据本发明实施例一种3D NAND存储器件的制造方法的流程示意图;

图3-5示出了根据本发明实施例一种3D NAND存储器件的结构示意图。

具体实施方式

为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图对本发明的具体实施方式做详细的说明。

在下面的描述中阐述了很多具体细节以便于充分理解本发明,但是本发明还可以采用其它不同于在此描述的其它方式来实施,本领域技术人员可以在不违背本发明内涵的情况下做类似推广,因此本发明不受下面公开的具体实施例的限制。

正如背景技术的描述,在3D NAND存储器的制备工艺中,首先在衬底100上形成由氮化硅(SiN)层122和氧化硅(SiO

目前常用多晶硅作为沟道层的材料,但是随着堆叠层数的增多,沟道孔的深度不断增大,采用多晶硅作为沟道层的材料时沟道电流越来越小,影响器件的性能。

本申请人经研究发现,硅锗(Si

为此,本申请实施例提供一种3D NAND存储器件的制造方法,包括:提供衬底,衬底上形成有堆叠层,堆叠层中形成有沟道孔;在沟道孔中依次形成存储功能层、种子层和沟道层,沟道层包括硅锗层。这样,在存储功能层上形成种子层,之后在种子层上生长硅锗层,由于种子层为单原子层,从而能够在种子层上外延生长高质量的硅锗层,且由于硅锗层具有较高的载流子迁移率,能够提高3D NAND存储器件的电学性能。

为了便于理解本申请的技术方案和技术效果,以下将结合附图对具体的实施例进行详细的说明。

参考图2和图3所示,在步骤S01中,提供衬底200,所述衬底200上形成有堆叠层,所述堆叠层中形成有沟道孔224。

在本申请实施例中,衬底200为半导体衬底,例如可以为Si衬底、Ge衬底、SiGe衬底、SOI(绝缘体上硅,Silicon On Insulator)或GOI(绝缘体上锗,Germanium OnInsulator)等。在其他实施例中,半导体衬底还可以为包括其他元素半导体或化合物半导体的衬底,例如GaAs、InP或SiC等,还可以为叠层结构,例如Si/SiGe等,还可以为其他外延结构,例如SGOI(绝缘体上硅锗)等。在本实施例中,所述衬底200为体硅衬底。

堆叠层用于在其中形成垂直于衬底方向的存储单元串,堆叠层可以包括交替层叠的绝缘层221和牺牲层222,堆叠层可以由单个堆叠(Single deck)来形成,也可以由多个子堆叠(Multiple deck)依次层叠形成,堆叠层中的绝缘层221或牺牲层222的层数越多,形成的存储单元串中包括的存储单元就越多,器件的集成度就越高。牺牲层222用于为后续形成的栅极层占据位置,绝缘层221位于相邻的牺牲层222之间,牺牲层222与衬底200之间以及顶层的牺牲层222上,在具体的实施例中,绝缘层221可以为氧化硅,牺牲层222可以为氮化硅。

本申请实施例中,在堆叠层中形成有贯穿堆叠层至衬底200中的沟道孔224,参考图3所示,在沟道孔224的底部可以形成有外延结构210,参考图4所示,外延结构210可以作为下选择管器件的沟道。该外延结构210可以通过在衬底200上外延生长半导体材料形成,例如单晶硅。形成沟道孔224的工艺可以为,在堆叠层上形成硬掩模层,在硬掩模层上方旋涂光刻胶层,通过曝光显影等工艺形成图案化的光刻胶层,该光刻胶层固化的图案可以由3D NAND存储器制造工艺中用于形成沟道孔的掩模版确定。而后,利用刻蚀工艺将光刻胶图案转移至硬掩模层上,以硬掩模层为遮蔽刻蚀堆叠层中的绝缘层221和牺牲层222。例如采用干法刻蚀堆叠层,以形成暴露衬底200的沟道孔224,而后可以去除硬掩模层和光刻胶层。

在步骤S02中,在所述沟道孔224中依次形成存储功能层230、种子层234和沟道层235,所述沟道层235包括硅锗层,参考图5所示。

本申请实施例中,在沟道孔224中形成存储功能层230,参考图4所示,存储功能层230包括在沟道孔224的侧壁和底部依次层叠的阻挡层231、电荷存储层232以及隧穿层(Tunneling layer)233。阻挡层231、电荷存储层232以及隧穿层233可以为ONO叠层,ONO(Oxide-Nitride-Oxide)叠层即氧化物、氮化物和氧化物的叠层,具体的,遂穿层233的材料可以为氧化硅或掺氮氧化硅。随后,刻蚀沟道孔224底部的阻挡层231、电荷存储层232以及隧穿层233,以打开外延结构210。在存储功能层230的侧壁和底部以及暴露的外延结构210表面生长种子层235,参考图5所示,种子层235例如可以为硅层,硅层为单原子层,从而有利于后续在硅层上生长高质量的硅锗层。本实施例中,可以在温度范围为300~400℃时,利用二异丙胺硅烷(Di-iso-propylaminosilane,H

而后,在种子层234表面形成沟道层235,沟道层235可以为硅锗层,硅锗为半导体合金材料,且硅锗具有较高的载流子迁移率从而能够提高沟道电流,进而提高器件的电学性能。由于硅层为单原子层且利用外延生长技术在硅层表面生长硅锗层,从而能够在硅层表面有序生长硅锗层以获得高质量的硅锗层,进而提高沟道电流。本实施例中,可以在温度范围为500~600℃,压力小于1mTorr下,利用硅烷与锗烷作为气源,采用超高真空化学气相沉积(ultrahigh vacuum chemical vapor deposition,UHVCVD)工艺形成硅锗层。硅烷例如可以为甲硅烷(SiH

本实施例中,在堆叠层中形成栅线缝隙,例如可以采用反应离子刻蚀方法刻蚀堆叠层,从而在堆叠层中形成暴露衬底的栅线缝隙。在形成栅线缝隙之后,通过栅线缝隙将堆叠层中的牺牲层222去除,可以选择对牺牲层222和绝缘层221具有高选择比的酸液腐蚀牺牲层222,在去除牺牲层222之后,对原来牺牲层的区域进行金属填充形成栅极层,填充的金属可以为钨,也可以是其他可以作为栅极的金属。堆叠层中的栅极层可以包括存储单元的栅极层以及选择栅的栅极层,选择栅可以包括源极选择栅(Source Selection Gate,SSG)和/或漏极选择栅(Drain Selection Gate,DSG)。在具体的实施例中,可以在金属填充之前,沉积高K栅介质层材料,从而在绝缘层221和栅极层之间形成高k栅介质层。

之后,还可以完成器件的其他加工工艺,例如共源极工艺以及栅线缝隙填充工艺等。

以上对本申请实施例提供的一种3D NAND存储器件的制造方法进行了详细的描述,本申请实施例还提供一种3D NAND存储器件,包括:

衬底200,所述衬底200上形成有堆叠层,所述堆叠层中形成有沟道孔224;

所述沟道孔224中依次形成有存储功能层230、种子层234和沟道层235,所述沟道层235为硅锗层。

本申请实施例中,在衬底200上形成堆叠层,堆叠层可以包括交替层叠的绝缘层221和栅极层,绝缘层221位于相邻的栅极层之间、栅极层和衬底200之间,以进行电学隔离。堆叠层中形成有沟道孔224,在沟道孔224中依次形成存储功能层230、种子层234和沟道层235,存储功能层230包括在沟道孔224的侧壁和底部依次层叠的阻挡层231、电荷存储层232以及隧穿层233。阻挡层231、电荷存储层232以及隧穿层233可以为ONO叠层,ONO(Oxide-Nitride-Oxide)叠层即氧化物、氮化物和氧化物的叠层。具体的,遂穿层的材料为氧化硅或掺氮氧化硅。本实施例中,种子层234为单原子硅层。沟道层235为硅锗层,由于硅锗具有较高的载流子迁移率,硅锗层作为沟道层时能够提高沟道电流,进而提高器件的电学性能。

本申请实施例还提供一种半导体机台,用于形成上述3D NAND存储器件,包括:

反应腔室,所述反应腔室用于形成所述种子层和所述沟道层;

第一输入管道,所述第一输入管道用于向所述反应腔室通入形成所述种子层的气源;

第二输入管道,所述第二输入管道用于向所述反应腔室通入形成所述沟道层的气源。

在具体的应用中,将器件置于反应腔室内,打开第一输入管道,关闭第二输入管道,利用第一输入管道向反应腔室内通入形成种子层的气源,例如H

本说明书中的各个实施例均采用递进的方式描述,各个实施例之间相同相似的部分互相参见即可,每个实施例重点说明的都是与其它实施例的不同之处。尤其,对于器件实施例而言,由于其基本相似于方法实施例,所以描述得比较简单,相关之处参见方法实施例的部分说明即可。

以上所述仅是本发明的优选实施方式,虽然本发明已以较佳实施例披露如上,然而并非用以限定本发明。任何熟悉本领域的技术人员,在不脱离本发明技术方案范围情况下,都可利用上述揭示的方法和技术内容对本发明技术方案做出许多可能的变动和修饰,或修改为等同变化的等效实施例。因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所做的任何的简单修改、等同变化及修饰,均仍属于本发明技术方案保护的范围内。

- 一种3D NAND存储器件及其制造方法、半导体机台

- 台阶结构的制作方法、3D NAND存储器件的制造方法及3D NAND存储器件