一种基于FPGA的总线复用型FLASH读写系统

文献发布时间:2023-06-19 11:32:36

技术领域

本发明涉及一种基于FPGA的总线复用型FLASH读写系统,属于数据读写控制领域。

背景技术

MICRO公司的MT29F系列FLASH采用数据总线与地址总线复用设计,无法用DSP的EMIF总线或其他通信总线控制,需要DSP软件控制管脚实现读写时序,且单次仅读写一个字节,读写效率低,占用机时长。

发明内容

本发明解决的技术问题是:针对目前现有技术中,无法用DSP的EMIF总线或其他通信总线控制,需要DSP软件控制管脚实现读写时序的问题,提出了一种基于FPGA的总线复用型FLASH读写系统。

本发明解决上述技术问题是通过如下技术方案予以实现的:

一种基于FPGA的总线复用型FLASH读写系统,包括FPGA读写模块、DSP模块、FLASH模块,FPGA读写模块管脚分别与DSP模块的EMIF总线、FLASH模块连接,FPGA读写模块接收DSP模块发送的指令并转换为FLASH模块输入信号,FLASH模块根据输入信号进行存储并供DSP模块读取。

所述DSP模块包含EMIF总线,地址总线大于4位,数据总线为32位;

所述FPGA读写模块点号大于100,内置的逻辑门电路大于1000门;

所述FLASH模块为满足MT29F时序要求的型号。

所述FPGA读写模块能够自动识别读指令、写指令,当DSP模块输入写指令时,具体流程如下:

(1)接收DSP模块写入的写指令;

(2)cs端口清零;

(3)将写指令中16~23bit数据输入数据总线,将27bit数据写入CLE端口,将26bit数据写入ALE端口,将24bit数据写入we端口线;

(4)于10ns后拉高we端口线,并于下一个10ns后清零CLE端口、ALE端口及数据总线;

(5)将写指令的7~0bit数据输入数据总线,将11bit数据写入CLE端口,将10bit数据写入ALE端口,将8bit数据写入we端口线;

(6)于10ns后拉高we端口线,并于下一个10ns后清零CLE端口、ALE端口及数据总线;

(7)拉高cs端口;

(8)终止流程。

当DSP模块输入读指令时,具体流程如下:

(1)接收DSP模块写入的读指令,并确定读指令操作数量;

(2)判断当前FPGA读写模块的读取计数器数字是否不小于读指令操作数量,若不小于,则进入步骤(16),若小于,则将FPGA读写模块的读取计数器清零;

(3)将re端口计数清零;

(4)拉低cs端口和re端口;

(5)10ns后将re端口置为1;

(6)读取FLASH模块中数据总线内的数据,存入8位寄存器reg1中,使读取计数器加1;

(7)10ns后将re端口拉低;

(8)10ns后将re端口置为1,读取FLASH模块中数据总线内的数据,存入8位寄存器reg2中,使读取计数器加1;

(9)10ns后将re端口拉低;

(10)10ns后将re端口置为1,读取FLASH模块中数据总线内的数据,存入8位寄存器reg3中,使读取计数器加1;

(11)10ns后将re端口拉低;

(12)10ns后将re端口置为1,读取FLASH模块中数据总线内的数据,存入8位寄存器reg4中,使读取计数器加1;

(13)cs端口拉高;

(14)将寄存器reg1、reg2、reg3、reg4中的数据同时写入FPGA读写模块的读寄存器;

(15)通过DSP模块读取读寄存器的数据,并返回步骤(2);

(16)终止流程。

根据FPGA读写模块的输入时钟周期调整we端口线、re端口信号低电平时间长度不小于10ns,写入数据至ALE端口、CLE端口的有效时间不低于20ns。

本发明与现有技术相比的优点在于:

本发明提供的一种基于FPGA的总线复用型FLASH读写系统,通过单次DSP写操作,可将2字节有效数据写入FLASH,同时可通过单次DSP读操作,可读取FLASH中4字节数据,针对现有技术关于MT29F系列FLASH读取设计的缺陷,提出了新的读写系统设计及流程设计,解决了无法用DSP的EMIF总线或其他通信总线控制,需要DSP软件控制管脚实现读写时序的问题,大大改进读写效率。

附图说明

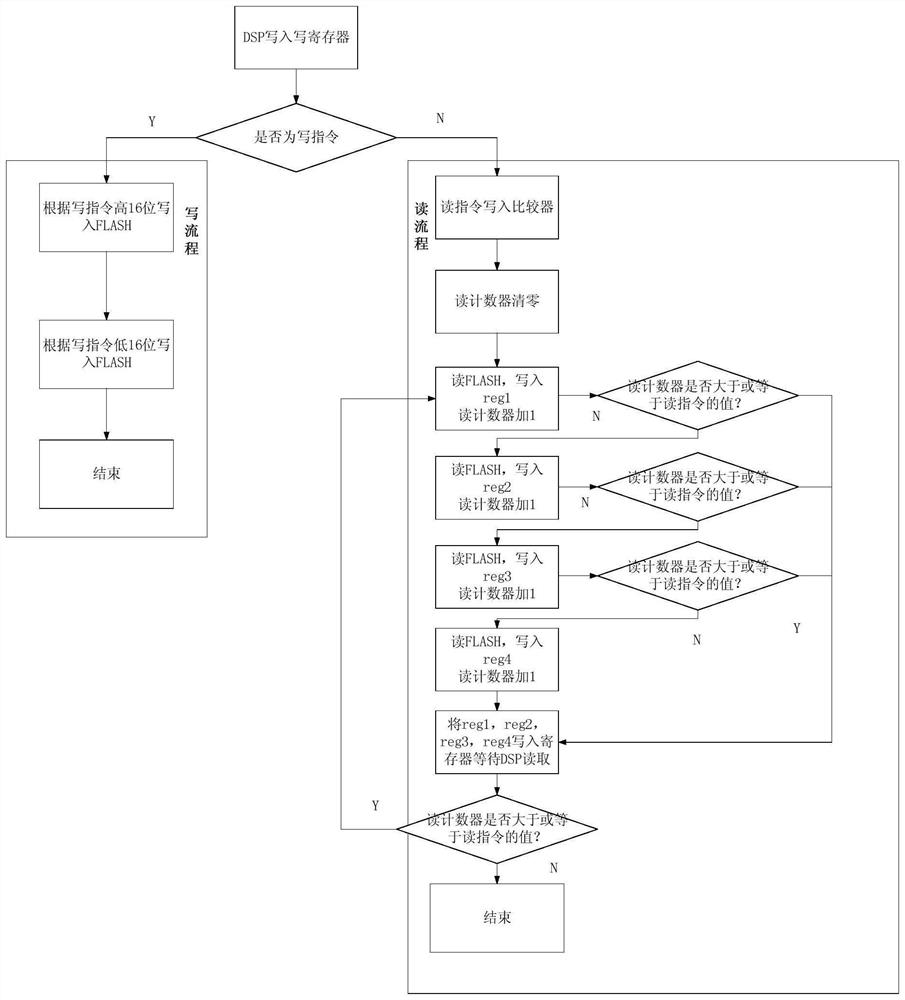

图1为发明提供的FLASH读写系统读写流程示意图;

图2为发明提供的FLASH读写系统结构示意图;

具体实施方式

一种基于FPGA的总线复用型FLASH读写系统,针对现有技术中,MT29F系列FLASH采用数据总线与地址总线复用设计,无法用DSP的EMIF总线或其他通信总线控制,需要DSP软件控制管脚实现读写时序的问题,通过包括FPGA读写模块、DSP模块、FLASH模块的读写系统结构,实现改进读写效率的目的,整体读写系统结构具体为:

包括FPGA读写模块、DSP模块、FLASH模块,FPGA读写模块管脚分别与DSP模块的EMIF总线、FLASH模块连接,FPGA读写模块接收DSP模块发送的指令并转换为FLASH模块输入信号,FLASH模块根据输入信号进行存储并供DSP模块读取,其中:

DSP模块包含EMIF总线,地址总线大于4位,数据总线为32位;FPGA读写模块点号大于100,内置的逻辑门电路大于1000门;FLASH模块为满足MT29F时序要求的型号。

读写系统包括两种工作模式,分别为读模式、写模式,不同工作模式写整体工作流程不同,具体为:

当DSP模块输入写指令时,具体流程如下:

(1)接收DSP模块写入的写指令;

(2)cs端口清零;

(3)将写指令中16~23bit数据输入数据总线,将27bit数据写入CLE端口,将26bit数据写入ALE端口,将24bit数据写入we端口线;

(4)于10ns后拉高we端口线,并于下一个10ns后清零CLE端口、ALE端口及数据总线;

(5)将写指令的7~0bit数据输入数据总线,将11bit数据写入CLE端口,将10bit数据写入ALE端口,将8bit数据写入we端口线;

(6)于10ns后拉高we端口线,并于下一个10ns后清零CLE端口、ALE端口及数据总线;

(7)拉高cs端口;

(8)终止流程。

当DSP模块输入读指令时,具体流程如下:

(1)接收DSP模块写入的读指令,并确定读指令操作数量;

(2)判断当前FPGA读写模块的读取计数器数字是否不小于读指令操作数量,若不小于,则进入步骤(16),若小于,则将FPGA读写模块的读取计数器清零;

(3)将re端口计数清零;

(4)拉低cs端口和re端口;

(5)10ns后将re端口置为1;

(6)读取FLASH模块中数据总线内的数据,存入8位寄存器reg1中,使读取计数器加1;

(7)10ns后将re端口拉低;

(8)10ns后将re端口置为1,读取FLASH模块中数据总线内的数据,存入8位寄存器reg2中,使读取计数器加1;

(9)10ns后将re端口拉低;

(10)10ns后将re端口置为1,读取FLASH模块中数据总线内的数据,存入8位寄存器reg3中,使读取计数器加1;

(11)10ns后将re端口拉低;

(12)10ns后将re端口置为1,读取FLASH模块中数据总线内的数据,存入8位寄存器reg4中,使读取计数器加1;

(13)cs端口拉高;

(14)将寄存器reg1、reg2、reg3、reg4中的数据同时写入FPGA读写模块的读寄存器;

(15)通过DSP模块读取读寄存器的数据,并返回步骤(2);

(16)终止流程。

根据FPGA读写模块的输入时钟周期调整we端口线、re端口信号低电平时间长度不小于10ns,写入数据至ALE端口、CLE端口的有效时间不低于20ns。

下面结合具体实施例进行进一步说明:

在本实施例中,读写系统整体结构组成示意图如图2所示,图2所示连接的FPGA中,DSP向FLASH模块中写入读操作或写操作,该模块将信息写入FLASH或从FLASH中读取。

首先,DSP向FLASH中写入指令。当该指令bit31为1时为写指令,读写模块根据指令向FLASH中写入2字节;bit31为0时为读指令,读写模块将读取该数量的数据供DSP读取,整体流程如图1所示;

当读写模块识别为写指令时,该模块将写指令(32位)的16~23bit写入数据总线,27bit写入CLE,26bit写入ALE,24bit写入we线。经过10ns后we线拉高,再经过10ns后CLE和ALE,数据总线清零;该模块将寄存器的7~0比特放入数据总线,11bit写入CLE,10bit写入ALE,8bit写入we线。经过10ns后we线拉高,再经过10ns后CLE和ALE,数据总线清零,完成写操作。

当读写模块识别为读指令时,读写模块的读计数器清零,re线设置为低电平,10ns后re线设置为高电平,reg1寄存器读取FLASH数据总线数据并锁存;10ns后re线设置为低电平,再过10ns后re线设置为高电平,reg2寄存器读取FLASH数据总线数据并锁存;10ns后re线设置为低电平,再过10ns后re线设置为高电平,reg3寄存器读取FLASH数据总线数据并锁存;10ns后re线设置为低电平,再过10ns后re线设置为高电平,reg4寄存器读取FLASH数据总线数据并锁存;此时读写模块将暂停读取FLASH,并将reg1,reg2,reg3,reg4内容拼接为一个32位寄存器;当DSP读取该寄存器后,读写模块将继续读取FLASH中数据,直至读计数器大于或等于读指令的值。

本发明应用于带数据存储功能的卫星导航接收机,该模块可降低大量DSP读写机时,使DSP在正常运行卫星定位的同时进行数据读写。

以上所述,仅为本发明最佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。

本发明未详细说明部分属本领域技术人员公知常识。

- 一种基于FPGA的总线复用型FLASH读写系统

- 基于FPGA的多MCU读写NANDFlash的实现方法