一种精确获得PCB走线上下层介电常数差异的仿真方法

文献发布时间:2023-06-19 11:35:49

技术领域

本发明涉及电路板设计技术领域,尤其涉及一种精确获得PCB走线上下层介电常数差异的仿真方法。

背景技术

印制电路板(Printed Circuit Board,PCB板)又称印刷电路板、印刷线路板,是电子产品物理支撑以及信号传输的重要组成部分,多层板由很多个不同的芯板(简称core)和半固化片(简称PP片)压合而成。

由于芯板是在压合之前已经固化的结构,因此它的介电常数相对比较固定,但是半固化片在压合前是没固化,在压合过程中高温融化才会慢慢固化,因此压合前后半固化片的介电常数会有不小的差异。PCB设计在内层进行走线的时候,由于理论上上下层的介电常数是相同的,因此同方向的走线是不存在远端信号串扰的,但是实际上由于我们选用不同型号的芯板和半固化片,因此走线上下层介电常数还是会存在差异,就会导致远端信号串扰的产生。

因此,如何获得半固化片压合后的介电常数,进而利用走线上下层的介电常数差异优化PCB走线设计,上述问题有待解决。

发明内容

为了克服现有的技术的不足,本发明提供一种精确获得PCB走线上下层介电常数差异的仿真方法。

本发明技术方案如下所述:

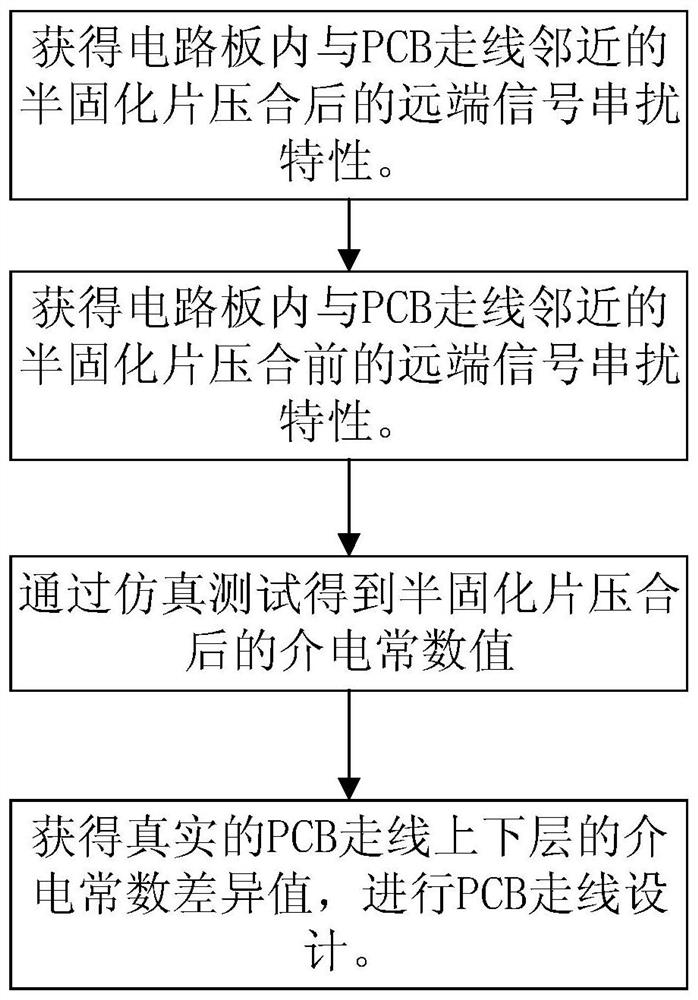

一种精确获得PCB走线上下层介电常数差异的仿真方法,其特征在于,包括以下步骤:

步骤1:获得电路板内与PCB走线邻近的半固化片压合后的远端信号串扰特性;

步骤2:获得电路板内与PCB走线邻近的半固化片压合前的远端信号串扰特性;

步骤3:在仿真软件中设置半固化片介电常数扫描范围,对半固化片压合前的介电常数按照设定值逐步扫描,直至仿真远端信号串扰结果与实际远端信号串扰测试结果拟合上,停止扫描,确定该值为半固化片压合后的介电常数;

步骤4:获得真实的PCB走线上下层的介电常数差异值,依据该差异值进行PCB走线设计。

根据上述方案的本发明,其特征在于,在步骤1中,利用频谱分析仪对已有电路板的叠层及走线数据进行测试,得到电路板内与PCB走线邻近的半固化片压合后的远端信号串扰特性。

根据上述方案的本发明,其特征在于,在步骤2中,在仿真软件中建立叠层模型和走线模型,在叠层模型中输入电路板的叠层参数,在走线模型中输入走线层的走线参数,然后进行仿真测试,得到电路板内与PCB走线邻近的半固化片压合前的远端信号串扰特性。

根据上述方案的本发明,其特征在于,仿真软件为ADS仿真软件。

根据上述方案的本发明,其特征在于,在步骤2中,输入的叠层参数包含与PCB走线邻近的半固化片介电常数、与PCB走线邻近的芯板介电常数、走线层距离上参考层的高度及走线层距离下参考层的高度。

根据上述方案的本发明,其特征在于,在步骤2中,输入的走线参数包含走线的宽度、走线的中心间距及走线的长度。

根据上述方案的本发明,其特征在于,在进行步骤2之前,还包括查表获得半固化片压合前的介电常数和芯板的介电常数的步骤。

根据上述方案的本发明,其有益效果在于,通过本发明的仿真方法,获得半固化片压合后的介电常数值,在进行PCB走线设计时,能够选择与芯板介电常数更接近的半固化片,减小半固化片和芯板之间的介电常数差异,进一步保证做出来的差分线具有更优的远端信号串扰特性。通过仿真方法获得半固化片压合后的介电常数与芯板的介电常数的差异,在PCB内层进行高速设计时,对于同组信号需要拉开多大的走线间距来保证一定的串扰裕量提供了更好的数据。

附图说明

为了更清楚地说明本发明实施例中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

图1为本发明的流程图;

图2为本发明的一个实施例中电路板的叠层结构;

图3为本发明的半固化片压合后的远端信号串扰测试结果示意图;

图4为本发明的仿真远端信号串扰结果和实际远端信号串扰测试结果拟合示意图一;

图5为发明的仿真软件扫描模型中扫描范围设置界面示意图;

图6为发明的仿真软件扫描模型中扫描获得的最优值界面示意图;

图7为本发明的仿真远端信号串扰结果和实际远端信号串扰测试结果拟合示意图二;

图8为本发明的不同介电常数差异远端信号串扰结果拟合示意图。

具体实施方式

下面结合附图以及实施方式对本发明进行进一步的描述:

如图2所示,本发明提供一个叠层为8层的电路板,8层板由芯板和半固化片压合而成,各层半固化片的型号相同,选用型号1078(RC70%);芯板的型号不同,选用型号1078(RC59%)和型号2116(RC55%)两种。

本实施例在第五层即L5中设计两根单端走线,走线的线宽为4.5mil,走线的线间距为4mil,走线的长度为5000mil。而第五层的上参考层为型号2116(RC55%)芯板,查表获得该芯板的介电常数为3.63;下参考层为型号1078(RC70%)半固化片,查表获得该半固化片的介电常数为3.18。为了获得PCB走线上下层介电常数的差异,进行仿真测试,仿真方法包括以下步骤:

如图1、图3所示,步骤1:利用频谱分析仪对8层板的叠层及走线数据进行测试,得到与PCB走线邻近的半固化片压合后的远端信号串扰特性,即介质损耗与频率的实际测试结果。

如图4所示,步骤2:在ADS仿真软件中建立叠层模型和走线模型,在叠层模型中输入8层板的叠层参数,包括,与PCB走线邻近的芯板介电常数,即L5层的上参考层的介电常数为3.63、与PCB走线邻近的半固化片介电常数,即L5层的下参考层的介电常数为3.18、L5层走线距离上参考层的高度为7.2mil、L5层走线距离下参考层的高度为29.5mil;在走线模型中输入走线层的走线参数,包括,走线的宽度为4.5mil、走线的中心间距为4mil、走线的长度为5000mil,然后进行仿真,得到与PCB走线邻近的半固化片压合前的远端信号串扰特性,即介质损耗与频率的仿真结果,发现仿真结果和测试结果拟合不上。

步骤3:在ADS仿真软件中设置半固化片介电常数扫描范围,对与PCB走线邻近的半固化片压合前介电常数进行扫描,按照设定值进行逐步扫描,进行仿真,直至仿真远端信号串扰结果与实际远端信号串扰测试结果拟合上,停止扫描,获得半固化片压合后的介电常数值。

如图5至图7所示,在本发明中,对L5层的下参考层半固化片介电常数进行扫描,此时该半固化片介电常数是压合前的值为3.18,设置一个扫描范围,最小值设置为3,最大值设置为3.5,为了获得更加精确的半固化片压合后的介电常数,扫描设定值0.02进行逐步扫描,进行仿真,直至仿真远端信号串扰结果和实际远端信号串扰测试结果拟合上,停止扫描,获得半固化片介电常数值为3.32,该值为半固化片压合后的介电常数。

在步骤3中,仿真扫描范围的获取:由于半固化片是由玻璃布和树脂两部分结合而成,而玻璃布压合前后相对稳定,反而是树脂在压合时会融化导致流胶,因此才影响了最终半固化片压合后的介电常数,根据树脂本身的介电常数在2.5到3左右,流胶会使得压合后的半固化片介电常数变高,结合流胶有一定的比例后,就能得到扫描范围。

在步骤3中,获得半固化片压合后的介电常数后,在制造电路板时,可以选择与芯板介电常数更接近的半固化片,能够保证做出来的差分线具有更好的远端信号串扰特性。

步骤4:获得真实的PCB走线上下层的介电常数差异值,依据该差异值进行PCB走线设计。

经过本发明仿真方法,发现半固化片的介电常数经压合后发生变化,由压合前的3.18变成压合后的3.32。计算半固化片压合后的介电常数与芯板的介电常数差异,可以依据差异多少来决定PCB走线间的间距。

在一个实施例中,经仿真,若半固化片压合后的介电常数与芯板的介电常数差异达到0.4,PCB走线设计需拉开3倍线宽间距,得到的远端信号串扰特性如图8中虚线图像。经仿真,若半固化片压合后的介电常数与芯板的介电常数差异达到0.2,PCB走线设计需拉开2倍线宽间距,得到的远端信号串扰特性如图8中实线图像。将两者远端信号串扰特性进行对比,结果表明介电常数差异小的结果也基本和介电常数差异大的结果接近,而在PCB设计时,进行2倍间距的走线布线就会节省很多空间,在PCB设计密度大的时候很有优势。

通过本发明的仿真方法,精确得到半固化片压合后的介电常数,并利用半固化片压合后的介电常数与芯板介电常数的差异,优化PCB走线设计,具有如下技术效果:

(1)在PCB设计时,能够选择与芯板介电常数更接近的半固化片,减小半固化片和芯板之间的介电常数差异,进一步保证做出来的差分线具有更优的远端信号串扰特性。

(2)精确获得半固化片压合后的介电常数与芯板的介电常数的差异,在PCB内层进行高速设计时,对于同组信号需要拉开多大的走线间距来保证一定的串扰裕量提供了更好的数据。

应当理解的是,对本领域普通技术人员来说,可以根据上述说明加以改进或变换,而所有这些改进和变换都应属于本发明所附权利要求的保护范围。

上面结合附图对本发明专利进行了示例性的描述,显然本发明专利的实现并不受上述方式的限制,只要采用了本发明专利的方法构思和技术方案进行的各种改进,或未经改进将本发明专利的构思和技术方案直接应用于其它场合的,均在本发明的保护范围内。

- 一种精确获得PCB走线上下层介电常数差异的仿真方法

- 片上多核处理器时钟精确并行仿真系统及仿真方法