集成电路、光电侦测器以及形成集成电路的方法

文献发布时间:2023-06-19 11:39:06

技术领域

本揭示案是关于一种集成电路、一种光电侦测器以及形成集成电路的方法。

背景技术

本揭示案是关于集成电路光子元件的领域。本揭示案特定言之是关于集成电路内的光电侦测器。许多光子集成电路包括光电侦测器。光电侦测器侦测光并产生指示此光的电信号。若光电侦测器未吸收入射光,则即使光入射在光电侦测器上,光电侦测器将亦不会产生电信号。此表示光电侦测器缺乏灵敏度。

发明内容

本揭示案提供了一种集成电路,包含半导体基板、环形沟槽、多个介电鳍片和多个光敏鳍片。环形沟槽在半导体基板中。多个介电鳍片在环形沟槽中。多个光敏鳍片定位在环形沟槽中,每一光敏鳍片在两个相邻的介电鳍片之间,其中多个介电鳍片及多个光敏鳍片配置作为圆形光栅,圆形光栅配置用以引导入射光围绕环形沟槽。

本揭示案提供了一种光电侦测器,包含半导体基板和圆形光栅。圆形光栅形成在半导体基板中。圆形光栅包括多个介电鳍片和多个光敏鳍片。每一光敏鳍片定位在相邻的多个介电鳍片之间。

本揭示案提供了一种形成集成电路的方法,包含以下操作。在半导体基板中形成环形沟槽。在环形沟槽中形成多个介电鳍片。在环形沟槽中形成多个光敏鳍片,每一光敏鳍片定位在相邻的多个介电鳍片之间。

附图说明

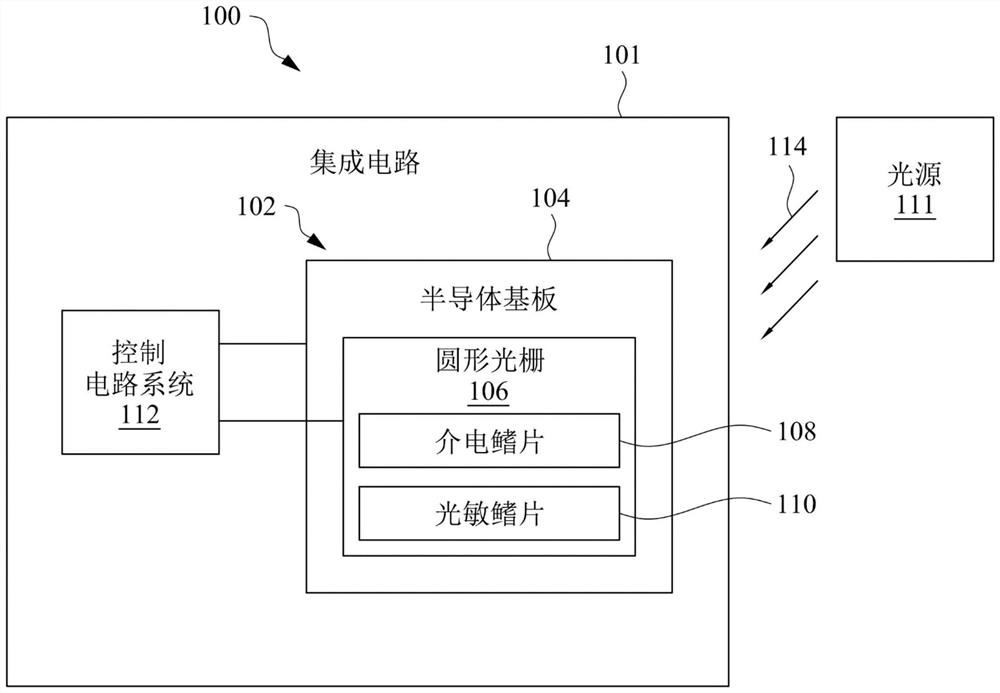

图1为根据一个实施例的集成电路的方块图;

图2为根据一个实施例的处在制造的中间阶段的集成电路的横截面图;

图3A为根据一个实施例的处在制造的中间阶段的集成电路的横截面图;

图3B为根据一个实施例的图3A的集成电路的俯视图;

图4为根据一个实施例的处在制造的中间阶段的集成电路的横截面图;

图5A为根据一个实施例的处在制造的中间阶段的集成电路的横截面图;

图5B为根据一个实施例的图5A的集成电路的俯视图;

图5C为根据一个实施例的图5B的集成电路的一部分沿横截线5C的横截面图;

图6A为根据一个实施例的处在制造的中间阶段的集成电路的横截面图;

图6B为根据一个实施例的图6A的集成电路的俯视图;

图6C为根据一个实施例的图6B的集成电路的一部分沿横截线6C的横截面图;

图7为根据一个实施例的处在制造的中间阶段的集成电路的横截面图;

图8A为根据一个实施例的处在制造的中间阶段的集成电路的横截面图;

图8B为根据一个实施例的图8A的集成电路的俯视图;

图9为根据一个实施例的集成电路的横截面图;

图10为根据一个实施例的用于形成集成电路的方法的流程图。

【符号说明】

100:光子系统

101:集成电路

102:光电侦测器

104:半导体基板

106:圆形光栅

108:介电鳍片

110:光敏鳍片

111:光源

112:控制电路系统

114:光

118:介电材料层

120:环形沟槽

122:底表面

124:外侧壁

125:内侧壁

127:介电材料层

130:侧壁介电涂层

131:缝隙

133:介电材料层

135:介电堆叠

136:电极

140:开口

141:晶体管

142:金属互连件

144:连接衬垫

1000:方法

具体实施方式

在以下描述中,描述了集成电路内的各种层及结构的许多厚度及材料。对于各种实施例而言,借助于实例给出特定尺寸及材料。熟悉此项技术者将认识到,根据本揭示案,可在不脱离本揭示案的范畴的情况下在许多情形下使用其他尺寸及材料。

以下揭示内容提供用于实施所描述标的的不同特征的许多不同实施例或实例。以下描述部件及布置的特定实例以简化本描述。当然,此些仅为实例,且并不意欲为限制性的。举例而言,在如下描述中第一特征在第二特征之上或在第二特征上形成可包括其中第一特征与第二特征形成为直接接触的实施例,且亦可包括其中额外特征可在第一特征与第二特征之间形成而使得第一特征与第二特征可不直接接触的实施例。另外,本揭示案可在各种实例中重复元件符号及/或字母。此重复是出于简化及清楚目的,且其自身并不表示所论述的各种实施例及/或配置之间的关系。

另外,为了描述简单,可在本文中使用诸如“在…下面”、“下方”、“下部”、“上方”、“上部”及其类似术语的空间相对术语,以描述如诸图中所绘示的一个元件或特征与另一(多个)元件或特征的关系。除了诸图中所描绘的定向以外,此些空间相对术语意欲涵盖元件在使用中或操作中的不同定向。装置可以其他方式定向(旋转90度或以其他定向),且可同样相应地解释本文中所使用的空间相对描述词。

在以下描述中,为了提供对本揭示案的各种实施例的透彻理解,阐述某些特定细节。然而,熟悉此项技术者将理解,本揭示案可在无此些特定细节的情况下实践。在其他情况下,并未详细描述与电子部件及制造技术相关联的熟知结构,以免不必要地混淆本揭示案的实施例的描述。

除非上下文另外要求,否则贯穿本说明书及权利要求书,词语“包括(comprise)”及其变体(诸如,“包括(comprises)”及“包括(comprising)”)应以开放性、包括性的意义来解释,亦即,“包括但不限于”。

诸如第一、第二及第三的序数的使用未必暗示次序的有序含义,而仅可在动作或结构的多个个例之间进行区分。

贯穿本说明书对“一个实施例”或“实施例”的引用意谓结合实施例描述的特定特征、结构或特性被包括在至少一个实施例中。因此,贯穿本说明书在各处出现的短语“在一个实施例中”或“在实施例中”未必皆指同一实施例。另外,可在一或更多个实施例中以任何适当方式组合特定特征、结构或特性。

如本说明书及随附权利要求书中所使用,除非内容另外明确指出,否则单数形式“一”及“该”包括复数对象。亦应注意,除非内容另外明确指出,否则术语“或”在其包括“及/或”的含义上使用。

图1为根据一个实施例的光子系统的方块图。光子系统100包括集成电路101及光源111。光源111输出光114。集成电路101侦测光114并基于光114产生信号。

在一个实施例中,集成电路101包括光电侦测器102及控制电路系统112。光电侦测器102包括半导体基板104。在此实施例中,在半导体基板104中形成圆形光栅106。圆形光栅106包括介电鳍片108及光敏鳍片110。

集成电路101可包括未在图1中详细绘示的各种层及结构。举例而言,集成电路101可包括各种半导体材料层、各种介电材料层以及各种金属互连结构。集成电路101可包括以复杂布置耦合在一起的晶体管。

集成电路101的光电侦测器102配置用以侦测入射在光电侦测器102上的光114。举例而言,光114可经由集成电路101的各种透明材料层入射在光电侦测器102上。光电侦测器102侦测光114。

控制电路系统112耦合至光电侦测器102。控制电路系统112可接收来自光电侦测器102的信号,包括响应于侦测光而产生的电信号。控制电路系统112可处理电信号,并可输出指示由光电侦测器102所侦测的光114的一或更多个参数的输出数据或其他信号。

在一个实施例中,控制电路系统112包括形成在集成电路101中的多个晶体管。晶体管可参与操作光电侦测器102并处理自光电侦测器102接收的信号。晶体管亦可参与和集成电路101的功能有关的其他处理,包括自记忆体读取数据,将数据写入记忆体,处理数据,输出数据以及控制通讯。

在一个实施例中,控制电路系统112可将电压施加至光电侦测器102。控制电路系统112可将光电侦测器偏置,以确保光电侦测器102所接收的光将导致电信号的产生,此些电信号可由控制电路系统112读取。因此,控制电路系统112可通过金属互连接线、金属插塞及导电接触件(可通过此些将电压施加至光电侦测器102并可自光电侦测器102接收信号)耦合至光电侦测器102。

在一个实施例中,光电侦测器102通过吸收光114来工作。更特定而言,光114由可被光电侦测器102吸收的光子构成。当光电侦测器102吸收光子时,电信号响应于光子的吸收而产生。因此,由光电侦测器102响应于吸收光子而产生的电信号来指示光114的特性或仅指示光114的存在。

当光穿越第一材料且入射在第一材料与第二材料的边界上时,光可在此边界处被反射或可经由边界透射至第二材料中。光在两种材料之间的边界处的反射或透射是基于两种材料的特性及光的特性。两种材料的相关特性可包括其透射系数及反射系数。光的相关特性可包括光的波长及光入射在边界上的角度。

当光穿越材料时,光的一部分可被材料吸收。将被材料吸收的光的量是(部分地)基于材料的吸收系数及光穿过材料的路径的长度。越高的吸收系数导致越高的吸收率。同样,穿越材料的越长路径导致材料中的越高吸收率。另外,材料的吸收系数随着光的波长变化。相比于其他波长的光,一种材料可能更容易吸收某些波长的光。

穿过材料的个别光子具有被材料吸收的机率。吸收机率取决于光子的波长、材料对彼波长的吸收系数,及光子穿越材料的路径的长度。所有此些因素皆与光电侦测器102侦测光的方式有关。

光电侦测器102利用光敏鳍片110来吸收并借此侦测光。光敏鳍片110由光敏材料制成。光敏材料为对选定波长范围的光具有相对高的吸收系数的材料。此选定范围可对应于可视光的特定颜色。选定范围可对应于与光学通讯相关联的波长范围。可视光及具有与光学通讯相关联的波长的光为根据本文所揭示的实施例的光电侦测器可侦测的光的实例。本揭示案的实施例并不限于侦测可视光及具有与光学通讯相关联的波长的光的光电侦测器。根据本揭示案的实施例包括能够侦测除了可视光或具有与光学通讯相关联的波长的光以外的光的光电侦测器。

集成电路101配置用以允许光114穿过各种层至圆形光栅106,而不会在到达圆形光栅106之前被吸收或反射。因此,集成电路101可包括具有低吸收系数及低反射系数的多个透明层,借此使得光114能够穿过集成电路101的此些透明层至圆形光栅106。

在一个实施例中,圆形光栅106包括形成在半导体基板104中的环形沟槽。介电鳍片108及光敏鳍片110各自在沟槽的内壁与沟槽的外壁之间延伸。介电鳍片108及光敏鳍片110以交替次序定位,使得每一光敏鳍片110定位在两个介电鳍片108之间。对应地,每一介电鳍片108定位在两个光敏鳍片110之间。

光电侦测器102利用圆形光栅106来增强光电侦测器102的灵敏度。圆形光栅106通过增大个别光子穿过光敏材料的路径的长度来增强光电侦测器102的灵敏度。特定而言,圆形光栅106配置用以接收相对于垂直成选定角度的入射光,将来自选定角度的光重新引导至实质上水平的角度,且接着使光114围绕圆形光栅106行进,直至其被光敏鳍片110中的一者吸收为止。因此,圆形光栅106配置用以使光114无限期地围绕圆形光栅106行进。

个别光子穿过光敏鳍片110中的一者的次数越多,光子会被光敏鳍片中的一者吸收的可能性便越大。圆形光栅106使光在实质上圆形的路径中无限期地穿越圆形光栅106。当光围绕圆形光栅106行进时,光将不断地遇到光敏鳍片110。因此,圆形光栅106有效地增大了光子穿越光敏材料的长度。在光敏材料内的越长路径导致光子会被光敏材料吸收的越高可能性。因此,在光敏材料内的较长路径导致光电侦测器102的灵敏度的有效增大。

在一个实施例中,圆形光栅106借助于在圆形光栅106内实施透镜效应(lensingeffect)而有助于引导光子停留在圆形光栅106内直至吸收为止。特定而言,介电鳍片108及光敏鳍片110形成为圆形光栅中的透镜。当每一鳍片在沟槽的内侧壁与外侧壁之间延伸时,每一鳍片具有选定曲率。鳍片的曲率具有透镜效应。鳍片的累积透镜效应引导光沿圆形路径穿过沟槽。此透镜效应的结果在于,光倾向于呈圆圈无限期地行进,直至其最终被光敏鳍片110中的一者吸收为止。

在一个实施例中,圆形光栅106有助于基于全内反射(total internalreflection)原理将光限制在圆形光栅106内。当穿越具有第一折射率n

θ

其中n

在一个实施例中,光电侦测器102包括光电二极管。光电二极管包括多个具有半导体材料的区域。举例而言,光敏鳍片110的光敏材料可包括掺杂有第一掺杂剂类型(P型或N型)的单晶半导体材料。半导体基板104可包括掺杂有第二掺杂剂类型的单晶半导体材料,此第二掺杂剂类型为第一掺杂剂类型的补充。光敏鳍片110及半导体基板104形成P-N接合区。当光子被光敏鳍片中的一者的光敏材料吸收时,电子接收对应于光子波长的能量,并自价带移至导带。控制电路系统112将光敏鳍片110及半导体基板104偏置,以使得导带中的电子流动成控制电路系统112所侦测到的电流。因此,控制电路系统112将光114的亮度或强度侦测为由电子形成的电流,此些电子通过光的吸收自价带过渡至导带。在不脱离本揭示案的范畴的情况下,光电二极管可包括除了上述彼些以外的P及N半导体区域的其他配置。另外,光电二极管可包括由固有半导体区域(intrinsic semiconductor regions)分离开的P及N区域。固有半导体区域可对应于实质上无掺杂剂的半导体区域。

在一个实施例中,光电侦测器102可为光电侦测器而非光电二极管。利用光敏鳍片110对光的吸收,光电侦测器的许多可能配置是可能的。在不脱离本揭示案的范畴的情况下,如本文所述的利用圆形光栅106来增大光在光敏鳍片110内的路径长度的原理可在此些其他类型的光电侦测器中实施。

在一个实施例中,光敏鳍片110的光敏材料包括锗,介电鳍片108的介电材料包括二氧化硅,且覆盖沟槽侧壁的介电材料包括二氧化硅。锗对100nm至1700nm之间的光的波长具有相对高的吸收系数。另外,锗具有为4的相对高的折射率。二氧化硅具有为1.46的折射系数。此材料组合导致以下的临界角度:

θ

因此,光敏材料与覆盖侧壁的介电材料之间的任何大于21.4°的光入射角将导致全内反射。

光敏材料可包括除了锗以外的材料。举例而言,光敏材料可包括硅、硅锗、铟镓砷化物、硫化铅、汞镉碲化物或其他光敏材料。熟悉此项技术者将认识到,根据本揭示案,在不脱离本揭示案的范畴的情况下,光敏材料可包括除了上述彼些以外的材料。光敏材料可包括一或更多个P掺杂区域。光敏材料可包括一或更多个N掺杂区域。光敏材料可包括P掺杂区域以及N掺杂区域。

介电鳍片108可包含除了二氧化硅以外的材料。举例而言,介电鳍片108可包含氮化硅、碳掺杂氧化硅,或其他介电材料。在不脱离本揭示案的范畴的情况下,可将许多种介电材料用于介电鳍片108。

覆盖沟槽的侧壁的介电材料层可包括除了二氧化硅以外的材料。举例而言,介电材料可包括氮化硅、碳掺杂氧化硅,或其他介电材料。在不脱离本揭示案的范畴的情况下,可利用许多种介电材料来覆盖沟槽的侧壁。

半导体基板104可包括一或更多个具有半导体材料的层,此半导体材料包括硅、锗、硅锗、碳化硅、砷化镓、砷化铟、磷化铟、硅锗碳化物、镓砷磷化物或镓铟磷化物。在不脱离本揭示案的范畴的情况下,可将其他半导体用于半导体基板104。

集成电路101可接合至第二集成电路。集成电路101可将光电侦测器102所产生的电子信号传递至包括在第二集成电路中的电路系统。第二集成电路可包括处理电路系统,以处理电信号。

图2为根据一个实施例的处在处理的中间阶段的集成电路101的一部分的横截面图。特定而言,图2的视图绘示用于在集成电路101内形成光电侦测器102的制程的一部分。在图2中所示的阶段,集成电路101的所绘示部分包括半导体基板104及介电材料层118。

半导体基板104可包括一或更多个具有半导体材料的层。半导体材料可包括硅、锗、硅锗、碳化硅、砷化镓、砷化铟、磷化铟、硅锗碳化物、镓砷磷化物或镓铟磷化物。在不脱离本揭示案的范畴的情况下,可将其他半导体材料用于半导体基板104。半导体基板104可包括一种单晶半导体材料或单晶半导体材料的多个层。

在一个实施例中,介电材料层118可包括氮化硅、氧化硅或另一介电材料。介电材料层118厚度在1μm与100μm之间。介电材料层118可通过一或更多个薄膜沉积制程来沉积,一或更多个薄膜沉积制程包括化学气相沉积、物理气相沉积、电浆增强化学气相沉积、原子层沉积或其他类型的沉积制程。在不脱离本揭示案的范畴的情况下,介电材料层118可包括除了上述彼些以外的材料、厚度及沉积制程。

图3A为根据一个实施例的处在处理的中间阶段的集成电路101的一部分的横截面图。在图3A中,已在半导体基板104中打开沟槽120。沟槽120限定底表面122、外侧壁124及内侧壁125。在一个实施例中,沟槽120可具有高达700μm的深度。在一些实施例中,沟槽120可具有高达700μm的宽度。在不脱离本揭示案的范畴的情况下,沟槽120可具有除了上述彼些以外的深度及宽度尺寸。

沟槽120为具有实质上矩形的横截面的环形或圆形沟槽。沟槽120在半导体基板104中形成完整的圆。此在图3B的俯视图中绘示地更清晰。沟槽的外侧壁的半径在100μm与2mm之间。内侧壁125的半径在10μm与1mm之间。在不脱离本揭示案的范畴的情况下,可将其他尺寸用于沟槽120。环形沟槽120的一个目的在于形成光栅,此光栅使光114在环形沟槽周围行进,直至被光敏材料吸收为止。因此,如以下将更详细描述,可基于入射光114的预期波长以及介电鳍片及光敏鳍片的透镜效应来选定沟槽的尺寸。

在一个实施例中,通过利用光微影技术形成沟槽120。光微影技术可包括在介电材料层118上沉积光阻剂,经由光微影遮罩将光阻剂暴露于光,以及根据遮罩所限定的环形图案移除光阻剂的部分。

在光阻剂已图案化之后,将集成电路101暴露于蚀刻制程。蚀刻制程首先蚀刻介电材料层118的已曝光部分。可使用一或更多个湿式蚀刻、干式蚀刻或其他类型的蚀刻制程来蚀刻介电材料层118。可在蚀刻介电材料层118的同一蚀刻制程期间蚀刻半导体基板104。或者,可在已蚀刻介电材料层118的已曝光部分之后,使用单独蚀刻制程来蚀刻半导体基板104。

在已对介电材料层118的已曝光部分及半导体基板104执行一或更多个蚀刻制程之后,沟槽120已形成。沟槽120包括外侧壁124、内侧壁125及底表面122。

图3B为根据一个实施例的图3A的集成电路101的俯视图。沟槽120具有环形或圆形的形状。介电材料层118覆盖半导体基板104的在沟槽120外部的表面。

图4为根据一个实施例的处在处理的中间阶段的集成电路101的一部分的横截面图。在图4中,介电材料层127已沉积在介电材料层118上及沟槽120中的半导体基板104上。介电材料层已经受平坦化制程,此平坦化制程自介电材料层118的顶部移除介电材料层127。介电材料层127可包括二氧化硅、氮化硅或另一介电材料。介电材料层127可通过薄膜沉积制程来沉积,该薄膜沉积制程包括化学气相沉积、物理气相沉积、电浆增强化学气相沉积、原子层沉积或其他薄膜沉积技术中的一或更多者。在不脱离本揭示案的范畴的情况下,可将除了上述彼些以外的其他介电材料及沉积制程用于介电材料层127。

图5A为根据一个实施例的处在处理的中间阶段的集成电路101的一部分的横截面图。图5B为图5A的集成电路101的俯视图。在图5A及图5B中,已图案化并蚀刻了介电材料层127,在一或更多个蚀刻制程之后,在沟槽120的外侧壁124及内侧壁125上留下侧壁介电涂层130。蚀刻制程亦留下自沟槽120的底表面122延伸的多个介电鳍片108(参见图5B及图5C)。侧壁介电涂层130及介电鳍片108为介电材料层127的残留物。

介电鳍片108及侧壁介电涂层130可(部分地)通过利用光微影技术来形成。举例而言,光微影技术可包括在介电材料层127上沉积光阻剂,经由光微影遮罩将光阻剂暴露于光,以及根据遮罩所限定的图案移除光阻剂的部分。

在光阻剂已图案化之后,介电材料层127的已曝光部分经受各向异性蚀刻制程。各向异性蚀刻制程在向下方向上选择性地进行蚀刻。此意谓各向异性蚀刻制程在向下方向上但不在其他方向上蚀刻介电材料层127。更特定而言,各向异性蚀刻在向下方向上比在其他方向上更迅速地蚀刻介电材料层。

在一个实施例中,介电鳍片108具有弯曲的形状,如在图5B的俯视图中所见。特定而言,介电鳍片108弯曲成透镜的形状。选定介电鳍片108的弯曲透镜形状,以使入射光114连续聚焦至环形沟槽120周围的圆形路径中。

蚀刻制程亦限定介电鳍片108之间的缝隙131。缝隙131具有透镜的弯曲形状。每对介电鳍片108通过缝隙131分离开。

图5A的横截面图穿过沟槽120中的缝隙131。然而,在实践中,由于介电鳍片108及缝隙131的弯曲形状,因此穿过环形沟槽120的中心的笔直横截线将穿过介电鳍片108以及缝隙131两者的部分。为了简化,图5A图示了仿佛沿仅穿过环形沟槽120的任一侧上的缝隙131的线截取的横截面。

图5C为根据一个实施例的沿图5B中所示的线5C穿过沟槽120的一部分的横截面图。线5C穿过多个介电鳍片108以及介电鳍片108之间的缝隙131。

在一个实施例中,介电鳍片108各自具有在1nm与100nm之间的宽度。缝隙131可具有与介电鳍片108相同的宽度。或者,缝隙131及介电鳍片108可具有不同宽度。

图6A为根据一个实施例的处在处理的中间阶段的集成电路101的横截面图。图6B为根据一个实施例的图6A的集成电路101的俯视图。在图6A及图6B中,光敏鳍片110已形成在介电鳍片108之间的缝隙131中的沟槽120中。可执行平坦化制程,以使介电鳍片及光敏鳍片110的高度均匀。

光敏鳍片110可弯曲且可具有透镜的形状,如在图6B的俯视图中所见。选定光敏鳍片110及介电鳍片108的透镜形状,以使光114在环形沟槽120周围的圆形路径中行进。如先前关于图5A至图5C所述,光敏鳍片110具有对应于介电鳍片108之间的缝隙131的宽度的宽度。

如先前关于图1所述,光敏材料为对选定波长范围的光有相对高的吸收系数的材料。另外,光敏鳍片110为与介电鳍片108的介电材料以及侧壁介电涂层130相比较而言具有相对高的折射率的材料。

在一个实施例中,光敏鳍片110的光敏材料包括锗、硅、硅锗、铟镓砷化物、硫化铅、汞镉碲化物或其他光敏材料中的一或更多者。熟悉此项技术者将认识到,根据本揭示案,在不脱离本揭示案的范畴的情况下,光敏材料可包括除了上述彼些以外的材料。

在一个实施例中,光敏鳍片110结合半导体基板104共同地形成光电二极管。因此,光敏鳍片110的光敏材料可包括单晶半导体结构。光敏鳍片110可各自包括用于当作光电二极管的一或更多个掺杂区域。光敏鳍片110可各自包括一或更多个P掺杂区域。光敏鳍片110可各自包括一或更多个N掺杂区域。光敏鳍片110可各自包括P掺杂区域以及N掺杂区域。

在一个实施例中,光敏鳍片经由磊晶生长沉积在沟槽120中。光敏鳍片110可自半导体基板104磊晶生长。特定而言,光敏鳍片110可自环形沟槽120的底表面122磊晶生长。半导体基板104的晶体结构当作种晶,以便生长光敏鳍片110的晶体结构。

磊晶生长可发生在一或更多个阶段中。若光敏鳍片110将经掺杂,则掺杂可在光敏鳍片110的磊晶生长期间原位发生。若光敏鳍片110包括多个不同掺杂的区域,则掺杂可在磊晶生长制程的连续阶段期间原位发生。光敏鳍片110可各自包括具有相对少的掺杂或无掺杂的固有区域。根据光电侦测器102的设计结合半导体基板104来选择各自区域中的掺杂分布及掺杂类型或掺杂不足。

环形沟槽120、光敏鳍片110及介电鳍片108共同地形成圆形光栅106。圆形光栅106配置用以将相对于垂直成45°至90°之间的角度入射的光114重新引导为实质上在水平方向上穿越圆形光栅106。在一个实例实施例中,光114相对于垂直成45°至90°之间的角度自光源111(诸如,光纤缆线)入射在圆形光栅106上。圆形光栅106将光重新引导至圆形光栅106内的实质上水平的轨迹,如通过图6C中的光114的路径所指示。透镜形介电鳍片108及光敏鳍片110的透镜效应导致现在实质上水平的光在沟槽120周围成圆形地行进,直至光114被光敏鳍片110中的一者吸收为止。在图6B中绘示光114的圆形路径。因为光成环形地穿越圆形光栅106,所以光极有可能最终被光敏鳍片110中的一者吸收,借此增强包括圆形光栅106的光电侦测器102的灵敏度。

图6C为根据一个实施例的沿图6B中所示的线6C穿过沟槽120的一部分的横截面图。线6C穿过多个介电鳍片108及多个光敏鳍片110。每一光敏鳍片110定位在两个介电鳍片108之间。每一介电鳍片108定位在两个光敏鳍片110之间。

图7为根据一个实施例的处在处理的中间阶段的集成电路101的横截面图。图7中,介电材料层133已沉积在圆形光栅106之上以及介电材料层118之上。介电材料层133可包括氧化硅、氮化硅或其他介电材料中的一或更多者。因此,介电材料层133可为另一介电材料层。

在一个实施例中,介电材料层133为与介电鳍片108及侧壁介电涂层130相同的材料。或者,介电材料层133可为与介电鳍片108及侧壁介电涂层130不同的材料。将介电材料层133选定为对将入射在圆形光栅106上的光114透明。此介电材料层可具有与光敏鳍片的折射率相同或不同的折射率。

图8A为根据一个实施例的处在处理的中间阶段的集成电路101的横截面图。图8B为根据一个实施例的图8A的集成电路101的俯视图。在图8A及图8B中,已在介电材料层133中蚀刻开口,且已在此开口中形成了电极136。

电极136包括一或更多种导电材料,诸如,金属或多晶硅。电极136为环形的,因为其接触光敏鳍片110中的每一者。电极136可将偏置电压施加至光敏鳍片110及/或可自光敏鳍片110读取信号。一或更多个电极亦可接触半导体基板104,以使得能够在半导体基板104与光敏鳍片110之间施加偏置电压。在不脱离本揭示案的范畴的情况下,接触光敏鳍片110的电极136可具有其他形状、位置及配置。

图9为根据一个实施例的集成电路101的横截面。图9绘示光电侦测器102,此光电侦测器102包括定位在半导体基板104上的圆形光栅106。为了简化,图9中未图示圆形光栅106的介电鳍片108及光敏鳍片110。多个晶体管141与半导体基板104结合形成。

介电堆叠135形成在介电材料层133上。集成电路101包括定位在整个介电堆叠135的金属互连件142。集成电路101包括一或更多个外部连接衬垫144。金属互连件142实现了晶体管141、光电侦测器102、连接衬垫144及可包括在集成电路101中的任何其他电路部件之间的连接。晶体管141可包括关于图1所描述的控制电路系统112。金属互连件142使得能够将偏置电压施加至光电侦测器102,以及自光电侦测器102读取信号。

开口140形成在介电堆叠135中。光源111(诸如,光纤缆线)将光114输出至开口140中。光114行进至圆形光栅106,且被重新引导为在圆形光栅106周围行进,直至光114被光敏鳍片110中的一者吸收为止。

集成电路101可为将来自光源111的光学信号变换成电信号的光子集成电路。逻辑集成电路可经由连接衬垫144耦合至集成电路101。逻辑集成电路可接收由光子集成电路101产生的电信号,且可处理此些电信号以自其提取数据。在此情形下,光子集成电路101可包括或可不包括晶体管141。逻辑集成电路可包括用于处理电信号的晶体管141。

在一个实施例中,圆形光栅106利用光栅耦合器的熟知原理来重新引导几乎垂直的入射光的轨迹。传统光栅耦合器并非圆形的。通常,传统光栅耦合器将光聚焦至波导中,此波导将光导引至可吸收光的光敏材料上。然而,若光敏材料在光首次通过时不吸收光,则光可能未经侦测便离开光敏材料。因此,因为大量入射光从未被光敏材料吸收,所以使用传统光栅耦合器的传统光电侦测器是低效的。图1至图9的圆形光栅106提供了一种具有增强的灵敏度的光电侦测器,因为光114环绕圆形光栅,直至其被光敏鳍片110中的一者吸收为止。

关于光栅耦合器的另外细节可在“用于光纤与纳米光子波导之间的耦合的光栅耦合器(Grating Couplers for Coupling between Optical Fibers and NanophotonicWaveguides)”(《日本应用物理学杂志(Japanese Journal of Applied Physics)》第45卷,第8A期,2006年,第6071-6077页)中找到,此案以引用方式并入本文中。

图10为根据一个实施例的用于形成集成电路的方法1000的流程图。在1002处,方法1000包括在半导体基板中形成环形沟槽。半导体基板的一个实例为图6A至图6C的半导体基板104。环形沟槽的一个实例为图6A至图6C的环形沟槽120。在1004处,方法1000包括在环形沟槽中形成多个介电鳍片。介电鳍片的一个实例为图6B、图6C的介电鳍片108。在1006处,方法1000包括在环形沟槽中形成多个光敏鳍片(110),每一光敏鳍片(110)定位在相邻的多个介电鳍片之间。光敏鳍片的一个实例为图6A至图6C的光敏鳍片110。

在一个实施例中,一种集成电路包括半导体基板、在半导体基板中的环形沟槽,及在环形沟槽中的多个介电鳍片。集成电路包括定位在环形沟槽中的多个光敏鳍片,每一光敏鳍片在两个相邻的介电鳍片之间。多个介电鳍片及多个光敏鳍片配置作为圆形光栅,圆形光栅配置用以引导入射光围绕环形沟槽。

在一个实施例中,圆形光栅及半导体基板配置作为光电侦测器,光电侦测器配置用以侦测入射在圆形光栅上的光。在一个实施例中,光电侦测器通过在多个光敏鳍片中吸收光来侦测光。在一个实施例中,多个光敏鳍片及半导体基板配置作为光电二极管。在一个实施例中,多个光敏鳍片包含锗。在一个实施例中,半导体基板包含硅。在一个实施例中,多个介电鳍片包含氧化硅。在一个实施例中,环形沟槽包括内侧壁、外侧壁和侧壁介电涂层。内侧壁限定环形沟槽的内部横向边界。外侧壁限定环形沟槽的外部横向边界。侧壁介电涂层覆盖内侧壁及外侧壁。在一个实施例中,集成电路包括环形电极,环形电极接触多个光敏鳍片。在一个实施例中,环形沟槽具有实质上矩形的横截面。在一个实施例中,多个光敏鳍片及多个介电鳍片是弯曲的。在一个实施例中,多个光敏鳍片及多个介电鳍片当作多个透镜,多个透镜引导光围绕环形沟槽。

在一个实施例中,一种光电侦测器包括半导体基板,及形成在半导体基板中的圆形光栅。圆形光栅包括多个介电鳍片及多个光敏鳍片,每一光敏鳍片定位在相邻的多个介电鳍片之间。

在一个实施例中,光电侦测器包括环形沟槽,环形沟槽形成在半导体基板中,其中多个介电鳍片及多个光敏鳍片定位在环形沟槽中。在一个实施例中,圆形光栅配置用以引导光围绕环形沟槽。

在一个实施例中,一种方法形成集成电路的包括在半导体基板中形成环形沟槽,及在环形沟槽中形成多个介电鳍片。此方法包括在环形沟槽中形成多个光敏鳍片,每一光敏鳍片定位在相邻的多个介电鳍片之间。

在一个实施例中,形成集成电路的方法进一步包括通过磊晶生长自环形沟槽的底表面形成多个光敏鳍片。在一个实施例中,多个光敏鳍片为单晶半导体鳍片。在一个实施例中,形成集成电路的方法进一步包括形成与多个光敏鳍片接触的电极。在一个实施例中,形成集成电路的方法进一步包括在集成电路中形成开口以将光接收至环形沟槽中。

可组合上述各种实施例以提供另外实施例。必要时可修改实施例的态样,以采用各个专利、申请案及公布的概念,以便提供另外实施例。

可根据以上详细描述对实施例作出此些及其他改变。大体而言,在权利要求书中,所使用的术语不应被解释为将权利要求限制为说明书及权利要求书中所揭示的特定实施例,而应解释为包括所有可能的实施例以及此些权利要求享有的等效物的全部范畴。因此,权利要求范围并不受揭示内容限制。

- 集成电路、光电侦测器以及形成集成电路的方法

- 光电集成电路装置、光电集成电路系统及传输方法