一种低输入电源幅度的电平转换电路

文献发布时间:2023-06-19 11:44:10

技术领域

本发明涉及电子电路技术领域,尤其是涉及一种低输入电源幅度的电平转换电路。

背景技术

对于包括众多数字或者模拟模块的片上系统(SoC)芯片来说,数字模块与模拟模块通常对应不同的电源电压,即使是同为数字模块或者模拟模块,其供电电压的大小都可能不同。例如数字模块的核心电压通常低于1V,但是输入输出(IO)接口模块的供电电压通常为锂电池电压(3.3V~4.2V)或者片外提供的高电源电压。SoC中不同的数字模块或者模拟模块与数字模块之间通常采用数字信号进行交互,显然不同电源电压的数字信号之间不能直接耦合,因此电平转换电路是SoC芯片中不可或缺的基础模块。电平转换电路通常包括两种类型,第一种是将高电源电压数字信号转换为低电源电压数字信号,这通常不需要非常特殊的电路结构,只需要反相器即可,因为高电源电压数字信号直接可以驱动低电源电压供电的反相器,从而得到低电源电压的数字信号。该电平转换电路唯一需要注意的是构成反相器的NMOS管与PMOS管的耐压值不能低于高电源电压的最大值。第二种电平转换电路是将低电源电压数字信号转换为高电源电压数字信号,不能仅仅采用反相器进行电平转换,因为低电源电压数字信号不能充分驱动高电源电压供电的反相器,即当输入信号为高电平,从电压幅度上看为低电源电压,但是反相器的供电为高电源电压,此时反相器的NMOS管导通,PMOS也有可能导通,从而导致输出逻辑值不能确定。

现有的电平转换电路存在以下问题:

较低的数字电源VDDL无法充分驱动高阈值电压的NMOS管,导致高电源电压输出数字信号无法随着低电源电压输入信号翻转而有效翻转。

发明内容

本发明提供一种低输入电源幅度的电平转换电路,以解决现有的电平转换电路高电源电压输出数字信号无法随着低电源电压输入信号翻转而有效翻转的技术问题。

本发明的实施例提供了一种低输入电源幅度的电平转换电路,包括:

第一PMOS管、第二PMOS管、第一NMOS管、第二NMOS管、第一反相器、第二反相器、第三反相器、第四反相器和第五反相器;

信号输入端分别与所述第一反相器的输入端和所述第三反相器的输入端连接,所述第一反相器的输出端分别与所述第二反相器的输入端和所述第五反相器的输出端连接;所述第二反相器的输出端分别与所述第一NMOS管的栅端和所述第四反相器的输入端连接;所述第三反相器的输出端与所述第一NMOS管的源端连接;所述第五反相器的输出端与所述第二NMOS管的源端连接;所述第四反相器的输出端分别与所述第二NMOS管的栅端和所述第一PMOS管的漏端连接;所述第二NMOS管的漏端分别与所述第一PMOS管栅端和所述第二PMOS管的漏端连接;

所有NMOS管的体端均接地;所有PMOS管的体端均与高电源输入端连接;所有反相器均与低电源输入端连接。

进一步的,所有所述反相器均包括一个低阈值电压PMOS管和一个低阈值电压NMOS管。

进一步的,所述反相器的输入端与所述低阈值电压NMOS管的栅端和所述低阈值电压PMOS管的栅端连接,所述低阈值电压PMOS管的源端和体端均与所述低电源输入端连接,所述低阈值电压NMOS管的源端和体端均与地连接,所述低阈值电压PMOS管的漏端和所述低阈值电压NMOS管的漏端均与所述反相器的输出端连接。

进一步的,所有所述反相器中的低阈值电压PMOS管的源端和体端均与所述低电源输入端连接。

进一步的,所述第一PMOS管和所述第二PMOS管为同一类型PMOS管。

进一步的,所述第一NMOS管和所述第二NMOS管为同一类型MMOS管。

进一步的,所述第一PMOS管和所述第二PMOS管均为高阈值电压PMOS管。

进一步的,所述第一NMOS管和所述第二NMOS管均为自然NMOS管。

本发明实施例能够在极低输入电源幅度下实现快速数字信号逻辑电平的低到高转换,使高电源电压输出数字信号能够随着低电源电压输入信号翻转有效翻转。

进一步的,在完成低电平到高电平的转换后,电平转换电路保持彻底关断状态,静态电流几乎为0,能够有效解决现有的低转高电平转换电路在较低的输入侧电源电压情况下不能工作的问题,且本发明实施例提供的电平转换电路结构简单,消耗面积小,适用于大规模SoC设计中。

附图说明

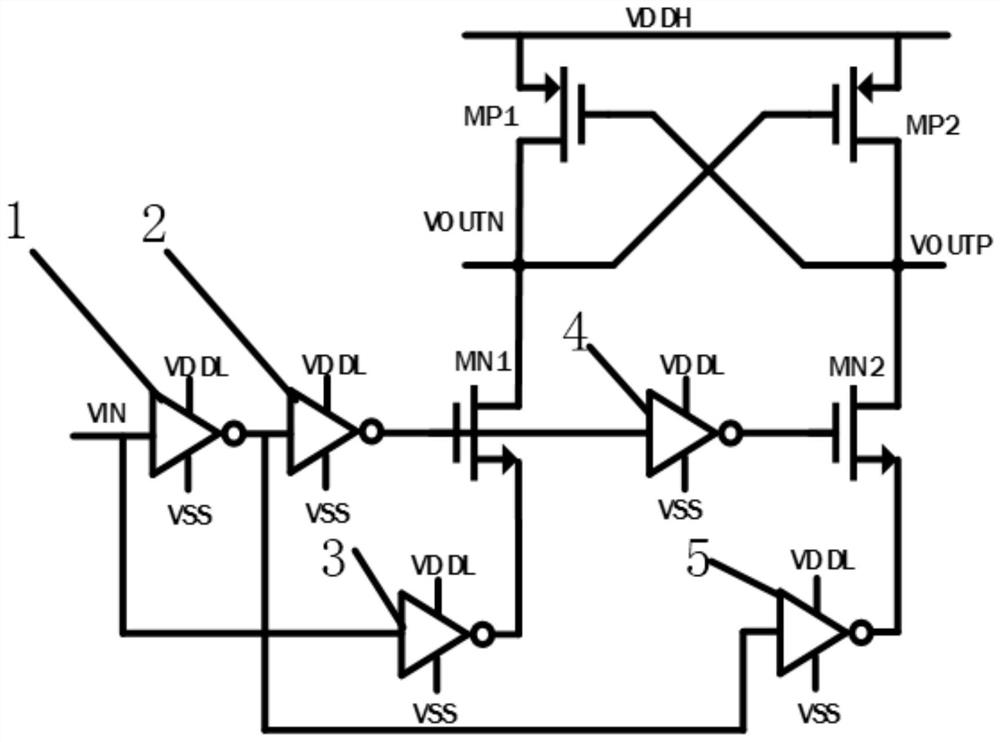

图1是本发明实施例提供的低输入电源幅度的电平转换电路的结构示意图。

图2是本发明实施例提供的反相器的结构示意图;

图3是本发明实施例提供的输入数字信号VIN和输出数字信号VOUTP的波形变化示意图;

图4是本发明实施例提供的在输入数字信号分别为VDDL和VSS下的电平转换电路的静态电流示意图。

其中,说明书附图中的附图标记如下:

1、第一反相器;2、第二反相器;3、第三反相器;4、第四反相器;5、第五反相器。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

在本申请的描述中,需要理解的是,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本申请的描述中,除非另有说明,“多个”的含义是两个或两个以上。

在本申请的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本申请中的具体含义。

请参阅图1,本发明的实施例提供了一种低输入电源幅度的电平转换电路,包括:

第一PMOS管、第二PMOS管、第一NMOS管、第二NMOS管、第一反相器1、第二反相器2、第三反相器3、第四反相器4和第五反相器5;

信号输入端分别与第一反相器1的输入端和第三反相器3的输入端连接,第一反相器1的输出端分别与第二反相器2的输入端和第五反相器5的输出端连接;第二反相器2的输出端分别与第一NMOS管的栅端和第四反相器4的输入端连接;第三反相器3的输出端与第一NMOS管的源端连接;第五反相器5的输出端与第二NMOS管的源端连接;第四反相器4的输出端分别与第二NMOS管的栅端和第一PMOS管的漏端连接;第二NMOS管的漏端分别与第一PMOS管栅端和第二PMOS管的漏端连接;

所有NMOS管的体端均接地;所有PMOS管的体端均与高电源输入端连接;所有反相器均与低电源输入端连接。

在本发明实施例中,VDDH为高电源电压,对应输出侧的数字信号高电平大小,VDDL为低电源电压,对应输入侧的数字信号高电平大小,VSS为参考地,VIN为输入逻辑信号,其高电平幅度为VDDL,VOUTP为输出逻辑信号,其高电平幅度为VDDH,VOUTN为输出反向逻辑信号,其高电平幅度为VDDH。本发明实施例的电平转换电路设置有第一PMOS管MP1、第二PMOS管MP2,第一NMOS管MN1、第二NMOS管MN2,以及五个反相器。

当VIN为VSS时,第三反相器3的输出电压为VDDL,即第一NMOS管MN1的源端电压为VDDL,第一NMOS管MN1的栅端电压为VSS,此时第一NMOS管MN1的删源电压为-VDDL,将第一NMOS管MN1彻底关断,能够有效减少电平转换电路的漏电流,且能够使得VOUTN与VSS之间无直流通路。可选地,当VIN为VSS时,第四反相器4的输出电压为VDDL,第五反相器5的输出电压为VSS,第二NMOS管MN2的栅源电压为VDDL,由于第一NMOS管MN2、第二NMOS管MN2均为自然MOS管,其阈值电压接近于0,因此第二NMOS管MN2处于强导通状态,VOUTP与VSS之间存在低阻通路,VOUTP被拉到接近VSS,此时第一PMOS管MP1导通,VOUTN被拉到VDDH,彻底关闭MP2,此时VOUTP为VSS并保持不变。

进一步地,将第一NMOS管MN1关闭,从VDDH经过第一PMOS管MP1和第一NMOS管MN1到VSS的静态电流几乎为0;由于第二PMOS管MP2彻底关闭,从VDDH经过MP2和MN2到VSS的静态电流几乎为0。VIN与VOUT都为VSS,即都为对应电源幅度的逻辑0。

当VIN为VDDL时,第五反相器5的输出电压为VDDL,即第二NMOS管MN2的源端电压为VDDL,第二NMOS管MN2的栅端电压为VSS,此时第二NMOS管MN2的栅源电压为-VDDL,将第二NMOS管MN2彻底关断,能够有效减少电平转换电路的漏电流,且能够使得VOUTP与VSS之间无直流通路;可选地,当VIN为VDDL时,第二反相器2的输出电压为VDDL,第三反相器3的输出电压为VSS,此时第一NMOS管MN1的栅源电压为VDDL,由于自然MOS管的阈值电压接近于0,因此第一NMOS管MN1处于强导通状态,VOUTN与VSS之间存在低阻通路,VOUTN被拉到接近VSS,此时第二PMOS管MP2导通,VOUTP被拉到VDDH,彻底关闭MP1,此时VOUTN为VSS并保持不变。由于第二NMOS管MN2彻底关闭,从VDDH经过第二PMOS管MP2和第二NMOS管MN2到VSS的静态电流几乎为0;由于第一PMOS管MP1彻底关闭,从VDDH经过第一PMOS管MP1和第一NMOS管MN1到VSS的静态电流几乎为0。需要说明的是,当VIN为VDDL,VOUTP为VDDH,都为对应电源幅度的逻辑1。

本发明实施例能够在极低输入电源幅度下实现快速数字信号逻辑电平的低到高转换,使高电源电压输出数字信号能够随着低电源电压输入信号翻转有效翻转。

作为本发明实施例的一种具体实施方式,所有反相器均包括一个低阈值电压PMOS管和一个低阈值电压NMOS管。

请参阅图2,反相器的输入端与低阈值电压NMOS管的栅端和低阈值电压PMOS管的栅端连接,低阈值电压PMOS管的源端和体端均与低电源输入端连接,低阈值电压NMOS管的源端和体端均与地连接,低阈值电压PMOS管的漏端和低阈值电压NMOS管的漏端均与反相器的输出端连接。

在本发明实施例中,将反相器的输入端标记为a,输出端标记为b。每一反相器的电路结构均相同,均右一个低阈值电压PMOS管和一个低阈值电压NMOS管。需要说明的是,每一反相器其内部的PMOS管和NMOS管的尺寸可以根据需要进行设计。

作为本发明实施例的一种具体实施方式,所有反相器中的低阈值电压PMOS管的源端和体端均与低电源输入端连接。

作为本发明实施例的一种具体实施方式,第一PMOS管和第二PMOS管为同一类型PMOS管。第一NMOS管和第二NMOS管为同一类型MMOS管。

具体地,第一PMOS管和第二PMOS管均为高阈值电压PMOS管,第一NMOS管和第二NMOS管均为自然NMOS管。

请参阅图3-4,在一种具体的实施例中,在当前22nm工艺下,数字核心的工作电源电压设置为750mV,模拟电源电压或者IO部分的高电源电压设置为3.3V。数字信号的频率设置为10MHz。第一反相器1、第二反相器2及第四反相器4的尺寸较小,第三反相器3和第五反相器5的尺寸较大。请参阅图3,为本发明实施例提供的输入数字信号VIN和输出数字信号VOUTP的波形变化示意图,可以看出在750mV的极低输入端电源电压和3.3V的高输出端电源电压下,10MHz的高频数字信号依然可以顺利通过。请参阅图4,为本发明实施例提供的在输入数字信号分别为VDDL和VSS下的电平转换电路的静态电流示意图,其不包含第一反相器1-第五反相器5的静态漏电,可以看到其在120摄氏度下的最大漏电流仅为0.7nA,本发明实施例提供的电平转换电路具有极低的静态漏电。

实施本发明实施例,具有以下有益效果:

本发明实施例能够在极低输入电源幅度下实现快速数字信号逻辑电平的低到高转换,使高电源电压输出数字信号能够随着低电源电压输入信号翻转有效翻转。

进一步的,在完成低电平到高电平的转换后,电平转换电路保持彻底关断状态,静态电流几乎为0,能够有效解决现有的低转高电平转换电路在较低的输入侧电源电压情况下不能工作的问题,且本发明实施例提供的电平转换电路结构简单,消耗面积小,适用于大规模SoC设计中。

以上是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也视为本发明的保护范围。

- 一种低输入电源幅度的电平转换电路

- 一种低输入电源幅度的电平转换电路