电子封装件及其制法

文献发布时间:2023-06-19 11:44:10

技术领域

本发明有关一种半导体封装制程,尤指一种具屏蔽结构的电子封装件及其制法。

背景技术

随着电子产业的蓬勃发展,大部分的电子产品均朝向小型化及高速化的目标发展,尤其是通讯产业的发展已普遍将通讯装置运用整合于各类电子产品,例如行动电话(Cell phone)、膝上型电脑(laptop)等。然而上述的电子产品需使用高频的射频芯片,且射频芯片可能相邻设置数字集成电路、数字信号处理器(Digital Signal Processor,简称DSP)或基带芯片(BB,Base Band),造成电磁干扰(Electromagnetic Interference,简称EMI)问题,因此必需进行电磁屏蔽(Electromagnetic Shielding)处理。

现有避免EMI的射频(Radio frequency,简称RF)模块的制法,如图1A至图1C所示,将多个射频芯片11a,11b与非射频式电子元件11电性连接在一封装基板10上,再以例如环氧树脂的封装层13包覆各该射频芯片11a,11b与该非射频式电子元件11,并于该封装层13上形成一金属薄膜14。该射频模块1通过该封装层13保护该射频芯片11a,11b、非射频式电子元件11及封装基板10,并避免外界水气或污染物的侵害,且通过该金属薄膜14保护该些射频芯片11a,11b免受外界EMI影响。

然而,现有射频模块1的外围虽可通过包覆该金属薄膜14以达到避免EMI的目的,但若射频芯片11a,11b如为低频元件,则单一金属薄膜14作为屏障层仍难以防止电磁干扰。

因此,如何克服上述现有技术的问题,实已成为目前业界亟待克服的难题。

发明内容

鉴于上述现有技术的种种缺陷,本发明提供一种电子封装件及其制法,避免电子元件受外部电磁波干扰的问题。

本发明的电子封装件,包括:承载件;电子元件,其设于该承载件上且电性连接该承载件;多个屏蔽线,其设于该承载件上且跨越该电子元件以遮盖该电子元件,其中,该多个屏蔽线相互交错;以及封装层,其形成于该承载件上以包覆该电子元件及屏蔽线。

本发明亦提供一种电子封装件的制法,包括:提供一设有至少一电子元件的承载件,且该电子元件电性连接该承载件;形成多个屏蔽线于该承载件上,以令该屏蔽线跨越该电子元件,使该屏蔽线遮盖该电子元件,其中,该多个屏蔽线相互交错;以及形成封装层于该承载件上,以令该封装层包覆该电子元件及屏蔽线。

前述的电子封装件及其制法中,该屏蔽线的相对两端部分别连接至该承载件。

前述的电子封装件及其制法中,该屏蔽线为打线制程的焊线。

前述的电子封装件及其制法中,该多个屏蔽线沿其中一方向形成。

前述的电子封装件及其制法中,该多个屏蔽线沿多方向形成。

前述的电子封装件及其制法中,该屏蔽线外露于该封装层。

前述的电子封装件及其制法中,该屏蔽线为弧线,其弧顶外露于该封装层。例如,该弧顶齐平该封装层的表面。

前述的电子封装件及其制法中,还包括形成屏蔽件于该封装层上。

由上可知,本发明的电子封装件及其制法,主要通过该屏蔽线跨越该电子元件,以作为屏蔽结构,借以避免该电子元件受外部电磁波干扰的问题,且通过交错型屏蔽线以形成不规则通道,借以破坏幅射路径,故能达到更小的电磁幅射量,以提升电磁干扰的屏蔽效果。

此外,若该电子元件为低频元件,则通过埋设于该封装层内的屏蔽线能提供较好的防电磁干扰效果。

附图说明

图1A至图1C为现有射频模块的制法的剖面示意图。

图2A至图2E为本发明的电子封装件的制法的剖视示意图。

图2B’及图2B”为图2B的不同形式的局部上视示意图。

附图标记说明

1 射频模块

10 封装基板

11 非射频式电子元件

11a,11b 射频芯片

13,24 封装层

14 金属薄膜

2 电子封装件

20 承载件

20a 第一侧

20b 第二侧

20’ 绝缘保护层

200 电性接触垫

201 接地垫

202 接地层

21 电子元件

21a 作用面

21b 非作用面

22 焊线

23,23’ 屏蔽线

23a,23b 端部

230 弧顶

24a 第一表面

24b 第二表面

25 屏蔽件

S 切割路径。

具体实施方式

以下通过特定的具体实施例说明本发明的实施方式,本领域的技术人员可由本说明书所揭示的内容轻易地了解本发明的其他优点及功效。

须知,本说明书所附附图所绘示的结构、比例、大小等,均仅用以配合说明书所揭示的内容,以供本领域的技术人员的了解与阅读,并非用以限定本发明可实施的限定条件,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本发明所能产生的功效及所能达成的目的下,均应仍落在本发明所揭示的技术内容得能涵盖的范围内。同时,本说明书中所引用的如“第一”、“第二”、“上”、及“一”等的用语,亦仅为便于叙述的明了,而非用以限定本发明可实施的范围,其相对关系的改变或调整,在无实质变更技术内容下,当亦视为本发明可实施的范畴。

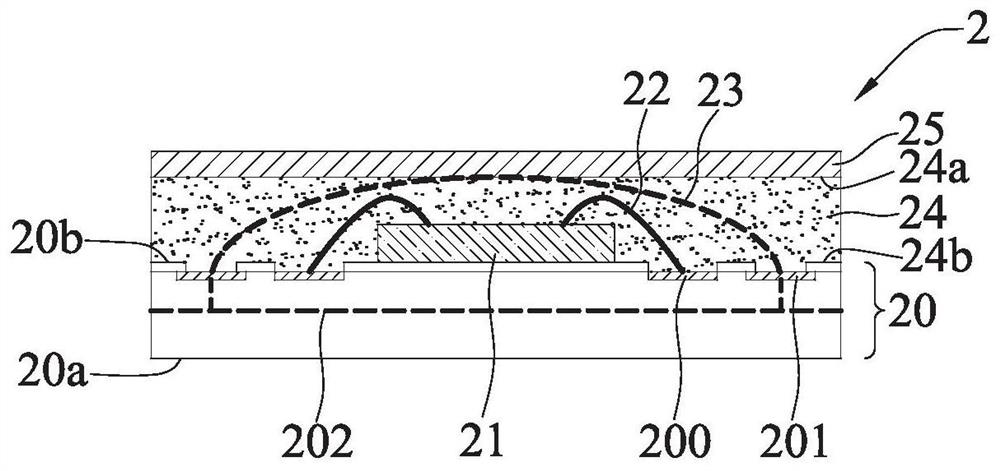

图2A至图2E为本发明的电子封装件2的制法的剖视示意图。

如图2A所示,提供一承载件20及至少一电子元件21,该承载件20具有相对的第一侧20a与第二侧20b,且该电子元件21设于该承载件20的第一侧20a上并电性连接该承载件20。

于本实施例中,该承载件20为具有核心层与线路结构的基板(substrate)或无核心层(coreless)的线路结构,该线路结构于介电材上形成线路层(图略),如扇出(fan out)型重布线路层(redistribution layer,简称RDL),且介电材为如聚对二唑苯(Polybenzoxazole,简称PBO)、聚酰亚胺(Polyimide,简称PI)、预浸材(Prepreg,简称PP)等。例如,该基板的最外侧具有线路层与绝缘保护层20’,该线路层包含多个外露于该绝缘保护层20’的电性接触垫200与接地垫201,且该接地垫201电性连接该基板的内部线路的接地层202。应可理解地,该承载件20亦可为其它可供承载如芯片等电子元件的承载单元,例如导线架(lead-frame)或硅中介板(silicon interposer)等载件,并不限于上述。

此外,该电子元件21为主动元件、被动元件或其组合者,且该主动元件例如为半导体芯片,而该被动元件例如为电阻、电容及电感。该电子元件21为射频芯片或其它半导体芯片,例如,蓝牙芯片或无线热点(Wi-Fi(Wireless Fidelity))芯片,其具有作用面21a与相对该作用面21a的非作用面21b,且该作用面21a上具有多个电极垫(图略),并以该非作用面21b设于该承载件20的第一侧20a上,使该电子元件21以其电极垫通过多个焊线22以打线方式电性连接该承载件20的线路层;或者,该电子元件21以该些电极垫通过多个导电凸块(图略)以覆晶方式电性连接该线路层;亦或,该电子元件21可直接接触该线路层以电性连接该线路层。然而,有关该电子元件21电性连接该承载件20的方式不限于上述。

如图2B所示,形成多个跨越该电子元件21的屏蔽线23于该承载件20的第一侧20a上,令该些屏蔽线23遮盖该电子元件21的作用面21a。

于本实施例中,该屏蔽线23的相对两端部23a,23b分别连接至该些接地垫201。例如,两屏蔽线23于单一处交错形成,如图2B’所示。

此外,该屏蔽线23为打线制程的焊线,如弧形金线,针对单一电子元件21沿其中一方向(如X或Y方向)布设多个条屏蔽线23,如图2B’所示;或者,针对单一电子元件21沿多方向(如X方向及Y方向)布设多个条屏蔽线23,23’,如图2B”所示。

如图2C所示,形成一封装层24于该承载件20的第一侧20a上,以令该封装层24包覆该电子元件21、焊线22及屏蔽线23。

于本实施例中,该封装层24为绝缘材,如聚酰亚胺(polyimide,简称PI)、干膜(dryfilm)、如环氧树脂(epoxy)的封装胶体或封装材(molding compound)。例如,该封装层24的制程可选择液态封胶(liquid compound)、喷涂(injection)、压合(lamination)或模压(compression molding)等方式形成于该承载件20上。

此外,该封装层24具有相对的第一表面24a与第二表面24b,以令该封装层24以其第二表面24b结合于该承载件20的第一侧20a上,且令该屏蔽线23的至少部分表面外露于该封装层24的第一表面24a。例如,可通过整平制程,使该封装层24的第一表面24a齐平该屏蔽线23的弧顶230,以令该屏蔽线23的弧顶230外露于该封装层24的第一表面24a。具体地,该整平制程通过研磨方式,移除该封装层24的部分材质。应可理解地,有关外露该屏蔽线23的方式繁多,如开孔,并不限于上述。

如图2D所示,形成一屏蔽件25于该封装层24的第一表面24a上,且令该屏蔽件25接触该屏蔽线23。

于本实施例中,该屏蔽件25为导电材,其材质不同于该封装层24的材质。例如,该屏蔽件25为导电层,如铜(Cu)、镍(Ni)、铁(Fe)或铝(Al)等,其以电镀、如溅镀(sputtering)的化学镀膜、涂布(coating)或其它方式形成。

如图2E所示,沿如图2D所示的切割路径S进行切单制程,以获取多个电子封装件2,且可于该承载件20的第二侧20b上形成多个如焊球的导电元件(图略),供该电子封装件2接置一如电路板的电子装置(图略)。

于本实施例中,该电子封装件2为可发出电磁波者,如射频(Radio frequency,简称RF)模块。

因此,本发明的制法主要通过该屏蔽线23,23’跨越该电子元件21,以作为屏蔽结构,借以避免该电子元件21受外部电磁波干扰的问题,且通过交错型屏蔽线23,23’以形成不规则通道,借以破坏幅射路径,达到更小的电磁幅射量,以提升电磁干扰的屏蔽效果。

此外,若该电子元件21为低频元件,则通过将该些屏蔽线23,23’埋设于该封装层24内以更靠近该电子元件21,使该些屏蔽线23,23’能提供较好的防电磁干扰效果。

本发明亦提供一种电子封装件2,包括:一承载件20、一电子元件21以及多个屏蔽线23。

所述的承载件20具有多个接地垫201。

所述的电子元件21设于该承载件20上且电性连接该承载件20。

所述的屏蔽线23设于该承载件20上且跨越该电子元件21以遮盖该电子元件21,其中,该多个屏蔽线23相互交错。

所述的封装层24形成于该承载件20上以包覆该电子元件21及屏蔽线23。

于一实施例中,该屏蔽线23的相对两端部23a,23b分别连接至该承载件20的接地垫201。

于一实施例中,该屏蔽线23为打线制程的焊线。

于一实施例中,该多个屏蔽线23对应该电子元件沿其中一方向布设。

于一实施例中,该多个屏蔽线23,23’对应该电子元件沿多方向布设。

于一实施例中,该屏蔽线23外露于该封装层24。

于一实施例中,该屏蔽线23为弧线,其弧顶230外露于该封装层24。例如,该弧顶230齐平该封装层24的第一表面24a。

于一实施例中,所述的电子封中件2还包括一形成于该封装层24上的屏蔽件25。

综上所述,本发明的电子封装件及其制法,通过该屏蔽线的设计,以避免该电子元件受外部电磁波干扰的问题。

上述实施例仅用以例示性说明本发明的原理及其功效,而非用于限制本发明。任何本领域技术人员均可在不违背本发明的精神及范畴下,对上述实施例进行修改。因此本发明的权利保护范围,应如随附的权利要求书所列。

- 电子封装件及其制法暨封装用基板及其制法

- 电子封装件的制法及电子封装结构