用于高压栅驱动芯片的高共模瞬态抑制差分信号接收电路

文献发布时间:2023-06-19 11:45:49

技术领域

本发明涉及一种用于高压栅驱动芯片的高共模瞬态抑制差分信号接收电路,属于集成电路技术领域。

背景技术

在智能电网、移动通信以及新能源汽车等新兴产业的牵引下,电力电子应用系统要求进一步提高系统的效率、小型化和增加功能,特别要求系统装备在尺寸、质量、功率和效率之间的权衡,比如服务器电源管理、电池充电器和太阳能电场的微逆变器。新一代电力电子整机系统对其内部高压栅驱动芯片的可靠性、速度、智能化提出了更高的需求,从而进一步提高整机可靠性,并降低整机系统设计复杂度。高压栅驱动芯片作为系统信号处理部分和执行部分的桥梁,将高压功率器件与控制电路、外围接口电路及保护电路等集成在一起,需要在功率集成技术就是需要在有限的芯片面积上实现高低压兼容、高性能、高效率与高可靠性。

图1示出了电力电子应用系统中最常用的一种高压栅驱动芯片,该电路为典型高压半桥栅驱动芯片及应用系统电路框图。典型半桥驱动电路分为高侧和低侧两路通道驱动电路,高侧驱动电路采用自举升压的方式实现信号传输控制,两路低压输入HI和LI,分别进入高侧和低侧两路通道。在低侧LI输入高电平期间,LO输出高电平,开关ML导通,开关节点(SW)被下拉至地,输入电源电压为VCC,高侧电路电源电压为VDD(HB点电压),通过自举二极管给自举电容充电使得自举电容两端电压差接近VCC。当高侧HI输入高电平期间,HO输出高电平,高侧管MH开启,开关节点电压上升至VH,即SW上升至VH。由于自举电容两端电压不变,故HB点电压=自举电压VHB被自举到SW+VCC。高侧电路始终保持电源电压VHB–SW≈VCC,SW在0和VH之间摆动,导致高侧电路电源电压VDD和衬底电位存在巨大的波动,产生非常严重的共模噪声。由于高/低侧输出电压最大值之间存在VH的压差,芯片内部产生高/低侧输出信号的电路之间必须进行高压隔离;此外,高压和低压区电路之间还必须进行信号连接,因此芯片内必须有负责隔离区两侧之间信号传输功能的隔离区信号传输模块;图1中高压隔离信号传输模块00即为完成上述2大核心功能的电路模块。

由于功率半导体器件的应用场景存在很大差异,VH电压可以从40V跨度到6500V,电流从几安培跨度到上百安培,开关频率从几KHz跨度到几MHz,不同的应用场景对于栅驱动IC的性能和成本要求完全不同。VH大小直接决定了芯片内部高/低侧信号电路之间的电气隔离等级,而在芯片内部实现不同等级的电气隔离功能模块,所需要采用的电路器件技术和成本质量等级存在较大差异。用于栅驱动IC的高压电气隔离技术主要有单片集成隔离技术和物理绝缘隔离技术两大类。其中,单片集成的隔离技术主要为PN结隔离技术,PN结隔离技术常用于实现650V以下的单片集成栅驱动IC产品;物理绝缘隔离技术将高低压信号处理电路在物理空间上隔离开,可实现超过6500V的超高压电气隔离,但是该技术实现栅驱动IC产品必须采用芯片组封装集成,具体实现时可采用变压器、电容或光电耦合进行高低压电路之间隔离区的信号传输。

图2给出了现有技术中一种电容隔离驱动电路架构的示意图,其中,两个信号通信模块:发送端电路与接收端电路各自连接于一接地电压Vgnd1和Vgnd2,其中所设置的隔离电路20旨在将这两个接地电压Vgnd1和Vgnd2隔绝开来。众所周知,DI是电容隔离驱动电路的输入,RO是其输出。在信号的传输过程中,首先,输入DI控制发送端电路产生一组差动信号,通过配置于该发送端电路与接收端电路之间的2组隔离电容,将来自发送端的差动信号耦合至接收端电路,通过信号解调和输出驱动,得到输出信号RO。然而,由于在该两个接地电压Vgnd1和Vgnd2之间通常会存在有一定程度的共模瞬时噪声,将使得信号在传输过程中产生错误。举例来说,两个接地电压之间的尖峰(spike)、电力回路、抑或是任何系统上的缺失都是常见的瞬时噪声因素之一。

如图3所示,共模瞬时噪声形成的干扰波形示意图,在这些数据图标中,共模瞬时噪声V

发明内容

本发明的目的是针对高压绝缘隔离栅驱动芯片的系统应用中不可避免的共模瞬态干扰噪声问题,提供一种具有高共模瞬态噪声抑制特性的差分信号接收电路。

按照本发明提供的技术方案,所述用于高压栅驱动芯片的高共模瞬态抑制差分信号接收电路包括:输入接收电路、X级前后级联的共模可调放大电路、高灵敏度共模可调放大电路、输出整形电路和共模自适应调整电路;所述输入接收电路首先接收正端接收信号RXP和负端接收信号RXN,经滤波处理得到正端输入信号Vip和负端输入信号Vin;正端输入信号Vip和负端输入信号Vin进入X级前后级联的共模可调放大电路中的第一级共模可调放大电路,最终得到第X级共模可调放大电路的正端输出信号VoXp和负端输出信号VoXn;正端输出信号VoXp和负端输出信号VoXn分别连接高灵敏度共模可调放大电路的正输入端和负输入端,高灵敏度共模可调放大电路输出一组差分输出信号,包括正端输出信号VoNp和负端输出信号VoNn;输出整形电路根据正端输出信号VoNp和负端输出信号VoNn的大小,经处理得到最终的输出数据Dout;所述共模自适应调整电路根据电源和地电压信号的变化,自适应产生用于各级放大电路的共模调整信号C11,C12,C21,C22,…,CX1,CX2,共模自适应调整电路产生的共模调整信号C11和C12分别连接到第一级共模可调放大电路的共模调整信号输入端;共模调整信号C21和C22分别连接到第二级共模可调放大电路的共模调整信号输入端;以此类推,共模调整信号CX1和CX2分别连接到第X级共模可调放大电路的共模调整信号输入端;共模自适应调整电路还产生共模调整信号CN1和CN2,分别连接到高灵敏度共模可调放大电路的共模调整信号输入端;其中,X为大于1的正整数,N为大于X的正整数。

具体的,所述输入接收电路包括:正端隔离电容C51、正端接地电阻R51、正端耦合电容C52、正端共模电阻R53、负端隔离电容C53、负端接地电阻R52、负端耦合电容C54、负端共模电阻R54和接收共模产生电路;所述正端隔离电容C51的左端和负端隔离电容C53的左端分别连接到正端接收信号RXP和负端接收信号RXN;正端隔离电容C51的右端连接到正端接地电阻R51的下端和正端耦合电容C52的左端;负端隔离电容C53的右端连接到负端接地电阻R52的下端和负端耦合电容C54的左端;正端耦合电容C52的右端连接到正端共模电阻R53的上端,并作为正端输入信号Vip的输出端;负端耦合电容C54的右端连接到负端共模电阻R54的下端,并作为负端输入信号Vin的输出端;正端共模电阻R53的下端和负端共模电阻R54的上端相连,并同时连接到接收共模产生电路的共模输出端Vicm。

具体的,所述接收共模产生电路包括:NMOS管M60、NMOS管M61、PMOS管M62、NMOS管M63、PMOS管M610、NMOS管M611、PMOS管M612、NMOS管M613、NMOS管M614、PMOS管M615和电阻R61,以及一个施密特触发器;

NMOS管M60的栅极连接到输入共模电压Vcm;NMOS管M60的漏极连接到PMOS管M62的漏极和栅极、以及NMOS管M63的栅极;NMOS管M61的栅极连接到输入共模控制信号Vctrl;NMOS管M61的漏极和NMOS管M63的漏极相连,并连接到所述施密特触发器的输入端;所述施密特触发器的输出端同时连接到PMOS管M610栅极、NMOS管M611栅极、PMOS管M612栅极和NMOS管M613栅极;PMOS管M610的漏极和NMOS管M611的漏极相连,还连接到NMOS管M614的栅极;PMOS管M612的漏极和NMOS管M613的漏极相连,还连接到PMOS管M615的栅极;NMOS管M614的源极和PMOS管M615的源极相连,还作为所述共模输出端Vicm的输出端口;NMOS管M614的漏极连接到高输入共模电平Vcmh,PMOS管M615的漏极连接到低输入共模电平Vcml;NMOS管M613的源极连接到电阻R61的上端;NMOS管M60源极、NMOS管M61源极、NMOS管M611源极和电阻R61的下端同时连接到地电压GND;PMOS管M62源极、NMOS管M63源极和PMOS管M610源极同时连接到电源电压VDD。

具体的,所述接收共模产生电路能够动态跟踪调整共模输出端Vicm的大小;并且采用NMOS管传输所述高输入共模电平Vcmh,采用PMOS管传输所述低输入共模电平Vcml。

具体的,所述高灵敏度共模可调放大电路为前后两级全差分放大电路,包括互相连接的前级共模可调放大电路以及后级的差动差分放大电路;所述前级共模可调放大电路的正输入端即高灵敏度共模可调放大电路的正输入端,前级共模可调放大电路的负输入端即高灵敏度共模可调放大电路的负输入端;差动差分放大电路的正输出端VoNp即高灵敏度共模可调放大电路的正输出端,差动差分放大电路的负输出端VoNn即高灵敏度共模可调放大电路的负输出端。

具体的,所述前级共模可调放大电路的左侧包括:通过漏极串联的PMOS管M81和NMOS管M83;PMOS管M81的源极连接电源VDD,PMOS管M81的栅极和源极之间连接电容C81,PMOS管M81的栅极还连接到偏置电阻R81的上端,PMOS管M81的漏极还连接到偏置电阻R82下端;偏置电阻R81下端和偏置电阻R82上端相连,还作为所述差动差分放大电路第一信号输入端;NMOS管M83的漏极连接PMOS管M81的漏极,还连接到所述差动差分放大电路第三信号输入端;NMOS管M83的栅极连接前级共模可调放大电路的正输入端,接收正端输出信号VoXp;所述前级共模可调放大电路的右侧包括:通过漏极串联的PMOS管M82和NMOS管M84;PMOS管M82的源极连接电源VDD,PMOS管M82的栅极和源极之间连接电容C82,PMOS管M82的栅极还连接到偏置电阻R83的上端,PMOS管M82的漏极还连接到偏置电阻R84下端;偏置电阻R83下端和偏置电阻R84上端相连,还作为所述差动差分放大电路第二信号输入端;NMOS管M84的漏极连接PMOS管M82的漏极,还连接到所述差动差分放大电路第四信号输入端;NMOS管M84的栅极连接前级共模可调放大电路的负输入端,接收负端输出信号VoXn;所述前级共模可调放大电路左右两侧的PMOS管M81和PMOS管M82源极并联,NMOS管M83和NMOS管M84的源极并联;NMOS管M83源极和NMOS管M84源极连接对地NMOS管M85漏极、NMOS管M86漏极和NMOS管M87漏极;对地NMOS管M85栅极连接偏置电压Vb1,提供放大器正常工作所需的偏置电流;NMOS管M86栅极和NMOS管M87栅极分别连接到共模调整信号CN1和CN2。

具体的,所述差动差分放大电路内部包括:PMOS管M88、PMOS管M89、PMOS管M812、PMOS管M813、NMOS管M810、NMOS管M811、NMOS管M814、NMOS管M815和电阻R85;PMOS管M88的栅极为差动差分放大电路第一信号输入端,PMOS管M89的栅极为差动差分放大电路第二信号输入端,PMOS管M812为差动差分放大电路第三信号输入端,PMOS管M813为差动差分放大电路第四信号输入端;PMOS管M88的漏极和PMOS管M89的漏极相连,并连接到NMOS管M810的漏极,同时作为差动差分放大电路的正输出端VoNp;PMOS管M812的漏极和PMOS管M813的漏极相连,并连接到电阻R85的上端;电阻R85的下端连接NMOS管M814的漏极,同时作为差动差分放大电路的负输出端VoNn;NMOS管M810和NMOS管M811构成共源共栅电流源结构,NMOS管M814和NMOS管M815构成共源共栅电流源结构,NMOS管M810和NMOS管M814的栅极接相同的偏置电压Vb81,NMOS管M811和NMOS管M815的栅极接相同的偏置电压Vb82。

具体的,所述输出整形电路包括依次连接的三级比较器、带RC滤波功能的缓冲器、施密特触发器和输出反相器,输出反相器的输出端即为最终的输出数据Dout;所述带RC滤波功能的缓冲器内部电路连接关系为:PMOS管M41栅极和NMOS管M42栅极同时连接到三级比较器的比较输出电压,PMOS管M41漏极和NMOS管M42漏极同时连接到PMOS管M43栅极和NMOS管M44栅极,PMOS管M43的漏极连接到电阻R41的上端,电阻R41的下端连接到电阻R42的上端、电容C41的上端和施密特触发器的输入端,电阻R42的下端连接到NMOS管M44的漏极,PMOS管M41源极和PMOS管M43源极同时连接到电源电压VCC,NMOS管M42源极和NMOS管M44源极以及电容C41的下端同时连接到地电压GND。

具体的,所述共模自适应调整电路包括:共模检测电路、共模检测信号传输电路、调整共模信号产生电路和共模调整信号选择电路;所述共模检测电路用于检测电源和衬底噪声,并在噪声大于阈值时改变共模检测信号Vcm_det的大小,共模检测信号Vcm_det连接到共模检测信号传输电路,经过共模检测信号传输电路产生共模选择开关控制信号N11,N12,N21,N22,…,NX1、NX2以及NN1,NN2,并输出到共模调整信号选择电路;共模调整信号选择电路根据上述共模选择开关控制信号产生和调整共模调整信号C11,C12,C21,C22,…,CX1,CX2以及CN1,CN2的大小并输出;调整共模信号产生电路用于产生共模调整信号选择电路需要的各类共模偏置信号,并输出到共模调整信号选择电路。

具体的,所述共模检测电路包括:PMOS管M111、PMOS管M112和NMOS管M113;其中,PMOS管M111的栅极和漏极相连,并连接到PMOS管M112的漏极和NMOS管M113的栅极;PMOS管M112的栅极和NMOS管M113的漏极相连,并作为共模检测信号Vcm_det的输出节点;PMOS管M111和PMOS管M112的源极连接电源电压VDD,NMOS管M113的源极连接到地电压GND。

本发明的优点是:本发明所提供的高共模瞬态抑制差分信号接收电路,一方面,可自动检测地电位共模瞬态噪声的大小,并在噪声超过阈值时对共模瞬态噪声产生的误差进行动态补偿。另一方面,输出整形电路进一步采用RC低通滤波和施密特触发器组合滤波,以滤除高频噪声的影响,从而产生稳定数据输出。本发明可以广泛应用于各类高压绝缘隔离栅驱动芯片和数据隔离器中。

附图说明

图1为一种典型半桥栅驱动电路及应用系统结构图。

图2为一种电容隔离驱动电路架构的示意图。

图3为电容隔离驱动电路共模瞬时干扰波形示意图。

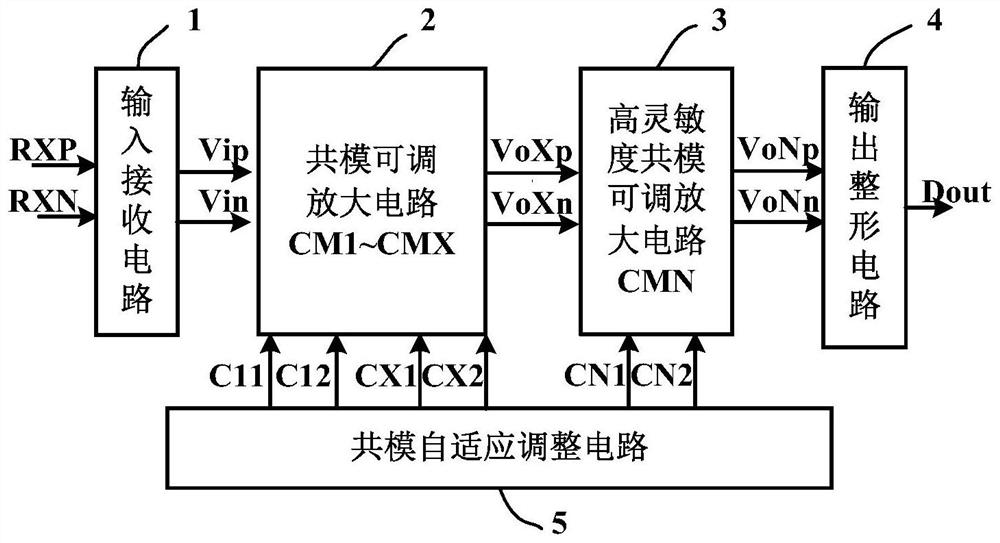

图4为本发明高共模瞬态抑制差分信号接收电路总体框图。

图5为本发明输入接收电路的一种实施例。

图6为本发明接收共模产生电路的一种实施例。

图7为本发明共模可调放大电路的一个级联单元。

图8为本发明高灵敏度共模可调放大电路的一种实施例。

图9为本发明输出整形电路的一种实施例。

图10为本发明共模自适应调整电路实施例。

图11为图10中共模检测电路的一种实施例。

图12为图11所示电路的工作波形。

具体实施方式

下面结合附图和实施例对本发明进行进一步详细的说明。

如图4所示,本发明的电路结构包括:输入接收电路1、X级前后级联的共模可调放大电路2(CM1~CMX)、高灵敏度共模可调放大电路3(CMN)、输出整形电路4和共模自适应调整电路5。

输入接收电路1首先接收到图2中所示发送电路通过隔离电容耦合进来的差分信号正端接收信号RXP和负端接收信号RXN,经滤波处理得到正端输入信号Vip和负端输入信号Vin;正端输入信号Vip和负端输入信号Vin然后进入X级前后级联的共模可调放大电路2(CM1~CMX),得到第X级共模可调放大电路CMX的正端输出信号VoXp和负端输出信号VoXn;正端输出信号VoXp和负端输出信号VoXn分别连接高灵敏度共模可调放大电路3的正输入端和负输入端,得到高灵敏度共模可调放大电路3的差分输出信号正端输出信号VoXp和负端输出信号VoXn;输出整形电路4根据正端输出信号VoXp和负端输出信号VoXn的大小,经处理得到最终的数据输出Dout。所述共模自适应调整电路5根据电源和地电压信号的变化,自适应产生用于各级放大电路和高灵敏度共模可调放大电路3的共模调整信号C11,C12,C21,C22,…,CX1,CX2,CN1,CN2,共模自适应调整电路5产生的共模调整信号C11和共模调整信号C12分别连接到第一级共模可调放大电路CM1的共模调整信号输入端;共模调整信号C21和共模调整信号C22分别连接到第二级共模可调放大电路CM2的共模调整信号输入端;……以此类推,共模调整信号CX1和共模调整信号CX2分别连接到第X级共模可调放大电路CMX的共模调整信号输入端;共模调整信号CN1和共模调整信号CN2分别连接到高灵敏度共模可调放大电路3(CMN)的共模调整信号输入端。其中,X为大于1的正整数,N为大于X的正整数。

图4所述共模自适应调整电路5内部自动检测电源电压VDD和地电位Vgnd波动引起的瞬态共模噪声大小,并在瞬态共模噪声超过一定阈值时,调整共模调整信号C11,C12,C21,C22,…,CX1,CX2,CN1,CN2的值并对应输出给X级前后级联的共模可调放大电路CM1~CMX和高灵敏度共模可调放大电路3(CMN),从而调整X级前后级联的共模可调放大电路CM1~CMX和高灵敏度共模可调放大电路3的共模电平,使之补偿瞬态共模噪声的影响。除共模自适应调整之外,本发明还采用了高可靠输出整形电路4,采用RC低通滤波和施密特触发器组合滤波,以滤除高频噪声的影响,最终得到不受瞬态共模噪声影响的数据输出Dout。

图5为本发明输入接收电路1的一种实现方式,该电路由正端隔离电容C51、正端接地电阻R51、正端耦合电容C52、正端共模电阻R53、负端隔离电容C53、负端接地电阻R52、负端耦合电容C54、负端共模电阻R54和接收共模产生电路101构成。所述正端隔离电容C51的左端和负端隔离电容C53的左端分别连接到正端接收信号RXP和负端接收信号RXN;正端隔离电容C51的右端连接到正端接地电阻R51的下端和正端耦合电容C52的左端;负端隔离电容C53的右端连接到负端接地电阻R52的下端和负端耦合电容C54的左端;正端耦合电容C52的右端连接到正端共模电阻R53的上端,并作为正端输入信号Vip的输出端;负端耦合电容C54的右端连接到负端共模电阻R54的下端,并作为负端输入信号Vin的输出端;正端共模电阻R53的下端和负端共模电阻R54的上端相连,并同时连接到接收共模产生电路101的共模输出端Vicm。

图5所述电路中正端隔离电容C51和负端隔离电容C53均为高压电容,电容尺寸通常达到几十fp;正端耦合电容C52和负端耦合电容C54均为低压电容,其电容值也相对较小。正端接收信号RXP和负端接收信号RXN从输入到输出,经过2级隔直耦合滤波,得到正端输入信号Vip和负端输入信号Vin。正端输入信号Vip和负端输入信号Vin的共模电平,由接收共模产生电路101提供。

图6为本发明接收共模产生电路101的一种实现方式。该电路包括NMOS管M60、NMOS管M61、PMOS管M62、NMOS管M63、PMOS管M64、PMOS管M65、NMOS管M66、NMOS管M67、PMOS管M68、NMOS管M69、PMOS管M610、NMOS管M611、PMOS管M612、NMOS管M613、NMOS管M614、PMOS管M615和电阻R61。其中,PMOS管M64、PMOS管M65、NMOS管M66、NMOS管M67、PMOS管M68和NMOS管M69构成施密特触发器600。

NMOS管M60的栅极连接到输入共模电压Vcm;NMOS管M60的漏极连接到PMOS管M62的漏极和栅极、以及NMOS管M63的栅极;NMOS管M61的栅极连接到输入共模控制信号Vctrl;NMOS管M61的漏极和NMOS管M63的漏极相连,并连接到所述施密特触发器600的输入端;施密特触发器600的输出端同时连接到PMOS管M610、NMOS管M611、PMOS管M612和NMOS管M613的栅极;PMOS管M610的漏极和NMOS管M611的漏极相连,还连接到NMOS管M614的栅极;PMOS管M612的漏极和NMOS管M613的漏极相连,还连接到PMOS管M615的栅极;NMOS管M614的源极和PMOS管M615的源极相连,还作为所述共模输出端Vicm的输出端口;NMOS管M614的漏极连接到高输入共模电平Vcmh,PMOS管M615的漏极连接到低输入共模电平Vcml;NMOS管M613的源极连接到电阻R61的上端;NMOS管M60的源极、NMOS管M61的源极、NMOS管M611的源极和电阻R61的下端,同时连接到地电压GND;PMOS管M62的源极、NMOS管M63的源极、PMOS管M64的源极和PMOS管M610的源极同时连接到电源电压VDD。

图6所示电路的功能在于根据输入共模电压Vcm的变化,动态跟踪调整共模输出端Vicm的大小,减小输入共模电压的影响。假设输入共模Vcm减小,则施密特触发器600的输入端将会同步减小,假设该波动超过施密特触发器600的阈值,则施密特触发器600输出将会变为高电平,PMOS管M615将会导通,共模输出端Vicm将输出低输入共模电平Vcml,使之匹配和输入共模变化;假设输入共模Vcm增大,并超过施密特触发器600的阈值,则NMOS管M614导通,共模输出端Vicm将输出高输入共模电平Vcmh;可以看出,对于不同的输入共模波动,图6电路均可以实现输入共模变化的动态补偿。图6所示电路中,为使共模输出端Vicm更好的实现共模信号输出,采用NMOS管传输高输入共模电平Vcmh,采用PMOS管传输低输入共模电平Vcml。

图7为本发明共模可调放大电路2的一个级联单元的一种实现方式。该电路为全差分单级放大电路。该电路左侧包括:通过漏极串联的PMOS管M71和NMOS管M73;所述PMOS管M71的源极连接电源VDD,PMOS管M71的栅极和源极之间连接电容C71,PMOS管的栅极和漏极之间连接偏置电阻R71;所述NMOS管M73的漏极输出负端输出信号Vo1n连接到下一个级联单元的负输入端(第二个级联单元输出负端输出信号Vo2n到下一个级联单元,以此类推),NMOS管M73的栅极连接共模可调放大电路2的正输入端Vip;该电路的右侧包括:通过漏极串联的PMOS管M72和NMOS管M74;所述PMOS管M72的源极连接电源VDD,PMOS管M72的栅极和源极之间连接电容C72,PMOS管M72的栅极和漏极之间连接偏置电阻R72;所述NMOS管M74的漏极输出正端输出信号Vo1p到下一个级联单元的正输入端(第二个级联单元输出正端输出信号Vo2p到下一个级联单元,以此类推),NMOS管M74的栅极连接共模可调放大电路2的负输入端Vin;所述放大电路两侧的PMOS管M71和PMOS管M72源极并联,NMOS管M73和NMOS管M74的源极并联;所述NMOS管M73和NMOS管M74的源极连接对地NMOS管M75、NMOS管M76和NMOS管M77的漏极;所述对地NMOS管M75的栅极连接偏置电压Vb1,提供放大器正常工作所需的偏置电流;所述NMOS管M76和NMOS管M77的栅极分别连接到共模调整信号C11和C12。

通过改变共模调整信号C11和C12的大小,流过NMOS管M73和NMOS管M74的偏置电流就会发生改变,图7所示级联单元的负端输出信号Vo1n和正端输出信号Vo1p的输出电压就会对应的同时发生改变,从而实现输出共模电压的调整。本发明采用多级如图7所示的相同的共模可调放大电路前后级联,由第X级共模可调放大电路CMX输出正端输出信号VoXp和负端输出信号VoXn,最终实现共模噪声的动态补偿。

图8为本发明高灵敏度共模可调放大电路3的一种实现方式。该电路为前后两级全差分放大电路,前级共模可调放大电路采用和图7类似的放大电路结构,后级放大电路为差动差分放大电路(DDA)。前级共模可调放大电路的正输入端即高灵敏度共模可调放大电路3的正输入端,前级共模可调放大电路的负输入端即高灵敏度共模可调放大电路3的负输入端;所述差动差分放大电路的正输出端VoNp即高灵敏度共模可调放大电路3的正输出端,差动差分放大电路的负输出端VoNn即高灵敏度共模可调放大电路3的负输出端。

所述前级共模可调放大电路的左侧包括:通过漏极串联的PMOS管M81和NMOS管M83;所述PMOS管M81的源极连接电源VDD,PMOS管M81的栅极和源极之间连接电容C81,PMOS管M81的栅极还连接到偏置电阻R81的上端,PMOS管M81的漏极还连接到偏置电阻R82下端;所述偏置电阻R81下端和偏置电阻R82上端相连,还作为所述差动差分放大电路第一信号输入端;所述NMOS管M83的漏极连接PMOS管M81的漏极,还连接到所述差动差分放大电路第三信号输入端;NMOS管M83的栅极连接前级共模可调放大电路的正输入端VoXp;该电路的右侧包括:通过漏极串联的PMOS管M82和NMOS管M84;所述PMOS管M82的源极连接电源VDD,PMOS管M82的栅极和源极之间连接电容C82,PMOS管M82的栅极还连接到偏置电阻R83的上端,PMOS管M82的漏极还连接到偏置电阻R84下端;所述偏置电阻R83下端和偏置电阻R84上端相连,还作为所述差动差分放大电路第二信号输入端;所述NMOS管M84的漏极连接PMOS管M82的漏极,还连接到所述差动差分放大电路第四信号输入端;NMOS管M84的栅极连接前级共模可调放大电路的负输入端VoXn;所述放大电路两侧的PMOS管M81和PMOS管M82源极并联,NMOS管M83和NMOS管M84的源极并联;所述NMOS管M83和NMOS管M84的源极连接对地NMOS管M85、NMOS管M86和NMOS管M87的漏极;所述对地NMOS管M85的栅极连接偏置电压Vb1,提供放大器正常工作所需的偏置电流;所述NMOS管M86和NMOS管M87的栅极分别连接到共模调整信号CN1和CN2。

所述差动差分放大电路内部包括:PMOS管M88、PMOS管M89、PMOS管M812、PMOS管M813、NMOS管M810、NMOS管M811、NMOS管M814、NMOS管M815和电阻R85;所述PMOS管M88的栅极为差动差分放大电路第一信号输入端,PMOS管M89的栅极为差动差分放大电路第二信号输入端,PMOS管M812为差动差分放大电路第三信号输入端,PMOS管M813为差动差分放大电路第四信号输入端;PMOS管M88的漏极和PMOS管M89的漏极相连,并连接到NMOS管M810的漏极,同时作为差动差分放大电路的正输出端VoNp;PMOS管M812的漏极和PMOS管M813的漏极相连,并连接到电阻R85的上端;电阻R85的下端连接NMOS管M814的漏极,同时作为差动差分放大电路的负输出端VoNn;NMOS管M810和NMOS管M811构成共源共栅电流源结构,NMOS管M814和NMOS管M815构成共源共栅电流源结构,NMOS管M810和NMOS管M814的栅极接相同的偏置电压Vb81,NMOS管M811和NMOS管M815的栅极接相同的偏置电压Vb82。

图9为本发明输出整形电路4实现方式,包括PMOS管M401、PMOS管M402、PMOS管M403、PMOS管M404、PMOS管M405、PMOS管M406、PMOS管M409、NMOS管M407、NMOS管M408、NMOS管M4010、电阻R401、电阻R402、PMOS管M41、PMOS管M43、PMOS管M45、PMOS管M46、PMOS管M49、PMOS管M411、NMOS管M42、NMOS管M44、NMOS管M47、NMOS管M48、NMOS管M410、NMOS管M412、电阻R41、电阻R42和电容C41。

其中,PMOS管M401、PMOS管M402、PMOS管M403、PMOS管M404、PMOS管M405、PMOS管M406、PMOS管M409、NMOS管M407、NMOS管M408、NMOS管M4010、电阻R401和电阻R402构成三级比较器;PMOS管M41、PMOS管M43、NMOS管M42、NMOS管M44、电阻R41、电阻R42和电容C41组成一个带RC滤波功能的缓冲器;PMOS管M45、PMOS管M46、PMOS管M49、NMOS管M47、NMOS管M48、NMOS管M410组成一个施密特触发器;PMOS管M411和NMOS管M412组成一个输出反相器。所述带RC滤波功能的缓冲器的输入端连接到所述宽电压范围比较器电路的比较输出电压Vo1,带RC滤波功能的缓冲器的输出端连接到施密特触发器的输入端,施密特触发器的输出端连接到输出反相器的输入端,输出反相器的输出端即为所述用于高压栅驱动芯片的高共模瞬态抑制差分信号接收电路最终的数据输出Dout。

所述三级比较器内部电路结构为:PMOS管M401、PMOS管M402、PMOS管M403、电阻R401和电阻R402组成三级比较器的输入级,PMOS管M404、PMOS管M405、PMOS管M406、NMOS管M407、NMOS管M408组成三级比较器的放大级,PMOS管M409和NMOS管M4010组成三级比较器的输出级;所述带RC滤波功能的缓冲器内部电路连接关系为:PMOS管M41和NMOS管M42的栅极同时连接到所述三级比较器的比较输出电压,PMOS管M41和NMOS管M42的漏极同时连接到PMOS管M43和NMOS管M44的栅极,PMOS管M43的漏极连接到电阻R41的上端,电阻R41的下端连接到电阻R42的上端、电容C41的上端和施密特触发器的输入端,电阻R42的下端连接到NMOS管M44的漏极,PMOS管M41和PMOS管M43的同时源极连接到电源电压VCC,NMOS管M42和NMOS管M44的源极以及电容C41的下端同时连接到地电压GND。

图9所述的本发明输出整形电路4,一方面是提供了三级比较器将输入差分信号转换成一个标准的数字逻辑信号Dout;另外一方面采用RC低通滤波和施密特触发器组合滤波,保持了一定的迟滞量是为了有效滤除共模噪声引起的高频干扰影响。

图10为本发明共模自适应调整电路5的具体实现方式,该电路包括共模检测电路500、共模检测信号传输电路501、调整共模信号产生电路502和共模调整信号选择电路503。所述共模检测电路500用于检测电源和衬底噪声,并在噪声大于一定阈值时改变共模检测信号Vcm_det的大小,共模检测信号Vcm_det连接到共模检测信号传输电路501,Vcm_det经过共模检测信号传输电路501产生共模选择开关控制信号N11,N12,N21,N22,…,NX1、NX2以及NN1,NN2,并输出到共模调整信号选择电路503;共模调整信号选择电路503根据上述共模选择开关控制信号产生和调整共模调整信号C11,C12,C21,C22,…,CX1,CX2以及CN1,CN2的大小并输出;调整共模信号产生电路502用于产生共模调整信号选择电路503需要的各类共模偏置信号,并输出到共模调整信号选择电路503。

图10所示的电路中,所述共模检测信号传输电路501采用分布式的反相器链实现,共模检测信号Vcm_det经过分布式的N组反相器链传播,得到N组共模控制信号。所述调整共模信号产生电路502由电源电压VDD到地电压GND的一条偏置信号通路,产生高输入共模电平Vcmh和低输入共模电平Vcml。对于Vcmh和Vcml的实现方式,图中给出的是一种硬件开销最小的实现方式,采用基准电压分压或者LDO等其他电路同样可以实现相同功能,在此不再描述。所述共模调整信号选择电路503其内部电路为开关选择阵列,开关阵列根据共模选择开关控制信号N11,N12,N21,N22,…,NX1、NX2以及NN1,NN2的值,决定共模调整信号C11,C12,C21,C22,…,CX1,CX2以及CN1,CN2的输出。

图11为本发明共模检测电路500实现方式。所述共模检测电路500用于检测电源和衬底噪声,并在噪声大于一定阈值时改变共模检测信号Vcm_det的大小,以控制图10中给出的共模自适应调整电路5的输出。所述共模检测电路500由PMOS管M111、PMOS管M112和NMOS管M113构成;其中,PMOS管M111的栅极和漏极相连,并连接到PMOS管M112的漏极和NMOS管M113的栅极;PMOS管M112的栅极和NMOS管M113的漏极相连,并作为共模检测信号Vcm_det的输出节点;PMOS管M111和PMOS管M112的源极连接电源电压VDD,NMOS管M113的源极连接到地电压GND。

图12中给出了所述共模检测电路500的工作波形示意图。假设电路工作在半桥驱动的高侧电路中,则GND连接到半桥输出SW,因此需要在0和VH之间摆动;高侧电路的电源电压VDD是自举电压VHB,由自举电容在SW电位基础上自举浮动,故正常工作时VDD=VHB=SW+VCC。由于电容自举充电也需要一定的充电时间,在电容充电过程中,VHB不能完全同步SW的波动,这势必导VHB相对SW存在一定的延时,在延时区间内电源和地之间的压差不严格等于VCC,相当于电源共模噪声,该噪声幅度足够大时势必影响电路功能,产生比较器的误触发。

如图12所示波形,在半桥输出SW稳定时,VDD和GND电压处于稳定状态,M111导通,M113导通,Vcm_det将会被M113拉低到GND,处于低电平;当半桥输出SW由0向VH切换时,GND电压同步向VH切换,但是VDD存在一定延时,产生一定的延时区间,在延时区间内VDD还未达到VH+VCC,M113的栅极电压不足以让M113导通,M113将关闭,在寄生电容的作用下Vcm_det将会受GND影响产生一个尖峰高脉冲,直到VDD达到VH+VCC,此时M113重新导通,Vcm_det将会被M113拉低到GND。

以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 用于高压栅驱动芯片的高共模瞬态抑制差分信号接收电路

- 用于高压栅驱动芯片的高精度输入信号接收电路