一种用于共源共栅射频低噪声放大器共栅管的偏置电路

文献发布时间:2023-06-19 11:49:09

技术领域

本发明属于无线通信技术领域,具体涉及一种用于共源共栅射频低噪声放大器共栅管的偏置电路。

背景技术

目前,在传统共源共栅射频低噪声放大器中,对共栅管偏置电压常采用由晶体管或电阻对电源电压进行分压的方法产生,但该分压电压随电源电压变化,随着集成电路工艺的发展,晶体管沟道长度缩减,沟道长度调制效应导致共源共栅组态共源管电流受共栅管阈值电压及栅极电压的影响较大,进而射频放大器静态电流量产表现一致性较差,为了保证放大器偏置电流一致性,有技术手段采用数字Fuse电流对电流进行校准修调,导致芯片集成成本和测试成本较高。

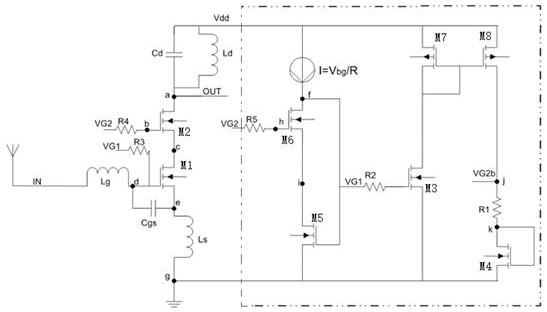

如图1所示,由第五MOS管M5,第六MOS管M6,第五电阻R5,电流源I及电阻Ra、Rb构成传统放大器偏置电路,传统方式下,VG2c连接到VG2作为共栅管的偏置电压,

在此偏置条件下

Vce=Vdd*(Rb/(Ra+Rb))-Vod_M2-Vth_M2-Veg

Vig=Vdd*(Rb/(Ra+Rb))-Vod_M6-Vth_M6

Vod_M2/Vth_M2分别为第二MOS管M2的过驱动电压和阈值电压,Veg接近0V。

Vod_M6/Vth_M6分别为第六MOS管M6的过驱动电压和阈值电压。

若电源电压Vdd变化或第二MOS管M2,第六MOS管M6阈值电压发生变化时,第一MOS管M1的漏源电压Vce就会发生变化,第五MOS管M5管的漏源电压Vig就会发生变化,在短沟道效应下,第一MOS管M1,第五MOS管M5的漏源电压变化会显著影响到其偏置电流大小,从而使得放大器增益,噪声系数及线性度发生较大变化,超出设计指标范围。

发明内容

本发明的目的是提供一种用于共源共栅射频低噪声放大器共栅管的偏置电路,以解决现有技术中由于沟道长度调制效应导致共源共栅组态共源管电流受共栅管阈值电压及栅极电压的影响较大,进而射频放大器静态电流量产表现一致性较差的问题。

为实现上述目的,本发明采用的技术方案为:一种用于共源共栅射频低噪声放大器共栅管的偏置电路,包括共源共栅射频低噪声放大器发大电路,还包括偏置电压产生电路,该电路包括电流源I、第六MOS管M6、第五MOS管M5、第三MOS管M3、第四MOS管M4、第七MOS管M7、第八MOS管M8、第一电阻R1,第五电阻R5、第二电阻R2,电源电压Vdd经电流源I与第六MOS管M6的漏极相连接,第六MOS管M6的栅极通过第五电阻R5耦合到电压源VG2以接收偏置电压,第六MOS管M6的源极与第五MOS管M5的漏极相连,第五MOS管M5的源极接地,第五MOS管M5的栅极与第六MOS管M6的漏极相连后输出第一电压VG1,第一电压VG1通过第二电阻R2与第三MOS管M3的栅极相连,第三MOS管M3的源极、第四MOS管M4源极接地,第三MOS管M3的漏极与第七MOS管M7的源极相连,第四MOS管M4的漏极通过与第一电阻R1与第八MOS管M8的源极相连后输出第二电压VG2b,第七MOS管M7、第八MOS管M8的漏极连接电源电压Vdd,第七MOS管M7、第八MOS管M8的栅极相连。

进一步地,所述第三MOS管M3、第四MOS管M4、第五MOS管M5、第六MOS管M6为NMOS管。

进一步地,第七MOS管M7、第八MOS管M8为PMOS管。

本发明的有益效果为:采用一电流源的电流流入由电阻和MOS管组合系统产生一个偏置电压的方式来给共栅管做偏置电压,可以大大减小放大器静态电流随电源电压,电阻及MOS器件不同批次阈值变化引起的变化,改善放大器各项特性的稳定性。

附图说明

图1是现有技术共源共栅射频低噪声放大器共栅管偏置电路图;

图2是本发明一种用于共源共栅射频低噪声放大器共栅管的偏置电路图。

具体实施方式

下面结合附图对本发明做进一步的详细描述。

如图2所示,一种用于共源共栅射频低噪声放大器共栅管的偏置电路,包括由第一MOS管M1、第二MOS管M2、电感Lg、Ls、Ld,电容Cgs、Cd,第三电阻R3、第四电阻R4、第五电阻R5构成的共源共栅射频低噪声放大器发大电路,还包括偏置电压产生电路,该电路包括电流源I、第六MOS管M6、第五MOS管M5、第三MOS管M3、第四MOS管M4、第七MOS管M7、第八MOS管M8、第一电阻R1,第五电阻R5、第二电阻R2,电源电压Vdd经电流源I与第六MOS管M6的漏极相连接,第六MOS管M6的栅极通过第五电阻R5耦合到电压源VG2以接收偏置电压,第六MOS管M6的源极与第五MOS管M5的漏极相连,第五MOS管M5的源极接地,第五MOS管M5的栅极与第六MOS管M6的漏极相连后输出第一电压VG1,第一电压VG1通过第二电阻R2与第三MOS管M3的栅极相连,第三MOS管M3的源极、第四MOS管M4源极接地,第三MOS管M3的漏极与第七MOS管M7的源极相连,第四MOS管M4的漏极通过与第一电阻R1与第八MOS管M8的源极相连后输出第二电压VG2b,第七MOS管M7、第八MOS管M8的漏极连接电源电压Vdd,第七MOS管M7、第八MOS管M8的栅极相连。

本发明偏置电压产生电路包括第一级NMOS放大管(共源管)的偏置电压产生电路和第二级NMOS管(共栅管)的偏置电压产生电路,第二级共栅管的偏置电压产生电路可以减小第一级共源管的偏置电压产生电路电流随电源电压Vdd,电阻,MOS管工艺角的变化。

由第三MOS管M3、第四MOS管M4、第七MOS管M7、第八MOS管M8和第一电阻R1、第二电阻R2组成的电路产生的电压VG2b替代由传统放大器偏置电路中产生的电压VG2c,将电压VG2b连接到VG2作为放大器共栅管的偏置电压。

在本发明提供的偏置电路中

Vce=Vbg*R1/Rb+Vod_M4+Vth_M4-Vod_MN2-Vth_MN2-Veg

Vig=Vbg*R1/Rb+Vod_M4+Vth_M4-Vod_MN6-Vth_MN6

Vbg为基准电压,Vod_M4、Vth_M4分别为第四MOS管M4的过驱动电压和阈值电压,由于同种类型的器件阈值电压在一阶近似时理想条件下相等,故电压公式变为如下:

Vce=Vbg*R1/Rb+Vod_M4-Vod_MN2-Veg

Vig=Vbg*R1/Rb+Vod_M4-Vod_M6

由于器件的过驱动电压取决于其偏置电流和尺寸,故第一MOS管M1的漏源电压Vce,第五MOS管M5的漏源电压Vig和电源电压Vdd,电阻及器件本身的阈值电压无关,在短沟道器件应用中,本发明偏置电压产生电路可以大大减小放大器静态电流随电源电压,电阻及MOS器件不同批次阈值变化引起的变化,改善放大器各项特性的稳定性。

本发明的工作原理是:外部偏置电流经过第五MOS管M5/第三MOS管M3及第七MOS管M7/第八MOS管M8镜像后流入第一电阻R1和第四MOS管M4产生电压VG2b,该电压直接连到VG2上作为放大器共栅管第二MOS管M2的偏置电压,从而保证该管栅极电压随MOS管阈值电压变化而变化,也消除了偏置电流产生电阻变化引起的变化,使得第一MOS管M1漏端c的电压不随MOS管阈值和电阻R的变化而变化,保证了放大器电路偏置状态的稳定性,从而使其性能稳定性提高。

本发明在应用时可以将相应的MOS器件替换为对等的BJT器件。

以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 一种用于共源共栅射频低噪声放大器共栅管的偏置电路

- 一种具有输出阻抗自调节功能的MOS管共栅共源电流源偏置电路