一种多通道数据采集控制电路

文献发布时间:2023-06-19 11:49:09

技术领域

本申请涉及震动监测数据采集技术领域,更具体地,涉及一种多通道数据采集控制电路。

背景技术

现有的基于网络端口的数据采集监控主控制电路,一般能接入5-8台数据采集设备,并且每台数据采集设备为三通道数据,故采集监控主控制电路接入能力低、接入数据量小,数据采集效率低,无法满足大型监控系统需求。

因此,如何提供一种可以进一步提高数据采集效率的数据采集控制电路,是目前亟待解决的技术问题。

发明内容

本发明提供一种多通道数据采集控制电路,用以解决现有技术中数据采集控制电路接入能力低,接入数据量小的技术问题。

所述电路包括:

网络端口单元,包括第一扩展网口单元和第二扩展网口单元,用于通过所述第一扩展网口单元和所述第二扩展网口单元接入数据采集设备;

通讯端口单元,用于将所述数据采集设备采集的数据发送到数据接收设备;

串口单元,用于提供UART端口;

存储单元,用于基于大容量存储介质进行数据存储;

时钟管理单元,用于接收网络授时信号;

芯片U1,用于对所述网络端口单元、所述通讯端口单元、所述串口单元、所述存储单元和所述时钟管理单元进行管理;

其中,所述网络端口单元、所述通讯端口单元、所述串口单元、所述存储单元和所述时钟管理单元分别与所述主控制芯片U1连接。

在本申请一些实施例中,所述第一扩展网口单元包括芯片U4、电感L2、电容C20、电容C21、电容C22、电容C23、电容C24、电容C26、电阻R12、电阻R13、电阻R14、电阻R15、电阻R16、电阻R17、电阻R18、电阻R19、电阻R20、电阻R21、电阻R22、电阻R23、电阻R24、电阻R25、电阻R26、电阻R27、电阻R28、电阻R29、电阻R30和接插件J5,其中,

芯片U1的F14管脚连接电阻R19的一端,电阻R19的另一端连接芯片U4的32管脚,芯片U4的32管脚连接电容C24一端和电阻R18的一端,电容C24的另一端接地,电阻R18的另一端接3.3V电源,芯片U1的G13管脚连接芯片U4的21管脚,芯片U4的21管脚连接电阻R24的一端,电阻R24的另一端连接3.3V电源,芯片U1的A7管脚接芯片U4的12管脚,芯片U1的C7管脚接芯片U4的11管脚,芯片U4的11管脚还连接电阻R12的一端和电阻R13的一端,电阻R12的另一端和电阻R13的另一端接3.3V电源,芯片U1的E12管脚接芯片U4的16管脚,芯片U1的D12管脚接芯片U4的15管脚,芯片U1的C12管脚连接电阻R26的一端和地,电阻R26的另一端接芯片U4的18管脚,芯片U1的B12管脚接芯片U4的24管脚,芯片U1的A12管脚接芯片U4的25管脚,芯片U1的A13管脚接芯片U4的23管脚,芯片U1的B13管脚接芯片U4的9管脚,芯片U1的C13管脚接芯片U4的20管脚,芯片U4的20管脚接电阻R25的一端,电阻R25的另一端接3.3V电源,芯片U4的4管脚连接接插件J5的4管脚和电阻R30的一端,芯片U4的5管脚连接接插件J5的3管脚和电阻R29的一端,芯片U4的6管脚连接接插件J5的2管脚和电阻R28的一端,芯片U4的7管脚连接接插件J5的1管脚和电阻R27的一端,电阻R27另一端、电阻R28另一端、电阻R29另一端、电阻R30另一端连接3.3V电源,芯片U4的1管脚接地,芯片U4的2管脚连接电容C22的一端和电容C23的一端,电容C22的另一端和电容C23的另一端接地,芯片U4的3管脚连接电感L2的一端、电容C20的一端和电容C21的一端,电感L2的另一端接3.3V电源,电容C20的另一端和电容C21的另一端接地,芯片U4的10脚连接电阻R14的一端,电阻R14的另一端接地,芯片U4的13管脚接电阻R15的一端,电阻R15的另一端接地,芯片U4的14管脚接电阻R16的一端,电阻R16的另一端接3.3V电源,芯片U4的15管脚接电阻R17一端,电阻R17的另一端接地, 芯片U4的17管脚连接电容C26一端和3.3V电源,电容C26的另一端接地,芯片U4的28管脚连接电阻R23一端,电阻R23另一端接地,芯片U4的29管脚连接电阻R22的一端,电阻R22的另一端接3.3V电源,芯片U4的30管脚接电阻R21一端,芯片U4的31管脚接电阻R20的一端,电阻R20的另一端和电阻R21的另一端均接地,芯片U4的33管脚接地,

其中,芯片U4采用KSZ8081RNB模块,或W5500芯片、或W5100芯片、或INtel 82571芯片、或INtel 82572芯片、或INtel 82573芯片。

在本申请一些实施例中,所述第二扩展网口单元包括芯片U3、电阻R7、电阻R8、电容C7、电容C8、接插件J3和接插件J4,其中,

芯片U1的M14管脚连接电阻R8的一端,电阻R8另一端连接芯片U3的11管脚,芯片U1的L13管脚接芯片U3的8管脚,芯片U3的8管脚连接电阻R7的一端,电阻R7的另一端接3.3V电源,芯片U1的J13管脚接芯片U3的9管脚,芯片U3的10管脚接地,芯片U3的12管脚连接3.3V电源及电容C7的一端、电容C8的一端,电容C7的另一端、电容C8的另一端均接地,芯片U3的6管脚接接插件J3的1管脚,接插件J3的2管脚接地,芯片U3的TX+脚连接接插件J4的1管脚,芯片U3的TX-脚连接接插件J4的2管脚,芯片U3的RX+脚连接接插件J4的3管脚,芯片U3的RX-脚连接接插件J4的4管脚,

其中,芯片U3采用USR-K3模块、或USR-K1模块、或USR-K2模块、或USR-K4模块。

在本申请一些实施例中,所述通讯端口单元包括接插件J2,其中,

芯片U1的L3管脚连接接插件J2的4管脚,芯片U1的L4管脚接接插件J2的5管脚,芯片U1的P3管脚接接插件J2的2管脚,芯片U1的N4管脚接接插件J2的3管脚,接插件J2的1管脚和6管脚接地。

在本申请一些实施例中,所述串口单元包括电阻R3和接插件J1,其中,

芯片U1的P4管脚连接接插件J1的3管脚,接插件J1的3管脚连接电阻R3的一端,电阻R3的另一端连接3.3V电源,芯片U1的P5管脚连接接插件J1的1管脚,接插件J1的2管脚接地。

在本申请一些实施例中,所述存储单元包括芯片U6、电容C29、电容C30、电容C31、电阻R2、电阻R33、电阻R34、电阻R35、电阻R36和三极管Q1,其中,

芯片U1的J1管脚连接芯片U6的7管脚,芯片U1的K1管脚连接芯片U6的8管脚,芯片U1的H2管脚连接芯片U6的1管脚,芯片U1的J2管脚连接芯片U6的2管脚,芯片U1的J3管脚连接电阻R33的一端,电阻R33的另一端连接芯片U6的5管脚,芯片U1的J4管脚连接芯片U6的3管脚和电阻R2的一端,电阻R2的另一端连接3.3V电源,芯片U6的4管脚连接3.3电源、电容C29的一端、电容C30的一端和电容C31的一端,电容C29的另一端、电容C30另一端和电容C31的另一端均接地,芯片U6的9管脚接电阻R34的一端和三极管Q1的b管脚,电阻R34的另一端接3.3V电源,三极管Q1的c管脚连接电阻R35的一端和电阻R36的一端,电阻R35的另一端连接3.3V电源,电阻R36的另一端连接U1的D13管脚,三极管Q1的e管脚、芯片U6的6管脚、10管脚、11管脚、12管脚、13管脚均接地。

在本申请一些实施例中,所述时钟管理单元包括芯片U7、电阻R9、电阻R37、电阻R38、电阻R39、电阻R40、电容C9、电容C10、电容C11、电容C12、电容C32、电容C33、电容C34、晶振X1、晶振X2和电池BT1,其中,

芯片U1的G1管脚连接芯片U7的7管脚,芯片U7的7管脚还连接电阻R40的一端,芯片U1的G3管脚接芯片U7的8管脚,芯片U7的8管脚还连接电阻R39的一端,电阻R39的另一端和电阻R40的另一端接3.3V电源,芯片U1的H1管脚接芯片U7的1管脚,芯片U7的1管脚还连接电阻R38的一端,芯片U7的2管脚连接电阻R37的一端,电阻R37的另一端和电阻R38的另一端连接3.3V电源,芯片U7的3管脚连接3.3V电源、电容C32的一端和电容C33的一端,电容C32另一端和电容C33的另一端均接地,电容U7的5管脚接电容C34的一端和电池BT1的正极,电容C34的另一端和电池BT1的负极均接地,芯片U7的6管脚接地,芯片U1的P11管脚连接电阻R9的一端、电容C9的一端和晶振X1的3管脚,电阻R9的另一端接地,电容C9的另一端连接晶振X1的4管脚并接地,芯片U1的N11脚连接晶振X1的1管脚和电容C10的一端,电容C10的另一端连接晶振X1的2脚并接地,芯片U1的N9管脚连接晶振X2的1管脚和电容C11的一端,电容C11的另一端接地,芯片U1的P9管脚连接晶振X2的2管脚和电容C12的一端,电容C12的另一端接地,

其中,芯片U7采用SD3078、或SD3077、或SD3031。

在本申请一些实施例中,所述电路还包括用于将外部电源转换为3.3V电源的电源转换模块,所述电源转换模块包括芯片U5、电阻R31、电阻R32、电容C26、电容C27、电容C28、电感L3和稳压管W1,其中,

芯片U5的1管脚接电容C26的一端,电容C26的另一端接芯片U5的8管脚,芯片U5的5管脚接电阻R31的一端和电阻R32的一端,电阻R31的另一端接输入电源DC_IN,电阻R32的另一端接地,芯片U5的7管脚接电容C27的一端和输入电源DC_IN,电容C27的另一端连接芯片U5的6管脚并接地,电感L3的一端和电容C28的一端接芯片U5的4管脚并连接3.3V电源,电感L3的另一端接芯片U5的8管脚和稳压管W1的负极,稳压管W1的正极接地,电容C28的另一端接地,

其中,芯片U5采用LM2675-3.3、或LM2765LDX-3.3、或LM2765LD-3.3、或LM2765M-3.3、或LM2765MX-3.3、或LM2765N-3.3。

在本申请一些实施例中,所述电路还包括电容C1、电容C2、电容C3、电容C4、电容C13、电容C14、电容C15、电容C16、电容C18、电容C19、电容C20、电阻R1、电阻R10、电阻R11、接插件J6和接插件J7,其中,

芯片U1的F9管脚、F10管脚和J10管脚的共接点连接电容C1的一端、电容C2的一端、电容C3的一端、电容C4的一端和3.3V电源,电容C1的另一端、电容C2的另一端、电容C3的另一端和电容C4的另一端均接地,芯片U1的F13管脚连接电阻R1的一端,电阻R1的另一端接地,芯片U1的L1管脚、L2管脚和K4管脚的共接点连接3.3V电源、电容C13的一端、电容C14的一端、电容C15的一端、电容C16的一端和C17的一端,电容C13的另一端、电容C14的另一端、电容C15的另一端、电容C16的另一端和电容C17的另一端均接地,芯片U1的M1管脚和M2管脚共接于电感L1的一端,电感L1的另一端连接电容C18的一端、电容C19的一端和电阻R11的一端,电容C18另一端和电容C19的另一端均接地,电阻R11的另一端接芯片U1的J5管脚,芯片U1的 K3管脚连接电阻R10的一端和电容C20的一端,电阻R10的另一端连接3.3V电源,电容C20的另一端接地,U1的N1管脚、N2管脚和K6管脚均接地,芯片U1的K14管脚连接接插件J6的2管脚,芯片U1的L14管脚连接接插件J6的3管脚,接插件J6的1管脚接地,芯片U1的E14管脚连接接插件J7的3管脚,芯片U1的F12管脚连接J7的4管脚,芯片U1的L12管脚接外界信号GPS_PULSE。

在本申请一些实施例中,所述芯片U1采用MIMAXRT1052CVL5B芯片、或MIMAXRT1052CVL5A与IS25LP064组合的芯片、或MIMAXRT1062CVL5A与IS25LP064组合的芯片。

与现有技术对比,本发明具备以下有益效果:

本发明公开了一种多通道数据采集控制电路,包括:网络端口单元,包括第一扩展网口单元和第二扩展网口单元,用于通过所述第一扩展网口单元和所述第二扩展网口单元接入数据采集设备;通讯端口单元,用于将所述数据采集设备采集的数据发送到数据接收设备;串口单元,用于提供UART端口;存储单元,用于基于大容量存储介质进行数据存储;时钟管理单元,用于接收网络授时信号;芯片U1,用于对所述网络端口单元、所述通讯端口单元、所述串口单元、所述存储单元和所述时钟管理单元进行管理,通过基于第一扩展网口单元和第二扩展网口单元接入数据采集设备,并基于通讯端口单元进行数据发送,可同时接入最多20台六通道震动数据采集设备,同步进行最多20路三分量加速度、三分量倾角监测数据采集及存储,并实现了实时数据发送、历史数据发送、网络授时等功能,从而进一步提高了数据采集效率。

附图说明

为了更清楚地说明本申请实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地 ,下面描述中的附图仅仅是本申请的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

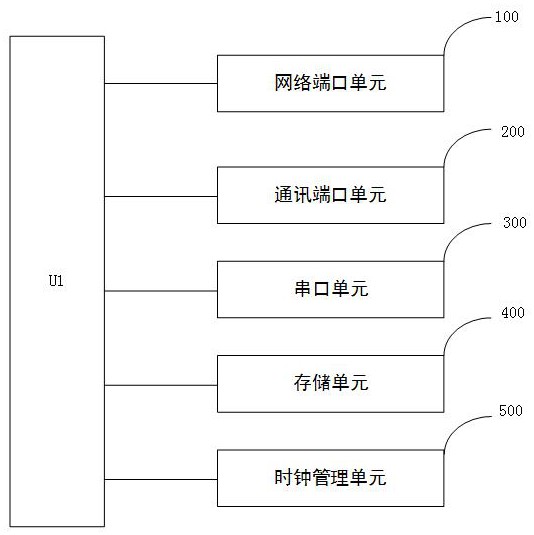

图1示出了本发明实施例提出的一种多通道数据采集控制电路的结构示意图;

图2示出了本发明实施例中芯片U1相关接口电路的结构示意图;

图3示出了本发明实施例中芯片U1、芯片U3、接插件J1、接插件J2、接插件J3、接插件J4相关电路的结构示意图;

图4示出了本发明实施例中芯片U4和接插件J5相关电路的结构示意图;

图5示出了本发明实施例中芯片U5、芯片U6、芯片U7、接插件J6和接插件J7相关电路的结构示意图。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

本申请实施例提供一种多通道数据采集控制电路,如图1所示,所述电路包括:

网络端口单元100,包括第一扩展网口单元和第二扩展网口单元,用于通过所述第一扩展网口单元和所述第二扩展网口单元接入数据采集设备;

本实施例中,数据采集设备可以为六通道震动数据采集设备,包括三分量加速度检测传感器和三分量倾角检测传感器。

通讯端口单元200,用于将所述数据采集设备采集的数据发送到数据接收设备;

为了提高数据发送效率,在本申请优选的实施例中,通讯端口单元200为高速SPI(Serial Peripheral Interface,串行外设接口)通信端口,数据接收设备可以为进行数据分析和计算的计算机设备或后端服务器。

串口单元300,用于提供UART(Universal Asynchronous Receiver/Transmitter,通用异步收发传输器)端口;

存储单元400,用于基于大容量存储介质进行数据存储;

时钟管理单元500,用于接收网络授时信号和控制数据处理速度;

芯片U1,用于对所述网络端口单元100、所述通讯端口单元200、所述串口单元300、所述存储单元400和所述时钟管理单元500进行管理;

其中,所述网络端口单元100、所述通讯端口单元200、所述串口单元300、所述存储单元400和所述时钟管理单元500分别与所述主控制芯片U1连接。

为了可靠的基于第一扩展网口单元接入数据采集设备,提高数据采集效率,在本申请一些实施例中,如图2和图4所示,所述第一扩展网口单元包括芯片U4、电感L2、电容C20、电容C21、电容C22、电容C23、电容C24、电容C26、电阻R12、电阻R13、电阻R14、电阻R15、电阻R16、电阻R17、电阻R18、电阻R19、电阻R20、电阻R21、电阻R22、电阻R23、电阻R24、电阻R25、电阻R26、电阻R27、电阻R28、电阻R29、电阻R30和接插件J5,其中,

芯片U1的F14管脚连接电阻R19的一端,电阻R19的另一端连接芯片U4的32管脚,芯片U4的32管脚连接电容C24一端和电阻R18的一端,电容C24的另一端接地,电阻R18的另一端接3.3V电源,从而实现对芯片U4的复位功能;

芯片U1的G13管脚连接芯片U4的21管脚,芯片U4的21管脚连接电阻R24的一端,电阻R24的另一端连接3.3V电源,从而实现上电后对芯片U4芯片初始化功能;

芯片U1的A7管脚接芯片U4的12管脚,芯片U1的C7管脚接芯片U4的11管脚,芯片U4的11管脚还连接电阻R12的一端和电阻R13的一端,电阻R12的另一端和电阻R13的另一端接3.3V电源,芯片U1的E12管脚接芯片U4的16管脚,芯片U1的D12管脚接芯片U4的15管脚,芯片U1的C12管脚连接电阻R26的一端和地,电阻R26的另一端接芯片U4的18管脚,芯片U1的B12管脚接芯片U4的24管脚,芯片U1的A12管脚接芯片U4的25管脚,芯片U1的A13管脚接芯片U4的23管脚,芯片U1的B13管脚接芯片U4的9管脚,芯片U1的C13管脚接芯片U4的20管脚,芯片U4的20管脚接电阻R25的一端,电阻R25的另一端接3.3V电源,芯片U4的4管脚连接接插件J5的4管脚和电阻R30的一端,芯片U4的5管脚连接接插件J5的3管脚和电阻R29的一端,芯片U4的6管脚连接接插件J5的2管脚和电阻R28的一端,芯片U4的7管脚连接接插件J5的1管脚和电阻R27的一端,电阻R27另一端、电阻R28另一端、电阻R29另一端、电阻R30另一端连接3.3V电源,从而使芯片U1通过芯片U4实现第一扩展网口,并且为第一扩展网口提供控制信号和数据信号;

芯片U4的1管脚接地,芯片U4的2管脚连接电容C22的一端和电容C23的一端,电容C22的另一端和电容C23的另一端接地,芯片U4的3管脚连接电感L2的一端、电容C20的一端和电容C21的一端,电感L2的另一端接3.3V电源,电容C20的另一端和电容C21的另一端接地,芯片U4的10脚连接电阻R14的一端,电阻R14的另一端接地,芯片U4的13管脚接电阻R15的一端,电阻R15的另一端接地,芯片U4的14管脚接电阻R16的一端,电阻R16的另一端接3.3V电源,芯片U4的15管脚接电阻R17一端,电阻R17的另一端接地, 芯片U4的17管脚连接电容C26一端和3.3V电源,电容C26的另一端接地,芯片U4的28管脚连接电阻R23一端,电阻R23另一端接地,芯片U4的29管脚连接电阻R22的一端,电阻R22的另一端接3.3V电源,芯片U4的30管脚接电阻R21一端,芯片U4的31管脚接电阻R20的一端,电阻R20的另一端和电阻R21的另一端均接地,芯片U4的33管脚接地,从而为芯片U4提供可靠电源;

其中,芯片U4采用KSZ8081RNB模块,或W5500芯片、或W5100芯片、或INtel 82571芯片、或INtel 82572芯片、或INtel 82573芯片,实现10/100Mbps通信速率。

为了可靠的基于第二扩展网口单元接入数据采集设备,提高数据采集效率,在本申请一些实施例中,如图2和图3所示,所述第二扩展网口单元包括芯片U3、电阻R7、电阻R8、电容C7、电容C8、接插件J3和接插件J4,其中,

芯片U1的M14管脚连接电阻R8的一端,电阻R8另一端连接芯片U3的11管脚,从而实现对芯片U3的复位功能控制;

芯片U1的L13管脚接芯片U3的8管脚,芯片U3的8管脚连接电阻R7的一端,电阻R7的另一端接3.3V电源,芯片U1的J13管脚接芯片U3的9管脚,芯片U3的10管脚接地,芯片U3的12管脚连接3.3V电源及电容C7的一端、电容C8的一端,电容C7的另一端、电容C8的另一端均接地,从而为芯片U3提供可靠的电源;

芯片U3的6管脚接接插件J3的1管脚,接插件J3的2管脚接地,芯片U3的TX+脚连接接插件J4的1管脚,芯片U3的TX-脚连接接插件J4的2管脚,芯片U3的RX+脚连接接插件J4的3管脚,芯片U3的RX-脚连接接插件J4的4管脚,从而实现第二扩展网口,以进行网络启动控制和数据传输。

其中,芯片U3采用USR-K3模块、或USR-K1模块、或USR-K2模块、或USR-K4模块,实现10/100Mbps通信速率。

为了可靠的进行数据发送,在本申请一些实施例中,如图2和图3所示,所述通讯端口单元包括接插件J2,其中,

芯片U1的L3管脚连接接插件J2的4管脚,芯片U1的L4管脚接接插件J2的5管脚,芯片U1的P3管脚接接插件J2的2管脚,芯片U1的N4管脚接接插件J2的3管脚,接插件J2的1管脚和6管脚接地,从而形成一个高速SPI通信端口,用来与外部数据接收设备进行数据通信。

本实施例中,接插件J4可以直连一台支持网络通信的传感设备,接插件J5可以通过一个多路路由器或交换机接入多台支持网络通信的传感设备,从而实现多路传感设备并行采集管理,单台传感设备的单通道最高采样速率可以达到200Hz。这些数据均可以通过该网络实时接收并可以由接插件J2形成的高速SPI通信端口实时发送出去。

为了进一步提高数据处理效率,在本申请一些实施例中,如图2和图3所示,所述串口单元包括电阻R3和接插件J1,其中,

芯片U1的P4管脚连接接插件J1的3管脚,接插件J1的3管脚连接电阻R3的一端,电阻R3的另一端连接3.3V电源,芯片U1的P5管脚连接接插件J1的1管脚,接插件J1的2管脚接地,从而实现一个UART端口,用于与外界通讯。

为了进一步提高数据采集效率,在本申请一些实施例中,如图2和图5所示,所述存储单元包括芯片U6、电容C29、电容C30、电容C31、电阻R2、电阻R33、电阻R34、电阻R35、电阻R36和三极管Q1,其中,

芯片U1的J1管脚连接芯片U6的7管脚,芯片U1的K1管脚连接芯片U6的8管脚,芯片U1的H2管脚连接芯片U6的1管脚,芯片U1的J2管脚连接芯片U6的2管脚,芯片U1的J3管脚连接电阻R33的一端,电阻R33的另一端连接芯片U6的5管脚,芯片U1的J4管脚连接芯片U6的3管脚和电阻R2的一端,电阻R2的另一端连接3.3V电源,芯片U6的4管脚连接3.3电源、电容C29的一端、电容C30的一端和电容C31的一端,电容C29的另一端、电容C30另一端和电容C31的另一端均接地,芯片U6的9管脚接电阻R34的一端和三极管Q1的b管脚,电阻R34的另一端接3.3V电源,三极管Q1的c管脚连接电阻R35的一端和电阻R36的一端,电阻R35的另一端连接3.3V电源,电阻R36的另一端连接U1的D13管脚,三极管Q1的e管脚、芯片U6的6管脚、10管脚、11管脚、12管脚、13管脚均接地,从而实现扩展SD卡存储器,完成基于SD存储卡存储控制信号及数据信号的操作。

为了提高存储单元的兼容性,在本申请优选的实施例中,所述大容量存储介质具体为包括MicroSD存储卡、SD存储卡、miniSD存储卡中的任一种存储卡,本领域技术人员可灵活选择不同的存储卡容量,如16GB、32GB、64GB、128GB、256GB等。

为了可靠的进行时钟管理,在本申请一些实施例中,如图2、图3和图5所示,所述时钟管理单元包括芯片U7、电阻R9、电阻R37、电阻R38、电阻R39、电阻R40、电容C9、电容C10、电容C11、电容C12、电容C32、电容C33、电容C34、晶振X1、晶振X2和电池BT1,其中,

芯片U1的G1管脚连接芯片U7的7管脚,芯片U7的7管脚还连接电阻R40的一端,芯片U1的G3管脚接芯片U7的8管脚,芯片U7的8管脚还连接电阻R39的一端,电阻R39的另一端和电阻R40的另一端接3.3V电源,芯片U1的H1管脚接芯片U7的1管脚,芯片U7的1管脚还连接电阻R38的一端,芯片U7的2管脚连接电阻R37的一端,电阻R37的另一端和电阻R38的另一端连接3.3V电源,芯片U7的3管脚连接3.3V电源、电容C32的一端和电容C33的一端,电容C32另一端和电容C33的另一端均接地,芯片U7的6管脚接地,从而为芯片U7提供可靠的电源并使芯片U1为芯片U7提供控制信号和数据信号;

电容U7的5管脚接电容C34的一端和电池BT1的正极,电容C34的另一端和电池BT1的负极均接地,从而为芯片U7提供可靠的备用电源;

芯片U1的P11管脚连接电阻R9的一端、电容C9的一端和晶振X1的3管脚,电阻R9的另一端接地,电容C9的另一端连接晶振X1的4管脚并接地,芯片U1的N11脚连接晶振X1的1管脚和电容C10的一端,电容C10的另一端连接晶振X1的2脚并接地,从而实现高速时钟设计。

芯片U1的N9管脚连接晶振X2的1管脚和电容C11的一端,电容C11的另一端接地,芯片U1的P9管脚连接晶振X2的2管脚和电容C12的一端,电容C12的另一端接地,从而实现低速时钟设计。

在需要高速处理的情况下以高速时钟信号进行工作,在不需要高速处理的情况下以低速时钟信号进行工作,由此实现低功耗和高速处理。

其中,芯片U7为时钟芯片,可采用SD3078、或SD3077、或SD3031。

为了进一步提高电路的可靠性,在本申请一些实施例中,如图2和图5所示,所述电路还包括用于将外部电源转换为3.3V电源的电源转换模块,所述电源转换模块包括芯片U5、电阻R31、电阻R32、电容C26、电容C27、电容C28、电感L3和稳压管W1,其中,

芯片U5的1管脚接电容C26的一端,电容C26的另一端接芯片U5的8管脚,芯片U5的5管脚接电阻R31的一端和电阻R32的一端,电阻R31的另一端接输入电源DC_IN,电阻R32的另一端接地,芯片U5的7管脚接电容C27的一端和输入电源DC_IN,电容C27的另一端连接芯片U5的6管脚并接地,电感L3的一端和电容C28的一端接芯片U5的4管脚并连接3.3V电源,电感L3的另一端接芯片U5的8管脚和稳压管W1的负极,稳压管W1的正极接地,电容C28的另一端接地,从而使得外部输入的电源DC_IN转换为与该通道数据采集控制电路匹配的3.3V电源,电源DC_IN可以为12V。

其中,芯片U5采用LM2675-3.3、或LM2765LDX-3.3、或LM2765LD-3.3、或LM2765M-3.3、或LM2765MX-3.3、或LM2765N-3.3。

为了进一步提高电路的可靠性,在本申请一些实施例中,如图2和图5所示,所述电路还包括电容C1、电容C2、电容C3、电容C4、电容C13、电容C14、电容C15、电容C16、电容C18、电容C19、电容C20、电阻R1、电阻R10、电阻R11、接插件J6和接插件J7,其中,

芯片U1的F9管脚、F10管脚和J10管脚的共接点连接电容C1的一端、电容C2的一端、电容C3的一端、电容C4的一端和3.3V电源,电容C1的另一端、电容C2的另一端、电容C3的另一端和电容C4的另一端均接地,电容C1、电容C2、电容C3、电容C4对电源进行滤波处理,从而实现为芯片U1提供稳定的工作电源。

芯片U1的F13管脚连接电阻R1的一端,电阻R1的另一端接地,芯片U1的L1管脚、L2管脚和K4管脚的共接点连接3.3V电源、电容C13的一端、电容C14的一端、电容C15的一端、电容C16的一端和C17的一端,电容C13的另一端、电容C14的另一端、电容C15的另一端、电容C16的另一端和电容C17的另一端均接地,从而为芯片U1提供可靠的电源。

芯片U1的M1管脚和M2管脚共接于电感L1的一端,电感L1的另一端连接电容C18的一端、电容C19的一端和电阻R11的一端,电容C18另一端和电容C19的另一端均接地,电阻R11的另一端接芯片U1的J5管脚,从而为芯片U1的J5管脚提供高精度的电源。

芯片U1的 K3管脚连接电阻R10的一端和电容C20的一端,电阻R10的另一端连接3.3V电源,电容C20的另一端接地,U1的N1管脚、N2管脚和K6管脚均接地,从而为芯片U1提供可靠的工作电源。

芯片U1的K14管脚连接接插件J6的2管脚,芯片U1的L14管脚连接接插件J6的3管脚,接插件J6的1管脚接地,从而实现芯片U1的程序下载串口。

芯片U1的E14管脚连接接插件J7的3管脚,芯片U1的F12管脚连接J7的4管脚,从而实现由接插件J7的3管脚脚输入仿真调试数据,由接插件J7的4管脚输入仿真调试时钟信号,进行对芯片U1的功能代码仿真测试。

芯片U1的L12管脚接外界信号GPS_PULSE,从而可以接入外界输入的GPS秒脉冲信号。

为了提高芯片U1的兼容性,在本申请一些实施例中,所述芯片U1采用MIMAXRT1052CVL5B芯片、或MIMAXRT1052CVL5A与IS25LP064组合的芯片、或MIMAXRT1062CVL5A与IS25LP064组合的芯片。

通过应用以上技术方案,多通道数据采集控制电路包括:网络端口单元,包括第一扩展网口单元和第二扩展网口单元,用于通过所述第一扩展网口单元和所述第二扩展网口单元接入数据采集设备;通讯端口单元,用于将所述数据采集设备采集的数据发送到数据接收设备;串口单元,用于提供UART端口;存储单元,用于基于大容量存储介质进行数据存储;时钟管理单元,用于接收网络授时信号;芯片U1,用于对所述网络端口单元、所述通讯端口单元、所述串口单元、所述存储单元和所述时钟管理单元进行管理;其中,所述网络端口单元、所述通讯端口单元、所述串口单元、所述存储单元和所述时钟管理单元分别与所述主控制芯片U1连接,基于该多通道数据采集控制电路可同时接入最多20台六通道震动数据采集设备,同步进行最多20路三分量加速度、三分量倾角监测数据采集及存储,并实现了实时数据发送、历史数据发送、网络授时等功能,从而进一步提高了数据采集效率。

最后应说明的是:以上实施例仅用以说明本申请的技术方案,而非对其限制;尽管参照前述实施例对本申请进行了详细的说明,本领域的普通技术人员当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不驱使相应技术方案的本质脱离本申请各实施例技术方案的精神和范围。

- 一种多通道数据采集控制电路

- 一种多通道结构化数据采集系统及数据采集方法