半导体结构的形成方法

文献发布时间:2023-06-19 11:52:33

技术领域

本发明涉及半导体制造技术领域,特别涉及一种半导体结构的形成方法。

背景技术

在互补金属氧化物半导体场效应管(CMOS)芯片制造中,栅极结构的制程是一道非常重要的工序,栅极结构的大小会直接影响器件的各种电性参数。因此,栅极结构关键尺寸的均匀性的控制变得非常重要。

目前在晶圆上形成栅极结构时,各区域晶圆上的栅极结构的高度存在较大差异,例如中间区域的栅极结构的高度与边缘区域的栅极结构的高度不同。并且,对晶圆上的栅极结构进行刻蚀时,通常晶圆上刻蚀速率的分布是固定的,这可能会导致刻蚀结束后,各区域的栅极结构的高度的差异进一步扩大,进而严重影响形成的半导体结构的性能。

因此,需要提出一种半导体结构的形成方法,以改善晶圆上的栅极结构高度的均匀性。

发明内容

本发明解决的技术问题是提供一种半导体结构的形成方法,能改善晶圆上栅极结构高度的均匀性,提高晶圆生产的可靠性和良率。

为解决上述技术问题,本发明实施例提供一种半导体结构的形成方法,包括:提供衬底,所述衬底包括中间区域和边缘区域,所述衬底上具有栅极结构,所述中间区域的所述栅极结构的高度与所述边缘区域的所述栅极结构的高度具有差异;采用至少一次沉积工艺在所述衬底、所述栅极结构表面形成覆盖层,位于高度高的所述栅极结构上的所述覆盖层的厚度小于位于高度低的所述栅极结构上的所述覆盖层的厚度;在每次形成完所述覆盖层后,均刻蚀所述覆盖层及部分厚度的所述栅极结构。

可选的,所述覆盖层的材料为碳氢聚合物。

可选的,所述沉积工艺包括等离子体沉积工艺。

可选的,采用控温方法形成所述覆盖层。

可选的,所述控温方法包括:提供控温基板,将所述衬底放置在所述控温基板上;通过所述控温基板控制所述衬底的温度,使高度高的所述栅极结构的温度高于高度低的所述栅极结构的温度。

可选的,所述栅极结构包括:介电层;功函数层,位于所述介电层表面;以及栅极材料层,位于所述功函数层表面。

可选的,刻蚀所述栅极结构的方法包括:先刻蚀所述栅极材料层;再刻蚀所述功函数层和所述介电层。

可选的,当所述沉积工艺为一次时,在所述衬底、所述栅极结构表面形成覆盖层,位于高度高的所述栅极结构上的所述覆盖层的厚度小于位于高度低的所述栅极结构上的所述覆盖层的厚度;刻蚀所述覆盖层及部分厚度的所述栅极结构。

可选的,当所述沉积工艺为多次时,在所述衬底、所述栅极结构表面形成覆盖层;刻蚀所述覆盖层和部分厚度的所述栅极结构;循环进行形成所述覆盖层以及刻蚀所述覆盖层和所述栅极结构的步骤。

可选的,所述沉积工艺的次数为5~10次。

与现有技术相比,本发明实施例的技术方案具有以下有益效果:

在栅极结构上形成覆盖层,且位于高度高的栅极结构上的覆盖层的厚度小于位于高度低的栅极结构上的覆盖层的厚度,通过调整覆盖层的厚度来调整不同区域衬底的刻蚀速率的分布,使高度高的栅极结构的刻蚀速率快,高度低的栅极结构的刻蚀速率慢,使最终刻蚀结束后,不同区域衬底上栅极结构高度的差异缩小,提高栅极结构高度统一性,很好地改善了不同区域衬底上栅极结构高度的均匀性,从而提高半导体结构的性能。

附图说明

图1至图5是本发明一实施例中半导体结构的形成方法各步骤对应的结构示意图。

具体实施方式

由背景技术可知,目前不同区域衬底上刻蚀速率的分布是固定的,如果在高度高的栅极结构所在区域的刻蚀速率快,在高度低的栅极结构所在区域的刻蚀速率慢,保持这样的刻蚀速率分布直至刻蚀结束,会导致栅极结构高度的差异进一步扩大,对半导体结构的性能造成不利影响。

为了解决上述问题,发明人经过研究,提出一种半导体结构的形成方法,在栅极结构上形成覆盖层,且位于高度高的栅极结构上的覆盖层的厚度小于位于高度低的栅极结构上的覆盖层的厚度,通过覆盖层的厚度的差异来调整不同区域衬底刻蚀速率的分布,使高度高的栅极结构的刻蚀速率慢,高度低的栅极结构的刻蚀速率快,刻蚀结束后能有效较小栅极结构之间的高度差异,改善不同区域衬底上栅极结构高度的均匀性。

为使本发明的上述目的、特征和有益效果能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

图1至图5是本发明一实施例中半导体结构的形成方法各步骤对应的结构示意图。

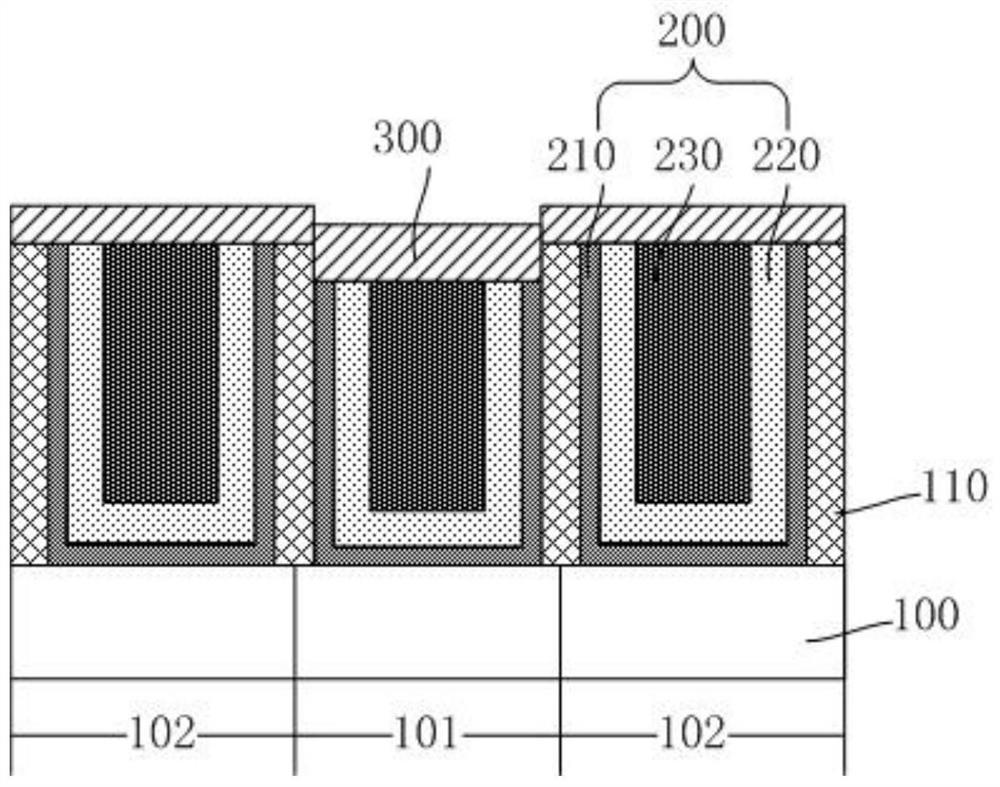

参考图1,提供衬底100,所述衬底100包括中间区域101和边缘区域102,所述衬底100上具有栅极结构200,所述中间区域101的所述栅极结构200的高度和所述边缘区域102的所述栅极结构200的高度具有差异。

所述衬底100为后续半导体结构的形成提供工艺平台。所述衬底100可以用于形成鳍式场效应晶体管,也可以用于形成平面晶体管。

本实施例中,所述衬底100为硅衬底;其他实施例中,所述衬底的材料还可以为锗、锗化硅、碳化硅、砷化镓或镓化铟,所述衬底还可以为绝缘体上硅或绝缘体上锗衬底等。

本实施例中,所述栅极结构200为金属栅极结构。具体的,所述栅极结构200包括介电层210,所述介电层210位于所述衬底100上;功函数层220,位于所述介电层210表面;以及栅极材料层230,位于所述功函数层220表面。

本实施例中,所述介电层210的材料为高K(K大于3.9)介质材料;所述功函数层220包括P型功函数材料,如TiN、TaN等,或N型功函数材料,如TiAl、TaAl等;所述栅极材料层230为金属,如钨。

本实施例中,形成所述栅极结构200的工艺为后栅工艺;其他实施例中,形成所述栅极结构200的工艺还可为前栅工艺。

本实施例中,还在所述衬底100上形成层间介质层110,所述层间介质层位于相邻所述栅极结构200之间的所述衬底100上。

所述层间介质层110的材料为绝缘介质材料。本实施例中,所述层间介质层110的材料为二氧化;其他实施例中,所述层间介质层110的材料也可以是碳氧化硅或氮氧化硅。

本实施例中,所述中间区域101和所述边缘区域102的所述衬底100上都具有若干栅极结构200,位于所述中间区域101的所述栅极结构200之间的高度相对来说比较均匀,位于所述边缘区域的所述栅极结构200之间的高度也比较均匀,但是所述中间区域101的所述栅极结构200和所述边缘区域102的所述栅极结构200的高度具有较大差异。

需要说明的是,本实施例中,通过采用先进工艺控制(APC)装置对同一衬底上的所述栅极结构200的高度进行控制;在形成所述覆盖层之前,先采用所述先进工艺控制装置检测位于所述衬底不同区域的所述栅极结构的高度分布。

本实施例中,所述中间区域101的栅极结构200的高度低于所述边缘区域102的栅极结构200的高度;其他实施例中,也可以是中间区域的栅极结构的高度高于边缘区域的栅极结构的高度。

参考图2,采用至少一次沉积工艺在所述衬底100、所述栅极结构200表面形成覆盖层300,位于高度高的所述栅极结构200上的所述覆盖层300的厚度小于位于高度低的所述栅极结构200上的所述覆盖层300的厚度。

本实施例中,所述衬底100上具有层间介质层110,所述覆盖层300覆盖所述层间介质层110和所述栅极结构200的表面。

本实施例中,所述中间区域101的所述栅极结构200上的所述覆盖层300的厚度,大于所述边缘区域102的所述栅极结构200上的所述覆盖层300的厚度。

在高度高的所述栅极结构200上沉积厚度小的所述覆盖层300,在高度低的所述栅极结构200上沉积厚度大的所述覆盖层300,后续刻蚀所述覆盖层300和所述栅极结构200时,通过所述覆盖层300厚度的差异,以及所述覆盖层300和所述栅极结构200的刻蚀选择比,改变衬底上不同区域的刻蚀速率分布,使高度高的所述栅极结构200的刻蚀速率快,高度低的所述栅极结构200的刻蚀速率慢,从而减小刻蚀结束后不同区域的所述衬底100上所述栅极结构200高度的差异,得到栅极高度均匀性高的半导体结构。

所述覆盖层300采用温度敏感性材料,本实施例中,所述覆盖层300的材料为碳氢聚合物。

本实施例中,所述沉积工艺为等离子体沉积工艺,主要通过等离子体轰击形成所述覆盖层300。

本实施例中,采用控温方法形成所述覆盖层300。

具体的,所述控温方法包括:提供控温基板(图未示),将所述衬底100放置在所述控温基板上;通过所述控温基板控制所述衬底100的温度,使高度高的所述栅极结构200的温度高于高度低的所述栅极结构200的温度。

由于所述覆盖层300的材料采用温度敏感性材料,温度变化对所述覆盖层300的沉积产生影响,温度高,形成的所述覆盖层300的厚度小;温度低,形成的所述覆盖层300的厚度大。因而可以在同一次沉积工艺中形成不同厚度的覆盖层300,即在高度高的所述栅极结构200上沉积厚度小的所述覆盖层300,在高度低的所述栅极结构200上沉积厚度大的所述覆盖层300。

本实施例中,通过所述控温基板控制所述中间区域101的所述衬底100的温度低于所述边缘区域102的所述衬底100的温度,使中间区域101的所述栅极结构200的温度低于所述边缘区域102的所述栅极结构200的温度,从而使所述中间区域101的所述栅极结构200上的覆盖层300的厚度大于所述边缘区域102的所述栅极结构200上的覆盖层300的厚度。

在每次形成完所述覆盖层300后,均刻蚀所述覆盖层300及部分厚度的所述栅极结构200。

具体的,当所述沉积工艺为一次时,在所述衬底100、所述栅极结构200表面形成所述覆盖层300;刻蚀所述覆盖层300及部分厚度的所述栅极结构200。

当沉积工艺为多次时,在所述衬底100、所述栅极结构200表面形成所述覆盖层300;刻蚀所述覆盖层300及部分厚度的所述栅极结构200;循环进行形成所述覆盖层300以及刻蚀所述覆盖层300和所述栅极结构200的步骤,直至所述栅极结构200达到预设高度。

本实施例中,刻蚀所述覆盖层300的工艺为干法刻蚀工艺。

参考图3至图4,本实施例中,具体刻蚀所述栅极结构200的方法包括:先刻蚀所述栅极材料层230;再刻蚀所述功函数层220和所述介电层210,直至所述功函数层220和所述介电层210的达到预设高度。

本实施例中,最终刻蚀形成的栅极结构,所述栅极材料层230与所述功函数层220和所述介电层210的顶部齐平。

其他实施例中,也可以是所述栅极材料层230的顶部高于所述功函数层220和所述介电层210的顶部。

本实施例中,刻蚀所述栅极材料层230的工艺为干法刻蚀工艺,所述干法刻蚀的工艺参数包括:刻蚀气氛包括BCl

本实施例中,刻蚀所述功函数层220和所述介电层210的工艺为干法刻蚀工艺,所述干法刻蚀的工艺参数包括:刻蚀气氛包括CF

需要说明的是,刻蚀所述覆盖层300以及位于所述覆盖层300下方的栅极材料层230时,刻蚀所述覆盖层300的工艺参数与刻蚀所述栅极材料层230的工艺参数相同;刻蚀所述覆盖层300以及位于所述覆盖层300下方的功函数层220和所述介电层210时,刻蚀所述覆盖层300的工艺参数与刻蚀所述功函数层220和所述介电层210的工艺参数相同。

本实施例中,所述沉积工艺为多次,所述沉积工艺的次数为5~10次。

本实施例中,具体的循环过程包括:形成所述覆盖层300、刻蚀所述覆盖层300、刻蚀所述栅极材料层230、刻蚀所述功函数层220和所述介电层210的步骤,再重复上述步骤5~10次。

参考图5,通过每次沉积所述覆盖层300,逐渐缩小所述栅极结构200之间的高度差异,循环刻蚀结束后所述衬底100上不同区域的所述栅极结构200的高度统一,均匀性更好。

本实施例中,所述先进工艺控制装置还用于控制不同衬底之间的所述栅极结构的高度,使不同的衬底之间的栅极结构的高度也具有较高的均匀性,从而提高半导体生产的良率和可靠性。

本实施例中,所述先进工艺控制装置包括反馈控制,所述反馈控制的反馈参数为后一衬底中栅极结构刻蚀需要的刻蚀时间。

具体的,当前衬底上的所述栅极结构刻蚀结束后,所述先进工艺控制装置记录所述刻蚀所述栅极材料层的刻蚀时间、所述功函数层和所述介电层的刻蚀时间;并检测刻蚀结束后所述衬底不同区域的所述栅极结构的高度分布;将刻蚀结束后的栅极高度数据与预设的栅极高度进行对比;根据对比结构调整下一衬底所述栅极材料层的刻蚀时间、所述功函数层和所述介电层的刻蚀时间,提高下一衬底的栅极结构的刻蚀结果准确性,同时提高衬底与衬底之间所述栅极结构高度的均匀性。

所述先进工艺控制装置可以用于一个衬底对一个衬底的工艺中,也可以用于一批衬底对一批衬底的工艺中。

本实施例中,通过应用所述先进工艺控制装置,不仅可以实现同一衬底上栅极结构高度的统一,还可以实现不同衬底上栅极结构高度的统一,从而提高半导体的生产良率和可靠性。

虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

- 半导体封装结构、半导体封装结构的形成方法以及半导体组装结构的形成方法

- 栅极结构的形成方法、半导体器件的形成方法以及半导体器件