管理降低功率的存储器操作

文献发布时间:2023-06-19 11:52:33

技术领域

本文所描述的实施例总体上涉及用于通过在等待存储器操作完成的同时使存储器控制器的至少一部分进入低功率模式来减少存储器装置在存储器操作期间的能耗的系统和方法。

背景技术

通常提供存储器装置作为计算机或其它电子装置中的内部半导体集成电路。存在许多不同类型的存储器,包括易失性存储器和非易失性存储器。易失性存储器需要电力来维护其数据,且包括各种形式的随机存取存储器(RAM),例如动态随机存取存储器(DRAM)或同步动态随机存取存储器(SDRAM)等。非易失性存储器可以在不通电时保留所存储的数据(在某些情况下可实施为只读存储器(ROM)),且可以包括一或多个存储技术,例如快闪存储器(例如,NAND或NOR快闪存储器)、电可擦除可编程ROM(EEPROM)、静态RAM(SRAM)、铁电RAM(FeRAM)、可擦除可编程ROM(EPROM)、电阻可变存储器,例如相变随机存取存储器(PCRAM)、电阻随机存取存储器(RRAM)、磁阻随机存取存储器(MRAM)或3D XPoint

快闪存储器用作广泛的电子应用的非易失性存储器。快闪存储器装置通常包括允许高存储器密度、高可靠性和低功率消耗的一或多组单晶体管、浮置栅极或电荷俘获存储器单元。两种常见类型的快闪存储器阵列架构包括NAND和NOR架构,它们以每种架构的基本存储器单元所布置的逻辑形式命名。存储器阵列的存储器单元通常被布置成矩阵。在实例中,阵列的行中的每个浮置栅极存储器单元的栅极耦合到存取线(例如,字线)。在NOR架构中,阵列的列中的每个存储器单元的漏极耦合到数据线(例如,位线)。在NAND架构中,阵列的串中的每个存储器单元的漏极在源极线与位线之间以源极到漏极的方式串联耦合在一起。

存储器装置的功率消耗是常见的问题,因为存储器装置越来越多地出现于各种功率敏感环境中,例如蜂窝式电话、平板计算机、物联网(IOT)装置和各种其它装置。因此,有助于提高存储器装置的功率使用效率的改进可以提供显著的技术和实践优势。

发明内容

本申请的一个方面涉及一种存储器装置,包含:存储器阵列;以及存储器控制器,被配置成从主机装置接收命令,所述存储器控制器包括处理电路系统,所述处理电路系统包括一或多个处理器,且被配置成执行操作,所述操作包括:启动存储器阵列中的第一存储器管理操作;在第一存储器管理操作期间将存储器控制器中的至少一个组件置于较低功率模式;基于第一存储器管理操作的预测完成时间设置唤醒时间;以及当唤醒事件和唤醒时间到期中的至少一个发生时,将存储器控制器切换出较低功率模式。

本申请的另一方面涉及一种管理存储器装置的功率使用的方法,所述存储器装置包含存储器阵列和存储器控制器,所述存储器控制器被配置成从主机装置接收指令,所述方法包括:启动存储器阵列中的第一存储器管理操作;在第一存储器管理操作期间将存储器控制器中的至少一个组件置于较低功率模式;基于第一存储器管理操作的预测完成时间设置唤醒时间;以及当唤醒事件和唤醒时间到期中的至少一个发生时,将存储器控制器切换出较低功率模式。

本申请的又一方面涉及至少一种装置可读存储介质,其包含指令,所述指令在由存储器控制器的一或多个处理器执行时使得一或多个处理器执行以下操作,所述操作包含:启动存储器阵列中的第一存储器管理操作;在第一存储器管理操作期间将存储器控制器中的至少一个组件置于较低功率模式;基于第一存储器管理操作的预测完成时间设置唤醒时间;以及当唤醒事件和唤醒时间到期中的至少一个发生时,将存储器控制器切换出较低功率模式。

本申请的又一方面涉及一种机器的机器可读介质,其存储指令,所述指令在被执行时使机器执行所述管理存储器装置的功率使用的方法。

附图说明

在不一定按比例绘制的附图中,相同的标号可以描述不同视图中的类似组件。具有不同字母后缀的相同数字可表示类似组件的不同实例。附图以实例而非限制的方式一般性地说明了本文档中讨论的各种实施例。

图1示出包括存储器装置的环境的实例的概念化图。

图2至3是示出NAND架构半导体存储器阵列的实例的示意图。

图4是示出存储器模块的实例的框图。

图5描绘示出样本实施例中的实例NAND装置的编程的时序图。

图6描绘系统挂起硬件的实例实施例的示意图。

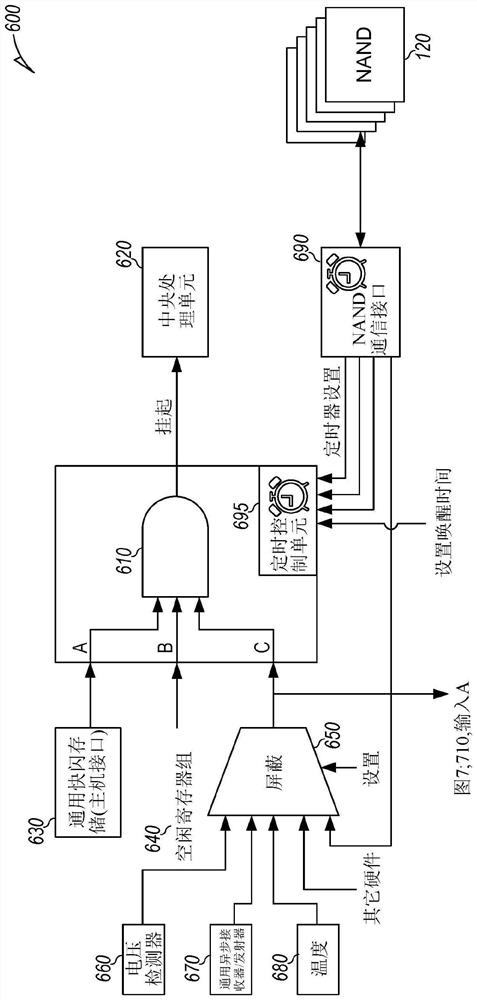

图7描绘系统唤醒硬件的实例实施例的示意图。

图8描绘多核系统挂起硬件的实例的示意图。

图9描绘多核系统唤醒硬件的实例的示意图。

图10A至B示出诸如图6和7的系统挂起/唤醒硬件的实例操作的流程图。

图11是描绘可结合所述系统挂起/唤醒硬件和/或方法的机器的实例的框图。

具体实施方式

由于移动装置的有限电池容量,移动装置市场对移动装置的整体能耗特别敏感。结果,对与移动装置相关联的存储装置的操作的能量效率提出了高期望。已经提出了多种技术来更有效地使用能量完成特定一组主机命令和服务,以便数据请求进出存储装置。本文描述的系统和方法通过提供系统挂起/唤醒操作来提供存储装置的有效能量使用,其减少耗时的存储器操作(例如存储器编程和擦除操作)期间的能耗。

例如,取决于待编程的每单元的位的数目,编程NAND组件可能需要若干毫秒;并且数据擦除操作可能花费更长的时间,例如长达30ms。在这些操作期间,通常将包括一或多个处理器的存储器控制器中的物理电路系统可能除了等待NAND操作的完成之外不做任何事情,这使存储器控制器消耗不必要的能量。

本文描述了用于在存储器装置除了等待存储器操作完成之外不进行其它操作的此类时间期间节省能量的技术。在此类“等待”时间期间,存储器控制器中的一些物理电路系统,在一些实例中为处理器(或处理器的一部分,诸如核)。可以被置于较低功率模式并且当存储器操作完成时被唤醒。下文将在NAND存储器装置的实例上下文中描述此类技术。

存储器装置包括单独的存储器管芯,其例如可以包括包含实施一(或多个)所选择的存储技术的一或多个存储器单元阵列的存储区域。此存储器管芯通常包括用于操作(多个)存储器阵列的支持电路系统。有时通常称为“被管理存储器装置”的其它实例包括与被配置成控制一或多个存储器管芯的操作的存储器控制器功能性相关联的一或多个存储器管芯的组合件。此存储器控制器功能性可简化与例如本文稍后论述的“主机”的外部装置的互操作性,且进一步促进(通常)多个离散存储器装置的管理。在此些被管理存储器装置中,可在也并入存储器阵列的一或多个管芯上或在单独的管芯上实施控制器功能性。在其它存储器装置中,一或多个存储器装置可与存储器控制器功能性组合以形成固态驱动器(SSD)存储卷。

在实施称为“被管理NAND”装置的NAND快闪存储器单元的被管理存储器装置的实例中描述本公开的实例实施例。然而,这些实例并不限制本公开的范围,其可由实施其它存储器存储技术的存储器装置实施,例如本文中先前论述的非限制性实例。被管理NAND装置可用作各种形式的电子装置中的主要或辅助存储器且通常用于移动装置中。

NOR或NAND架构半导体存储器阵列中的每个快闪存储器单元可被编程为两个或两个以上编程状态。例如,单级单元(SLC)可表示两个编程状态中的一个(例如,1或0),表示一个数据位。快闪存储器单元还可表示两个以上编程状态,从而允许制造较高密度存储器而不增加存储器单元的数目,因为每个单元可表示一个以上二进制数字(例如,一个以上位)。此些单元可称为多状态存储器单元、多位单元或多级单元(MLC)。在某些实例中,MLC可指可每单元存储两位数据(例如,四个编程状态中的一个)的存储器单元,TLC可指可每单元存储三位数据(例如,八个编程状态中的一个)的存储器单元,且QLC可每单元存储四位数据。MLC在本文中以其更广泛的上下文使用,以指代可每单元存储一位以上数据的任何存储器单元(即,其可表示两个以上编程状态;因此,术语MLC在本文中在更广泛的上下文中使用,以通用于每单元存储2、3、4或更多位数据的存储器单元)。

可根据公认的工业标准来配置和操作被管理存储器装置。例如,被管理NAND装置可以是(作为非限制性实例)通用快闪存储(UFS

SSD可以用作计算机的主存储装置等;并且在例如性能、尺寸、重量、耐用性、工作温度范围和功耗方面提供优于具有移动部件的传统硬盘驱动器的优点。例如,SSD相对于常规磁盘驱动器可具有减少的寻道时间、等待时间或其它延迟。SSD使用非易失性存储器单元,例如快闪存储器单元,从而允许驱动器更加通用且紧凑。

SSD和被管理存储器装置都可以包括数个存储器装置,包括数个管芯或逻辑单元(例如,逻辑单元号或LUN),并且通常包括存储器控制器,所述存储器控制器包括处理电路系统,所述处理电路系统通常包括一或多个处理器、执行逻辑功能以操作存储器装置或与外部系统接口。此些SSD和被管理存储器装置可以包括一或多个快闪存储器管芯,所述快闪存储器管芯上包括数个存储器阵列和外围电路系统。快闪存储器阵列可以包括组织成数个物理页的数个存储器单元块。在一些实例中,SSD还可以包括DRAM或SRAM(或其它形式的存储器管芯或其它存储器结构),例如作为控制器的一部分。类似地,被管理NAND装置可以包括与NAND存储阵列分离且在控制器内或与控制器分离的易失性和/或非易失性存储器的一或多个阵列。SSD和被管理NAND装置均可从主机接收与存储器操作相关联的命令,所述存储器操作例如为在存储器装置与主机之间传送数据(例如,用户数据和相关联的完整性数据,例如错误数据和地址数据等)的读取或写入操作,或从一或多个存储器装置擦除数据的擦除操作。

将主要参考根据UFS标准构造和操作的被管理NAND装置来描述当前实施例。尽管此些被管理NAND装置和UFS标准仅表示相关的实例配置;并且当前的方法和结构可以利用实施其它存储技术和/或实施其它标准或操作协议的存储器装置来实施。

本描述阐述用于管理存储器装置的存储器装置、方法及机器可读介质的实例,所述存储器装置包括被配置成从主机装置接收指令的存储器控制器。存储器控制器被配置为执行包括在存储器管理操作期间将存储器控制器置于较低功率模式的操作,并且在许多实例中,基于存储器管理操作的预测完成时间来设置唤醒时间(其可以由例如与存储器阵列通信的存储器通信接口提供)。存储器控制器还操作以在例如以下至少之一时将存储器控制器切换出较低功率模式:接收到另一存储器管理操作;唤醒时间到期;以及从一或多个所选择的硬件资源接收中断。在实例实施例中,存储器阵列是NAND存储器阵列,并且存储器管理操作是以下中的一个:对NAND存储器阵列的一部分进行编程,擦除NAND存储器阵列的一部分,以及从NAND存储器阵列读取。

图1示出环境100的实例,其包括主机装置105和存储器装置110,被配置成经由通信接口111进行通信。主机装置105或存储器装置110可以被包括在多种产品150中,例如物联网(IoT)装置(例如,冰箱或其它设备、传感器、电动机或致动器、移动通信装置、汽车、无人驾驶飞机等)中以支持产品150的处理、通信或控制。

存储器装置110包括存储器控制器115和存储器阵列120,所述存储器阵列包括例如数个单独的存储器管芯(例如,3D NAND管芯的堆叠)。在实例中,存储器装置110可以是主机装置105的离散存储器或存储装置组件。在其它实例中,存储器装置110可以是集成电路(例如,芯片上系统(SOC)等)的一部分,其与主机装置以是105的一或多个其它组件堆叠或以其它方式被包括在一起。在这些实例中,存储器装置110经由通信接口111与主机装置105组件通信。因此,如本文所述,即使当存储器装置110集成到主机装置105中时,主机或主机装置105操作也不同于存储器装置110的操作。

各种形式的通信接口可用于在存储器装置110与主机装置105的一或多个其它组件之间传送数据,例如串行高级技术附接(SATA)接口、外围组件互连高速(PCIe)接口、通用串行总线(USB)接口、通用快闪存储(UFS)接口、eMMC

存储器控制器115可从主机105接收指令,且可与存储器阵列120通信,例如将数据传送到(例如,写入)存储器阵列120的存储器单元、平面、子块、块或页中的一或多个或从其(例如,读取)或对其进行擦除。例如,存储器控制器115包括处理电路系统,所述处理电路系统可以包括一或多个处理器,这些处理器在存在时运行以执行存储在存储器装置中的指令。为了本实例的目的,指令将作为固件来讨论,尽管指令也可以作为软件来呈现;并且所描述的功能的全部或一些部分也可以在包括一或多个组件或集成电路的电路系统中实施。

例如,存储器控制器115可以包括一或多个存储器控制单元、电路或组件,其被配置成控制跨越存储器阵列120的存取且提供主机105与存储器装置110之间的转换层。另外,存储器控制器可以包括存储器接口,以与相关联的存储器装置接口。在一些实例中,存储器接口可为开放NAND快闪接口(ONFI)。虽然存储器控制器115在本文中被示出为存储器装置110封装的一部分,但可采用其它配置,例如存储器控制器115为主机105的组件(例如,作为与存储器装置110分离的主机105的芯片上系统上的离散封装),或甚至经由主机105的中央处理单元(CPU)实施。

存储器管理器125可以包括与各种存储器管理功能相关联的用于执行的多个组件或集成电路和/或指令等。在一些实施例中,存储器管理器125的功能由执行固件指令的控制器(或处理器)来实施,所述固件指令在一些实例中将被存储在存储器控制器115内。在其它实例中,存储器管理器125可至少部分由存储器控制器115内的一或多个处理器实施,所述处理器可执行存储在存储器阵列120中的指令。类似地,管理表130可存储在存储器控制器115或存储器阵列120中。在此些实例中,指令和/或管理表130可以存储在存储器阵列120的NAND管芯的某些块中,并且在操作期间被加载到存储器控制器115的工作存储器中。

出于本说明书的目的,将在NAND存储器的上下文中描述实例存储器操作和管理功能。本领域技术人员将认识到,其它形式的非易失性存储器可以具有类似的存储器操作或管理功能。此类NAND管理功能包括损耗均衡、无用单元收集、回收、错误检测或校正、块退出或一或多个其它存储器管理功能。存储器管理器125可将主机命令(例如,从主机接收的命令)解析或格式化为装置命令(例如,与存储器阵列120的操作相关联的命令等),或生成用于阵列控制器135或存储器装置110的一或多个其它组件的装置命令(例如,以实现各种存储器管理功能)。此些内部生成的操作,例如无用单元收集、损耗均衡等可导致以与外部引导的存储器操作所提供的方式相同的方式执行可提供如本文所述的功率管理操作的机会的操作。

存储器管理器125可以包括一组管理表130,被配置成维护与存储器装置110的一或多个组件相关联的各种信息(例如,与存储阵列或耦合到存储控制器115的一或多个存储单元相关的各种信息)。例如,管理表130可以包括关于耦合到存储器控制器115的存储器单元的一或多个块的块年龄、块擦除计数、错误历史或一或多个错误计数(例如,写入操作错误计数、读取位错误计数、读取操作错误计数、擦除错误计数等)的信息。在某些实例中,如果针对错误计数中的一或多个检测到的错误的数目高于阈值,则位错误可被称作不可校正的位错误。管理表130可维护可校正或不可校正位错误的计数等。在实例中,管理表130可以包括转换表或逻辑到物理(L2P)映射。

阵列控制器135可以包括功率管理电路系统145,其可以包括存储器控制器115的处理器的至少一部分,且在所选择的实施方案中,其可以包括被配置成执行本文所述的功率管理功能的额外硬件电路系统。如下文将更详细论述,这些功率管理功能可以包括在正执行NAND存储器操作时将例如处理器或处理器核的电路系统置于较低功率模式中;以及响应于在此电路系统外部识别出的事件,将系统电路切换出较低功率模式。

阵列控制器135还可包括被配置成控制与将数据写入到存储器装置110的耦合到存储器控制器115的一或多个存储器单元,从所述一或多个存储器单元读取数据或擦除所述一或多个存储器单元作的电路系统或组件等。存储器操作可基于例如从主机105接收的主机命令,或由存储器管理器125内部生成(例如,与磨损均衡、错误检测或校正相关联)。

阵列控制器135还可包括错误校正码(ECC)组件140,其可包括ECC引擎或其它电路系统,被配置成检测或校正与将数据写入到存储器装置110的耦合到存储器控制器115的一或多个存储器单元或从其读取数据相关联的错误。存储器控制器115可被配置成基于由阵列控制器135维护的ECC数据而主动检测与数据的各种操作或存储相关联的错误发生(例如,位错误,操作错误等)并从所述错误发生恢复。这使得存储器控制器115能够维护在主机105与存储器装置110之间传送的数据的完整性或维护所存储数据的完整性。该完整性维护的一部分可以包括移除(例如,退出)失效的存储器资源(例如,存储器单元、存储器阵列、页、块等)以防止将来的错误。

存储器阵列120可以包括布置在例如装置、平面、子块、块或页中的若干存储器单元。作为一个实例,48GB TLC NAND存储器装置可以包括每页18,592字节(B)的数据(16,384+2208字节),每块1536页,每平面548块,以及每装置4个或更多个平面。作为另一实例,32GBMLC存储器装置(每单元存储两位数据(即,4个可编程状态))可以包括每页18,592字节(B)的数据(16,384+2208字节),每块1024页,每平面548块和每装置4个平面,但与对应的TLC存储器装置相比,所需的写入时间减少了一半,编程/擦除(P/E)周期增加了两倍。其它实例可以包括其它数目或布置。在一些实例中,存储器装置或其一部分可选择性地以SLC模式或以所需MLC模式(例如TLC、QLC等)操作。

在操作中,数据通常以页为单位写入到NAND存储器装置110或从其读取,且以块为单位擦除。然而,根据需要,可对较大或较小组的存储器单元执行一或多个存储器操作(例如,读取、写入、擦除等)。NAND存储器装置110的数据传送大小通常被称作页,而主机的数据传送大小通常被称作扇区。

在一些实例中,存储器阵列可包含数个NAND管芯,且特定NAND管芯的存储器控制器115的一或多个功能可实施于所述特定管芯上的管芯上控制器上。也可以利用控制功能的其它组织和描绘,诸如用于每个管芯、平面、超级块、块、页面等的控制器。

尽管数据页可以包括数个字节的用户数据(例如,包括数个数据扇区的数据有效负载)及其对应元数据,但页的大小通常仅指用于存储用户数据的字节的数目。例如,具有4KB的页大小的数据页可以包括4KB的用户数据(例如,假设扇区大小为512B的8个扇区)以及数个字节(例如,32B,54B,224B等)的对应于用户数据的元数据,例如完整性数据(例如,错误检测或校正码数据)、地址数据(例如,逻辑地址数据等)或与用户数据相关联的其它元数据。

不同类型的存储器单元或存储器阵列120可提供不同页大小或可需要与其相关联的不同量的元数据。例如,不同的存储器装置类型可具有不同的位错误率,其可导致确保数据页的完整性所必需的不同量的元数据(例如,具有较高位错误率的存储器装置可比具有较低位错误率的存储器装置需要更多字节的错误校正码数据)。例如,MLC NAND快闪装置可具有比对应的SLC NAND快闪装置高的位错误率。这样,MLC装置可能比对应的SLC装置需要更多的元数据字节用于错误数据。

图2是示出图1中示出的类型的NAND存储器装置110的3D NAND架构半导体存储器阵列200的示例的示意图,包括以块(例如,块A 201A,块B 201B等)和子块(例如,子块A

每串存储器单元包括在源极线(SRC)235或源极侧选择栅(SGS)(例如,第一至第三A

在物理页内,每层表示一行存储器单元,而每个存储器单元串表示一列。子块可以包括一或多个物理页。块可以包括数个子块(或物理页)(例如,128、256、384等)。尽管本文中示出为具有两个块,但每个块具有两个子块,每个子块具有单个物理页,每个物理页具有三个存储器单元串,且每个串具有8层存储器单元。在其它实例中,存储器阵列200可以包括更多或更少的块、子块、物理页、存储器单元串、存储器单元或层。例如,每个存储器单元串可根据需要包括更多或更少层(例如,16、32、64、128等),以及电荷存储晶体管上方或下方的一或多个额外半导体材料层(例如,选择栅极、数据线等)。例如,48GB TLC NAND存储器装置可以包括每页18,592字节(B)的数据(16,384+2208字节),每块1536页,每平面548块,以及每装置4个或更多个平面。

存储器阵列200中的每个存储器单元包括控制栅极(CG),耦合到(例如,电耦合或以其它方式可操作地连接到)存取线(例如,字线(WL)WL0

在实例中,存储器阵列200可以包括数层半导体材料(例如,多晶硅等),被配置成耦合每个存储器单元的控制栅极(CG)或阵列的相应层的选择栅极(或CG或选择栅极的一部分)。可使用位线(BL)和选择栅极等的组合来存取、选择或控制阵列中的特定存储器单元串,且可使用一或多个存取线(例如,WL)来存取、选择或控制所述特定串中的一或多个层级处的特定存储器单元。

图3示出NAND架构半导体存储器阵列300的一部分的实例示意图,NAND架构半导体存储器阵列300包括布置成串(例如,第一至第三串305至307)和层(例如,示出为相应字线(WL)WL0至WL7 310至317,漏极侧选择栅极(SGD)线325,源极侧选择栅极(SGS)线330等)的二维阵列的多个存储单元302,以及感测放大器或类似装置360。例如,存储器阵列300可示出例如图2中所示出的3D NAND架构半导体存储器装置的存储器单元的一个物理页的一部分的实例示意图。

每串存储器单元使用相应的源极侧选择栅极(SGS)330(例如,第一至第三SGS 331至333)耦合到源极线(SRC)335,且使用相应的漏极侧选择栅极(SGD)(例如,第一至第三SGD326至328)耦合到相应的数据线(例如,第一至第三位线(BL)BL0至BL2 320至322)。尽管在图3的实例中以8个层(例如,使用字线(WL)WL0至WL7 310至317)和三个数据线(BL0至BL2326至328)来说明,但根据需要,其它实例可以包括具有更多或更少层或更多或更少数据线的存储器单元串。

在NAND架构半导体存储器阵列中,例如实例存储器阵列300,可通过感测与含有所选择的存储器单元的特定数据线相关联的电流或电压变化来存取所选择的存储器单元302的状态。可使用一或多个驱动器存取存储器阵列300(例如,通过控制电路、一或多个处理器、数字逻辑等)。在实例中,一或多个驱动器可通过将特定电位驱动到一或多个数据线(例如,位线BL0至BL2)、存取线(例如,字线WL0至WL7)或选择栅极来激活特定存储器单元或存储器单元组,这取决于希望对特定存储器单元或存储器单元组执行的操作类型。

为了将数据编程或写入到存储器单元,可将编程电压(Vpgm)(例如,一或多个编程脉冲等)施加到所选择的字线(例如,WL4),且因此施加到耦合到所选择的字线的每个存储器单元的控制栅极(例如,耦合到WL4的存储器单元的第一至第三控制栅极(CG)341至343)。编程脉冲可开始于例如15V或接近15V,且在某些实例中,可在每个编程脉冲施加期间增大量值。当将编程电压施加到所选择的字线时,可将例如接地电位Vss的电位施加到作为编程的目标的存储器单元的数据线(例如,位线)和衬底(且因此,源极与漏极之间的沟道),从而导致从沟道到目标存储器单元的浮置栅极的电荷转移(例如,直接注入或福勒至诺德海姆(FN)隧穿等)。

对比之下,可将通过电压(V

例如,如果将编程电压(例如,15V或更高)施加到例如WL4的特定字线,则可将10V的通过电压施加到例如WL3、WL5等的一或多个其它字线,以禁止非目标存储器单元的编程或保留存储在此些存储器单元上的并非作为编程的目标的值。随着所施加的编程电压与非目标存储器单元之间的距离增加,抑制对非目标存储器单元进行编程所需的通过电压可减小。例如,在将15V的编程电压施加到WL4的情况下,可将10V的通过电压施加到WL3和WL5,可将8V的通过电压施加到WL2和WL6,可将7V的通过电压施加到WL1和WL7等。在其它实例中,通过电压或字线的数目等可更高或更低,或更多或更少。

感测放大器360耦合到数据线(例如,第一、第二或第三位线(BL0至BL2)320至322)中的一或多个,其可通过感测特定数据线上的电压或电流来检测相应数据线中的每个存储器单元的状态。

在施加一或多个编程脉冲(例如,Vpgm)之间,可执行检验操作以确定所选择的存储器单元是否已达到其既定编程状态。如果所选择的存储器单元已达到其既定编程状态,则可禁止其进一步编程。如果所选择的存储器单元尚未达到其既定编程状态,则可施加额外编程脉冲。如果所选择的存储器单元在特定数目的编程脉冲(例如,最大数目)之后尚未达到其既定编程状态,则可将所选择的存储器单元或与此所选择的存储器单元相关联的串、块或页标记为有缺陷。

为了擦除存储器单元或一组存储器单元(例如,擦除通常在块或子块中执行),可将擦除电压(Vers)(例如,通常Vpgm)施加到擦除目标存储器单元的衬底(且因此沟道,位于源极与漏极之间)(例如,使用一或多个位线、选择栅极等),同时将目标存储器单元的字线保持在例如接地Vss的电位,导致从目标存储器单元的浮置栅极到沟道的电荷转移(例如,直接注入或Fowler至Nordheim(FN)隧穿等)。

图4是示出图1中所示出类型的存储器装置400的实例的框图,其包括存储器阵列402,存储器阵列402具有多个存储器单元404和一或多个电路或组件以提供与存储器阵列402的通信或对其执行一或多个存储器操作。存储器装置400可以包括行解码器412,列解码器414,感测放大器420,页缓冲器422,选择器424,输入/输出(I/O)电路426和存储器控制单元430。

存储器阵列402的存储器单元404可布置成块,例如第一块402A和第二块402B。每个块可以包括子块。例如,第一块402A可以包括第一和第二子块402A

存储器控制单元430可根据在控制线432上接收的一或多个信号或指令来控制存储器装置400的存储器操作,所述信号或指令包括例如指示所需操作(例如,写入、读取、擦除等)的一或多个时钟信号或控制信号,或在一或多个地址线416上接收的地址信号(A0至AX)。存储器装置400外部的一或多个装置可以控制控制线432上的控制信号或地址线416上的地址信号的值。存储器装置400外部的装置的实例可以包括但不限于主机、存储控制器、处理器或图4中未示出的一或多个电路或组件。

存储器装置400可使用存取线406和第一数据线410来将数据传送到(例如,写入或擦除)或从(例如,读取)存储器单元404中的一或多个。存储器控制单元430可以包括状态机431,耦合到行解码器412、列解码器414和I/O电路426。状态机431还可以输出快闪存储器的状态数据,例如READY/BUSY或PASS/FAIL。在一些设计中,状态机431可被配置成管理编程过程。行解码器412和列解码器414可接收并解码来自地址线416的地址信号(A0至AX),确定将存取存储器单元404中的哪一者,且将信号提供到存取线406(例如,多个字线(WL0至WLm)中的一或多个)或第一数据线410(例如,多个位线(BL0至BLn)中的一或多个)中的一或多个,如上文所描述。

存储器装置400可以包括感测电路系统,例如感测放大器420,被配置成使用第一数据线410确定(例如,读取)存储单元404上的数据值或确定要写入的数据的值。例如,在存储器单元404的所选择的串中,感测放大器420中的一或多个可响应于通过所选择的串在存储器阵列402中流动到数据线410的读取电流来读取所选择的存储器单元404中的逻辑电平。

存储器装置400外部的一或多个装置可使用I/O线(DQ0至DQN)408、地址线(A0至AX)416或控制线432与存储器装置400通信。输入/输出(I/O)电路426可将数据值传送进或传送出存储器装置400,例如使用I/O线408,例如根据控制线432和地址线416传送进或传送出页缓冲器422或存储器阵列402。在将数据编程到存储器阵列402的相关部分中之前,页缓冲器422可以存储从存储器装置400外部的一或多个装置接收的数据,或在将数据传输到存储器装置400外部的一或多个装置之前,页缓冲器422可以存储从存储器阵列402读取的数据。

列解码器414可接收地址信号(A0至AX)416并将其解码为一或多个列选择信号(CSEL1至CSELn)。选择器424(例如,选择电路)可接收列选择信号(CSEL1至CSELn)并选择页缓冲器422中表示将从存储器单元404读取或将编程到存储器单元中的数据的值的数据。可以使用第二数据线418在页面缓冲器422与I/O电路426之间传送所选择的数据。在一些实例中,快闪转换层(未图示)可将主机提供的地址映射到行解码器412和列解码器414用以读取存储器阵列402中的数据的物理存储器地址。

存储器控制单元430可从外部源或电源(例如,内部或外部电池,AC到DC转换器等)接收正电源信号和负电源信号,例如电源电压Vcc 434和接地电位Vss 436。在某些实例中,存储器控制单元430可以包括调节器428以在内部提供正或负电源信号。

如上所述,本文描述的系统和方法通过提供减少NAND操作(特别是那些花费大量时间的操作,诸如NAND编程和NAND擦除操作)期间的能耗的系统挂起/唤醒操作来提供存储装置的有效能量使用。例如,图5图示示出在样本实施例中,对参考图1描述的类型的存储器装置的TLC存储器单元区域的编程的时序图500。如图所示,当NAND组件执行用于编程TLC存储器单元的第一级的第一遍510时,存储器控制器115的处理器(CPU)(或监督编程操作的处理器的至少一部分)基本上是未激活的,在520处等待NAND操作的完成。如所属领域的技术人员已知,可以不同方式完成编程,包括针对MLC单元的多个经编程层级中的每个通过一或多遍过程来编程。

在许多实例中,一旦处理器已启动编程操作,便例如通过图4的实例存储器装置的存储器控制单元430将编程处理到个别NAND存储器装置,所述存储器控制单元接着将对存储器阵列的所选择的区域执行编程的特定物理(电)操作。类似地,当NAND存储器装置执行用于编程TLC单元的第二级的第二遍530时,处理器(或其部分)也实质上是未激活的,在540处等待NAND操作完成。NAND页的编程对于TLC阵列可能需要高达3ms,而对于QLC阵列可能需要高达10ms;并且对于数据擦除操作可能需要高达30ms。在这些操作520和540期间,NAND存储器控制器115的相关联的处理器(或其部分)基本上是未激活的,这使得存储器控制器115的处理器在ICCQ上消耗不必要的能量。根据本描述,在这种“等待”时间期间,将存储器控制器的一部分(在许多实例中,处理器的至少一部分)置于较低功率模式中,且在预期操作完成时或发生需要存储器控制器的“注意”的另一事件时被唤醒。

如本文所述,“较低功率模式”可以是由特定存储器技术和/或操作协议支持的数个低功率状态中的任一个。例如,JEDEC UFS v3.0规范支持数个功率状态,包括加电和较低(降低的)功率状态,包括预激活、激活、空闲、预断电、断电、预睡眠和睡眠。在不同的存储器技术中,较低功率状态也可称为休眠、停滞、睡眠、深度停滞或深度睡眠状态。睡眠模式可以包括多个低功率模式,每个模式以增加的唤醒时间为代价使用逐渐减少的功率。同样,较低功率模式可以包括时钟门控模式,其中整个存储器控制器的仅一部分(通常为小部分)将保持接通且存储器控制器的其余部分可断开。因此,如本文所使用,“较低功率模式”包括其中停用一或多个存储器控制器资源以减少功率消耗的任何条件。一些较低功率模式可以包括改变处理器或其它组件的时钟速率或另一性能参数。

图6示出实例实施例中的系统挂起硬件600的硬件图,其例如可被实现为图1的存储器控制器115的功率管理电路系统145的一部分。为了本实例的目的,系统挂起硬件600用于挂起对处理器(CPU 620)在存储器控制器115内的操作。唤醒功能将参考图7的系统唤醒硬件700来讨论。虽然系统挂起硬件600和系统唤醒硬件700是彼此互补的电路(并且如下所述可以共享一些组件),但是为了清楚起见,相对于这些附图分别讨论实现互补功能的电路。

在说明性实例中,系统挂起硬件600包括一或多个定时控制单元695,以便为操作系统挂起硬件600和系统唤醒硬件700提供定时和控制功能。定时控制单元(TCU)695可以在电路系统中实施,或者通过使用处理器执行来自软件或固件的指令来实施。在所选择的实施例中,定时控制单元695可以至少部分地通过使用存储器控制器内的处理器来实施;其可以是专用处理器/控制器,或者在一些实施方案中,CPU 620的一部分不受系统硬件600的挂起操作的影响。如下所述,所述TCU通常将包括一或多个定时器,其在功能上至少部分响应于与NAND通信接口690和NAND状态寄存器720的通信,所述NAND状态寄存器可以是例如NAND通信接口内的寄存器,但这不是必需的。

系统挂起硬件600还包括与门610,其将挂起信号发送到存储器控制器的CPU 620以挂起CPU的所选择的操作及/或在所选择的条件下将CPU 620切换到较低功率模式。在一个实例实施例中,当输入A、B和C都是逻辑1与门610时,提供输出,指示:(i)未收到其它内存管理操作;(ii)唤醒时间未到期;以及(iii)在存储器管理操作期间,未从被选择来切换存储器控制器115进入(或退出)较低功率模式的硬件资源接收到中断。在实例实施例中:(i)输入A是来自UFS接口630的指示信号,指示没有接收到新的协议命令供存储器装置110处理;(ii)输入B是空闲寄存器组信号640,其由系统挂起硬件600的TCU 695设置以启用挂起操作;以及(iii)输入C是来自屏蔽寄存器650的输入,指示所有硬件模块,例如电压检测器660、通用异步接收器/发射器(UART)670、温度传感器680和NAND通信接口690都空闲a、d/或处于无错误状态,且屏蔽寄存器650未从NAND通信接口690接收到NAND错误信号。屏蔽寄存器650可由设置信号685设置,该设置信号由系统挂起硬件600提供,以选择(多个)硬件资源,从而在存储器管理操作期间将存储器控制器115切换进入较低功率模式和从较低功率模式切换出来。因此,对于用于将CPU 620切换到较低功率模式的系统挂起硬件600,应在输入A处不接收新的NAND命令,应在输入B处设置空闲寄存器,且所选择的硬件模块(多个)应在输入C处未激活。此外,基于来自NAND通信接口690的预测延迟(与正在执行操作的一或多个NAND装置通信),CPU(和/或其它硬件)可被置于适当的低功率模式。例如,到下一个事件(或者如果没有事件)的时间越多,功率节省模式可以越积极。

在实例实施例中,与门610的唤醒时间由系统挂起硬件600的TCU 695提供,这又基于正在执行的NAND命令来建立。例如,NAND通信接口690向系统挂起硬件600提供相应的信号,以确定是否超过最小休眠时间,从而有足够的时间使CPU 620进入较低功率模式。当这样的时间可用时,TCU 695设置定时器来建立CPU 620返回正常操作的唤醒时间。在实例实施例中,响应于NAND存储器阵列120的NAND管芯操作,通过使用NAND通信接口来建立唤醒定时器。

本领域的技术人员将理解,门610不必是与门。例如,当以下每项均为真时,可使用与非门输出挂起信号:

a)没有其它存储器操作:该信号将为真,直到命令到达然后变为假;b)定时器未到期:该信号将为真,直到定时器到期,然后变为假;以及c)没有中断:该信号将为真,直到发生中断然后变为假。另一方面,这些子信号中的每个可以以肯定的方式表示,很可能每个都是中断信号:a)存在存储器操作--该信号将为假,直到命令到达,然后将变为真;b)定时器已经到期--该信号将为假,直到定时器启动然后变为真;以及c)存在中断--该信号将为假,直到发生中断,然后变为真。在后一种情况下,使用或非门来发出挂起信号。其它变化对于本领域技术人员来说是清楚的。

在实例实施例中,系统挂起硬件600TCU 695管理系统挂起硬件600。例如,在切换输入A处的NAND长时间消耗操作以指示正在处理耗时的NAND操作(即,编程/擦除/复制回)之后,如果没有其它任务需要运行,如果在输入B处设置空闲寄存器,且如果没有其它硬件是激活的,则将CPU 620置于空闲状态。系统挂起硬件600还配置定时器以基于由NAND通信接口690提供的对NAND操作时间的预测来设置从硬件挂起状态的唤醒时间。系统挂起硬件600还设置硬件屏蔽寄存器650以选择其忙状态选通系统挂起硬件600以将CPU 620切换到较低功率模式的硬件的源。系统挂起硬件600还设置屏蔽寄存器650以指定其中断应在较低功率模式结束时唤醒CPU 620的硬件的来源。例如,中断可以是到达输入A的新协议命令,纠错(ECU)数据解码完成,UART串行通信端口/协议;联合测试行动小组标记(JTAG);和/或在输入C处切换的通用输入/输出(GPIO)外围信号、电压电平检测等。硬件屏蔽寄存器650与系统唤醒硬件700共享,如下文所述。

图7示出系统唤醒硬件700的实例实施方案的硬件图,在实例实施例中,该系统唤醒硬件被提供为存储器控制器115(图1)的一部分。在所描绘的实例中,系统唤醒硬件700包括唤醒CPU 620的或门710,当TCU 695内的定时器在输入C处到期时,在输入B处接收新协议命令,或在输入A处从屏蔽寄存器650接收指示所选择的硬件组件中的任一者已变为激活的且产生中断的硬件中断。因此,如果任何指示的条件被满足,则CPU 620被唤醒并从较低功率模式切换到正常操作。

一旦CPU 620被唤醒,唤醒系统700检查定时器是否到期或CPU 620是否被输入A处的硬件中断唤醒。如果CPU 620被定时器唤醒,则CPU检查NAND状态寄存器720以确定NAND操作是否已经完成。另一方面,如果CPU 620被输入A处的硬件中断唤醒,则620 CPU处理硬件所请求的任务。此后,CPU 620检查等待时间是否仍大于预测的剩余NAND操作时间。如果是,可以将类似的系统硬件配置为重新进入系统挂起模式。如果没有未决的NAND操作,则CPU620可被硬件事件唤醒。

图8示出用于多处理器核(标识为CPU1和CPU2)的系统挂起硬件800的实例实施方案的硬件图。系统挂起硬件800将图6的系统挂起硬件600与通常以805表示的附加挂起电路合并,以控制CPU2 820的操作,该附加挂起电路可以是例如第二处理器核,但在其它实例中可以是第二处理器。在实例实施例中,处理器核可以独立地睡眠。而且,一个处理器/核可以控制另一处理器/核的睡眠操作。在所示出的实施例中,以图6的实施例复制或共享组件(例如,与门810对应于与门610且空闲寄存器设置信号840对应于空闲寄存器设置信号640)。然而,硬件状态涉及向各个核心处理器,CPU 620(CPU1)或CPU2 820提供输入的元件的硬件状态。此外,在此实施例中,可响应于每个相应核心可能已在NAND存储器阵列120上启动的多个存储器操作而为所述核心中的每个提供多个定时器。在一些实例中,这些多个定时器可以包括在单个TCU 695内;或者,如在所描绘的实例中所描绘,通过单独的TCU 895。而且,在该实施例中,唤醒系统700在开始NAND操作之后检查是否仍然需要CPU1 620。如果不是,则CPU1 620进入挂起/较低功率模式。唤醒系统700还在TCU 695、895中设置相应的定时器,其中基于对每个核的相应NAND操作(多个)完成的预测来设置期望的唤醒定时。例如,对于包括四个NAND管芯的NAND阵列,CPU1可以启动第一管芯上的第一编程操作和第二管芯上的擦除操作;而CPU2可以在第三管芯上启动第二编程操作。CPU1可从NAND通信接口690接收定时器设置,以在TCU 695中设置多个定时器,例如用于第一编程操作的第一定时器设置为2ms,并且用于擦除操作的第二定时器设置为10ms。然而,如果由CPU2启动的第三管芯上的第二编程操作包括实质上更多的正被编程的数据,则TCU 895中的定时器可以在八个8ms处建立,以响应来自NAND通信接口690的通信。系统挂起硬件800还可配置系统挂起硬件800输入屏蔽寄存器650和850来为每个处理器选择源硬件,对于每个处理器,BUSY状态将自动选通系统挂起硬件600和805以进入较低功率模式。系统挂起硬件800还可配置系统挂起硬件的输出屏蔽寄存器,使得挂起信号将通过输出屏蔽寄存器以选择将置于较低功率模式的硬件(例如CPU、ECU、外围装置等)。其活动可产生中断以降低动态功率的硬件并设置系统挂起硬件600/800的寄存器位以识别CPU 620/820和/或其它组件已被释放并准备进入较低功率模式。例如,在较低功率模式是时钟门控模式的情况下,系统可以门控时钟以减慢或停止以节省功率。在这种情况下,“挂起”信号减慢或停止时钟或者向CPU 620和/或CPU 830发送信号以停止。因此,仅核心的一小部分或核心外部的存储器控制器的一部分将保持在“始终开启”功率域中,且核心可处于较低功率模式中。

图9示出用于多核环境的实例系统唤醒硬件900的硬件图。系统唤醒硬件900包括图7的系统唤醒硬件700,并包括附加的唤醒硬件电路905。此外,硬件电路包括第二或门910,以便为CPU2 820提供唤醒指令。在该实施例中,组件被复制或与图7的实施例共享。如前所述,系统挂起硬件800的屏蔽寄存器650和850各自相应地与系统唤醒硬件900共享。在所描绘的实例实施例中,TCU 695中的单个定时器可经耦合以提供相应定时器信号作为到或门710和910中的每个的输入。然而,在其它实施例中,如参考图8所讨论的,在单独的TCU695和895中的单独的定时器可用于将定时器信号提供给相应的或门710、910(或提供给配置成生成唤醒信号给每个CPU 620/820的其它逻辑或电路系统)。

图10A至B示出实施例中由存储器控制器115(图1)实施的挂起/唤醒系统的操作流程图。所描绘的实例被配置成将处理器的一部分置于较低功率状态。尽管为清楚起见未明确描述,但可通过相同操作类似地将额外组件置于较低功率状态。类似地,代替处理器,存储器控制器内的其它电路系统而不是所述处理器可被置于较低功率状态。

在1000处,存储器控制器115检查是否正在实施耗时的NAND操作(即,编程/擦除/复制回)。该信息可用作NAND通信接口690为任何正在进行的操作提供的NAND操作时间的预测。如果在处理这样的操作,则存储器控制器115在1010处检查是否需要运行任何其它处理器任务(如在该实例中可以通过执行软件或固件来实施)。关于另一任务是否需要运行的确定可以相对于整个处理器,或者例如相对于处理器的所选核心来进行。例如,在使用多核处理器的情况下,在一些实例中,可以将对阵列中的各个存储器管芯执行的操作分配给处理器的单独核。

如果没有其它任务需要运行,则CPU 620在1020处被置于空闲状态(较低功率模式)(这可能导致改变整个处理器的操作参数,或仅仅改变其一部分);并且(TCU 695)定时器在1030处被配置成基于NAND操作时间的预测来设置从较低功率状态的唤醒时间,例如可以由NAND通信接口690提供。如上所述,基于NAND通信接口690中的预测延迟,CPU 620可被置于适当的低功率模式。例如,到下一事件的时间越多(或者如果没有事件未决),则低功率模式可能越积极。任选地,在1040处系统屏蔽寄存器650/850也被设置以选择硬件的源,其忙状态选通系统挂起硬件600以将CPU 620切换到较低功率模式;并且还任选地,可以在1050处被配置为指定其中断应当在较低功率模式结束时唤醒CPU 620的硬件源。这两个操作都是任选的,因为在一些系统中,可以独立于任何单独的NAND操作来设置屏蔽寄存器,例如系统启动时。和/或这样的硬件资源(多个)可以是预先建立的或CPU 620和/或TCU 695,例如在系统启动时或在装置制造时。

系统唤醒硬件在1055处监测(例如通过图7中的或门710)是否发生了可能的唤醒事件,该可能的唤醒事件可以包括多种类型的事件,例如:新的NAND操作、硬件中断、或TCU695中的定时器的到期等。一旦接收到硬件中断或新的NAND操作,系统唤醒硬件将唤醒CPU620,如1060处所示。一旦被唤醒,CPU 620将通过在1065处确定定时器是否已经到期来识别唤醒机制;并且如果不是,则在1070处确定接收到什么硬件中断或新操作;并且将在1075处理中断或新操作。

如果在1065处确定定时器已经到期,则CPU 620将检查以确定NAND操作是否已完成,如1080处所指示。类似地,当在1075处完成硬件中断或新操作的处理时,CPU将在1080处检查NAND操作是否已完成。如果确定NAND操作已完成,则CPU 620保持唤醒,如1055处所指示。如果确定NAND操作尚未完成,则CPU 620将在1090处确定存储器操作的剩余时间是否大于定时器上的剩余时间(由TCU 695建立),且如果是,则将如1095处所指示继续低功率模式,返回到操作1020。如果存储器操作的剩余时间不大于定时器上的剩余时间,则CPU 620将保持唤醒,如1085处所示。受益于本公开的本领域技术人员将清楚,可以对上述方法进行修改。例如,在1055处确定任何类型的唤醒事件可导致在1060处唤醒CPU。

因此,在实例实施例中,提供硬件挂起机制以在NAND操作完成时将存储器控制器115的处理器(CPU 620)置于较低功率模式,而不是简单地在处理器空闲时等待NAND操作完成。提供定时器以将CPU 620从较低功率模式中唤醒,并且硬件屏蔽选择使得挂起系统硬件能够响应影响对CPU 20的资源的需要的选通条件。因此,通过减少处理器和/或其它处理电路系统的空闲时间,挂起系统和唤醒系统协作以在NAND操作期间节省CPU能量。还将了解,通过设置定时器以在已知持续时间预测NAND忙操作,可进一步优化睡眠/唤醒时间和功率节省。同样,在可能的情况下,NAND系统可尽可能在唤醒CPU 620之前将数据解码并存放在缓冲器中并释放相关联的资源,借此允许CPU 620休眠较长的持续时间。

在实例实施例中,在存储器控制器115内可以有单个(或两个)处理器或处理器核,其执行指令以执行诸如关于图10A至B所讨论的实例的方法。一些实例实施例可以具有功率管理处理器--可能被实施为存储器控制器115内的单独的,可能更小的处理器或逻辑块;或者可替代地实施为处理器的小功率管理核心。在这样的实施例中,存储器控制器115能够在主处理器(直接控制存储器操作)处于低功率模式时执行指令。在这样的实例中,主处理器(例如CPU 620)将不会被唤醒,除非被功率管理处理器(或其它逻辑结构)唤醒。

图11示出可在其上执行本文所讨论的任何一或多个技术(例如,方法)的诸如存储器控制器之类的实例机器1100的框图。例如,机器1100内的任何存储器系统(主存储器1104、静态存储器1106和大容量存储装置1121)可实施以上相对于图6至10A至B描述的类型的存储器装置挂起和唤醒方法。在可替代的实施例中,机器1100可以作为独立机器操作或者可以连接(例如联网)到其它机器。在网络部署中,机器1100可以在服务器-客户端网络环境中以服务器机器、客户端机器或两者的能力进行操作。在实例中,机器1100可以在对等(P2P)(或其它分布式)网络环境中充当对等机器。机器1100可以是个人计算机(PC)、平板PC、机顶盒(STB)、个人数字助理(PDA)、移动电话、网络装置、IoT装置、汽车系统或能够执行指定由该机器要采取的动作的指令(按顺序或以其它方式)的任何机器。此外,尽管仅示出单个机器,但是术语“机器”还应被认为包括单独或联合执行指令集(或多个指令集)以执行本文讨论的任何一或多个方法的任何机器集合,诸如云计算、软件即服务(SaaS)、其它计算机集群配置。

如本文描述,实例可以包括逻辑、组件、装置、封装或机构,或者可以由其操作。电路系统是在包括硬件(例如,简单电路、门、逻辑等)的有形实体中实现的电路的集合(例如,一组电路)。电路系统成员资格可以随时间推移以及潜在的硬件可变性而灵活变化。电路系统包括可以在操作时单独或组合执行特定任务的成员。在实例中,电路系统的硬件可以被不变地设计为执行特定操作(例如,硬连线)。在实例中,电路系统的硬件可以包括可变连接的物理组件(例如,执行单元、晶体管、简单电路等),所述物理组件包括经物理修改(例如,磁性、电学、可移动地放置不变质量的粒子等)以对特定操作的指令进行编码的计算机可读介质。在连接物理组件时,硬件部件的基础电性质会发生变化,例如从绝缘体变为导体,反之亦然。所述指令使得参与的硬件(例如,执行单元或加载机构)能够经由可变连接在硬件中创建电路系统的成员以在操作时执行特定任务的一部分。因此,当装置正在操作时,计算机可读介质通信地耦合到电路系统的其它组件。在实例中,任何物理组件都可以在一个以上电路系统的一个以上成员中使用。例如,在操作中,执行单元可以在一个时间点在第一电路系统的第一电路中使用,并且可以在不同的时间被第一电路系统中的第二电路或第二电路系统中的第三电路重新使用。

机器(例如,计算机系统)1100(例如,主机装置105、存储器装置110等)可以包括硬件处理器1102(例如,CPU、图形处理单元(GPU)、硬件处理器核心或其任何组合,例如存储器控制器115等)、主存储器1104和静态存储器1106,其中的一些或全部可经由互连(例如,总线)1108彼此通信。机器1100还可以包括显示单元1110、字母数字输入装置1112(例如键盘)和用户界面(UI)导航装置1114(例如鼠标)。在实例中,显示单元1110、输入装置1112和UI导航装置1114可以是触摸屏显示器。机器1100还可以包括信号生成装置1118(例如,扬声器)、网络接口装置1120和一或多个传感器1116,例如全球定位系统(GPS)传感器、罗盘、加速度计或其它传感器。机器1100可以包括输出控制器1128,诸如串行(例如,USB、并行或其它有线或无线(例如,红外(IR)、近场通信(NFC)等)连接,以与一或多个外围装置(例如,打印机、读卡器等)进行通信或控制一或多个外围装置。

机器1100可以包括机器可读介质1122,在其上存储了一或多组数据结构或指令1124(例如,固件或软件),这些数据结构或指令体现本文描述的任何一或多个技术或功能或由其使用。在机器1100执行指令1124期间,所述指令还可以完全或至少部分地驻留在主存储器1104内、静态存储器1106内或硬件处理器1102内。在实例中,硬件处理器1102、主存储器1104或静态存储器1106中的一个或任意组合可以构成机器可读介质1122。

虽然将机器可读介质1122示出为单个介质,但术语“机器可读介质”可以包括被配置成存储一或多个指令1124的单个介质或多个介质(例如,集中式或分布式数据库,或相关联的缓存和服务器)。

术语“机器可读介质”可以包括能够存储或编码供机器1100执行且致使机器1100执行本公开的任何一或多个技术的任何介质,或能够存储、编码或携载由此类指令使用或与此类指令相关联的数据结构的任何介质。非限制性的机器可读介质实例包括固态存储器以及光和磁介质。在实例中,质量机器可读介质包含具有多个具有不变(例如静止)质量的粒子的机器可读介质。因此,质量机器可读介质不是瞬时传播信号。质量机器可读介质的具体实例可以包括:非易失性存储器,诸如半导体存储器装置(例如,电可编程只读存储器(EPROM)、电可擦除可编程只读存储器(EEPROM))和快闪存储器装置;磁盘,例如内部硬盘和可移动磁盘;磁光盘;以及CD-ROM和DVD-ROM盘。

指令1124(例如,软件、程序、操作系统(OS)等)或其它数据存储在存储装置1121上,可由存储器1104存取以供处理器1102使用。存储器1104(例如,DRAM)通常是快速的,但易失性的,且因此是与大容量存储装置1121不同类型的存储装置(例如,SSD),其适合于长期存储,包括在“关闭”状态下。指令1124或由用户或机器1100使用的数据通常被加载到存储器1104中,以供处理器1102使用。当存储器1104充满时,可以分配来自大容量存储装置1121的虚拟空间以补充存储器1104;然而,因为大容量存储装置1121装置通常比存储器1104慢,且写入速度通常至少是读取速度的两倍慢,所以虚拟存储器的使用可由于存储装置等待时间而大幅降低用户体验(与例如DRAM的存储器1104相比)。此外,将大容量存储装置1121用于虚拟存储器可极大地减少大容量存储装置1121的使用寿命。

与虚拟存储器相比,为了避免对大容量存储装置1121进行分页,虚拟存储器压缩(例如,

为移动电子装置优化的存储装置,或移动存储,传统上包括MMC固态存储装置(例如,微安全数字(microSD

指令1124还可以使用传输介质经由网络接口装置1120利用数个传输协议(例如,帧中继、因特网协议(IP)、传输控制协议(TCP)、用户数据报协议(UDP)、超文本传输协议(HTTP)等)中的任何一个通过通信网络1126来传输或接收。实例通信网络可以包括局域网(LAN)、广域网(WAN)、分组数据网络(例如,因特网)、移动电话网络(例如,蜂窝网络)、普通老式电话(POTS)网络,以及无线数据网络(例如,称为

术语“传输介质”应被理解为包括能够存储、编码或携带由机器1100执行的指令的任何无形介质,并且包括数字或模拟通信信号或其它无形介质以促进这种软件的通信。

为了更好地说明本文所述的方法和设备,下面将一组非限制性的实例实施例列出为数字标识的实例。

实例1是一种存储器装置,包含:存储器阵列;以及存储器控制器,被配置成从主机装置接收命令,所述存储器控制器包括处理电路系统,所述处理电路系统包括一或多个处理器,且被配置成执行操作,所述操作包括:启动所述存储器阵列中的第一存储器管理操作;在所述第一存储器管理操作期间将所述存储器控制器中的至少一个组件置于较低功率模式;基于所述第一存储器管理操作的预测完成时间设置唤醒时间;以及当唤醒事件和所述唤醒时间到期中的至少一个发生时将所述存储器控制器切换出所述较低功率模式。

在实例2中,实例1的所述主题,其中所述存储器阵列是NAND存储器阵列,并且所述存储器管理操作是NAND存储器管理操作。

在实例3中,实例2的所述主题,其中所述NAND存储器管理操作是所述NAND存储器阵列的编程、所述NAND存储器阵列的擦除和所述NAND存储器阵列的读取中的一个。

在实例4中,实例1至3中的任何一或多个的所述主题,其中所述唤醒事件包含:在所述存储器控制器处请求第二存储器操作。

在实例5中,实例4的所述主题,其中在所述存储器控制器处从主机接收对第二存储器操作的所述请求。

在实例6中,实例4至5中的任何一或多个的所述主题,其中在所述存储器控制器中生成所述存储器控制器对第二存储器操作的所述请求。

在实例7中,实例1至6中的任何一或多个所述主题,其中所述唤醒事件包含来自指定硬件组件的硬件中断。

在实例8中,实例1至7中的任何一或多个的所述主题,其中将所述存储器控制器置于所述较低功率模式包含:当未接收到其它存储器管理操作、未从被指定为将所述存储器控制器切换进所述较低功率模式和从所述较低功率模式切换出的硬件资源接收到中断时向所述存储器控制器提供挂起信号。

在实例9中,实例1至8中的任何一或多个的所述主题,其中将所述存储器控制器置于所述较低功率模式包含:从在输入处至少接收是否已经接收到另一存储器管理操作的指示、所述唤醒时间是否已经到期的指示、以及是否已经从被指定为将所述存储器控制器切换进所述较低功率模式和从所述较低功率模式切换出的所述硬件资源接收到中断的指示的门向所述存储器控制器输出挂起信号。

在实例10中,实例1至9中的任何一或多个的所述主题,其中设置所述唤醒时间包含:从与所述存储器阵列通信的接口接收所述存储器管理操作的所述预测完成时间:以及基于所述存储器管理操作的所述预测完成时间,进入选择的功率节省模式。

在实例11中,实例10的所述主题,其中至少部分响应于所述第一存储器管理操作的所述预测完成时间,从多个可能的功率节省模式中选择所述选择的功率节省模式。

在实例12中,实例1至11中的任何一或多个的所述主题,其中在接收到所述唤醒事件或定时器到期中的至少一个时将所述存储器控制器切换出所述较低功率模式包含:在所述较低功率模式下向所述存储器控制器的所述组件提供唤醒信号。

在实例13中,实例12的所述主题,其中将所述存储器控制器切换出所述较低功率模式包含:从在输入处至少接收是否已经接收到另一存储器管理操作的指示、所述唤醒时间是否已经到期的指示、以及是否已经从被指定为将所述存储器控制器切换进所述较低功率模式和从所述较低功率模式切换出的硬件资源接收到中断的指示的或门输出所述唤醒信号到所述存储器控制器。

在实例14中,实例1至13的任何一或多个所述主题任选地包括指示所述第一存储器管理操作的状态的状态寄存器。

在实例15中,实例14的所述主题,其中所述存储器控制器操作还包含:确定所述唤醒时间是否已经到期、以及检查所述状态寄存器以确定所述第一存储器管理操作是否已经完成;并且,在所述唤醒时间到期或所述第一存储器管理操作完成时,将所述存储器控制器中的所述至少一个组件切换出所述较低功率模式。

在实例16中,实例15的所述主题,其中当所述存储器控制器确定是否已经接收到所述中断时,所述存储器控制器还执行指令以处理由所述中断请求的任务,然后检查所述存储器管理操作是否已经完成,并且当完成时,将所述存储器控制器从所述较低功率模式切换出。

在实例17中,实例1至16中的任何一或多个的所述主题,其中所述存储器控制器包含至少两个处理器,其中第一处理器执行指令以执行所述至少两个处理器的挂起/唤醒操作。

实例18是一种管理存储器装置的功率使用的方法,所述存储器装置包含存储器阵列和存储器控制器,所述存储器控制器被配置成从主机装置接收指令,所述方法包括:启动所述存储器阵列中的第一存储器管理操作;在所述第一存储器管理操作期间将所述存储器控制器中的至少一个组件置于较低功率模式;基于所述第一存储器管理操作的预测完成时间设置唤醒时间;以及当唤醒事件和所述唤醒时间到期中的至少一个发生时将所述存储器控制器切换出所述较低功率模式。

在实例19中,实例18的所述主题,其中所述存储器阵列是NAND存储器阵列,并且在存储器管理操作期间将所述存储器控制器置于较低功率模式包含:所述NAND存储器阵列的编程、所述NAND存储器阵列的擦除和所述NAND存储器阵列的读取中的一个期间将所述存储器控制器置于较低功率模式。

在实例20中,实例18至19中的任何一或多个的所述主题,其中将所述存储器控制器置于较低功率模式包含:在所述存储器管理操作期间,当未接收到其它存储器管理操作、所述唤醒时间未到期、并且未从被选择为将所述存储器控制器切换进所述较低功率模式和从所述较低功率模式切换出的硬件资源接收到中断时,向所述存储器控制器提供挂起信号。

在实例21中,实例20的所述主题,其中将所述存储器控制器置于所述较低功率模式包含:在所述存储器管理操作期间,从在输入处至少接收是否已经接收到另一存储器管理操作的指示、所述唤醒时间是否已经到期的指示、以及是否已经从被选择为将所述存储器控制器切换进所述较低功率模式和从所述较低功率模式切换出的所述硬件资源接收到中断的指示的门向所述存储器控制器输出所述挂起信号。

在实例22中,实例18至21中的任何一或多个的所述主题,其中设置所述唤醒时间包含:从与所述存储器阵列通信的存储器通信接口接收所述存储器管理操作的所述预测完成时间,以及基于所述存储器管理操作的所述预测完成时间,在所述存储器管理操作的更长预测完成时间内进入更积极的功率节省模式。

在实例23中,实例18至22中的任何一或多个的所述主题,其中所述存储器阵列包含多个存储器管芯,并且其中基于所述存储器管理操作的所述预测完成时间设置唤醒时间包含:为由相应存储器管芯正在执行的不同存储器操作设置单独的唤醒时间。

在实例24中,实例18至23中的任何一或多个的所述主题,其中当接收到另一存储器管理操作、所述唤醒时间到期以及从被选择为将所述存储器控制器切换进所述较低功率模式和从所述较低功率模式切换出的硬件资源接收到中断中的至少一个时,将所述存储器控制器切换出所述较低功率模式包含:在所述存储器管理操作期间,当已经接收到另一存储器管理操作、所述唤醒时间已经到期以及已经从被选择为将所述存储器控制器切换进所述较低功率模式和从所述较低功率模式切换出的硬件资源接收到中断时,向所述存储器控制器提供唤醒信号。

在实例25中,实例24的所述主题,其中将所述存储器控制器切换出所述较低功率模式包含:在所述存储器管理操作期间,从在输入处至少接收是否已经接收到另一存储器管理操作的指示、所述唤醒时间是否已经到期的指示、以及是否已经从被选择为将所述存储器控制器切换进所述较低功率模式和从所述较低功率模式切换出的硬件资源接收到中断的指示的或门输出所述唤醒信号到所述存储器控制器。

在实例26中,实例24至25中的任何一或多个的所述主题任选地包括:当唤醒时间已经到期时,检查指示所述存储器管理操作的状态的状态寄存器以确定所述存储器管理操作是否已经完成,并且当已经完成时,将所述存储器控制器切换出所述较低功率模式。

在实例27中,实例24至26中的任何一或多个的所述主题任选地包括:当已经接收到中断时,处理由所述中断请求的任务,然后检查所述存储器管理操作是否已经完成,并且当已经完成时,将所述存储器控制器切换出所述较低功率模式。

实例28是至少一种非暂时性装置可读存储介质,其包含指令,所述指令在由存储器控制器的一或多个处理器执行时使得所述一或多个处理器执行以下操作,所述操作包含:启动存储器阵列中的第一存储器管理操作;在所述第一存储器管理操作期间将所述存储器控制器中的至少一个组件置于较低功率模式;基于所述第一存储器管理操作的预测完成时间设置唤醒时间;以及当唤醒事件和所述唤醒时间到期中的至少一个发生时将所述存储器控制器切换出所述较低功率模式。

在实例29中,根据实例28的所述主题,其中所述存储系统包含NAND存储器阵列,所述介质还包含指令,用于通过在对所述NAND存储器阵列进行编程、对所述NAND存储器阵列进行擦除和对所述NAND存储器阵列进行读取中的一个期间将所述存储器控制器置于较低功率模式来在所述存储器管理操作期间将所述存储器控制器置于较低功率模式。

在实例30中,实例28至29中的任何一或多个的所述主题可任选地包括指令,用于通过在所述存储器管理操作期间,当未接收到其它存储器管理操作、所述唤醒时间未到期、并且未从被选择为将所述存储器控制器切换进所述较低功率模式和从所述较低功率模式切换出的硬件资源接收到中断时,向所述存储器控制器提供挂起信号来将所述存储器控制器置于所述较低功率模式。

在实例31中,实例29至30中的任何一或多个的所述主题任选地包括指令,用于通过从在输入处至少接收是否已经接收到另一存储器管理操作的指示、所述唤醒时间是否已经到期的指示、以及是否已经从被选择为将所述存储器控制器切换进所述较低功率模式和从所述较低功率模式切换出的所述硬件资源接收到中断的指示的门向所述存储器控制器输出所述挂起信号来将所述存储器控制器置于所述较低功率模式。

在实例32中,实例28至31中的任何一或多个的所述主题任选地包括指令,用于从与所述存储器阵列通信的存储器通信接口接收所述存储器管理操作的所述预测完成时间,以及基于所述存储器管理操作的所述预测完成时间,在所述存储器管理操作的更长预测完成时间内进入更积极的功率节省模式来设置所述唤醒时间。

在实例33中,根据实例28至32中的任何一或多个的所述主题,其中所述存储系统包含多个存储器管芯,所述主题还包含指令,用于通过为由相应存储器管芯正在执行的不同存储器操作设置单独的唤醒时间来基于所述存储器管理操作的预测完成时间设置唤醒时间。

在实例34中,实例28至33中的任何一或多个的所述主题任选地包括指令,用于通过在所述存储器管理操作期间,当已经接收到另一存储器管理操作、所述唤醒时间已经到期以及已经从被选择为将所述存储器控制器切换进所述较低功率模式和从所述较低功率模式切换出的硬件资源接收到中断时,向所述存储器控制器提供唤醒信号来当接收到另一存储器管理操作、所述唤醒时间到期以及从被选择为将所述存储器控制器切换进所述较低功率模式和从所述较低功率模式切换出的硬件资源接收到中断中的至少一个时,将所述存储器控制器切换出所述较低功率模式。

在实例35中,实例34的所述主题可任选地包括指令,用于通过在所述存储器管理操作期间,从在输入处至少接收是否已经接收到另一存储器管理操作的指示、所述唤醒时间是否已经到期的指示、以及是否已经从被选择为将所述存储器控制器切换进所述较低功率模式和从所述较低功率模式切换出的硬件资源接收到中断的指示的或门输出所述唤醒信号到所述存储器控制器来将所述存储器控制器切换出所述较低功率模式。

在实例36中,实例34至35中的任何一或多个的所述主题任选地包括指令,用于当唤醒时间已经到期时,检查指示所述存储器管理操作的状态的状态寄存器以确定所述存储器管理操作是否已经完成,并且当已经完成时,将所述存储器控制器切换出所述较低功率模式。

在实例37中,实例34至36中的任何一或多个的所述主题可任选地包括指令,用于当已经接收到中断时,处理由所述中断请求的任务,然后检查所述存储器管理操作是否已经完成,并且当已经完成时,将所述存储器控制器切换出所述较低功率模式。

在实例38中,实例1至17中任何实例的所述存储器装置可并入实例1至17的一或多个其它实例中发现的结构、特征或功能性。

在实例39中,实例1至17中任何实例的所述存储器装置可被配置成执行实例18到27的任何方法。

在实例40中,实例1至17中任何实例的所述存储器装置可并入实例28至37中的任一机器可读介质。

在实例41中,实例18至27的任何方法可适于通过使用根据实例1至17的任何实例的存储器装置来执行。

实例42,实施18至27的任何方法可适合于包括在实例18至27的一或多个其它实例中识别的操作或功能。

在实例43中,实例28至37中任何实例的机器可读介质可适于执行实例18至27中的任何方法。

在实例44中,实例1至17的任何存储器装置可以包括实例28至37的非暂时性装置可读存储介质,其被配置成存储可执行以执行存储器装置的一或多个操作的指令。

在实例45中,实例1至17的任何存储器装置可并入到电子系统中,所述电子系统还包含主机处理器和在所述主处理器与所述存储器装置之间延伸的通信总线。

在实例46中,实例18至27的任何方法可以由包括主机处理器和在所述主机处理器和所述存储器装置之间延伸的通信接口的电子系统执行。

上述详细描述包括对附图的参考,附图形成详细描述的一部分。附图通过说明的方式示出其中可以实践本文描述的系统和方法的具体实施例。这些实施例在本文也被称为“实例”。此些实例可以包括除了示出或描述的那些之外的元素。然而,本发明人还设想了仅提供示出或描述的那些元素的实例。此外,本发明人还考虑使用相对于本文示出或描述的特定实例(或其一或多个方面),或者相对于其它实例(或其一或多个方面)示出或描述的那些元素(或其一或多个方面)的任何组合或置换的实例。

在本文件中,如在专利文件中通常使用的,术语“一”或“一个”用于包括一或多于一个,其与“至少一个”或“一或多个”的任何其它情况或使用无关。在本文件中,除非另有说明,术语“或”用于指非排他性的或,使得“A或B”可以包括“A但不是B”、“B但不是A”和“A和B”。在随附权利要求中,术语“包括”和“在其之中”用作相应术语“包含”和“其中”的简明英语等同物。此外,在所附权利要求中,术语“包括”和“包含”是开放式的,即,包括除了在权利要求中的该术语之后列出的那些元素之外的元素的系统、装置、物品或过程仍然被认为落入该权利要求的范围内。此外,在随附权利要求中,术语“第一”、“第二”和“第三”等仅用于作为标记,而无意为其对象强加数值要求。

在各种实例中,本文描述的组件、控制器、处理器、单元、引擎或表可以包括存储在物理装置上的物理电路系统或固件等。如本文所使用的,“处理器”意味着任何类型的计算电路,例如但不限于微处理器、微控制器、图形处理器、数字信号处理器(DSP)或任何其它类型的处理器或处理电路,包括一组处理器或多核装置。

根据本公开及本文中所描述的各种实施例包括利用竖直结构的存储器单元(例如,存储器单元的NAND串)的存储器。如本文所使用的,将相对于其上形成存储器单元的衬底的表面运用取向形容词(即,将竖直结构看作为远离衬底表面延伸,将竖直结构的底端看作为最接近衬底表面的末端,并且将竖直结构的顶端看作为最远离衬底表面的末端)。

如本文所使用的,操作存储器单元包括从存储器单元读取、向存储器单元写入或擦除存储器单元。将存储器单元置于预期状态的操作在本文中称为“编程”,且可以包括对存储器单元进行写入和/或从存储器单元进行清除(例如,存储器单元可以被编程为擦除状态)。

根据本公开的一或多个实施例,位于存储器装置内部或外部的存储器控制器(例如,处理器、控制器、固件等)能够确定(例如,选择、设置、调整、计算、改变、清除、通信、调适、导出、界定、利用、修改、应用等)磨损周期的数量或磨损状态(例如,记录磨损周期,在发生磨损周期时对存储器装置的操作进行计数,跟踪其发起的存储器系统的操作,评估对应于磨损状态的存储装置特性等)。

根据本公开的一或多个实施例,存储器存取装置可以被配置为随着每次存储器操作向存储器装置提供磨损周期信息。存储器装置控制电路系统(例如,控制逻辑)可以被编程为以补偿对应于磨损周期信息的存储器装置性能变化。存储器装置可接收磨损周期信息并响应于磨损周期信息确定一或多个操作参数(例如,值、特性)。

应当理解,当元件被称为在另一元件“上”、“连接到”或“耦合到”另一元件时,它可以直接在另一元件上、与另一元件连接或耦合,或者可以存在中间元件。相反,当元件被称为“直接”在另一元件“上”、“直接连接到”另一元件或与另一元件“直接耦合”时,不存在中间元件或层。如果在附图中将两个元件示出为用线连接,则两个元件可耦合或直接耦合,除非另有指示。

本文描述的方法实例可以是至少部分地由机器或计算机实施的。一些实例可以包括用指令编码的计算机可读介质或机器可读介质,所述指令可操作用以将电子装置配置为执行以上实例中描述的方法。此些方法的实施方案可以包括诸如微代码、汇编语言代码、高级语言代码等代码。此代码可以包括用于执行各种方法的计算机可读指令。所述代码可以形成计算机程序产品的部分。此外,代码可被有形地存储在一或多个易失性或非易失性有形计算机可读介质上,诸如在执行期间或在其它时间。这些有形计算机可读介质的实例可以包括但不限于硬盘、可移动磁盘、可移动光盘(例如,CD和DVD)、磁带盒、存储卡或棒、RAM、ROM、SSD、UFS装置、eMMC装置等。

以上描述旨在是说明性的,而不是限制性的。例如,上述实例(或其一或多个方面)可以彼此组合使用。可以使用其它实施例,如本领域的普通技术人员在阅读以上描述时使用的。应当理解,它将不用于解释或限制权利要求的范围或含义。此外,在以上详细描述中,可将各种特征组合在一起以简化本公开。这不应当被解释为意味着未经要求保护的公开特征对于任何权利要求是必不可少的。相反,发明主题可在于少于特定公开实施例的所有特征。因此,所附权利要求书由此并入具体详细描述中,其中每个权利要求独立地作为单独的实施例,且预期此类实施例可以各种组合或排列彼此组合。本发明的范围应该参考所附权利要求以及这些权利要求所赋予的等同物的全部范围来确定。

- 管理降低功率的存储器操作

- 经由动态存储器操作状态的存储器功率管理