半导体装置

文献发布时间:2023-06-19 11:55:48

关联申请的相互参照

本申请基于2018年11月23日提出的日本专利申请第2018-219795号,这里引用其记载内容。

技术领域

本发明涉及半导体装置。

背景技术

以往,例如在专利文献1中提出了夹着栅极区域而配置源极区域和漏极区域的半导体元件。源极区域具有与源极区域用的接触件连接的1个接触区域。漏极区域具有与漏极区域用的接触件连接的1个接触区域。接触件是与布线连接的电极。

现有技术文献

专利文献

专利文献1:日本特开平7-122743号公报

发明内容

在半导体技术的领域中,持续地进行异物的筛查等的检查检测率及制造工艺的异物减少对策。但是,在上述以往的技术中,与源极区域及漏极区域连接的接触件是1个。因此,在接触件上附着有异物的情况下,有可能接触断开(contact open)。并且,减少接触断开的不良状况的检查方法尚未确立。因而,需要减少接触断开的不良状况本身。

本发明的目的在于,提供具备能够减少接触断开的不良状况的结构的半导体装置。

本发明的一技术方案的半导体装置包括半导体层、源极区域、漏极区域、栅极电极、第1电极部及第2电极部。

半导体层具有主表面,沿着主表面的面方向中的一个方向而在主表面侧产生沟道。

源极区域及漏极区域以夹着半导体层中的产生沟道的部分的方式形成在半导体层的表层部。

栅极电极形成在沟道的上方,并且沿着主表面的面方向中的一个方向形成。

第1电极部连接到半导体层的主表面中的与源极区域对应的区域。第2电极部连接到半导体层的主表面中的与漏极区域对应的区域。

第1电极部具有连接到与源极区域对应的区域的多个第1接触件。第2电极部具有连接到与漏极区域对应的区域的多个第2接触件。

将半导体层的主表面的面方向中的一个方向定义为栅极电极的栅极宽度方向。多个第1接触件沿着栅极电极的栅极宽度方向配置为一列。多个第2接触件沿着栅极电极的栅极宽度方向配置为一列。

由此,由于设有多个第1接触件,所以第1接触件全部成为接触断开是不容易的。同样,由于设有多个第2接触件,所以第2接触件全部成为接触断开是不容易的。因而,能够减少接触断开的不良状况。

附图说明

关于本发明的上述及其他目的、特征及优点,根据参照附图的下述详细说明会更加明确。

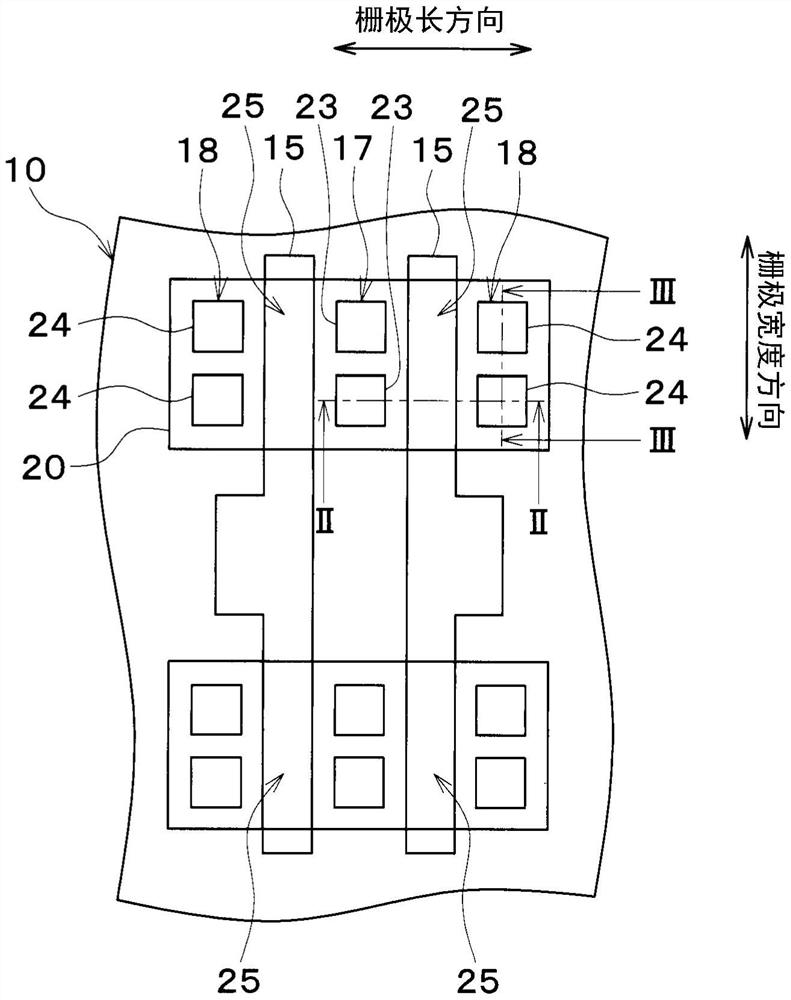

图1是第1实施方式的半导体装置的平面图。

图2是图1的II-II剖视图。

图3是图1的III-III剖视图。

图4是表示第1实施方式的第1电极部的变形例的平面图。

图5是第2实施方式的半导体装置的平面图。

图6是表示第2实施方式的第1电极部的变形例的平面图。

图7是表示第2实施方式的第1电极部的变形例的平面图。

图8是表示第2实施方式的第1电极部的变形例的平面图。

图9是表示第2实施方式的第1电极部的变形例的平面图。

具体实施方式

以下,参照附图说明用来实施本发明的多个实施方式。在各实施方式中有时对于与在先前实施方式中说明的事项对应的部分赋予相同的标号而省略重复说明。在各实施方式中仅说明结构的一部分的情况下,关于结构的其他部分能够应用先前说明的其他实施方式。不仅是在各实施方式中明示了能够具体组合的部分彼此的组合,只要组合不特别产生障碍,即使不明示也能够将实施方式彼此部分地组合。

(第1实施方式)

以下,参照附图对第1实施方式进行说明。本实施方式的半导体装置例如是N型的MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor:MOSFET)。

如图1~图3所示,半导体装置10包括N型的半导体层11、N型的源极区域12、N型的漏极区域13、栅极氧化膜14、栅极电极15、绝缘膜16、第1电极部17及第2电极部18。

如图2及图3所示,半导体层11具有主表面19。半导体层11例如是SOI基板的硅层。半导体层11例如也可以是单独的硅基板。

此外,半导体层11具有P型的阱区域20。阱区域20是在半导体层11的主表面19侧形成的一定的区域。在半导体层11的主表面19侧,沿着半导体层11的主表面19的面方向中的一个方向产生沟道。沟道在阱区域20中的主表面19侧产生。

源极区域12及漏极区域13是在半导体层11的表层部形成的N型的区域。“半导体层11的表层部”是半导体层11的厚度方向上的主表面19侧的区域。表层部包括主表面19。与电源侧电连接的N型的区域成为漏极区域13。与地电位侧电连接的N型的区域成为源极区域12。

源极区域12及漏极区域13以夹着半导体层11中的产生沟道的部分的方式而形成在阱区域20中的主表面19侧。即,源极区域12及漏极区域13隔开一定的间隔而形成。

如图2所示,栅极氧化膜14形成在半导体层11的主表面19中的产生沟道的区域。栅极氧化膜14通过半导体层11的主表面19的氧化处理等而形成。栅极氧化膜14例如是SiO

栅极电极15形成在栅极氧化膜14之上。即,栅极电极15形成在沟道的上方。如果向栅极电极15施加栅极电压,则在半导体层11的表层部产生沟道。由此,在漏极-源极间流过电流。

此外,如图1所示,栅极电极15沿着半导体层11的主表面19的面方向中的一个方向形成。即,栅极电极15被布局为直线状。栅极电极15例如是多晶硅。多晶硅例如通过CVD法形成。

这里,将半导体层11的主表面19的面方向中的一个方向定义为栅极电极15的栅极宽度方向。此外,在半导体层11的主表面19的面方向上,将与栅极宽度方向垂直的方向定义为栅极长方向。由此,源极区域12及漏极区域13沿着栅极宽度方向形成,并且在栅极长方向上分离。

如图2及图3所示,绝缘膜16主要形成在半导体层11的主表面19。绝缘膜16将半导体层11的主表面19中的与源极区域12及漏极区域13对应的区域、栅极氧化膜14以及栅极电极15覆盖。绝缘膜16例如是硅氧化膜。绝缘膜16例如通过CVD法形成。

此外,绝缘膜16具有多个孔21、22。各孔21、22是接触孔。第1孔21设有两个。第1孔21通向半导体层11的主表面19中的与源极区域12对应的区域。两个第1孔21沿着栅极电极15的栅极宽度方向配置为一列。

第2孔22设有两个。第2孔22通向半导体层11的主表面19中的与漏极区域13对应的区域。两个第2孔22沿着栅极电极15的栅极宽度方向配置为一列。另外,绝缘膜16还具有通向栅极电极15的未图示的接触孔。

第1电极部17是源极用的电极。第1电极部17连接到半导体层11的主表面19中的与源极区域12对应的区域。第1电极部17具有连接到与源极区域12对应的区域的两个第1接触件23。

两个第1接触件23分别埋入到两个第1孔21中。即,如图1所示,两个第1接触件23沿着栅极电极15的栅极宽度方向配置为一列。换言之,在栅极长方向上,从栅极电极15到一个第1接触件23的距离与从栅极电极15到另一个第1接触件23的距离相同。

在本实施方式中,两个第1接触件23沿着栅极电极15的栅极宽度方向相互分离地配置。即,两个第1接触件23沿着栅极宽度方向离开。

第2电极部18是漏极用的电极。第2电极部18连接到半导体层11的主表面19中的与漏极区域13对应的区域。第2电极部18具有连接到与漏极区域13对应的区域的多个第2接触件24。

两个第2接触件24分别埋入在两个第2孔22中。即,两个第2接触件24沿着栅极电极15的栅极宽度方向配置为一列。在栅极长方向上,从栅极电极15到一个第2接触件24的距离与从栅极电极15到另一个第2接触件24的距离相同。两个第2接触件24沿着栅极电极15的栅极宽度方向相互分离地配置。

各接触件23、24的平面形状例如是正方形。各接触件23、24的平面形状也可以是长方形。各接触件23、24例如是Al、Cu、W等金属材料。各接触件23、24与未图示的布线连接。各接触件23、24例如通过CVD法形成。

如图1所示,在本实施方式中,栅极电极15在栅极长方向上形成有两条。此外,阱区域20在栅极宽度方向上相互分离地形成有两处。在半导体层11的主表面19的面方向上,两处阱区域20与两条栅极电极15交叉。

在一个阱区域20中,源极区域12位于阱区域20中的两条栅极电极15之间。漏极区域13形成在阱区域20中的没有被两条栅极电极15夹着的位置。即,在栅极长方向上形成有两个半导体元件25。源极区域12对于两个半导体元件25是共通的。

另一个阱区域20也是相同的构造。因而,在图1中将4个半导体元件25表示为1个单元。另外,单元既可以构成为数字单元,也可以构成为模拟单元。

如以上说明的那样,由于在半导体装置10中设有两个第1接触件23,所以第1接触件23双方成为接触断开是不容易的。同样,由于设有两个第2接触件24,所以第2接触件24全部成为接触断开是不容易的。因而,能够减少半导体装置10的接触断开的不良状况。

本发明的发明者们形成许多将各接触件23、24设有2个的半导体装置10,并且调查了成为接触断开的半导体装置10的数量。结果,接触断开的半导体装置10大致是0。根据该结果可知,能够减少接触断开的不良状况。

此外,已知产生通过在半导体层11中流过电流从而开关时间随着半导体层11的温度上升而增加等温度特性。但是,各接触件23、24在栅极宽度方向上配置为一列。换言之,在栅极长方向上,从栅极电极15到各第1接触件23的距离相同,所以能够将在栅极长方向上电流流动的范围限制在最小限度。即,能够将在栅极长方向上产生热的范围限制在最小限度。因而,即使各接触件23、24的数量是两个,也能够提供对于温度特性耐受力强的半导体装置10。

此外,由于在半导体装置10中各接触件23、24设有2个,所以能够得到与设置1个的情况相比对于制造偏差耐受性强的半导体装置10。进而,即使两个第1接触件23中的一个成为接触断开,另一个的电连接也被保持。由此,能够防止半导体元件25的动作速度的下降。

作为变形例,如图4所示,第1电极部17也可以具有3个第1接触件23。在此情况下,3个第1接触件23沿着栅极宽度方向设为一列。此外,第1接触件23并不限于3个,也可以设置4个以上。关于第2电极部18也是同样的。

(第2实施方式)

在本实施方式中,主要对与第1实施方式不同的部分进行说明。如图5所示,第1电极部17具有第1连接部26。第1连接部26是比栅极长方向上的第1接触件23的宽度窄的宽度的电极。第1连接部26将第1接触件23的一个与另一个连接。第1连接部26连接在栅极长方向上的各第1接触件23的中央。

此外,第2电极部18具有第2连接部27。第2连接部27是比栅极长方向上的第2接触件24的宽度窄的宽度的电极。第2连接部27将第2接触件24的一个与另一个连接。第2连接部27连接在栅极长方向上的各第2接触件24的中央。

各连接部26、27埋在形成于绝缘膜16的接触孔中。第1连接部26与源极区域12连接。第2连接部27与漏极区域13连接。

因而,两个第1接触件23被第1连接部26在栅极宽度方向上连接。此外,两个第2接触件24被第2连接部27在栅极宽度方向上连接。由此,布线与各接触件23、24的连接面积增加了各连接部26、27的面积的量,所以能够进一步减少接触断开的不良状况。

作为变形例,也可以如图6所示,第1连接部26与栅极长方向上的各第1接触件23的一端侧连接。当然,第1连接部26也可以与栅极长方向上的各第1接触件23的另一端侧连接。这关于第2接触件24也是同样的。

作为变形例,第1电极部17也可以具有多个第1连接部26。例如如图7所示,两条第1连接部26与栅极长方向上的各第1接触件23的两端连接。或者,如图8所示,两条第1连接部26与栅极长方向上的各第1接触件23的两端以外的位置连接。第1连接部26并不限于两条,也可以是3条以上。这关于第2电极部18也是同样的。

作为变形例,也可以如图9所示,3个第1接触件23中的相邻第1接触件23彼此被第1连接部26在栅极宽度方向上连接。连接方法可以与图6~图8所示的方法相同。当然,对于4个以上的第1接触件23也能够应用。这关于第2接触件24也是同样的。

本发明并不限定于上述的实施方式,在不脱离本发明的主旨的范围内能够如以下这样各种各样地变形。

例如,半导体装置10并不限定于图2及图3所示的元件构造。MOSFET也可以被构成为P型。此外,也可以在源极区域12及漏极区域13形成接触用的N+型区域。在此情况下,各接触件23、24与接触用的区域连接。

在上述各实施方式中,各接触件23、24各为两个,但并不限定于各接触件23、24是相同数量。各接触件23、24也可以是多个的个数并且被设定为不同的个数。

依据实施例记述了本发明,但应理解的是本发明并不限定于该实施例及构造。本发明也包含各种各样的变形例及等价范围内的变形。除此以外,各种各样的组合及形态、进而在它们中仅包含一要素、其以上或其以下的其他组合及形态也落入在本发明的范畴及思想范围中。

- 晶体、结晶性氧化物半导体、包含结晶性氧化物半导体的半导体膜、包含晶体和/或半导体膜的半导体装置以及包含半导体装置的系统

- 半导体光发射装置的制造方法、半导体光发射装置、半导体装置的制造方法、半导体装置、一种装置的制造方法、以及一种装置