半导体集成电路装置

文献发布时间:2023-06-19 12:02:28

技术领域

本公开涉及一种包括标准单元(以下看情况也简称为单元)的半导体集成电路装置,该标准单元包括立体构造晶体管。

背景技术

标准单元方式是在半导体衬底上形成半导体集成电路的一种已知方法。标准单元方式指的是以下方式,即事先将具有特定逻辑功能的基本单元(例如反相器、锁存器、触发器、全加器等)作为标准单元准备好,然后将多个标准单元布置在半导体衬底上,再用布线将这些标准单元连接起来,这样来设计LSI芯片。

LSI的基本构成要素即晶体管通过缩小栅极长度(按比例缩小:scaling)而实现了集成度的提高、工作电压的降低以及工作速度的提高。但是,近年来,出现的问题是过度地按比例缩小会引起截止电流,截止电流又会引起功耗显著增大。为解决该问题,人们已开始积极对立体构造晶体管进行研究,即将晶体管构造从现有的平面型变为立体型。

在非专利文献1、2中,作为新型装置公开了一种立体构造装置及使用该立体构造装置的标准单元,该立体构造装置是将立体构造的P型FET和N型FET沿垂直方向层叠在衬底上而得到的。

非专利文献1:Ryckaert J.et al.,″The Complementary FET(CFET)for CMOSscaling beyond N3″,2018Symposium on VLSI Technology Digest of TechnicalPapers

非专利文献2:A.Mocuta et al.,″Enabling CMOS Scaling Towards 3nm andBeyond″,2018Symposium on VLSI Technology Digest of Technical Papers

发明内容

-发明要解决的技术问题-

在本说明书中,对于将立体构造的P型FET和N型FET沿垂直方向层叠在衬底上而得到的立体构造装置,参照非专利文献1的记载将其称为CFET(Complementary FET:互补场效应晶体管)。此外,将与衬底垂直的方向称为深度方向。

此处,在标准单元中,除了例如“与非门”、“或非门”等具有逻辑功能的单元(以下看情况称为逻辑单元)以外,还包括不具有逻辑功能的单元。不具有逻辑功能的单元例如有“填充单元”。“填充单元”是指以下单元,其不具有逻辑功能,对电路块的逻辑功能不做贡献,且布置在逻辑单元之间。

到目前为止,还没有人对采用了CFET的填充单元的构造、包括采用了CFET的填充单元的半导体集成电路的版图做具体的研究。

本公开提供一种包括采用了CFET的填充单元的半导体集成电路装置的版图。

-用以解决技术问题的技术方案-

第一方面的公开是一种半导体集成电路装置,包括具有逻辑功能的第一标准单元和与所述第一标准单元相邻布置且不具有逻辑功能的第二标准单元。所述第一标准单元包括第一电源布线、第二电源布线、第一晶体管以及第二晶体管,所述第一电源布线沿第一方向延伸,且供给第一电源电压,所述第二电源布线沿所述第一方向延伸,且供给与所述第一电源电压不同的第二电源电压,所述第一晶体管是第一导电型的立体构造晶体管,所述第二晶体管是第二导电型的立体构造晶体管,形成在深度方向上比所述第一晶体管高的位置,且俯视时所述第二晶体管的沟道部布置在与所述第一晶体管的沟道部有重合的位置,所述第二标准单元包括第三电源布线、第四电源布线、第一虚设晶体管以及第二虚设晶体管,所述第三电源布线沿所述第一方向延伸,且供给所述第一电源电压,所述第四电源布线沿所述第一方向延伸,且供给所述第二电源电压,所述第一虚设晶体管是所述第一导电型的立体构造晶体管,所述第一虚设晶体管的沟道部在与所述第一方向垂直的第二方向上布置在与所述第一晶体管的沟道部相同的位置,且在深度方向上与所述第一晶体管布置于相同的层,所述第二虚设晶体管是所述第二导电型的立体构造晶体管,所述第二虚设晶体管的沟道部在所述第二方向上布置在与所述第二晶体管的沟道部相同的位置,且在所述深度方向上与所述第二晶体管布置于相同的层。

根据该方面,第一晶体管和第一虚设晶体管的沟道部在第二方向上布置在相同的位置。第一晶体管和第一虚设晶体管在深度方向上布置于相同的层。第二晶体管和第二虚设晶体管的沟道部在第二方向上布置在相同的位置。第二晶体管和第二虚设晶体管在深度方向上布置于相同的层。也就是说,通过将第一、第二晶体管布置在第二标准单元中,能够抑制晶体管布置的疏密不匀。这样一来,就能够抑制半导体集成电路装置的制造偏差,从而能够提高成品率。

第二方面的公开是一种半导体集成电路装置,包括具有逻辑功能的第一标准单元和与所述第一标准单元相邻布置且不具有逻辑功能的第二标准单元。所述第一标准单元包括第一电源布线、第二电源布线、第一晶体管、第二晶体管、第一、第二局部布线以及第三、第四局部布线,所述第一电源布线沿第一方向延伸,且供给第一电源电压,所述第二电源布线沿所述第一方向延伸,且供给与所述第一电源电压不同的第二电源电压,所述第一晶体管是第一导电型的立体构造晶体管,所述第二晶体管是第二导电型的立体构造晶体管,形成在深度方向上比所述第一晶体管高的位置,且俯视时所述第二晶体管的沟道部布置在与所述第一晶体管的沟道部有重合的位置,所述第一、第二局部布线沿与所述第一方向垂直的第二方向延伸,且分别与所述第一晶体管的源极和漏极相连,所述第三、第四局部布线沿所述第二方向延伸,且分别与所述第二晶体管的源极和漏极相连,所述第二标准单元包括第三电源布线、第四电源布线、第五局部布线以及第六局部布线,所述第三电源布线沿所述第一方向延伸,且供给所述第一电源电压,所述第四电源布线沿所述第一方向延伸,且供给所述第二电源电压,所述第五局部布线在所述深度方向上与所述第一、第二局部布线布置于相同的层,所述第六局部布线在所述深度方向上与所述第三、第四局部布线布置于相同的层,所述第五、第六局部布线中的至少一者在俯视时与所述第三、第四电源布线有重合。

根据该方面,第一标准单元与第二标准单元相邻布置。第一、第二、第五局部布线布置于相同的层。第三、第四、第六局部布线布置于相同的层。也就是说,在半导体集成电路装置的下部,第一、第二、第五局部布线布置得很有规律。在半导体集成电路装置的上部,第三、第四、第六局部布线也布置得很有规律。这样一来,就能够抑制半导体集成电路装置的制造偏差,从而能够提高成品率。

-发明的效果-

根据本公开,就采用了CFET的半导体集成电路装置而言,能够抑制制造和性能上的偏差,能够提高成品率。

附图说明

图1是俯视图,示出采用了第一实施方式所涉及的标准单元的电路块下部的版图构造之例;

图2是俯视图,示出采用了第一实施方式所涉及的标准单元的电路块上部的版图构造之例;

图3是图1和图2的版图构造的俯视横向剖视图;

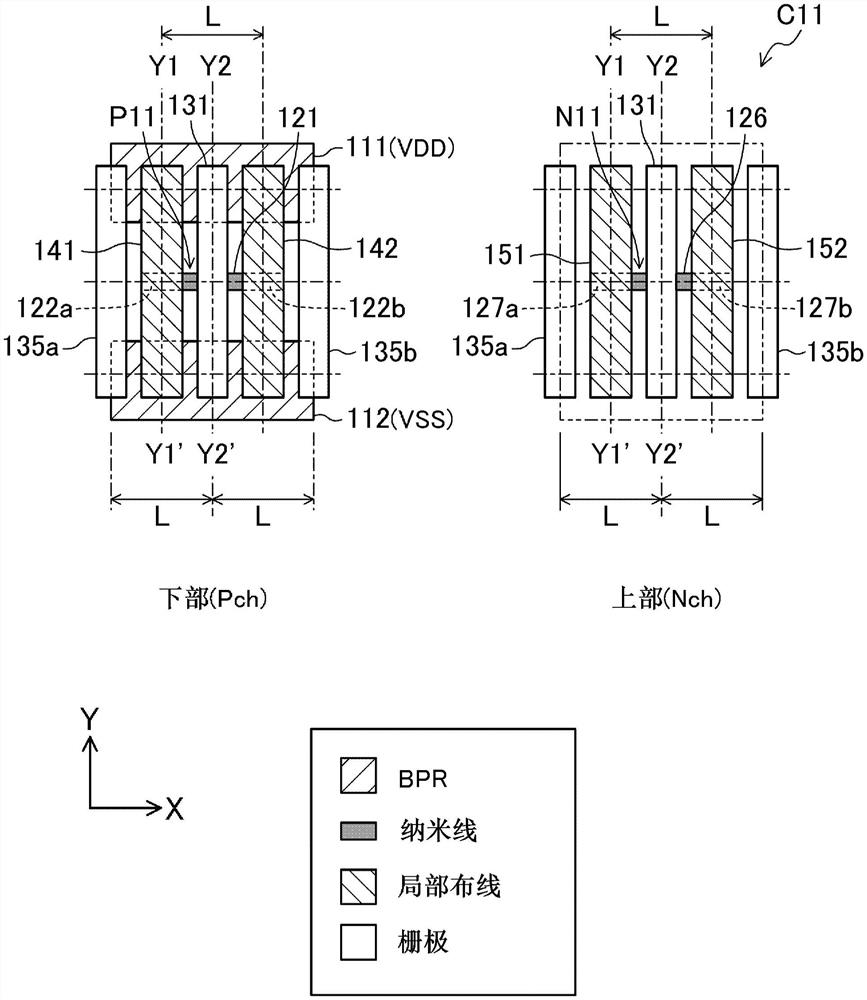

图4(a)、(b)是俯视图,示出第一实施方式所涉及的反相器单元的版图构造;

图5(a)、(b)是俯视图,示出第一实施方式所涉及的填充单元的版图构造;

图6(a)、(b)是图4的版图构造的俯视纵向剖视图;

图7(a)、(b)是俯视图,示出第一实施方式所涉及的填充单元的另一版图构造;

图8(a)、(b)是俯视图,示出第一实施方式所涉及的填充单元的另一版图构造;

图9(a)、(b)是俯视图,示出第一实施方式所涉及的填充单元的另一版图构造;

图10(a)、(b)是俯视图,示出第一实施方式所涉及的填充单元的另一版图构造;

图11(a)、(b)是俯视图,示出第一实施方式所涉及的填充单元的另一版图构造;

图12(a)、(b)是俯视图,示出第二实施方式所涉及的填充单元的版图构造;

图13(a)、(b)是俯视图,示出第二实施方式所涉及的填充单元的另一版图构造;

图14(a)、(b)是俯视图,示出第二实施方式所涉及的填充单元的另一版图构造;

图15(a)、(b)是俯视图,示出第二实施方式所涉及的填充单元的另一版图构造;

图16是剖视图,示出包括CFET的半导体装置的构造;

图17是剖视图,示出包括CFET的半导体装置的构造;

图18是剖视图,示出包括CFET的半导体装置的构造;

图19是剖视图,示出包括CFET的半导体装置的构造。

具体实施方式

下面,参照附图对实施方式进行说明。在以下实施方式中,设半导体集成电路装置包括多个标准单元(在本说明书中,看情况简称为单元),该多个标准单元中的至少一部分标准单元包括CFET,即包括将立体构造的P型FET和N型FET沿垂直方向层叠在衬底上而得到的立体构造装置。

首先,对CFET的基本构造进行说明。图16~图19是示出包括CFET的半导体装置的构造的图,图16是X方向的剖视图,图17是Y方向的栅极部分的剖视图,图18是Y方向的源极/漏极部分的剖视图,图19是俯视图。需要说明的是,X方向是纳米线延伸的方向,Y方向是栅极延伸的方向,Z方向是与衬底面垂直的方向。此外,图16~图19是简图,各部的尺寸和位置等未必一致。

在该半导体装置中,在硅(Si)衬底等半导体衬底301的表面形成有元件隔离区302,由元件隔离区302划分出元件有源区30a。在元件有源区30a,N型FET形成在P型FET上。

在元件有源区30a,堆叠晶体管构造390a形成在半导体衬底301上。堆叠晶体管构造390a包括形成在半导体衬底301上的栅极构造391。栅极构造391包括栅极电极356、多个纳米线358、栅极绝缘膜355以及绝缘膜357。栅极电极356沿Y方向延伸且沿Z方向立起。纳米线358沿X方向贯穿栅极电极356,且沿Y方向和Z方向排列。栅极绝缘膜355形成在栅极电极356与纳米线358之间。栅极电极356和栅极绝缘膜355在X方向上形成在从纳米线358的两端后退后的位置,在该后退的部分上形成有绝缘膜357。在半导体衬底301上且绝缘膜357的两边形成有绝缘膜316。321、322为层间绝缘膜。

如图17所示,栅极电极356通过设在开口部375处的过孔385与上层的布线相连。

例如,栅极电极356能够采用钛、氮化钛或多晶硅等。例如,栅极绝缘膜355能够采用氧化铪、氧化铝或铪铝氧化物等高介电常数材料。例如,纳米线358能够采用硅等。例如,绝缘膜316、绝缘膜357能够采用氧化硅或氮化硅等。

在该半导体装置中,沿Z方向排列的纳米线358的条数为四条,在元件有源区30a,靠半导体衬底301一侧的两条纳米线358的各端部形成有p型半导体层331p。与p型半导体层331p相接的两条局部布线386形成为沿X方向夹住栅极构造391。在远离半导体衬底301一侧的两条纳米线358的各端部形成有n型半导体层341n。与n型半导体层341n相接的两条局部布线388形成为沿X方向夹住栅极构造391。在局部布线386与局部布线388之间形成有绝缘膜332。在局部布线388上形成有绝缘膜389。例如,p型半导体层331p为p型SiGe层,n型半导体层341n为n型Si层。例如,绝缘膜332能够采用氧化硅或氮化硅等。

如图18所示,局部布线388通过过孔3071与埋入式布线3101相连。局部布线386通过过孔3072与埋入式布线3102相连。

像这样,堆叠晶体管构造390a具有P型FET,该P型FET包括栅极电极356、纳米线358、栅极绝缘膜355以及P型半导体层331p。在该P型FET中,一个P型半导体层331p作为源极区发挥作用,另一个P型半导体层331p作为漏极区发挥作用,纳米线358作为沟道发挥作用。堆叠晶体管构造390a还具有N型FET,该N型FET包括栅极电极356、纳米线358、栅极绝缘膜355以及N型半导体层341n。在该N型FET中,一个N型半导体层341n作为源极区发挥作用,另一个N型半导体层341n作为漏极区发挥作用,纳米线358作为沟道发挥作用。

需要说明的是,对于堆叠晶体管构造的上层,利用过孔和金属布线在晶体管间进行布线等,这些可由已知布线工艺实现。

需要说明的是,此处,P型FET和N型FET中的纳米线的条数分别为Y方向上四条、Z方向上两条,合计各八条,但纳米线的条数不限于此。P型FET和N型FET的纳米线的条数也可以不同。

在本说明书中,将形成在纳米线的两端且构成成为晶体管的源极或漏极的端子的半导体层部称为“焊盘”。在上述CFET的基本构造例中,p型半导体层331p和n型半导体层341n相当于焊盘。

在之后的实施方式的俯视图和剖视图中,有时会省略各绝缘膜等的图示。在之后的实施方式的俯视图和剖视图中,有时用简化的直线状形状示出纳米线及其两侧的焊盘。在本说明书中,像“同一尺寸”等意为尺寸等相同的表述包括制造上的偏差范围。

(第一实施方式)

图1是采用了第一实施方式所涉及的标准单元的电路块下部的版图例,图2是采用了第一实施方式所涉及的标准单元的电路块上部的版图例,图3是沿图1和图2的线X1-X1’剖开的剖面。图1和图2是电路块的俯视图。具体而言,图1示出下部,即包括形成在靠近衬底一侧的立体构造晶体管(此处为P型纳米线FET)的部分,图2示出上部,即包括形成在远离衬底一侧的立体构造晶体管(此处为N型纳米线FET)的部分。

需要说明的是,在以下说明中,在图1等俯视图中,将附图横向设为X方向(相当于第一方向),将附图纵向设为Y方向(相当于第二方向),将与衬底面垂直的方向设为Z方向(相当于深度方向)。在图1等俯视图中纵横延伸的虚线示出设计时用于布置部件的网格。网格在X方向上等间距布置,且在Y方向上等间距布置。需要说明的是,网格间距在X方向和Y方向上既可以相同也可以不同。

在图1和图2的版图中,沿X方向排列的多个单元构成单元列CR。并且,多个单元列CR沿Y方向排列着布置。在多个单元中,包括具有反相器的逻辑功能的反相器单元C1、C2和不具有逻辑功能的填充单元C11、C12、C12a。需要说明的是,沿Y方向将反相器单元C1反转过来即构成反相器单元C2。沿Y方向将填充单元C12反转过来即构成填充单元C12a。

此处,“填充单元”是指以下单元,其不具有逻辑功能,对电路块的逻辑功能不做贡献,且布置在逻辑单元之间。

在本实施方式中,在填充单元中布置有虚设焊盘。此处,“虚设焊盘”是指对电路的逻辑功能不做贡献的焊盘,换言之,即以下构造物,其与构成纳米线FET的焊盘具有相同的构造,且对电路块的逻辑功能不做贡献。

需要说明的是,在图1和图2中,示出包括反相器单元C1、C2和填充单元C11、C12、C12a的电路块的版图。不过,实际版图不限于此,可以布置任意的逻辑单元。

(反相器单元的构成)

图4是俯视图,示出反相器单元的版图构造。具体而言,图4(a)、(b)是反相器单元C1的俯视图。具体而言,图4(a)示出下部,图4(b)示出上部。

如图4(a)所示,在反相器单元C1的Y方向两端分别设有沿X方向延伸的电源布线11、12。电源布线11、12均为形成在埋入式布线层中的埋入式电源布线(BPR:Buried PowerRail)。电源布线11供给电源电压VDD,电源布线12供给电源电压VSS。

在M1布线层中形成有沿X方向延伸的布线71、72。布线71相当于输入A,布线72相当于输出Y。

在反相器单元C1的下部形成有沿X方向延伸的纳米线21;在反相器单元C1的上部形成有沿X方向延伸的纳米线26。纳米线21、26在俯视时重合。在纳米线21的两端形成有掺杂了P型半导体的焊盘22a、22b。在纳米线26的两端形成有掺杂了N型半导体的焊盘27a、27b。纳米线21构成P型晶体管P1的沟道部,焊盘22a、22b构成成为P型晶体管P1的源极或漏极的端子。纳米线26构成N型晶体管N1的沟道部,焊盘27a、27b构成成为N型晶体管N1的源极或漏极的端子。N型晶体管N1形成在Z方向上比P型晶体管P1高的位置。

栅极布线31在X方向的大致中央沿Y方向延伸且从反相器单元C1的下部朝向上部沿Z方向延伸。栅极布线31成为P型晶体管P1和N型晶体管N1的栅极。也就是说,由纳米线21、栅极布线31以及焊盘22a、22b构成P型晶体管P1;由纳米线26、栅极布线31以及焊盘27a、27b构成N型晶体管N1。在反相器单元C1的X方向两端分别形成有虚设栅极布线35a、35b。虚设栅极布线35a、35b与栅极布线31一样,沿Y方向和Z方向延伸。栅极布线31和虚设栅极布线35a、栅极布线31和虚设栅极布线35b在X方向上以同一中心间距L布置。

在反相器单元C1的下部形成有沿Y方向延伸的局部布线(Local Interconnect:LI)41、42。局部布线41与焊盘22a相连;局部布线42与焊盘22b相连。在反相器单元C1的上部形成有沿Y方向延伸的局部布线51、52。局部布线51与焊盘27a相连;局部布线52与焊盘27b相连。

局部布线41延伸至俯视时与电源布线11重合的位置,且通过触点(contact)61与电源布线11相连。触点61形成在俯视时电源布线11与局部布线41重合的位置。局部布线51延伸至俯视时与电源布线12重合的位置,且通过触点62与电源布线12相连。触点62形成在俯视时电源布线12与局部布线51重合的位置。局部布线42、52通过触点63相连。触点63形成在俯视时局部布线42与局部布线52重合的位置。

如图4所示,布线71(输入A)通过触点81与栅极布线31相连。布线72(输出Y)通过触点82与局部布线52相连。

如上所述,反相器单元C1具有P型晶体管P1和N型晶体管N1,实现输入A、输出Y的反相器电路。也就是说,反相器单元C1是具有逻辑功能的标准单元。

(填充单元的构成)

图5是示出填充单元的版图构造的图,图5(a)、(b)是俯视图,图6是俯视纵向剖视图。具体而言,图5(a)示出填充单元C11的下部,图5(b)示出上部。图6(a)是沿线Y1-Y1’剖开的剖面,图6(b)是沿线Y2-Y2’剖开的剖面。

如图5(a)所示,在填充单元C11的Y方向两端部分别设有沿X方向延伸的电源布线111、112。电源布线111、112均为形成在埋入式布线层中的埋入式电源布线(BPR)。电源布线111供给与电源布线11相同的电源电压VDD。电源布线112供给与电源布线12相同的电源电压VSS。

在填充单元C11的下部形成有沿X方向延伸的纳米线121;在填充单元C11的上部形成有沿X方向延伸的纳米线126。纳米线121、126俯视时重合。在纳米线121的两端形成有掺杂了P型半导体的虚设焊盘122a、122b。在纳米线126的两端形成有掺杂了N型半导体的虚设焊盘127a、127b。纳米线121构成P型虚设晶体管P11的沟道部。虚设焊盘122a、122b构成成为P型虚设晶体管P11的源极或漏极的端子。纳米线126构成N型虚设晶体管N11的沟道部。虚设焊盘127a、127b构成成为N型虚设晶体管N11的源极或漏极的端子N型虚设晶体管N11在Z方向上形成在比P型虚设晶体管P11高的位置。

还形成有虚设栅极布线131,虚设栅极布线131在X方向的大致中央沿Y方向延伸,且从填充单元C11的下部朝朝向上部沿Z方向延伸。在填充单元C11的X方向两端形成有虚设栅极布线135a、135b。虚设栅极布线135a、135b沿Y方向延伸,且从单元上部朝向单元下部沿Z方向延伸。虚设栅极布线131、135a、135b在X方向上以同一中心间距L布置。

虚设栅极布线131成为P型虚设晶体管P11和N型虚设晶体管N11的栅极。也就是说,由纳米线121、虚设栅极布线131以及虚设焊盘122a、122b构成P型虚设晶体管P11;由纳米线126、虚设栅极布线131以及虚设焊盘127a、127b构成N型虚设晶体管N11。

在填充单元C11的下部形成有沿Y方向延伸的局部布线141、142。局部布线141、142分别在俯视时与电源布线111、112有重合。局部布线141与虚设焊盘122a相连;局部布线142与虚设焊盘122b相连。

在填充单元C11的上部形成有沿Y方向延伸的局部布线151、152。局部布线151、152分别在俯视时与电源布线111、112有重合。局部布线151与虚设焊盘127a相连;局部布线152与虚设焊盘127b相连。

虚设栅极布线131和局部布线141、142、151、152与反相器单元C1不同,均未与其他布线相连。

如上所述,填充单元C11具有P型虚设晶体管P11和N型虚设晶体管N11。成为P型虚设晶体管P11和N型虚设晶体管N11各自的源极和漏极的虚设焊盘122a、122b、127a、127b分别与局部布线141、142、151、152相连。不过,局部布线141、142、151、152不与其他布线相连。也就是说,填充单元C11是不具有逻辑功能的标准单元。

如图3所示,反相器单元C1和填充单元C11沿X方向排列着布置。需要说明的是,布置在反相器单元C1与填充单元C11的交界处的虚设栅极布线相当于反相器单元C1的虚设栅极布线35b和填充单元C11的虚设栅极布线135a。

填充单元C11的纳米线121、126分别在Y方向上布置在与反相器单元C1的纳米线21、26相同的位置。纳米线121、126分别在Z方向上与纳米线21、26布置于相同的层。也就是说,填充单元C11的P型虚设晶体管P11和N型虚设晶体管N11分别与反相器单元C1的P型晶体管P1和N型晶体管N1在X方向上排列着布置,且在Z方向上布置于相同的层。

栅极布线31、虚设栅极布线131以及虚设栅极布线35a、35b(135a)、135b在X方向上以同一中心间距L布置。也就是说,栅极布线31、虚设栅极布线131以及虚设栅极布线35a、35b(135a)、135b在X方向上以等宽、等间距、等中心间距(中心间距L)布置。

局部布线141、142与局部布线41、42在Z方向上布置于相同的层,且在X方向上以同一中心间距L布置。也就是说,局部布线41、42、141、142在X方向上以等宽、等间距、等中心间距(中心间距L)布置。

局部布线151、152与局部布线51、52在Z方向上布置于相同的层,且在X方向上以同一中心间距L布置。也就是说,局部布线51、52、151、152在X方向上以等宽、等间距、等中心间距(中心间距L)布置。

根据以上构成,不具有逻辑功能的填充单元C11与具有逻辑功能的反相器单元C1相邻布置。反相器单元C1包括P型晶体管P1和N型晶体管N1,N型晶体管N1在Z方向上布置在比P型晶体管P1高的位置。填充单元C11包括P型虚设晶体管P11和N型虚设晶体管N11。填充单元C11的纳米线121、126分别在Y方向上布置在与反相器单元C1的纳米线21、26相同的位置。P型晶体管P1和P型虚设晶体管P11在Z方向上布置于相同的层。N型晶体管N1和N型虚设晶体管N11在Z方向上布置于相同的层。也就是说,通过将P型、N型虚设晶体管布置在填充单元C11中,能够抑制晶体管布置的疏密不匀。这样一来,就能够抑制采用了CFET的半导体集成电路装置的制造偏差,从而能够提高成品率。

在X方向上,最接近反相器单元C1的P型晶体管P1和N型晶体管N1的晶体管分别是填充单元C11的P型虚设晶体管P11和N型虚设晶体管N11。因此,由于P型虚设晶体管P11和N型虚设晶体管N11的存在,P型晶体管P1和N型晶体管N1各自到相邻晶体管的距离会被确定为一个规定值。也就是说,由于P型虚设晶体管P11和N型虚设晶体管N11的存在,能够对最接近逻辑单元(反相器单元C1)的单元端的晶体管(P型晶体管P1和N型晶体管N1)各自到相邻晶体管的距离估算出一个规定值。这样一来,能够提高对逻辑单元中的晶体管性能的估算精度。

反相器单元C1的栅极布线31、填充单元C11的虚设栅极布线131以及虚设栅极布线35a、35b(135a)、135b在X方向上以同一中心间距L布置。也就是说,栅极布线31、虚设栅极布线131以及虚设栅极布线35a、35b(135a)、135b布置得很有规律。这样一来,就能够抑制采用了CFET的半导体集成电路装置的制造偏差,从而能够提高成品率。

填充单元C11的局部布线141、142与反相器单元C1的局部布线41、42在Z方向上布置于相同的层,且在X方向上以同一中心间距L布置。填充单元C11的局部布线151、152与反相器单元C1的局部布线51、52在Z方向上布置于相同的层,且在X方向上以同一中心间距L布置。也就是说,局部布线41、42、141、142布置得很有规律。局部布线51、52、151、152也布置得很有规律。这样一来,就能够抑制采用了CFET的半导体集成电路装置的制造偏差,从而能够提高成品率。

(填充单元的变形例)

(其一)

图7是俯视图,示出本实施方式所涉及的填充单元的另一例。图7(a)示出单元下部,图7(b)示出单元上部。如图1和图7所示,填充单元C12与填充单元C11单元宽度(X方向的尺寸)不同。也就是说,填充单元C11的单元宽度为2L,而填充单元C12的单元宽度为4L。

具体而言,在填充单元C12的下部形成有沿X方向延伸的纳米线123a、123b、123c;在填充单元C12的上部形成有沿X方向延伸的纳米线128a、128b、128c。俯视时,纳米线123a、123b、123c分别与纳米线128a、128b、128c重合。

在纳米线123a的附图左侧形成有掺杂了P型半导体的虚设焊盘124a;在纳米线123a、123b之间形成有掺杂了P型半导体的虚设焊盘124b。在纳米线123b、123c之间形成有掺杂了P型半导体的虚设焊盘124c;在纳米线123c的附图右侧形成有掺杂了P型半导体的虚设焊盘124d。

在纳米线128a的附图左侧形成有掺杂了N型半导体的虚设焊盘129a;在纳米线128a、128b之间形成有掺杂了N型半导体的虚设焊盘129b。在纳米线128b、128c之间形成有掺杂7N型半导体的虚设焊盘129c;在纳米线128c的附图右侧形成有掺杂了N型半导体的虚设焊盘129d。

纳米线123a构成P型虚设晶体管P12的沟道部,虚设焊盘124a、124b构成成为P型虚设晶体管P12的源极或漏极的端子。纳米线123b构成P型虚设晶体管P13的沟道部,虚设焊盘124b、124c构成成为P型虚设晶体管P13的源极或漏极的端子。纳米线123c构成P型虚设晶体管P14的沟道部,虚设焊盘124c、124d构成成为P型虚设晶体管P14的源极或漏极的端子。

纳米线128a构成N型虚设晶体管N12的沟道部,虚设焊盘129a、129b构成成为N型虚设晶体管N12的源极或漏极的端子。纳米线128b构成N型虚设晶体管N13的沟道部,虚设焊盘129b、129c构成成为N型虚设晶体管N13的源极或漏极的端子。纳米线128c构成N型虚设晶体管N14的沟道部,虚设焊盘129c、129d构成成为N型虚设晶体管N14的源极或漏极的端子。

在填充单元C12的X方向两端,形成有沿Y方向延伸且从单元的下部朝向上部沿Z方向延伸的虚设栅极布线135a、135b。在虚设栅极布线135a、135b之间,以中心间距L形成有沿Y方向延伸且从单元的下部朝向上部沿Z方向延伸的虚设栅极布线132a、132b、132c。

虚设栅极布线132a成为P型虚设晶体管P12和N型虚设晶体管N12的栅极。虚设栅极布线132b成为P型虚设晶体管P13和N型虚设晶体管N13的栅极。虚设栅极布线132c成为P型虚设晶体管P14和N型虚设晶体管N14的栅极。也就是说,由纳米线123a、虚设栅极布线132a以及虚设焊盘124a、124b构成P型虚设晶体管P12。由纳米线123b、虚设栅极布线132b以及虚设焊盘124b、124c构成P型虚设晶体管P13。由纳米线123c、虚设栅极布线132c以及虚设焊盘124c、124d构成P型虚设晶体管P14。由纳米线128a、虚设栅极布线132a以及虚设焊盘129a、129b构成N型虚设晶体管N12。由纳米线128b、虚设栅极布线132b以及虚设焊盘129b、129c构成N型虚设晶体管N13。由纳米线128c、虚设栅极布线132c以及虚设焊盘129c、129d构成N型虚设晶体管N14。

在填充单元C12的下部形成有沿Y方向延伸的局部布线143~146。局部布线143~146在俯视时分别与电源布线111、112有重合。局部布线143~146分别与虚设焊盘124a~124d相连。局部布线143~146在X方向以同一中心间距L布置,且在Z方向上布置于相同的层。

在填充单元C12的上部形成有沿Y方向延伸的局部布线153~156。局部布线153~156在俯视时分别与电源布线111、112有重合。局部布线153~156分别与虚设焊盘129a~129d相连。局部布线153~156在X方向以同一中心间距L布置,且在Z方向上布置于相同的层。

虚设栅极布线132a~132c和局部布线143~146、153~156均未与其他布线等相连。

如上所述,填充单元C12具有P型虚设晶体管P12~P14和N型虚设晶体管N12~N14。成为P型虚设晶体管P12~P14和N型虚设晶体管N12~N14各自的源极和漏极的虚设焊盘124a~124d、129a~129d分别与局部布线143~146和局部布线153~156相连。不过,局部布线143146和局部布线153~156未与其他布线等相连。也就是说,填充单元C12是不具有逻辑功能的标准单元。

此处,如图1和图2的电路块所示,设填充单元C12与反相器单元C1相邻布置。在此情况下,填充单元C12的纳米线123a、123b、123c与反相器单元C1的纳米线21在Y方向上布置在相同的位置,且在Z方向上布置于相同的层。填充单元C12的纳米线128a、128b、128c与反相器单元C1的纳米线26在Y方向上布置在相同的位置,且在Z方向上布置于相同的层也就是说,填充单元C12的P型虚设晶体管P12、P13、P14与反相器单元C1的P型晶体管P1在X方向上排列着布置,且在Z方向上布置于相同的层。填充单元C12的N型晶体管N12、N13、N14与反相器单元C1的N型晶体管N1在X方向上排列着布置,且在Z方向上布置于相同的层。

栅极布线31、虚设栅极布线132a、132b、132c以及虚设栅极布线35a、35b(135a)、135b在X方向上以同一中心间距L布置。也就是说,栅极布线31、虚设栅极布线132a、132b、132c以及虚设栅极布线35a、35b(135a)、135b在X方向上以等宽、等间距、等中心间距布置。

局部布线143~146与反相器单元C1的局部布线41、42在X方向上以同一中心间距L布置,且在Z方向上布置于相同的层。也就是说,局部布线41、42、143~146在X方向上以等宽、等间距、等中心间距(中心间距L)布置。

局部布线153~156与反相器单元C1的局部布线51、52在X方向上以同一中心间距L布置,且在Z方向上布置于相同的层。也就是说,局部布线51、52、153~156在X方向上以等宽、等间距、等中心间距(中心间距L)布置。

根据本变形例所涉及的填充单元C12,能够收到与填充单元C11相同的效果。需要说明的是,单元宽度为2L、4L以外的填充单元也能够同样构成。

(其二)

图8是俯视图,示出第一实施方式所涉及的填充单元的版图构造的另一例。图8(a)示出单元下部,图8(b)示出单元上部。如图8所示,填充单元C13的构成基本上与图5所示的填充单元C11相同,但各局部布线的Y方向的长度不同。也就是说,局部布线147、148沿Y方向延伸至俯视时与电源布线111重合的位置,但与电源布线112没有重合。局部布线157、158沿Y方向延伸至俯视时与电源布线112重合的位置,但与电源布线111没有重合。

根据本变形例所涉及的填充单元C13,能够收到与填充单元C11相同的效果。

需要说明的是,局部布线147、148分别在俯视时与电源布线111有重合,局部布线157、158分别在俯视时与电源布线112有重合,但不限于此。局部布线147、148也可以分别在俯视时与电源布线111没有重合,且与电源布线112有重合。局部布线157、158也可以分别在俯视时与电源布线111有重合,且与电源布线112没有重合。局部布线147、148、157、158也可以分别在俯视时与电源布线111、112均没有重合。不过,局部布线147、148、157、158中的至少一者在俯视时要与电源布线111或电源布线112有重合。

(其三)

图9是俯视图,示出第一实施方式所涉及的填充单元的版图构造的另一例。图9(a)示出单元下部,图9(b)示出单元上部。如图9所示,在填充单元C14中,虚设焊盘122a、122b、127a、127b均不与局部布线相连。其他构成与填充单元C11相同。

在将填充单元C14布置成与反相器单元C1相邻的情况下,纳米线121、126分别在Y方向上布置在与反相器单元C1的纳米线21、26相同的位置。填充单元C14的P型虚设晶体管P11与反相器单元C1的P型晶体管P1在Z方向上布置于相同的层。填充单元C14的N型虚设晶体管N11与反相器单元C1的N型晶体管N1在Z方向上布置于相同的层。也就是说,通过将P型、N型虚设晶体管布置在填充单元C14中,能够抑制晶体管布置的疏密不匀。这样一来,就能够抑制采用了CFET的半导体集成电路装置的制造偏差,从而能够提高成品率。

反相器单元C1的栅极布线31、填充单元C14的虚设栅极布线131以及虚设栅极布线35a、35b(135a)、135b在X方向上以同一中心间距L布置。也就是说,栅极布线31、虚设栅极布线131以及虚设栅极布线35a、35b(135a)、135b布置得很有规律。这样一来,就能够抑制采用了CFET的半导体集成电路装置的制造偏差,从而能够提高成品率。

在X方向上,最接近反相器单元C1的P型晶体管P1和N型晶体管N1的晶体管分别是填充单元C14的P型虚设晶体管P11和N型虚设晶体管N11。因此,由于P型虚设晶体管P11和N型虚设晶体管N11的存在,P型晶体管P1和N型晶体管N1各自到相邻晶体管的距离就会确定为规定值。也就是说,由于P型虚设晶体管P11和N型虚设晶体管N11的存在,而能够将最接近逻辑单元(反相器单元C1)的单元端的晶体管(P型晶体管P1和N型晶体管N1)各自到相邻晶体管的距离估算为一个规定值。这样一来,能够提高逻辑单元中的晶体管性能的估算精度。

需要说明的是,在填充单元C14中,虚设焊盘122a、122b、127a、127b均不与局部布线相连,但不限于此。虚设焊盘122a、122b、127a、127b中的一部分可以与沿Y方向延伸的局部布线相连。与虚设焊盘122a、122b、127a、127b相连的局部布线在俯视时可以与电源布线111、112有重合,也可以没有重合。

(其四)

图10是俯视图,示出第一实施方式所涉及的填充单元的版图构造的另一例。图10(a)示出单元下部,图10(b)示出单元上部。如图9所示,填充单元C15的构成基本上与图4所示的填充单元C11相同,但局部布线与电源布线通过触点相连。

在填充单元C15中形成有沿Z方向延伸的触点161~164。触点161~164分别布置在俯视时与电源布线111重合的位置。电源布线111和局部布线141通过触点161彼此相连。电源布线111和局部布线142通过触点162彼此相连。局部布线141、151通过触点163彼此相连。局部布线142、152通过触点164彼此相连。

根据本变形例所涉及的填充单元C15,能够收到与填充单元C11相同的效果。

虚设焊盘122a、122b、127a、127b分别通过局部布线141、142、151、152和触点161~164接收从电源布线111供给的电源电压VDD。也就是说,P型虚设晶体管P11的源极和漏极、N型虚设晶体管N11的源极和漏极均固定在同一电位VDD上。这样一来,能够减少P型、N型虚设晶体管的浮动节点,实现电路块工作的稳定化。

需要说明的是,电源布线111或电源布线112与虚设栅极布线131也可以通过触点相连,并将虚设栅极布线131的电位固定下来。

局部布线141、142、151、152通过触点161~164与电源布线111相连,但不限于此。局部布线141、142、151、152也可以通过触点与电源布线112相连。

局部布线141、142、151、152也可以分别在俯视时与电源布线112没有重合。

(其五)

图11是俯视图,示出第一实施方式所涉及的填充单元的版图构造的另一例。图11(a)示出单元下部,图11(b)示出单元上部。如图11所示,填充单元C16的构成基本上与图5所示的填充单元C11相同,但单元下部的局部布线的Y方向的长度不同,局部布线与电源布线通过触点相连。

在单元下部形成有沿Y方向延伸的局部布线149、150。局部布线149与虚设焊盘122a相连。局部布线150与虚设焊盘122b相连。局部布线149、150均在俯视时与电源布线111有重合,但与电源布线112没有重合。

在填充单元C16中形成有沿Z方向延伸的触点165~168。触点165、166在俯视时与电源布线111有重合。触点167、168在俯视时与电源布线112有重合。电源布线111和局部布线149通过触点165彼此相连。电源布线111和局部布线150通过触点166彼此相连。电源布线112和局部布线151通过触点167彼此相连。电源布线112和局部布线152通过触点168彼此相连。

根据本变形例所涉及的填充单元C16,能够收到与填充单元C11相同的效果。

虚设焊盘122a、122b分别通过局部布线149、150和触点165、166接收从电源布线111供给的电源电压VDD。虚设焊盘127a、127b分别通过局部布线151、152和触点167、168接收从电源布线112供给的电源电压VSS。也就是说,P型虚设晶体管P11的源极和漏极均以电位VDD固定下来。N型虚设晶体管N11的源极和漏极均以电位VSS固定下来。这样一来,能够减少P型、N型虚设晶体管的浮动节点,实现电路块工作的稳定化。

布置在填充单元C16的下部的局部布线149、150通过触点165、166接收从电源布线111供给的电源电压VDD。布置在填充单元C16的上部的局部布线151、152通过触点167、168接收从电源布线112供给的电源电压VSS。也就是说,在俯视时重合的局部布线149与局部布线151之间、在俯视时重合的局部布线150与局部布线152之间会产生布线电容。由该布线电容而产生电源间电容,因此能够实现向电路块供给的电源电位的稳定化。

局部布线149、150通过触点165、166与电源布线111相连,局部布线151、152通过触点167、168与电源布线112相连,但不限于此。也可以是局部布线149、150与电源布线112相连,局部布线151、152与电源布线111相连。在此情况下,局部布线149、150在俯视时与电源布线111没有重合,且与电源布线112有重合。

局部布线151、152也可以分别在俯视时与电源布线111没有重合。

<第二实施方式>

图12是示出第二实施方式所涉及的填充单元的版图构造的图,图12(a)示出单元下部,图12(b)示出单元上部。填充单元C21不具有P型、N型虚设晶体管。

如图12(a)所示,在填充单元C21的Y方向两端部分别设有沿X方向延伸的电源布线211、212。电源布线211、212均为形成在埋入式布线层中的埋入式电源布线(BPR)。电源布线211供给与电源布线11相同的电源电压VDD。电源布线212供给与电源布线12相同的电源电压VSS。

在填充单元C21中形成有虚设栅极布线231,虚设栅极布线231在X方向的大致中央沿Y方向延伸且从单元的上部朝向下部沿Z方向延伸。在填充单元C21的X方向两端形成有沿Y方向延伸且从单元的上部朝向下部沿Z方向延伸的虚设栅极布线235a、235b。虚设栅极布线231、235a、235b在X方向上以同一中心间距L布置。

在单元下部形成有沿Y方向延伸的局部布线241、242。局部布线241、242分别在俯视时与电源布线211、212有重合。局部布线241布置在俯视时虚设栅极布线231、235a之间。局部布线242布置在俯视时虚设栅极布线231、235b之间。

在单元上部形成有沿Y方向延伸的局部布线251、252。局部布线251、252分别在俯视时与电源布线211、212有重合。局部布线251在俯视时布置在虚设栅极布线231、235a之间。局部布线252在俯视时布置在虚设栅极布线231、235b之间。

虚设栅极布线231和局部布线241、242、251、252均未与其他布线相连。

在填充单元C21中未设置纳米线和虚设焊盘,也未形成P型虚设晶体管和N型虚设晶体管。也就是说,填充单元C21是不具有逻辑功能的标准单元。

此处,填充单元C21与反相器单元C1相邻布置。需要说明的是,布置在反相器单元C1与填充单元C21的交界处的虚设栅极布线相当于反相器单元C1的虚设栅极布线35b和填充单元C21的虚设栅极布线235a。

在此情况下,反相器单元C1的栅极布线31、填充单元C21的虚设栅极布线231以及虚设栅极布线35a、35b(235a)、235b在X方向上以同一中心间距L布置。也就是说,栅极布线31、虚设栅极布线231以及虚设栅极布线35a、35b(235a)、235b在X方向上以等宽、等间距、等中心间距布置。

局部布线241、242与反相器单元C1的局部布线41、42在Z方向上布置于相同的层,且在X方向上以同一中心间距L布置。也就是说,局部布线41、42、241、242在X方向上以等宽、等间距、等中心间距(中心间距L)布置。

局部布线251、252与反相器单元C1的局部布线51、52在Z方向上布置于相同的层,且在X方向上以中心间距L布置。也就是说,局部布线51、52、251、252在X方向上以等宽、等间距、等中心间距(中心间距L)布置。

根据以上构成,不具有逻辑功能的填充单元C21与具有逻辑功能的反相器单元C1相邻布置。填充单元C21的局部布线241、242与反相器单元C1的局部布线41、42在Z方向上布置于相同的层。填充单元C21的局部布线251、252与反相器单元C1的局部布线51、52在Z方向上布置于相同的层。也就是说,局部布线41、42、241、242布置得很有规律。局部布线51、52、251、252也布置得很有规律。这样一来,就能够抑制采用了CFET的半导体集成电路装置的制造偏差,从而能够提高成品率。

局部布线41、42、241、242在X方向上以同一中心间距L布置。局部布线51、52、251、252也在X方向上以同一中心间距L布置。也就是说,局部布线41、42、241、242布置得很有规律。局部布线51、52、251、252也布置得很有规律。这样一来,就能够抑制采用了CFET的半导体集成电路装置的制造偏差,从而能够提高成品率。

填充单元C21的虚设栅极布线231、反相器单元C1的栅极布线31以及虚设栅极布线35a、35b(235a)、235b在X方向上以同一中心间距L布置。也就是说,栅极布线31、虚设栅极布线231以及虚设栅极布线35a、35b(235a)、235b布置得很有规律。这样一来,就能够抑制采用了CFET的半导体集成电路装置的制造偏差,从而能够提高成品率。

需要说明的是,局部布线241、242、251、252分别在俯视时与电源布线211、212有重合,但不限于此。局部布线241、242、251、252也可以分别与电源布线211、212中的一者没有重合。

(填充单元的变形例)

(其一)

图13是示出第二实施方式所涉及的填充单元的另一版图构造的图,图13(a)示出单元下部,图13(b)示出单元上部。填充单元C22与填充单元C21的X方向的单元宽度不同。也就是说,填充单元C21的单元宽度为2L,而填充单元C22的单元宽度为L。

在单元下部且X方向的大致中央部形成有沿Y方向延伸的局部布线243。在单元上部且X方向的大致中央部形成有沿Y方向延伸的局部布线253。局部布线243、253分别在俯视时与电源布线211、212有重合。

在填充单元C22与反相器单元C1相邻布置的情况下,局部布线243与反相器单元C1的局部布线41、42在Z方向上布置于相同的层,且在X方向上以同一中心间距L布置。局部布线253与反相器单元C1的局部布线51、52在Z方向上布置于相同的层,且在X方向上以同一中心间距L布置。

根据本变形例所涉及的填充单元C22,局部布线243与反相器单元C1的局部布线41、42在Z方向上布置于相同的层。局部布线253与反相器单元C1的局部布线51、52在Z方向上布置于相同的层。也就是说,局部布线41、42、243布置得很有规律。局部布线51、52、253也布置得很有规律。这样一来,就能够抑制采用了CFET的半导体集成电路装置的制造偏差,从而能够提高成品率。

局部布线41、42、243在X方向上以同一中心间距L布置。局部布线51、52、253也在X方向上以同一中心间距L布置。也就是说,局部布线41、42、243布置得很有规律。局部布线51、52、253也布置得很有规律。这样一来,就能够抑制采用了CFET的半导体集成电路装置的制造偏差,从而能够提高成品率。

因为填充单元C22的单元宽度为L,所以能够将填充单元布置到逻辑单元的间距为L时那样极小间隙中。

(其二)

图14是示出第二实施方式所涉及的填充单元的另一版图构造的图,图14(a)示出单元下部,图14(b)示出单元上部。填充单元C23的构成基本上与图12所示的填充单元C21相同,但局部布线与电源布线通过触点相连。

在填充单元C23中形成有沿Z方向延伸的触点261~264。触点261264分别布置在俯视时与电源布线211重合的位置。电源布线211和局部布线241通过触点261彼此相连。电源布线211和局部布线242通过触点262彼此相连。局部布线241、251通过触点263彼此相连。局部布线242、252通过触点264彼此相连。

根据本变形例所涉及的填充单元C23,能够收到与填充单元C21相同的效果。

局部布线241、242、251、252分别通过触点261~264接收从电源布线211供给的同一电源电压VDD。也就是说,局部布线241、242、251、252均固定在同一电位VDD上。这样一来,能够减少浮动节点,实现电路块工作的稳定化。

需要说明的是,电源布线211或电源布线212与虚设栅极布线231也可以通过触点相连,并将虚设栅极布线231的电位固定下来。

局部布线241、242、251、252通过触点261~264与电源布线211相连,但不限于此。局部布线241、242、251、252也可以通过触点与电源布线212相连。

填充单元C23是单元宽度为2L的标准单元,但不限于此,填充单元C23的单元宽度也可以为L。在此情况下,不需要虚设栅极布线231、局部布线242、252以及触点262、264。

(其三)

图15是示出第二实施方式所涉及的填充单元的另一版图构造的图,图15(a)示出单元下部,图15(b)示出单元上部。填充单元C24的构成基本上与图12所示的填充单元C21相同,但局部布线与电源布线通过触点相连,且单元下部的局部布线的Y方向的长度不同。

在单元下部,局部布线244、245分别在俯视时与电源布线211有重合,但与电源布线212没有重合。

在填充单元C24中形成有沿Z方向延伸的触点265~268。触点265、266布置在俯视时与电源布线211重合的位置,触点267、268布置在俯视时与电源布线212重合的位置。电源布线211和局部布线244通过触点265彼此相连。电源布线211和局部布线245通过触点266彼此相连。电源布线212和局部布线251通过触点267彼此相连。电源布线212和局部布线252通过触点268彼此相连。

根据本变形例所涉及的填充单元C22,能够收到与填充单元C21相同的效果。

局部布线244、245通过触点265、266接收从电源布线211供给的电源电压VDD。局部布线251、252通过触点267、268接收从电源布线212供给的电源电压VSS。也就是说,局部布线244、245均固定在电位VDD上,局部布线251、252也均固定在电位VSS上。这样一来,能够减少浮动节点,实现电路块工作的稳定化。

在俯视时重合的局部布线244与局部布线251之间、在俯视时重合的局部布线245与局部布线252之间会产生布线电容。由该布线电容而产生电源间电容,因此能够实现向电路块供给的电源电位的稳定化。

局部布线244、245通过触点265、266与电源布线211相连,局部布线251、252通过触点267、268与电源布线212相连,但不限于此。也可以是局部布线244、245与电源布线212相连,局部布线251、252与电源布线211相连。在此情况下,局部布线244、245在俯视时与电源布线211没有重合,且与电源布线212有重合。

填充单元C24是单元宽度为2L的标准单元,但不限于此,填充单元C24的单元宽度也可以为L。在此情况下,不需要虚设栅极布线231、局部布线245、252以及触点266、268。

需要说明的是,在上述各实施方式和变形例中,在单元上部和下部,晶体管分别包括一条纳米线,但晶体管的一部分或全部晶体管都可以包括多条纳米线。在此情况下,可以俯视时沿Y方向设置多条纳米线,也可以沿Z方向设置多条纳米线。还可以沿Y方向和Z方向这两个方向分别设置多条纳米线。此外,在单元的上部和下部晶体管所包括的纳米线的条数可以不同。

在上述各实施方式中,举出纳米线FET作为立体构造晶体管之例进行了说明,但不限于此。例如,形成在各填充单元的下部的晶体管也可以是鳍式晶体管。

在图6中,示出的纳米线121、126的俯视纵向剖面形状为正方形,但不限于此。纳米线121、126的俯视纵向剖面形状也可以为正方形以外的形状(例如长方形)。

在反相器单元C1、C2和填充单元C11~C16中,在单元下部形成有P型晶体管,在单元上部形成有N型晶体管,但不限于此,也可以在单元上部形成P型晶体管,在单元下部形成N型晶体管。

电源布线11、12、111、112、211、212为埋入式布线,但不限于此。例如,电源布线11、12、111、112、211、212也可以布置在M1布线层中。

-产业实用性-

本公开能够应用于包括采用了CFET的标准单元的半导体集成电路,因此例如有助于提高半导体芯片的性能。

-符号说明-

11、12、111、112、211、212 电源布线

31 栅极布线

35a、35b、131、132a~132c、135a、135b、231、235a、235b 虚设栅极布线

41、42、51、52、141~158、241~245、251~253 局部布线

P1 P型晶体管

N1 N型晶体管

P11~P14 P型虚设晶体管

N11~N14 N型虚设晶体管

C1、C2 反相器单元

C11~C16、C21~C24 填充单元

- 半导体集成电路装置、半导体集成电路装置的安装结构及半导体集成电路装置的制造方法

- 半导体集成电路、包括半导体集成电路的系统设备及半导体集成电路控制方法