基于忆阻器的2T1R阵列及其并行操作方法和算法

文献发布时间:2023-06-19 12:07:15

技术领域

本发明属于神经网络技术领域,具体涉及一种基于忆阻器的2T1R阵列及其并行操作方法和算法。

背景技术

忆阻器是一种可以通过施加外部激励,调节其电导状态的非易失型器件。涉及大量乘积累加运算的运算过程,一般可以在忆阻器阵列上并行地进行。作为涉及大量乘积累加运算的代表,人工神经网络算法在忆阻器阵列上的并行实现,体现了忆阻器阵列并行运算的优势。

在使用1T1R阵列实现卷积神经网络算法时,由于图片会被分割成多个尺寸与卷积核大小相同的子图,然后使用卷积核对每个子图进行卷积计算。虽然多个卷积核可以并行处理每个子图,但是仍需将子图串行输入到忆阻器阵列上。在某些忆阻器参与进行卷积计算的过程中,忆阻器阵列上的其他忆阻器因没有可用的输入输出通道而被迫处于待机状态。

在对1T1R阵列中的忆阻器的电导值进行调整时,由于每个忆阻器的电导值的调整需求不同,在进行置位操作或复位操作时,最多只能同时对位于同一列的忆阻器进行操作,其他列的忆阻器只能等待串行地置位操作或复位操作。

发明内容

针对现有技术的以上缺陷或改进需求,本发明提出一种基于2T1R单元的忆阻器阵列,其目的在于在器件阵列数量有限的情况下,大幅提升计算和调整的并行程度以及阵列中器件的利用率。

在阐述本发明内容之前,定义本文中所使用的术语如下:

术语“2T1R阵列”是指:两个晶体管与一个忆阻器或阻变单元串联的结构。

术语“1T1R阵列”是指:一个晶体管与一个忆阻器或阻变单元串联的结构。

为实现上述目的,本发明的第一方面提供了一种基于忆阻器的2T1R 阵列,所述2T1R阵列包括相互连接的2T1R忆阻器单元电路,所述2T1R 忆阻器单元电路由第一个晶体管、第二个晶体管和一个忆阻器构成,所述 2T1R阵列为十字交叉结构,且所述2T1R忆阻器单元电路位于阵列的十字交叉点上。

根据本发明第一方面的基于忆阻器的2T1R阵列,其中,所述第一个晶体管与所述第二个晶体管相同或不同;

优选地,所述第一个晶体管和/或所述第二个晶体管为开关器件,优选自一下一种或多种:薄膜晶体管、场效应晶体管、双极型晶体管;

更优选地,所述场效应晶体管为MOS场效应晶体管。

根据本发明第一方面的基于忆阻器的2T1R阵列,其中,位于阵列中同一列的所述第一个晶体管的源极并联到阵列的底部电极,位于阵列中同一列的第一个晶体管的栅极并联到同一个电极上,忆阻器的负极与第一个晶体管的漏极串联,忆阻器的正极与第二个晶体管的漏极串联,每个忆阻器的正极连接一个电极,位于阵列中同一行的第二个晶体管通过源极和漏极串联在一起,位于阵列中同一列的第二个晶体管的栅极并联到同一个电极上。

优选地,所述2T1R阵列中,位于同一行的忆阻器的顶部电极通过忆阻器单元电路内的第二个晶体管串联起来,且位于同一行的每个顶部电极均可连接不同的外部电极。

根据本发明第一方面的基于忆阻器的2T1R阵列,其中,第一个晶体管的源极与第二个晶体管的漏极串联,位于阵列中同一列的第二个晶体管通过源极和漏极串联在一起,每个第一个晶体管的源极连接一个电极,忆阻器的负极与第一个晶体管的漏极串联,位于阵列中同一行的忆阻器的正极串联在同一个电极上,位于阵列中同一行的第二个晶体管的栅极并联到同一个电极上,位于阵列中同一列的第一个晶体管的栅极并联到同一个电极上。

优选地,所述2T1R阵列中,同一列的忆阻器单元电路的第一个晶体管的源极是通过单元电路内第二个晶体管串联起来的,且每个第一个晶体管的源极均可连接不同的外部电极。

本发明的第二方面提供了一种并行操作方法,所述并行操作方法使用第一方面所述的基于忆阻器的2T1R阵列进行并行操作;

优选地,所述并行操作方法包括:控制第二个晶体管的导通与关闭,在功能上将忆阻器阵列划分成多个子阵列,每个子阵列同时进行置位操作或复位操作,实现并行加速状态调整;

更优选地,所述并行操作方法包括:通过控制阵列中所述第二个晶体管阵列的导通与关闭,在功能上将忆阻器阵列划分成多个子阵列,每个忆阻器单元电路同时接收不同的电压激励,从而同时进行置位操作或复位操作,实现并行状态调整。

根据本发明第二方面的并行操作方法,其中,所述并行操作方法包括:控制阵列中所述第二个晶体管全部导通,使得所述2T1R忆阻器阵列中位于同一行的忆阻器单元电路的顶部电极通过同一个外部电极接收电压激励;

控制阵列中所述第二个晶体管全部关闭,使得所述2T1R忆阻器阵列中位于同一行的忆阻器单元电路的顶部电极分别连接到不同的外部电极,接收到不同的电压激励,并且不会对相邻列的忆阻器单元电路产生影响;和/ 或

分别控制阵列中位于不同列的所述第二个晶体管的导通和关闭,使得所述2T1R忆阻器阵列在功能上以列为单位划分成不同的子阵列,子阵列内部的所述第二个晶体管导通,相邻两个子阵列之间的所述第二个晶体管关闭,每个子阵列内部位于同一行的忆阻器单元电路的顶部电极通过同一个外部电极接收电压激励,不同子阵列分别连接到不同的外部电极,接收到不同的电压激励,并且不会对相邻的子阵列产生影响。

根据本发明第二方面的并行操作方法,其中,所述并行操作方法包括:

控制阵列中所述第二个晶体管全部导通,使得所述2T1R忆阻器阵列中位于同一列的忆阻器单元电路的底部电极并联到同一个外部电极以输出电流信号;

控制阵列中所述第二个晶体管全部关闭,使得所述2T1R忆阻器阵列中位于同一列的忆阻器单元电路的底部电极分别连接道不同的外部点击,输出各自的电流信号,并且不会和相邻行的忆阻器单元电路输出的电流信号累加;和/或

分别控制阵列中位于不同行的所述第二个晶体管的导通和关闭,使得所述2T1R忆阻器阵列在功能上以行为单位划分成不同的子阵列,子阵列内部的所述第二个晶体管阵列导通,相邻两个子阵列之间的所述第二个晶体管阵列关闭,每个子阵列内部位于同一列的忆阻器单元电路的底部电极并联到同一个外部电极以输出电流信号,不同子阵列分别连接道不同的外部电极,输出不同的电流信号,并且不会对相邻的子阵列产生影响。

本发明的第三方面提供了一种卷积神经网络算法,所述卷积神经网络算法使用第一方面所述的基于忆阻器的2T1R阵列或第二方面所述的并行操作方法进行卷积计算。

具体地,本发明提供了两种基于2T1R单元的忆阻器阵列,本发明还提供了使用2T1R阵列进行并行加速的操作方法。

所述第一种2T1R忆阻器阵列包括:相互连接的第一种2T1R忆阻器单元电路,所述第一种2T1R单元电路包含第一个晶体管、第二个晶体管和一个忆阻器,第一种2T1R忆阻器阵列为十字交叉结构,所述第一种2T1R单元电路位于阵列的十字交叉点上,位于阵列中同一列的所述第一个晶体管的源极并联到阵列的底部电极,位于阵列中同一列的第一个晶体管的栅极并联到同一个电极上,忆阻器的负极与第一个晶体管的漏极串联,忆阻器的正极与第二个晶体管的漏极串联,每个忆阻器的正极连接一个电极,位于阵列中同一行的第二个晶体管通过源极和漏极串联在一起,位于阵列中同一列的第二个晶体管的栅极并联到同一个电极上;

所述第二种2T1R忆阻器阵列,包括:相互连接的第二种2T1R单元电路;所述第二种2T1R单元电路包含第一个晶体管、第二个晶体管和一个忆阻器,所述第二种2T1R忆阻器阵列为十字交叉结构,第二种2T1R单元电路位于阵列的十字交叉点上,第一个晶体管的源极与第二个晶体管的漏极串联,位于阵列中同一列的第二个晶体管通过源极和漏极串联在一起,每个第一个晶体管的源极连接一个电极,忆阻器的负极与第一个晶体管的漏极串联,位于阵列中同一行的忆阻器的正极串联在同一个电极上,位于阵列中同一行的第二个晶体管的栅极并联到同一个电极上,位于阵列中同一列的第一个晶体管的栅极并联到同一个电极上;

所述并行操作方法包括:

使用所述第一种2T1R忆阻器阵列,通过控制阵列中位于同一列的第二个晶体管的导通与关闭,在功能上将忆阻器阵列按列划分成多个子阵列,每个子阵列可以同时施加不同的电压激励,实现并行加速运算;

使用所述第二种2T1R忆阻器阵列,通过控制阵列中位于同一行的第二个晶体管的导通与关闭,在功能上将忆阻器按行划分成多个子阵列,每个子阵列可以同时输出不同的电流信号,实现并行加速运算;

使用所述任意一种2T1R忆阻器阵列,通过控制第二个晶体管的导通与关闭,在功能上将忆阻器阵列划分成多个子阵列,每个子阵列可以同时进行置位操作或复位操作,实现并行加速状态调整。

例如,本发明提供的所述第一种2T1R忆阻器阵列,其中,2T1R忆阻器阵列与现有技术中的1T1R忆阻器阵列的区别在于,本发明中位于同一行的忆阻器的顶部电极是通过单元电路内的第二个晶体管串联起来的,且每个忆阻器的顶部电极均可连接不同的外部电极,而现有技术中的1T1R忆阻器阵列中位于同一行的忆阻器单元电路的顶部电极是直接并联起来的,且 1T1R阵列中位于同一行的忆阻器的顶部电极只能连接到同一个外部电极。

例如,本发明提供的所述第二种2T1R忆阻器阵列,其中,2T1R忆阻器阵列与现有技术中的1T1R忆阻器阵列的区别在于,本发明中位于同一列的忆阻器单元电路的第一个晶体管的源极是通过单元电路内第二个晶体管串联起来的,且每个第一个晶体管的源极均可连接不同的外部电极,而现有技术中的1T1R忆阻器阵列中位于同一列的忆阻器单元电路的底部电极是直接并联起来的,且位于同一列的每个底部电极只能连接到同一个外部电极。

例如,本发明提供的所述并行操作方法,使用所述第一种2T1R忆阻器阵列,可以控制所述阵列中的第二个晶体管全部导通,使得所述2T1R忆阻器阵列中位于同一行的忆阻器的顶部电极通过同一个外部电极接收电压激励;也可以控制所述阵列中的第二个晶体管全部关闭,使得所述2T1R忆阻器阵列中位于同一行的忆阻器的顶部电极分别连接到不同的外部电极,从而接收到不同的电压激励,并且不会对相邻列的忆阻器单元电路产生影响;也可以按需求分别控制位于不同列的所述第二个晶体管的导通和关闭,使得所述2T1R忆阻器阵列在功能上以列为单位划分成不同的子阵列,子阵列内部的所述第二个晶体管导通,相邻两个子阵列之间的所述第二个晶体管关闭,每个子阵列内部位于同一行的忆阻器单元电路的顶部电极通过同一个外部电极接收电压激励,不同子阵列分别连接到不同的外部电极,从而接收到不同的电压激励,并且不会对相邻的子阵列产生影响。

例如,本发明提供的所述并行操作方法,使用所述第二种2T1R忆阻器阵列,可以控制所述阵列中的第二个晶体管全部导通,使得所述2T1R忆阻器阵列中位于同一列的忆阻器的底部电极并联到同一个外部电极以输出电流信号;也可以控制所述神裂中的第二个晶体管全部关闭,使得所述2T1R 忆阻器阵列中位于同一列的忆阻器单元电路的底部电极分别连接到不同的外部电极,从而输出各自的电流信号,并且不会和相邻行的忆阻器单元电路输出的电流信号累加;也可以按需求分别控制位于不同行的所述阵列中的第二个晶体管的导通和关闭,使得所述2T1R忆阻器阵列在功能上以行为单位划分成不同的子阵列,子阵列内部的所述第二个晶体管导通,相邻两个子阵列之间的所述第二个晶体管关闭,每个子阵列内部位于同一列的忆阻器单元电路的底部电极并联到同一个外部电极以输出电流信号,不同子阵列分别连接道不同的外部电极,从而输出不同的电流信号,并且不会对相邻的子阵列产生影响。

例如,本发明提供的所述并行操作方法,使用所述任意一种2T1R忆阻器阵列实现并行状态调整。使用所述任意一种2T1R忆阻器阵列,通过控制阵列中所述第二个晶体管的导通与关闭,在功能上将忆阻器阵列划分成多个子阵列,每个忆阻器单元电路可以同时接收不同的电压激励,从而可以同时进行置位操作或复位操作,实现并行状态调整。

本发明的基于忆阻器的2T1R阵列可以具有但不限于以下有益效果:

1T1R忆阻器阵列需要串行完成的计算任务,2T1R忆阻器阵列可以在不增加阵列数量,只增加阵列规模的情况下并行完成。1T1R忆阻器阵列需要逐行或逐列完成的置位操作或复位操作,2T1R忆阻器阵列可以并行地同时对所有忆阻器进行置位或复位操作。提升了存内计算读取和写入的并行程度,提升了阵列器件的利用率。

附图说明

以下,结合附图来详细说明本发明的实施方案,其中:

图1示出了实施例1的2T1R忆阻器阵列的单元电路的示意图;

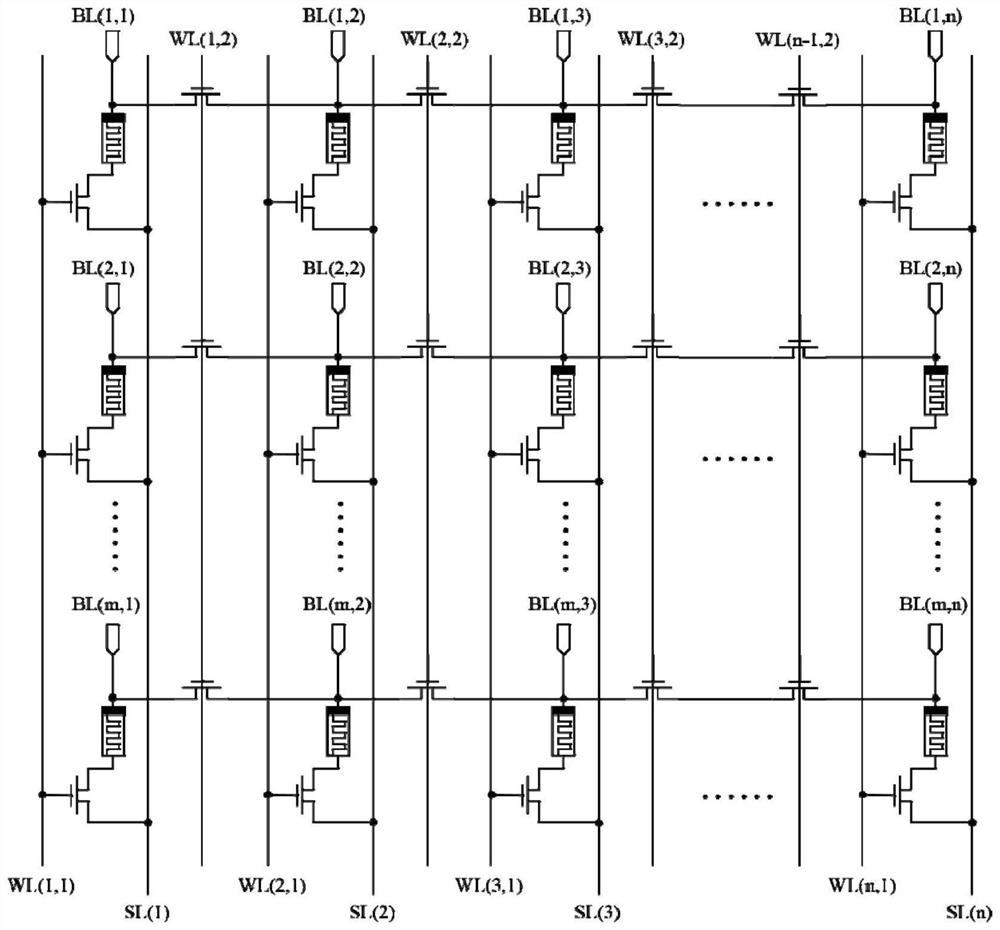

图2示出了试验例1的2T1R忆阻器阵列的示意图;

图3示出了实施例2的2T1R忆阻器阵列的单元电路的示意图;

图4示出了试验例2的2T1R忆阻器阵列的示意图;

图5示出了试验例3中全连接神经网络的单层计算的示意图和基于本发明2T1R忆阻器阵列实现全连接计算的示意图;其中,图5A示出了试验例3中一种全连接神经网络的单层的一部分全连接计算的示意图;图5B示出了试验例3中基于实施例1中的2T1R忆阻器阵列实现全连接计算的示意图。

图6示出了试验例4和试验例5中卷积神经网络的卷积层的卷积计算的示意图和试验例4中基于本发明的2T1R忆阻器阵列实现卷积计算的示意图;其中,图6A示出了试验例4和试验例5中一种卷积神经网络的卷积层的卷积计算的示意图;图6B示出了试验例4中基于实施例1的2T1R忆阻器阵列实现卷积计算的示意图。

图7示出了试验例5中基于实施例2的2T1R忆阻器阵列实现卷积计算的示意图。

图8示出了试验例6中一种基于实施例1的2T1R忆阻器阵列实现并行置位操作的示意图。

具体实施方式

下面通过具体的实施例进一步说明本发明,但是,应当理解为,这些实施例仅仅是用于更详细具体地说明之用,而不应理解为用于以任何形式限制本发明。

本部分对本发明试验中所使用到的材料以及试验方法进行一般性的描述。虽然为实现本发明目的所使用的许多材料和操作方法是本领域公知的,但是本发明仍然在此作尽可能详细描述。本领域技术人员清楚,在上下文中,如果未特别说明,本发明所用材料和操作方法是本领域公知的。

本实施例用于说明本发明的一种2T1R忆阻器阵列的结构。

图1为本实施例2T1R忆阻器阵列的2T1R单元电路的示意图。如图1所示,该2T1R单元电路包括第一个晶体管M1、第二个晶体管M2、一个忆阻器R1。

需要说明的是,本发明的试验例中采用的晶体管均可以为薄膜晶体管或场效应晶体管(例如MOS场效应晶体管)或其它特性相同的开关器件。这里采用的两个晶体管可以是相同的,也可以是不同的。这里采用的晶体管的源极、漏极在结构上可以是对称的,所以其源极、漏极在结构上可以是没有区别的。在本发明的试验例中,为了区分两个晶体管的电极,直接描述第一个晶体管M1的其中一极为M11极,另一极为M12极,描述第二个晶体管M2的其中一极为M21极,另一极为M22极。

本发明的试验例对采用的晶体管M1的类型不做限定,例如当晶体管M1 采用N型晶体管时,其栅极和字线端WL1连接,例如字线端WL1输入高电平时晶体管M1导通;晶体管M1的M11极可以是源极并被配置为和源线端 SL连接,例如晶体管M1可以通过源线端SL接收复位电压;晶体管M1的 M12极可以是漏极并被配置为和忆阻器R1的第二极(例如负极)连接,忆阻器R1的第一极(例如正极)和位线端BL1、BL2连接,例如忆阻器可以通过位线端BL1接收置位电压,也可以通过位线端BL2接收置位电压。例如当晶体管M1采用P型晶体管时,其栅极和字线端WL1连接,例如字线端 WL1输入低电平时晶体管M1导通;晶体管M1的第一极可以是漏极并被配置为和源线SL1连接,例如晶体管M1可以通过源线端SL1接收复位电压;晶体管M1的第二极可以是源极并被配置为和忆阻器R1的第二极(例如负极) 连接,忆阻器R1的第一极(例如正极)和位线端BL连接,例如忆阻器R1 可以通过位线端BL1接收置位电压。

本发明的试验例对采用的晶体管M2的类型不做限定,例如当晶体管M2 采用N型晶体管时,其栅极和字线端WL2连接,例如字线端WL2输入高电平时晶体管M2导通;晶体管M2的M21极可以是漏极并被配置为和忆阻器 R1的第一极(例如正极)连接,例如位线端BL1或BL2输入高电平时,晶体管M2的M21极将接收到高电平;晶体管M2的M22极可以是源极并被配置为和源线端SL2连接,例如当晶体管M2导通时,晶体管M2将向源线端 SL2输出电平值。例如当晶体管M2采用P型晶体管时,其栅极和字线端WL2 连接,例如字线端WL2输入低电平时晶体管M2导通;晶体管M2的M21 极可以是漏极并被配置为和忆阻器R1的第一极(例如正极)连接,例如位线端BL1或BL2输入高电平时,晶体管M2的M21极将接收到高电平;晶体管M2的M22极可以是源极并被配置为和源线端SL2连接,例如当晶体管 M2导通时,晶体管M2将向源线端SL2输出电流信号。

下面各试验例中使用的本实施例2T1R忆阻器阵列均以晶体管M1采用N 型晶体管且晶体管M2采用N型晶体管为例进行说明。

字线端WL1的作用是对晶体管M1的栅极施加相应电压,从而控制晶体管M1导通或关闭。在对忆阻器R1进行操作时,例如进行置位操作或复位操作,均需要先开启晶体管M1,即需要通过字线端WL1对晶体管M1的栅极施加导通电压。在晶体管M1导通后,例如,可以通过在源线端SL1和位线端BL1或BL2向忆阻器R1施加电压,以改变忆阻器R1的阻态。例如,可以通过位线端BL1或BL2施加置位电压,以使得该忆阻器R1处于低阻态;又例如可以通过源线端SL1施加复位电压,以是的该忆阻器R1处于高阻态。

字线端WL2的作用是对晶体管M2的栅极施加相应电压,从而控制晶体管M2导通或关闭。例如当晶体管M2导通时,源线端SL2的电平与字线端 BL1或BL2相关;又例如当晶体管M2关闭时,源线端SL2的电平与字线端 BL1或BL2无关。

需要说明的是,在本发明的试验例中,通过字线端WL1和位线端BL1 或BL2同时施加电压,使得忆阻器R1的电阻值越来越小,即忆阻器R1从高阻态变为低阻态,将使得忆阻器R1从高阻态变为低阻态的操作成为置位操作;通过字线端WL1和源线端SL1同时施加电压,使得忆阻器R1的电阻值越来越大,即忆阻器R1从低阻态变为高阻态,将使得忆阻器R1从低阻态变为高阻态的操作成为复位操作。例如,忆阻器R1具有阈值电压,在输入电压幅度小于忆阻器R1的阈值电压是,不会改变忆阻器R1的电阻值(或电导值)。在这种情况下,可以通过输入小于阈值电压的电压,利用忆阻器R1的电阻值 (或电导值)进行计算;也可以通过输入大于阈值电压的电压,改变忆阻器 R1的电阻值(或电导值)。

图2示出第一种2T1R忆阻器阵列,该忆阻器阵列由多个如图1中所示的2T1R忆阻器单元电路构成,例如多个忆阻器单元电路构成一个m行n列的阵列,m为大于1的整数,n为大于1的整数。图2中BL(1,1)、 BL(1,2)……BL(m,n)分别表示第一行第一列、第一行第二列……第m行第n 列的位线,每个忆阻器单元电路中的BL1端与对应位置的位线相连,每个忆阻器单元电路中的SL2端与同一行相邻忆阻器的BL2端相连;图2中 WL(1,1)、WL(2,1)……WL(n,1)分别表示第一列、第二列……第n列的主字线,每一列忆阻器单元电路中的晶体管M1的栅极并联到该列对应的主字线;图2 中的WL(1,2)、WL(2,2)……WL(n,2)分别表示第一列、第二列……第n列的辅字线,每一列忆阻器单元电路中的晶体管M2的栅极并联到该列对应的辅字线;图2中的SL(1)、SL(2)……SL(n)分别表示第一列、第二列……第n列的主源线,每一列的忆阻器单元电路中的晶体管M1的源极SL1和该列对应的主源线连接。

本实施例用于说明本发明的一种2T1R忆阻器阵列的结构。

图3为本实施例2T1R忆阻器阵列的2T1R单元电路的示意图。如图1所示,该2T1R单元电路包括第一个晶体管M1、第二个晶体管M2、一个忆阻器R1。

需要说明的是,本发明的试验例中采用的晶体管均可以为薄膜晶体管或场效应晶体管(例如MOS场效应晶体管)或其它特性相同的开关器件。这里采用的两个晶体管可以是相同的,也可以是不同的。这里采用的晶体管的源极、漏极在结构上可以是对称的,所以其源极、漏极在结构上可以是没有区别的。在本发明的试验例中,为了区分两个晶体管的电极,直接描述第一个晶体管M1的其中一极为M11极,另一极为M12极,描述第二个晶体管M2的其中一极为M21极,另一极为M22极。

本发明的试验例对采用的晶体管M1的类型不做限定,例如当晶体管M1 采用N型晶体管时,其栅极和字线端WL1连接,例如字线端WL1输入高电平时晶体管M1导通;晶体管M1的M11极可以是源极并被配置为和源线端 S1连接,并且和晶体管M2的M22极连接,例如晶体管M1可以向晶体管 M2输出电流信号,或者从源线端S1接收复位电压;晶体管M1的M12极可以是漏极并被配置为和忆阻器R1的第二极(例如负极)连接,忆阻器R1的第一极(例如正极)和位线端BL1连接,例如忆阻器可以通过位线端BL1接收置位电压。例如当晶体管M1采用P型晶体管时,其栅极和字线端WL1连接,例如字线端WL1输入低电平时晶体管M1导通;晶体管M1的M11极可以是漏极并被配置为和源线端S1连接,并且和晶体管M2的M22极连接,例如晶体管M1可以向晶体管M2输出电流信号,或者从源线端S1接收复位电压;晶体管M1的M12极可以是源极并被配置为和忆阻器R1的第二极(例如负极)连接,忆阻器R1的第一极(例如正极)和位线端BL1连接,例如忆阻器R1可以通过位线端BL1接收置位电压。

本发明的试验例对采用的晶体管M2的类型不做限定,例如当晶体管M2 采用N型晶体管时,其栅极和字线端WL2连接,例如字线端WL2输入高电平时晶体管M2导通;晶体管M2的M22极可以是漏极并被配置为和位线端 BL2连接,并且和晶体管M1的M11极连接,例如字线端BL2输入一个电流信号时,电流将通过晶体管M2的M22极流入到晶体管M2中;晶体管M2 的M21极可以是源极并被配置为和源线端SL2连接,例如当晶体管M2导通时,晶体管M2将向源线端SL2输出电流信号。例如当晶体管M2采用P型晶体管时,其栅极和字线端WL2连接,例如字线端WL2输入低电平时晶体管M2导通;晶体管M2的M22极可以是漏极并被配置为和位线端BL2连接,并且和晶体管M1的M11极连接,例如字线端BL2输入一个电流信号时,电流将通过晶体管M2的M22极流入到晶体管M2中;晶体管M2的M21极可以是源极并被配置为和源线端SL2连接,例如当晶体管M2导通时,晶体管 M2将向源线端SL2输出电流信号。

下面各试验例中使用的本实施例的2T1R忆阻器阵列均以晶体管M1采用 N型晶体管且晶体管M2采用N型晶体管为例进行说明。

字线端WL1的作用是对晶体管M1的栅极施加相应电压,从而控制晶体管M1导通或关闭。在对忆阻器R1进行操作时,例如进行置位操作或复位操作,均需要先开启晶体管M1,即需要通过字线端WL1对晶体管M1的栅极施加导通电压。在晶体管M1导通后,例如,可以通过在源线端SL1或SL2 和位线端BL1向忆阻器R1施加电压,以改变忆阻器R1的阻态。例如,可以通过位线端BL1施加置位电压,以使得该忆阻器R1处于低阻态;又例如可以通过源线端SL1或SL2施加复位电压,以是的该忆阻器R1处于高阻态。

字线端WL2的作用是对晶体管M2的栅极施加相应电压,从而控制晶体管M2导通或关闭。例如当晶体管M2导通时,源线端SL2的电平与源线端 SL1或位线端BL1相关;又例如当晶体管M2关闭时,源线端SL2的电平与源线端SL1或字线端BL1无关。

需要说明的是,在本发明的试验例中,通过字线端WL1和位线端BL1 同时施加电压,使得忆阻器R1的电阻值越来越小,即忆阻器R1从高阻态变为低阻态,将使得忆阻器R1从高阻态变为低阻态的操作成为置位操作;通过字线端WL1和源线端SL1或SL2同时施加电压,使得忆阻器R1的电阻值越来越大,即忆阻器R1从低阻态变为高阻态,将使得忆阻器R1从低阻态变为高阻态的操作成为复位操作。例如,忆阻器R1具有阈值电压,在输入电压幅度小于忆阻器R1的阈值电压是,不会改变忆阻器R1的电阻值(或电导值)。在这种情况下,可以通过输入小于阈值电压的电压,利用忆阻器R1的电阻值(或电导值)进行计算;也可以通过输入大于阈值电压的电压,改变忆阻器 R1的电阻值(或电导值)。

图4示出本实施例的2T1R忆阻器阵列,该忆阻器阵列由多个如图3中所示的2T1R忆阻器单元电路构成,例如多个忆阻器单元电路构成一个m行 n列的阵列,m为大于1的整数,n为大于1的整数。图2中BL1、BL2……BLm 分别表示第一行、第一行……第m行的位线,位于同一行的忆阻器单元电路的BL1端并联到对应行的位线上;图4中WL(1,1)、WL(2,1)……WL(n,1)分别表示第一列、第二列……第n列的主字线,每一列忆阻器单元电路中的晶体管M1的栅极并联到该列对应的主字线;图4中的WL(1,2)、 WL(2,2)……WL(m-1,2)分别表示第一行、第二行……第m-1行的辅字线,每一行忆阻器单元电路中的晶体管M2的栅极并联到该行对应的辅字线;图4 中的SL(1,1)、SL(1,2)……SL(m,n)分别表示第一行第一列、第一行第二列……第m行第n列的源线,每个忆阻器单元电路中的SL1端与对应位置的源线相连,每个忆阻器单元电路中的SL2端与同一列相邻忆阻器的BL2端相连。

忆阻器阵列擅长并行地运行乘积累加运算,通常使用1T1R忆阻器阵列实现各种包含乘积累加运算的算法。全连接神经网络的单层计算和卷积神经网络中的卷积计算包含大量乘积累加计算,因此,本发明以矩阵乘法计算、全连接计算、卷积计算和置位操作为例,展示2T1R忆阻器阵列如何提升并行程度,加速运算过程。

2T1R忆阻器阵列可以实现1T1R忆阻器阵列的功能,本试验例使用m行 n列的实施例1的2T1R忆阻器阵列实现一个m行n列的矩阵与一个m行1 列的矢量之间乘法计算。

一个m行n列大小的矩阵可以表示为图2所示的m行n列的2T1R忆阻器阵列。例如,矩阵第1列中的m个值对应的表示为图2所示的忆阻器阵列的第1列的m个忆阻器的电导值,矩阵第2列中的m个值对应的表示为图2 所示的忆阻器阵列的第2列的m个忆阻器的电导值,以此类推,矩阵第n列的m个值对应的表示为图2所示的忆阻器阵列的第n列的m个忆阻器的电导值。

m行1列的矢量可以表示为一组电压激励。例如,将电压激励施加在2T1R 忆阻器阵列的位线BL(1,1)、BL(2,1)……BL(m,1)上。

一个m行n列的矩阵和一个m行1列的矢量之间的乘法计算的结果是一个m行1列的矢量,计算结果可以表示为一组电流输出。例如,在2T1R忆阻器阵列的源线SL(1)、SL(2)……SL(n)上采集到的电流输出。

2T1R忆阻器阵列的操作方法是施加电压激励,采集电流输出。例如,对 2T1R忆阻器阵列的所有主字线和辅字线施加高电平以导通全部晶体管,对 2T1R忆阻器阵列的位线BL(1,1)、BL(2,1)……BL(m,1)并行输入电压激励,在 2T1R忆阻器阵列的源线SL(1)、SL(2)……SL(n)上采集到代表计算结果的输出电流。根据基尔霍夫定律可知,2T1R忆阻器阵列可以并行地完成乘积累加运算。

在上述操作方法中,主字线导通晶体管的目的是允许对应列的忆阻器参与计算,辅字线导通晶体管的目的是连接晶体管两侧的位线。当辅字线对应的晶体管全部导通时,m行n列的实施例1的2T1R忆阻器阵列在操作方法和功能上与m行n列的1T1R忆阻器阵列相似。在本试验例中,实施例1的 2T1R忆阻器阵列可以相同程度的并行地完成1T1R忆阻器阵列的计算任务。

2T1R忆阻器阵列可以实现1T1R忆阻器阵列的功能,本试验例使用m行 n列的实施例2的2T1R忆阻器阵列实现一个m行n列的矩阵与一个m行1 列的矢量之间乘法计算。

一个m行n列大小的矩阵可以表示为图4所示的m行n列的2T1R忆阻器阵列。例如,矩阵第1列中的m个值对应的表示为图4所示的忆阻器阵列的第1列的m个忆阻器的电导值,矩阵第2列中的m个值对应的表示为图4 所示的忆阻器阵列的第2列的m个忆阻器的电导值,以此类推,矩阵第n列的m个值对应的表示为图4所示的忆阻器阵列的第n列的m个忆阻器的电导值。

m行1列的矢量可以表示为一组电压激励。例如,将电压激励施加在2T1R 忆阻器阵列的位线BL1、BL2……BLm上。

一个m行n列的矩阵和一个m行1列的矢量之间的乘法计算的结果是一个m行1列的矢量,计算结果可以表示为一组电流输出。例如,在2T1R忆阻器阵列的源线SL(m,1)、SL(m,2)……SL(m,n)上采集到的电流输出。

2T1R忆阻器阵列的操作方法是施加电压激励,采集电流输出。例如,对 2T1R忆阻器阵列的所有主字线和辅字线施加高电平以导通全部晶体管,对2T1R忆阻器阵列的位线BL1、BL2……BLm并行输入电压激励,在2T1R忆阻器阵列的源线SL(m,1)、SL(m,2)……SL(m,n)上采集到代表计算结果的输出电流。根据基尔霍夫定律可知,2T1R忆阻器阵列可以并行地完成乘积累加运算。

在上述操作方法中,主字线导通晶体管的目的是允许对应列的忆阻器参与计算,辅字线导通晶体管的目的是连接晶体管两侧的位线。当辅字线对应的晶体管全部导通时,m行n列的实施例2的2T1R忆阻器阵列在操作方法和功能上与m行n列的1T1R忆阻器阵列相似。在本试验例中,实施例2的 2T1R忆阻器阵列可以相同程度的并行地完成1T1R忆阻器阵列的计算任务。

全连接神经网络的单层计算中包含大量乘积累加运算,本试验例使用一个m行n列的实施例1的2T1R忆阻器阵列实现具有m×n个输入神经元节点和1个输出神经元节点的全连接计算。

图5A为一种全连接神经网络的单层计算的示意图,图5B为基于实施例 1的2T1R忆阻器阵列实现图5A中的全连接计算的示意图。

如图5A所示,全连接神经网络的单层具有m×n个输入神经元节点,具有1个输出神经元节点。图5A所示的全连接计算等价于一个1行m×n列的矩阵与一个m×n行1列的矢量之间的矢量乘法。

如图5B所示,一个1行m×n列大小的矩阵可以表示为m行n列的实施例1的2T1R忆阻器阵列。例如,矩阵第1行第1列到第1行第m列的m个值可以表示为图5B所示的忆阻器阵列的第1列的m个忆阻器的电导值,矩阵第1行第m+1列到第1行第2m+1列的m个值可以表示为图5B所示的忆阻器阵列的第2列的m个忆阻器的电导值,以此类推,矩阵第1行第m(n-1)+1 列到第1行第m×n列的m个值可以表示为图5B所示的忆阻器阵列的第n列的m个忆阻器的电导值。

m×n行1列的矢量可以表示为n组电压激励。例如,将第1组m个电压激励施加在2T1R忆阻器阵列的第1列的位线BL(1,1)、BL(2,1)……BL(m,1) 上,将第2组m个电压激励施加在2T1R忆阻器阵列的第2列的位线BL(1,2)、 BL(2,2)……BL(m,2)上,以此类推,将第n组m个电压激励施加在2T1R忆阻器阵列的第n列的位线BL(1,n)、BL(2,n)……BL(m,n)上。

一个1行m×n列的矩阵和一个m×n行1列的矢量之间的乘法计算的结果是一个1行1列的矢量,计算结果可以表示为一组电流输出的和。例如,在 2T1R忆阻器阵列的源线SL(1)、SL(2)……SL(n)上采集到的电流输出的和。

2T1R忆阻器阵列的操作方法是施加电压激励,采集电流输出。例如,对 2T1R忆阻器阵列的所有主字线施加高电平以导通全部M1晶体管,2T1R忆阻器阵列的所有辅字线施加低电平以关闭全部M2晶体管,对2T1R忆阻器阵列的位线BL(1,1)、BL(2,1)……BL(m,1)……BL(1,n)、BL(2,n)……BL(m,n)并行输入电压激励,在2T1R忆阻器阵列的源线SL(1)、SL(2)……SL(n)上采集到输出电流并求和得到计算结果。根据基尔霍夫定律可知,2T1R忆阻器阵列可以并行地完成图5A所示的全连接计算。

在上述操作方法中,主字线导通M1晶体管的目的是允许对应列的忆阻器参与计算,辅字线关闭M2晶体管的目的是断开M2晶体管两侧的位线。当辅字线对应的M2晶体管全部关闭时,m行n列的2T1R忆阻器阵列在操作方法和功能上与n个m行1列的1T1R忆阻器阵列相似。若使用m行n列的 1T1R忆阻器阵列完成图5A所示的全连接计算任务,由于其只有m个位线可以施加电压激励,所以需要分别施加n次不同的电压激励才能完成全部计算任务。在本试验例中,实施例1的2T1R忆阻器阵列提升了并行程度,实施例1的2T1R忆阻器阵列完成图5A所示的全连接计算任务所需时间是1T1R 忆阻器阵列完成相同计算任务所需时间的1/n。

卷积神经网络中包含大量的卷积计算,其本质也属于乘积累加运算,本试验例使用一个9行2n列的实施例1的2T1R忆阻器阵列实现卷积计算,例如该卷积计算使用1个卷积核组,该卷积核组包含2个3×3大小的卷积核。

图6A为一种卷积神经网络的卷积计算的示意图,图6B为基于实施例1 的2T1R忆阻器阵列实现图6A中的卷积计算的示意图。

如图6A所示,本试验例中的卷积神经网络使用1个卷积核组对待处理图片进行卷积运算。本试验例中的卷积核组包含1个卷积核,卷积核尺寸为 3×3。本试验例中的卷积计算可以等效为图片像素值与卷积核之间的乘积累加运算。

如图6B所示,采用一个9行2n列的实施例1的2T1R忆阻器阵列表示卷积核中的值。例如,2T1R忆阻器阵列中的第1列的9个忆阻器的电导值用来表示卷积核1中9个权重w11,w12,……,w19,2T1R阵列中的第2列的9个忆阻器的电导值用来表示卷积核2中9个权重w21,w22,……,w29; 2T1R忆阻器阵列中的第3列、第5列、……、第2n-1列的忆阻器的电导值与第1列的忆阻器的电导值对应相同,2T1R忆阻器阵列中的第4列、第6 列、……、第2n列的忆阻器的电导值与第2列的忆阻器的电导值对应相同。

卷积层对待处理图像进行卷积处理,需要将待处理图像划分为多个子图,每个子图的尺寸与卷积核的尺寸大小相同。子图的像素值可以表示为一组电压激励。例如,将第1个子图的9个像素值对应的9个电压激励施加在2T1R 忆阻器阵列第1列的位线BL(1,1)、BL(2,1)……BL(9,1)上,将第2个子图的9 个像素值对应的9个电压激励施加在2T1R忆阻器阵列第3列的位线BL(1,3)、 BL(2,3)……BL(9,3)上,以此类推,将第n个子图的9个像素值对应的9个电压激励施加在2T1R忆阻器阵列第2n-1列的位线BL(1,n)、BL(2,n)……BL(9,n)上。

每个卷积核对应的卷积计算的结果是一组标量值,计算结果可以表示为一组电流输出。例如,在2T1R忆阻器阵列的源线SL(1)和SL(2)……SL(2n) 上采集到的电流输出值。

2T1R忆阻器阵列的操作方法是施加电压激励,采集电流输出。例如,对 2T1R忆阻器阵列的所有主字线施加高电平以导通全部M1晶体管。2T1R忆阻器阵列的第1列、第3列、……、第2n-1列辅字线施加高电平以导通对应列的M2晶体管,对2T1R忆阻器阵列的第2列、第4列、……、第2n-2列辅字线施加低电平以关闭对应列的M2晶体管。在2T1R忆阻器阵列的源线 SL(1)、SL(2)……SL(2n)上采集到输出电流值作为计算结果。根据基尔霍夫定律可知,2T1R忆阻器阵列可以并行地完成图6A所示的卷积计算。

在上述操作方法中,主字线导通M1晶体管的目的是允许对应列的忆阻器参与计算,辅字线导通部分列M2晶体管的目的是连接同一个卷积核组内的两个卷积核对应的忆阻器之间的位线,辅字线关闭部分列M2晶体管的目的是断开不同卷积核组的忆阻器之间的位线。

本试验例中,9行2n列的实施例1的2T1R忆阻器阵列在操作方法和功能上与n个9行2列的1T1R忆阻器阵列相似。若使用9行2n列的1T1R忆阻器阵列完成图6A所示的卷积计算任务,由于其只有9个位线可以施加电压激励,需要将各个子图的数据分批次串行地输入1T1R忆阻器阵列中,所以需要分别施加n次不同的电压激励才能完成全部计算任务。在本试验例中,实施例1的2T1R忆阻器阵列提升了并行程度,实施例1的2T1R忆阻器阵列完成图6A所示的全连接计算任务所需时间是1T1R忆阻器阵列完成相同计算任务所需时间的1/n。

本试验例使用一个18行2列的实施例2的2T1R忆阻器阵列实现卷积计算,例如该卷积计算使用1个卷积核组,该卷积核组包含2个3×3大小的卷积核。

图6A为一种卷积神经网络的卷积计算的示意图,图7为基于实施例2 的2T1R忆阻器阵列实现图6A中的卷积计算的示意图。

如图6A所示,本试验例中的卷积神经网络使用1个卷积核组对待处理图片进行卷积运算。本试验例中的卷积核组包含1个卷积核,卷积核尺寸为 3×3。本试验例中的卷积计算可以等效为图片像素值与卷积核之间的乘积累加运算。

如图7所示,采用一个18行2列的实施例2的2T1R忆阻器阵列表示卷积核中的值。例如,2T1R忆阻器阵列中的第1列第1行到第1列第9行的9 个忆阻器的电导值用来表示卷积核1中9个权重w1,1、w1,2……w1,9,2T1R 阵列中的第2列第1行到第2列第9行的的9个忆阻器的电导值用来表示卷积核2中9个权重w2,1、w2,2……w2,9;2T1R忆阻器阵列中的第10行到第 18行的忆阻器的电导值与第1行到第9行的忆阻器的电导值对应相同。

卷积层对待处理图像进行卷积处理,需要将待处理图像划分为多个子图,每个子图的尺寸与卷积核的尺寸大小相同。子图的像素值可以表示为一组电压激励。例如,将第1个子图的9个像素值对应的9个电压激励施加在2T1R 忆阻器阵列第1行到第9行的位线BL1、BL2……BL9上,将第2个子图的9 个像素值对应的9个电压激励施加在2T1R忆阻器阵列第10行到第18行的位线BL10、BL11……BL18上。

每个卷积核对应的卷积计算的结果是一组标量值,计算结果可以表示为一组电流输出。例如,在2T1R忆阻器阵列的源线SL(9,1),SL(9,2),SL(18,1), SL(18,2)上采集到的电流输出值。

2T1R忆阻器阵列的操作方法是施加电压激励,采集电流输出。例如,对 2T1R忆阻器阵列的所有主字线施加高电平以导通全部M1晶体管。2T1R忆阻器阵列的第1行、第2行……第8行、第10行、第11行……第17行辅字线施加高电平以导通对应列的M2晶体管,对2T1R忆阻器阵列的第9行辅字线施加低电平以关闭对应行的M2晶体管。在2T1R忆阻器阵列的源线 SL(9,1),SL(9,2),SL(18,1),SL(18,2)上采集到输出电流值作为计算结果。根据基尔霍夫定律可知,2T1R忆阻器阵列可以并行地完成图6A所示的卷积计算。

在上述操作方法中,主字线导通M1晶体管的目的是允许对应列的忆阻器参与计算,辅字线导通部分行M2晶体管的目的是连接同一个卷积核对应的忆阻器之间的源线,辅字线关闭部分列M2晶体管的目的是断开不同卷积核的忆阻器之间的源线。

本试验例中,18行2列的实施例2的2T1R忆阻器阵列在操作方法和功能上与2个18行2列的1T1R忆阻器阵列相似。若使用18行2列的1T1R忆阻器阵列完成图6A所示的卷积计算任务,由于其只有2个源线可以输出电流信号,需要将各个子图的数据分批次串行地输入1T1R忆阻器阵列中,所以需要分别施加n次不同的电压激励才能完成全部计算任务。在本试验例中,实施例2的2T1R忆阻器阵列提升了并行程度,实施例2的2T1R忆阻器阵列完成图6A所示的全连接计算任务所需时间是1T1R忆阻器阵列完成相同计算任务所需时间的1/2。

忆阻器阵列中各个忆阻器的电导值需要通过置位操作和复位操作进行调整。本试验例对一个m行n列的实施例1的2T1R忆阻器阵列并行地进行置位操作,实现对其忆阻器电导值进行调整。

图8为一种基于实施例1的2T1R忆阻器阵列实现并行置位操作的示意图。

如图8所示,本试验例中对m行n列的实施例1的2T1R忆阻器阵列中的部分忆阻器进行并行置位操作,以实现忆阻器电导值的调整。

在单独对某一列忆阻器进行置位操作时,这一列的源线接地,这一列中需要进行置位操作忆阻器所在的行的位线连接置位电压,这一列中不需要进行置位操作的忆阻器所在的行的位线接地。

图8所示的V表示置位操作过程中施加在忆阻器对应位线上的电压,其取值取决于实际应用中该忆阻器是否需要置位操作,若需要置位操作,则连接置位电压,若不需要置位操作,则接地。

2T1R忆阻器阵列进行并行置位操作方法是施加所需的电压激励。例如,对2T1R忆阻器阵列的所有主字线施加高电平以导通全部M1晶体管,2T1R 忆阻器阵列的所有辅字线施加低电平以关闭全部M2晶体管,对2T1R忆阻器阵列的位线BL(1,1)、BL(2,1)……BL(m,1)……BL(1,n)、BL(2,n)……BL(m,n) 并行输入所需的电压激励,将2T1R忆阻器阵列的源线SL(1)、SL(2)……SL(n) 接地。按照上述操作流程,2T1R忆阻器阵列可以并行地完成置位操作。

在上述操作方法中,主字线导通M1晶体管的目的是允许对应列的忆阻器参与置位操作,辅字线关闭M2晶体管的目的是断开M2晶体管两侧的位线。当辅字线对应的M2晶体管全部关闭时,m行n列的2T1R忆阻器阵列在置位操作的方法和效果上与n个m行1列的1T1R忆阻器阵列相似。若要对 m行n列的1T1R忆阻器阵列进行置位操作,由于其只有m个位线可以施加电压激励,所以需要分别施加n次不同的电压激励才能实现对所有列的忆阻器的置位操作。在本试验例中,实施例1的2T1R忆阻器阵列提升了并行程度,实施例1的2T1R忆阻器阵列完成置位操作任务所需时间是1T1R忆阻器阵列完成相同计算任务所需时间的1/n。

尽管本发明已进行了一定程度的描述,明显地,在不脱离本发明的精神和范围的条件下,可进行各个条件的适当变化。可以理解,本发明不限于所述实施方案,而归于权利要求的范围,其包括所述每个因素的等同替换。

- 基于忆阻器的2T1R阵列及其并行操作方法和算法

- 一种基于忆阻器阵列的球形数据分类装置及其操作方法