半导体装置及半导体存储装置

文献发布时间:2023-06-19 12:13:22

本申请案基于2020年2月7日申请的以往的日本专利申请案第2020-19361号的优先权的利益,且要求该利益,其全部内容通过引用而包含于此。

技术领域

本发明的实施方式涉及一种半导体装置及半导体存储装置。

背景技术

在氧化物半导体层形成有通道的氧化物半导体晶体管具备切断动作时的通道漏电流极小的优异特性。因此,例如,探讨将氧化物半导体晶体管应用于动态随机存取存储器(Dynamic Random Access Memory,DRAM)的存储单元的开关晶体管。

例如,将氧化物半导体晶体管应用于存储单元的开关晶体管的情况下,氧化物半导体晶体管会经过伴随于存储单元或配线的形成的热处理。因此,期待实现即使经过热处理,特性的变动也较少,耐热性较高的氧化物半导体晶体管。

发明内容

本发明提供一种耐热性较高的半导体装置。

实施方式的半导体装置具备:第1氧化物半导体层,具有第1区域、第2区域、及所述第1区域与所述第2区域之间的第3区域;栅电极;栅极绝缘层,设置在所述第3区域与所述栅电极之间;第1电极,与所述第1区域电连接;第2电极,与所述第2区域电连接;及第2氧化物半导体层,设置在所述第1区域与所述第1电极之间、及所述第2区域与所述第2电极之间中至少一处,包含铟(In)、铝(Al)及锌(Zn),且铝相对于铟、铝及锌的总和的原子比为8%以上23%以下,铟相对于铟、铝及锌的总和的原子比为45%以下。

附图说明

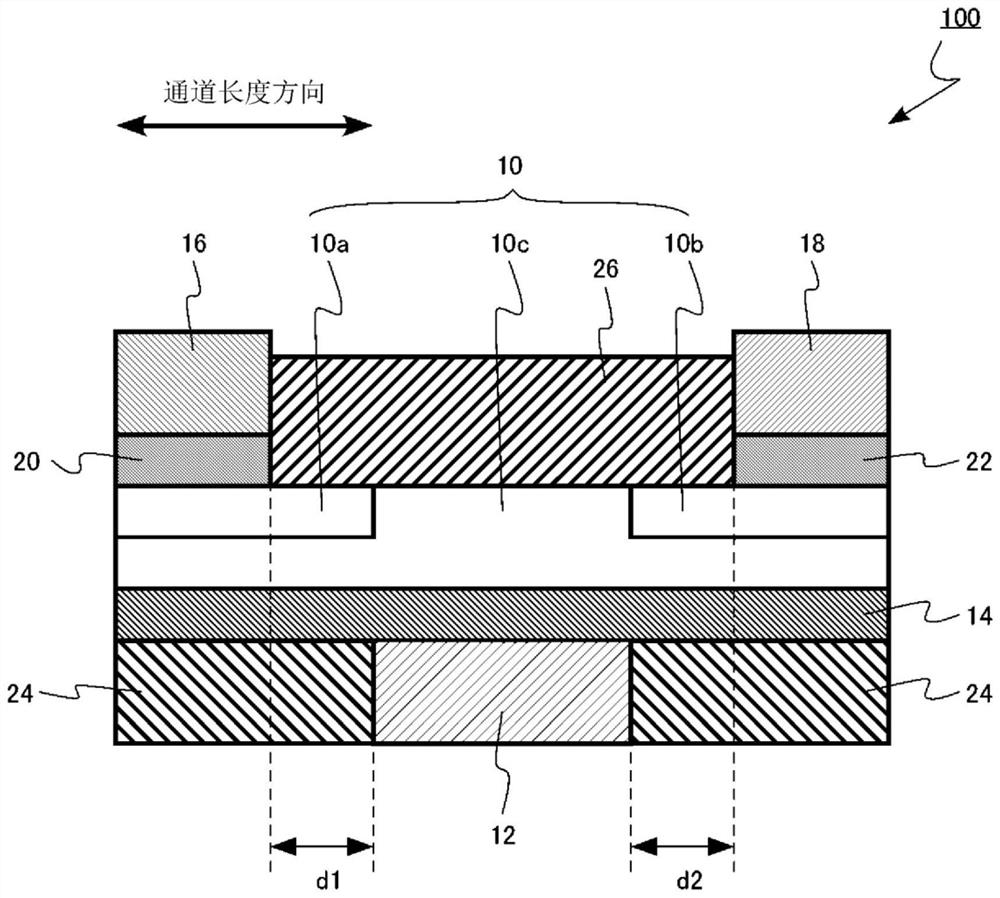

图1是第1实施方式的半导体装置的示意剖视图。

图2是表示第1实施方式的半导体装置的第2氧化物半导体及第3氧化物半导体层的化学组成范围的图。

图3是比较例的半导体装置的示意剖视图。

图4是第1实施方式的半导体装置的作用及效果的说明图。

图5是第1实施方式的半导体装置的作用及效果的说明图。

图6是表示第2实施方式的半导体装置的第1氧化物半导体层的化学组成范围的图。

图7是第3实施方式的半导体装置的示意剖视图。

图8是第4实施方式的半导体装置的示意剖视图。

图9是第4实施方式的半导体装置的示意剖视图。

图10是比较例的半导体装置的示意剖视图。

图11是第5实施方式的半导体存储装置的框图。

图12是第5实施方式的半导体存储装置的存储单元阵列的示意剖视图。

图13是第5实施方式的半导体存储装置的存储单元阵列的示意剖视图。

图14是第5实施方式的半导体存储装置的第1存储单元的示意剖视图。

图15是第5实施方式的半导体存储装置的第2存储单元的示意剖视图。

图16是第6实施方式的半导体装置的示意剖视图。

具体实施方式

以下,参照附图对本发明的实施方式进行说明。此外,在以下说明中,对相同或类似的部件等标注相同的符号,且对于已说明过一次的部件等会适当省略其说明。

另外,本说明书中,为了方便起见,有时会使用“上”或“下”这样的词语。“上”或“下”归根到底只不过是表示附图内的相对位置关系的词语,而不是规定相对于重力的位置关系的词语。

关于构成本说明书中的半导体装置及半导体存储装置的部件,其化学组成的定性分析及定量分析可采用例如二次离子质谱分析法(Secondary Ion Mass Spectrometry:SIMS)、能量分散型X射线光谱法(Energy Dispersive X-ray Spectroscopy:EDX)、拉塞福背向散射分析法(Rutherford Back-Scattering Spectroscopy:RBS)来进行。另外,对于构成半导体装置的部件的厚度、部件之间的距离等的测定,可使用例如透射型电子显微镜(Transmission Electron Microscope:TEM)。

(第1实施方式)第1实施方式的半导体装置具备:第1氧化物半导体层,具有第1区域、第2区域、及第1区域与第2区域之间的第3区域;栅电极;栅极绝缘层,设置在第3区域与栅电极之间;第1电极,与第1区域电连接;第2电极,与第2区域电连接;及第2氧化物半导体层,设置在第1区域与第1电极之间、及第2区域与第2电极之间中至少一处,包含铟(In)、铝(Al)及锌(Zn),且铝相对于铟、铝及锌的总和的原子比为8%以上23%以下,铟相对于铟、铝及锌的总和的原子比为45%以下。

图1是第1实施方式的半导体装置的示意剖视图。

第1实施方式的半导体装置为晶体管100。晶体管100是在氧化物半导体层形成有通道的氧化物半导体晶体管。晶体管100是在形成有通道的氧化物半导体层的下侧设置有栅电极,在上侧设置有源电极及漏电极的所谓底栅极型晶体管。

晶体管100具备第1氧化物半导体层10、栅电极12、栅极绝缘层14、源电极16、漏电极18、第2氧化物半导体层20、第3氧化物半导体层22、第1绝缘层24、第2绝缘层26。源电极16是第1电极的一个例子。漏电极18是第2电极的一个例子。

第1氧化物半导体层10具有第1区域10a、第2区域10b及第3区域10c。

晶体管100的接通动作时,在第1氧化物半导体层10形成成为电流路径的通道。将通道之中电子流通的方向称为通道长度方向。图1中以双向箭头表示通道长度方向。

第1氧化物半导体层10是氧化物半导体。第1氧化物半导体层10是金属氧化物。第1氧化物半导体层10例如为非晶体。

第1氧化物半导体层10包含例如铟(In)、镓(Ga)及锌(Zn)。第1氧化物半导体层10之中包含的金属元素当中,铟、镓及锌的总和的原子比例如为90%以上。另外,第1氧化物半导体层10之中包含的氧以外的元素当中,铟、镓及锌的总和的原子比例如为90%以上。例如,第1氧化物半导体层10之中,氧以外的元素当中不存在哪个元素具有比铟、镓及锌任一者大的原子比。

第1氧化物半导体层10具有第1区域10a、第2区域10b及第3区域10c。第3区域10c的至少一部分设置在第1区域10a与第2区域10b之间。

第1区域10a作为晶体管100的源极区域发挥作用,第2区域10b作为晶体管100的漏极区域发挥作用。另外,晶体管100的接通动作时,在第3区域10c形成通道。

第1区域10a与第2区域10b例如为n型半导体。第1区域10a的氧缺陷浓度、及第2区域10b的氧缺陷浓度高于例如第3区域10c的氧缺陷浓度。第1氧化物半导体层10之中的氧缺陷作为供体发挥作用。

第1区域10a的n型载子浓度、及第2区域10b的n型载子浓度高于例如第3区域10c的n型载子浓度。第1区域10a的电阻、及第2区域10b的电阻低于例如第3区域10c的电阻。

第1氧化物半导体层10的厚度例如为10nm以上100nm以下。

第1氧化物半导体层10采用例如原子层沉积法(Atomic Layer Deposition法:ALD法)来形成。

栅电极12设置在第1氧化物半导体层10的下侧。栅电极12例如为金属、金属化合物或半导体。栅电极12例如为钨(W)。栅电极12的栅极长度例如为20nm以上100nm以下。

栅极绝缘层14设置在第1氧化物半导体层10与栅电极12之间。栅极绝缘层14设置在第3区域10c与栅电极12之间。

栅极绝缘层14例如为氧化物或氮氧化物。栅极绝缘层14例如为氧化硅或氧化铝。栅极绝缘层14的厚度例如为2nm以上10nm以下。

此外,也可在第1氧化物半导体层10与栅极绝缘层14之间设置材料与栅极绝缘层14不同的未图示的氧化物层。

源电极16设置在第1氧化物半导体层10的上侧。第1氧化物半导体层10隔在栅电极12与源电极16之间。

源电极16设置在第1区域10a的上侧。源电极16与第1区域10a电连接。

源电极16例如为金属或金属化合物。源电极16例如为钨(W)。

漏电极18设置在第1氧化物半导体层10的上侧。第1氧化物半导体层10隔在栅电极12与漏电极18之间。

漏电极18设置在第2区域10b的上侧。漏电极18与第2区域10b电连接。

漏电极18例如为金属或金属化合物。源电极16例如为钨(W)。

第2氧化物半导体层20设置在第1氧化物半导体层10与源电极16之间。第2氧化物半导体层20设置在第1区域10a与源电极16之间。第2氧化物半导体层20与第1氧化物半导体层10相接。

第2氧化物半导体层20是氧化物半导体。第2氧化物半导体层20是金属氧化物。第2氧化物半导体层20例如为非晶体。

第2氧化物半导体层20包含铟(In)、铝(Al)及锌(Zn)。第2氧化物半导体层20是包含铟(In)、铝(Al)及锌(Zn)的氧化物。

第2氧化物半导体层20中,铝相对于铟、铝及锌的总和的原子比为8%以上23%以下。也就是说,第2氧化物半导体层20中,以Al/(In+Al+Zn)表达的原子比为8%以上23%以下。

第2氧化物半导体层20中,铟相对于铟、铝及锌的总和的原子比为45%以下。也就是说,第2氧化物半导体层20中,以In/(In+Al+Zn)表达的原子比为45%以下。

第2氧化物半导体层20中,铟相对于铟、铝及锌的总和的原子比例如为1%以上。也就是说,第2氧化物半导体层20中,以In/(In+Al+Zn)表达的原子比为1%以上。

第2氧化物半导体层20之中包含的金属元素当中,铟、铝及锌的总和的原子比例如为90%以上。另外,第2氧化物半导体层20之中包含的氧以外的元素当中,铟、铝及锌的总和的原子比例如为90%以上。例如,第2氧化物半导体层20之中,氧以外的元素当中不存在哪个元素具有比铟、铝及锌任一者大的原子比。

另外,第2氧化物半导体层20之中包含的金属元素当中,镓(Ga)、锡(Sn)及钛(Ti)各自的原子比都小于例如10%。

第3氧化物半导体层22设置在第1氧化物半导体层10与漏电极18之间。第3氧化物半导体层22设置在第2区域10b与漏电极18之间。第3氧化物半导体层22与第1氧化物半导体层10相接。

第3氧化物半导体层22是氧化物半导体。第3氧化物半导体层22是金属氧化物。第3氧化物半导体层22例如为非晶体。

第3氧化物半导体层22包含铟(In)、铝(Al)及锌(Zn)。第3氧化物半导体层22是包含铟(In)、铝(Al)及锌(Zn)的氧化物。

第3氧化物半导体层22中,铝相对于铟、铝及锌的总和的原子比为8%以上23%以下。也就是说,以Al/(In+Al+Zn)表达的原子比为8%以上23%以下。

第3氧化物半导体层22中,铟相对于铟、铝及锌的总和的原子比为45%以下。也就是说,第3氧化物半导体层22中,以In/(In+Al+Zn)表达的原子比为45%以下。

第3氧化物半导体层22中,铟相对于铟、铝及锌的总和的原子比例如为1%以上。也就是说,第3氧化物半导体层22中,以In/(In+Al+Zn)表达的原子比为1%以上。

第3氧化物半导体层22之中包含的金属元素当中,铟、铝及锌的总和的原子比例如为90%以上。另外,第3氧化物半导体层22之中包含的氧以外的元素当中,铟、铝及锌的总和的原子比例如为90%以上。例如,第3氧化物半导体层22之中,氧以外的元素当中不存在哪个元素具有比铟、铝及锌任一者大的原子比。

另外,第3氧化物半导体层22之中包含的金属元素当中,镓(Ga)、锡(Sn)及钛(Ti)各自的原子比都小于例如10%。

图2是表示第1实施方式的半导体装置的第2氧化物半导体层及第3氧化物半导体层的化学组成范围的图。图2是三角图。图2中带有影线的区域为第2氧化物半导体层20及第3氧化物半导体层22的化学组成范围。

图2中带有影线的区域内,铝相对于铟、铝及锌的总和的原子比为8%以上23%以下。也就是说,以Al/(In+Al+Zn)表达的原子比为8%以上23%以下。另外,图2中带有影线的区域内,铟相对于铟、铝及锌的总和的原子比为45%以下。也就是说,以In/(In+Al+Zn)表达的原子比为45%以下。

将栅电极12与源电极16之间的通道长度方向的距离(图1中的d1)、及栅电极12与漏电极18之间的通道长度方向的距离(图1中的d2)称为栅极偏移距离。栅极偏移距离d1例如为30nm以上。栅极偏移距离d2例如为30nm以上。

第1绝缘层24设置在第1氧化物半导体层10的下侧。第1绝缘层24例如为氧化物、氮化物或氮氧化物。第1绝缘层24例如为氧化硅、氮化硅或氮氧化硅。

第2绝缘层26设置在第1氧化物半导体层10的上侧。第2绝缘层26设置在源电极16与漏电极18之间。

第2绝缘层26将源电极16与漏电极18电分离。第2绝缘层26例如为氧化物、氮化物或氮氧化物。第2绝缘层26例如为氧化硅、氮化硅或氮氧化硅。

以下,对第1实施方式的半导体装置的作用及效果进行说明。

图3是比较例的半导体装置的示意剖视图。比较例的半导体装置为晶体管800。晶体管800是在氧化物半导体形成有通道的氧化物半导体晶体管。晶体管800是在形成有通道的氧化物半导体层的下侧设置有栅电极,在上侧设置有源电极及漏电极的底栅极型晶体管。

晶体管800具备第1氧化物半导体层10、栅电极12、栅极绝缘层14、源电极16、漏电极18、第1绝缘层24、第2绝缘层26、金属氧化物层30。源电极16是第1电极的一个例子。漏电极18是第2电极的一个例子。

第1氧化物半导体层10具有第1区域10a、第2区域10b及第3区域10c。

晶体管800在不具备第2氧化物半导体层20及第3氧化物半导体层22这一点上,与第1实施方式的晶体管100不同。另外。晶体管800在具备金属氧化物层30这一点上,与第1实施方式的晶体管100不同。

金属氧化物层30通过形成源电极16及漏电极18后所实施的热处理,而形成在第1氧化物半导体层10之上。也就是说,是通过第1氧化物半导体层10中包含的氧被源电极16及漏电极18吸收,使构成源电极16及漏电极18的金属氧化而形成的。

形成金属氧化物层30会使第1氧化物半导体层10与源电极16之间的接触电阻、及第1氧化物半导体层10与漏电极18之间的接触电阻增加。因此,会发生晶体管800的寄生电阻增加,晶体管800的接通电流减少的问题。

另外,第1氧化物半导体层10的第1区域10a及第2区域10b是通过形成源电极16及漏电极18后所实施的热处理,使氧被源电极16及漏电极18吸收而形成的。也就是说,通过第1氧化物半导体层10中包含的氧被源电极16及漏电极18吸收,而使第1氧化物半导体层10产生氧缺陷。通过产生氧缺陷,而形成n型载子浓度较高且电阻较低的第1区域10a及第2区域10b。

第1区域10a通过热处理,从源电极16向栅电极18那边横向延展。另外,第2区域10b通过热处理,从漏电极18向栅电极18那边横向延展。

在晶体管800中,第1区域10a与第2区域10b之间的距离成为通道长度。如果第1区域10a与第2区域10b之间的距离变短,那么晶体管800的通道长度变短。如果晶体管800的通道长度过短,那么就会发生晶体管800的阈值电压降低或截止漏电流增加的现象,因此不好。

所以,优选在栅电极12与源电极16之间设置指定的栅极偏移距离d1。另外,优选在栅电极12与漏电极18之间设置指定的栅极偏移距离d2。

在被源电极16及漏电极18吸收的氧较少的情况下,第1区域10a及第2区域10b的通道长度方向的延展量减少。因此,栅电极12与第1区域10a之间的间隔距离(图3中的d3)增加。另外,栅电极12与第2区域10b之间的间隔距离(图3中的d4)增加。

间隔距离d3及间隔距离d4变大会使晶体管800的寄生电阻增加。因此,会发生晶体管800的接通电流减少的问题。

第1实施方式的晶体管100在第1氧化物半导体层10与源电极16之间具备第2氧化物半导体层20,在第1氧化物半导体层10与漏电极18之间具备第3氧化物半导体层22。通过具备第2氧化物半导体层20与第3氧化物半导体层22,源电极16及漏电极18的氧化得到抑制。

因此,通过具备第2氧化物半导体层20与第3氧化物半导体层22,第1氧化物半导体层10与源电极16之间的接触电阻、及第1氧化物半导体层10与漏电极18之间的接触电阻的增加得到抑制。由此,晶体管100的接通电流的减少得到抑制。

图4是第1实施方式的半导体装置的作用及效果的说明图。图4是表示形成晶体管后的氮退火温度与接触电阻的关系的图。图中,圆形表示第1实施方式的情况,三角形表示比较例的情况。

在第1实施方式的情况下,第2氧化物半导体层20及第3氧化物半导体层22的化学组成使用的是图2中的点X的化学组成。

如图4所示,在比较例的情况下,通过400℃以上的氮退火,接触电阻上升。而另一方面,在第1实施方式的情况下,即使进行400℃以上的氮退火,接触电阻也不见变化。因此,第1实施方式的晶体管100中,即使实施热处理,接触电阻也不增加,具备较高的耐热性。

第1实施方式的晶体管100在第1氧化物半导体层10与源电极16之间具备第2氧化物半导体层20,在第1氧化物半导体层10与漏电极18之间具备第3氧化物半导体层22。通过具备第2氧化物半导体层20与第3氧化物半导体层22,第1区域10a及第2区域10b的通道长度方向的延展量增加。因此,栅电极12与第1区域10a之间的间隔距离减少。另外,栅电极12与第2区域10b之间的间隔距离减少。

通过间隔距离变小,晶体管100的寄生电阻减少。因此,第1实施方式的晶体管100的接通电流的减少得到抑制。

图5是第1实施方式的半导体装置的作用及效果的说明图。图5是表示在使晶体管的栅极偏移距离发生了变化的情况下晶体管的接通电流的图。图中,圆形表示第1实施方式的情况,三角形表示比较例的情况。

在第1实施方式的情况下,第2氧化物半导体层20及第3氧化物半导体层22的化学组成使用的是图2中的点X的化学组成。

晶体管的接通电流是在形成晶体管后且进行320℃的氮退火后测定的。栅极偏移距离为负的情况表示的是,栅电极12与源电极16或栅电极12与漏电极18在通道长度方向上分离而非重叠的情况。

由图5可知,在相同的栅极偏移距离下进行比较时,第1实施方式的情况比起比较例的情况,接通电流降低。认为其原因在于,在第1实施方式的情况下,第1区域10a及第2区域10b的通道长度方向的延展量较大,晶体管的寄生电阻降低。

第2氧化物半导体层20及第3氧化物半导体层22中,铝相对于铟、铝及锌的总和的原子比为8%以上23%以下。另外,铟相对于铟、铝及锌的总和的原子比为45%以下。

所述化学组成范围内的金属氧化物的透氧性较低。因为所述化学组成范围内的金属氧化物的透氧性较低,所以通过将其隔在第1氧化物半导体层10与源电极16之间、及第1氧化物半导体层10与漏电极18之间,能抑制源电极16及漏电极18的氧化。

尤其是,通过使第2氧化物半导体层20及第3氧化物半导体层22中铟相对于铟、铝及锌的总和的原子比为45%以下,构成第2氧化物半导体层20及第3氧化物半导体层22的金属氧化物的结晶化得到抑制。通过金属氧化物的结晶化得到抑制,其透氧性变低。

另外,所述化学组成范围内的金属氧化物的吸氧能力较高。所述化学组成范围内的金属氧化物因为吸氧能力较高,所以会从第1氧化物半导体层10吸收大量的氧。因此,第1区域10a及第2区域10b的通道长度方向的延展量增加。

从降低透氧性,提高吸氧能力的观点来说,第2氧化物半导体层20及第3氧化物半导体层22中,铟相对于铟、铝及锌的总和的原子比优选1%以上,更优选35%以上。

从容易制造晶体管100的观点来说,栅电极12与源电极16之间的距离、及栅电极12与漏电极18之间的距离优选30nm以上。

以上,根据第1实施方式,实现热处理后的接触电阻的增加得到抑制而具备较高耐热性的氧化物半导体晶体管。另外,根据第1实施方式,实现具备较低寄生电阻的氧化物半导体晶体管。

(第2实施方式)第2实施方式的半导体装置在第1氧化物半导体层包含铟(In)、铝(Al)及锌(Zn),且铝相对于铟、铝及锌的总和的原子比为8%以上23%以下,铟相对于铟、铝及锌的总和的原子比为70%以下这一点上,与第1实施方式的半导体装置不同。以下,对于与第1实施方式重复的内容会省略一部分记述。

图6是表示第2实施方式的半导体装置的第1氧化物半导体层的化学组成范围的图。图6是三角图。图6中带有影线的区域为第1氧化物半导体层10的化学组成范围。

第2实施方式的晶体管的第1氧化物半导体层10包含铟(In)、铝(Al)及锌(Zn),且铝相对于铟、铝及锌的总和的原子比为8%以上23%以下。也就是说,以Al/(In+Al+Zn)表达的原子比为8%以上23%以下。另外,图6中带有影线的区域内,铟相对于铟、铝及锌的总和的原子比为70%以下。也就是说,以In/(In+Al+Zn)表达的原子比为70%以下。

第1氧化物半导体层10的化学组成与第2氧化物半导体层20及第3氧化物半导体层22的化学组成不同。

第1氧化物半导体层10之中包含的金属元素当中,铟、铝及锌的总和的原子比例如为90%以上。另外,第1氧化物半导体层10之中包含的氧以外的元素当中,铟、铝及锌的总和的原子比例如为90%以上。例如,第1氧化物半导体层10之中,氧以外的元素当中不存在哪个元素具有比铟、铝及锌任一者大的原子比。

另外,第1氧化物半导体层10之中包含的金属元素当中,镓(Ga)、锡(Sn)及钛(Ti)各自的原子比都小于例如10%。

如果形成氧化物半导体晶体管后实施热处理,那么有例如阈值电压发生变动的风险。阈值电压的变动认为是由构成形成有通道的氧化物半导体层的金属氧化物中的氧与金属元素解离而导致的。换句话来说,认为是因为在构成形成有通道的氧化物半导体层的金属氧化物中形成氧缺陷,而导致阈值电压发生变动。期待实现即使经过热处理,阈值电压的变动也较少,耐热性较高的氧化物半导体晶体管。

将图6所示的化学组成范围内的金属氧化物应用于第1氧化物半导体层10的情况下,能实现即使经过热处理,阈值电压的变动也较少,耐热性较高的氧化物半导体晶体管。另外,能实现移动度较高的氧化物半导体晶体管。

从提高晶体管的耐热性的观点来说,第1氧化物半导体层10中,铝相对于铟、铝及锌的总和的原子比优选10%以上20%以下,更优选11%以上15%以下。

从提高晶体管的移动度的观点来说,第1氧化物半导体层10中包含的铟相对于铟、铝及锌的总和的原子比优选39%以上。从提高晶体管的移动度的观点来说,第1氧化物半导体层10中包含的铟相对于铟、铝及锌的总和的原子比优选比第2氧化物半导体层20及第3氧化物半导体层22中包含的铟相对于铟、铝及锌的总和的原子比大。

从抑制第1氧化物半导体层10的结晶化,使晶体管的特性稳定的观点来说,第1氧化物半导体层10中包含的铟相对于铟、铝及锌的总和的原子比优选45%以下,更优选41%以下。

根据第2实施方式,与第1实施方式同样地,实现热处理后的接触电阻的增加得到抑制而具备较高耐热性的氧化物半导体晶体管。另外,与第1实施方式同样地,实现具备较低寄生电阻的氧化物半导体晶体管。另外,实现热处理后的阈值电压的变动得到抑制而具备较高耐热性的氧化物半导体晶体管。另外,实现移动度较高的氧化物半导体晶体管。

(第3实施方式)第3实施方式的半导体装置在栅电极位于第1氧化物半导体层的上侧这一点上,与第1实施方式的半导体装置不同。以下,对于与第1实施方式重复的内容会省略一部分记述。

图7是第3实施方式的半导体装置的示意剖视图。

第3实施方式的半导体装置为晶体管200。晶体管200是在氧化物半导体层形成有通道的氧化物半导体晶体管。晶体管200是在形成有通道的氧化物半导体层的上侧设置有栅电极、源电极及漏电极的所谓顶栅极型晶体管。

晶体管200具备第1氧化物半导体层10、栅电极12、栅极绝缘层14、源电极16、漏电极18、第2氧化物半导体层20、第3氧化物半导体层22、第1绝缘层24。源电极16是第1电极的一个例子。漏电极18是第2电极的一个例子。

第1氧化物半导体层10具有第1区域10a、第2区域10b及第3区域10c。

根据第3实施方式,与第1实施方式同样地,实现热处理后的接触电阻的增加得到抑制而具备较高耐热性的氧化物半导体晶体管。另外,与第1实施方式同样地,实现具备较低寄生电阻的氧化物半导体晶体管。

(第4实施方式)第4实施方式的半导体装置在栅电极包围第1氧化物半导体层这一点上,与第1实施方式的半导体装置不同。以下,对于与第1实施方式重复的内容会省略一部分记述。

图8、图9是第4实施方式的半导体装置的示意剖视图。图9是图8的AA’剖视图。在图8中,将水平方向称为第1方向,将纵深方向称为第2方向,将上下方向称为第3方向。

第4实施方式的半导体装置为晶体管300。晶体管300是在氧化物半导体形成有通道的氧化物半导体晶体管。晶体管300是栅电极包围形成有通道的氧化物半导体层而设置的所谓环绕式栅极晶体管(Surrounding Gate Transistor,SGT)。晶体管300是所谓的纵式晶体管。

晶体管300具备第1氧化物半导体层10、栅电极12、栅极绝缘层14、源电极16、漏电极18、第2氧化物半导体层20、第3氧化物半导体层22、层间绝缘层32。源电极16是第1电极的一个例子。漏电极18是第2电极的一个例子。

第1氧化物半导体层10具有第1区域10a、第2区域10b及第3区域10c。

第1氧化物半导体层10设置在源电极16与漏电极18之间。晶体管300的接通动作时,在第1氧化物半导体层10形成成为电流路径的通道。第1氧化物半导体层10沿着第3方向延伸。第1氧化物半导体层10为沿着第3方向延伸的柱状。第1氧化物半导体层10例如为圆柱状。

将通道之中电子流通的方向称为通道长度方向。第3方向为晶体管300的通道长度方向。

第1氧化物半导体层10是氧化物半导体。第1氧化物半导体层10是金属氧化物。第1氧化物半导体层10例如为非晶体。

第1氧化物半导体层10包含例如铟(In)、镓(Ga)及锌(Zn)。第1氧化物半导体层10之中包含的金属元素当中,铟、镓及锌的总和的原子比例如为90%以上。另外,第1氧化物半导体层10之中包含的氧以外的元素当中,铟、镓及锌的总和的原子比例如为90%以上。例如,第1氧化物半导体层10之中,氧以外的元素当中不存在哪个元素具有比铟、镓及锌任一者大的原子比。

第1氧化物半导体层10具有第1区域10a、第2区域10b及第3区域10c。第3区域10c设置在第1区域10a与第2区域10b之间。

第1区域10a作为晶体管300的源极区域发挥作用,第2区域10b作为晶体管300的漏极区域发挥作用。另外,晶体管300的接通动作时,在第3区域10c形成通道。

第1区域10a与第2区域10b例如为n型半导体。第1区域10a的氧缺陷浓度、及第2区域10b的氧缺陷浓度高于例如第3区域10c的氧缺陷浓度。第1氧化物半导体层10之中的氧缺陷作为供体发挥作用。

第1区域10a的n型载子浓度、及第2区域10b的n型载子浓度高于例如第3区域10c的n型载子浓度。第1区域10a的电阻、及第2区域10b的电阻低于例如第3区域10c的电阻。

第1氧化物半导体层10的第1方向的宽度例如为20nm以上100nm以下。第1氧化物半导体层10的第3方向的长度例如为80nm以上200nm以下。

第1氧化物半导体层10采用例如原子层沉积法(Atomic Layer Deposition法:ALD法)来形成。

栅电极12包围第1氧化物半导体层10而设置。栅电极12设置在第1氧化物半导体层10的周围。

栅电极12例如为金属、金属化合物或半导体。栅电极12例如为钨(W)。栅电极12的栅极长度例如为20nm以上100nm以下。栅电极12的栅极长度为栅电极12的第3方向的长度。

栅极绝缘层14设置在第1氧化物半导体层10与栅电极12之间。栅极绝缘层14包围第1氧化物半导体层10而设置。栅极绝缘层14至少设置在第3区域10c与栅电极12之间。

栅极绝缘层14例如为氧化物或氮氧化物。栅极绝缘层14例如为氧化硅或氧化铝。栅极绝缘层14的厚度例如为2nm以上10nm以下。

此外,也可在第1氧化物半导体层10与栅极绝缘层14之间设置材料与栅极绝缘层14不同的未图示的氧化物层。

源电极16设置在第1氧化物半导体层10的下侧。源电极16设置在第1区域10a的下侧。源电极16与第1区域10a电连接。

源电极16例如为金属或金属化合物。源电极16例如为钨(W)。

漏电极18设置在第1氧化物半导体层10的上侧。漏电极18设置在第2区域10b的上侧。漏电极18与第2区域10b电连接。

漏电极18例如为金属或金属化合物。源电极16例如为钨(W)。

第2氧化物半导体层20设置在第1氧化物半导体层10与源电极16之间。第2氧化物半导体层20设置在第1区域10a与源电极16之间。第2氧化物半导体层20与第1氧化物半导体层10相接。

第2氧化物半导体层20是氧化物半导体。第2氧化物半导体层20是金属氧化物。第2氧化物半导体层20例如为非晶体。

第2氧化物半导体层20包含铟(In)、铝(Al)及锌(Zn)。第2氧化物半导体层20是包含铟(In)、铝(Al)及锌(Zn)的氧化物。

第2氧化物半导体层20中,铝相对于铟、铝及锌的总和的原子比为8%以上23%以下。也就是说,第2氧化物半导体层20中,以Al/(In+Al+Zn)表达的原子比为8%以上23%以下。

第2氧化物半导体层20中,铟相对于铟、铝及锌的总和的原子比为45%以下。也就是说,第2氧化物半导体层20中,以In/(In+Al+Zn)表达的原子比为45%以下。

第2氧化物半导体层20中,铟相对于铟、铝及锌的总和的原子比例如为1%以上。也就是说,第2氧化物半导体层20中,以In/(In+Al+Zn)表达的原子比为1%以上。

第2氧化物半导体层20之中包含的金属元素当中,铟、铝及锌的总和的原子比例如为90%以上。另外,第2氧化物半导体层20之中包含的氧以外的元素当中,铟、铝及锌的总和的原子比例如为90%以上。例如,第2氧化物半导体层20之中,氧以外的元素当中不存在哪个元素具有比铟、铝及锌任一者大的原子比。

另外,第2氧化物半导体层20之中包含的金属元素当中,镓(Ga)、锡(Sn)及钛(Ti)各自的原子比都小于例如10%。

第3氧化物半导体层22设置在第1氧化物半导体层10与漏电极18之间。第3氧化物半导体层22设置在第2区域10b与漏电极18之间。第3氧化物半导体层22与第1氧化物半导体层10相接。

第3氧化物半导体层22是氧化物半导体。第3氧化物半导体层22是金属氧化物。第3氧化物半导体层22例如为非晶体。

第3氧化物半导体层22包含铟(In)、铝(Al)及锌(Zn)。第3氧化物半导体层22是包含铟(In)、铝(Al)及锌(Zn)的氧化物。

第3氧化物半导体层22中,铝相对于铟、铝及锌的总和的原子比为8%以上23%以下。也就是说,以Al/(In+Al+Zn)表达的原子比为8%以上23%以下。

第3氧化物半导体层22中,铟相对于铟、铝及锌的总和的原子比为45%以下。也就是说,第3氧化物半导体层22中,以In/(In+Al+Zn)表达的原子比为45%以下。

第3氧化物半导体层22中,铟相对于铟、铝及锌的总和的原子比例如为1%以上。也就是说,第3氧化物半导体层22中,以In/(In+Al+Zn)表达的原子比为1%以上。

第3氧化物半导体层22之中包含的金属元素当中,铟、铝及锌的总和的原子比例如为90%以上。另外,第3氧化物半导体层22之中包含的氧以外的元素当中,铟、铝及锌的总和的原子比例如为90%以上。例如,第3氧化物半导体层22之中,氧以外的元素当中不存在哪个元素具有比铟、铝及锌任一者大的原子比。

另外,第3氧化物半导体层22之中包含的金属元素当中,镓(Ga)、锡(Sn)及钛(Ti)各自的原子比都小于例如10%。

将栅电极12与源电极16之间的通道长度方向的距离(图8中的d5)、及栅电极12与漏电极18之间的通道长度方向的距离(图8中的d6)称为栅极偏移距离。栅极偏移距离d5例如为30nm以上。栅极偏移距离d6例如为30nm以上。

层间绝缘层32设置在栅电极12、源电极16及漏电极18的周围。层间绝缘层32例如为氧化物、氮化物或氮氧化物。层间绝缘层32例如为氧化硅、氮化硅或氮氧化硅。

图10是比较例的半导体装置的示意剖视图。比较例的半导体装置为晶体管900。晶体管900是在氧化物半导体形成有通道的氧化物半导体晶体管。晶体管900是栅电极包围形成有通道的氧化物半导体层而设置的所谓SGT。晶体管900是所谓的纵式晶体管。

晶体管900在不具备第2氧化物半导体层20及第3氧化物半导体层22这一点上,与第4实施方式的晶体管300不同。另外。晶体管900在具备金属氧化物层30这一点上,与第4实施方式的晶体管300不同。

金属氧化物层30是通过形成源电极16及漏电极18后所实施的热处理而形成的。也就是说,是通过第1氧化物半导体层10中包含的氧被源电极16及漏电极18吸收,使构成源电极16及漏电极18的金属氧化而形成的。

形成金属氧化物层30会使第1氧化物半导体层10与源电极16之间的接触电阻、及第1氧化物半导体层10与漏电极18之间的接触电阻增加。因此,会发生晶体管900的寄生电阻增加,晶体管900的接通电流减少的问题。

另外,第1氧化物半导体层10的第1区域10a及第2区域10b是通过形成源电极16及漏电极18后所实施的热处理,使氧被源电极16及漏电极18吸收而形成的。也就是说,通过第1氧化物半导体层10中包含的氧被源电极16及漏电极18吸收,而使第1氧化物半导体层10产生氧缺陷。通过产生氧缺陷,而形成n型载子浓度较高且电阻较低的第1区域10a及第2区域10b。

在被源电极16及漏电极18吸收的氧较少的情况下,第1区域10a及第2区域10b的通道长度方向的延展量减少。因此,栅电极12与第1区域10a之间的间隔距离(图10中的d7)增加。另外,栅电极12与第2区域10b之间的间隔距离(图10中的d8)增加。

间隔距离d7及间隔距离d8变大会使晶体管900的寄生电阻增加。因此,会发生晶体管900的接通电流减少的问题。

第4实施方式的晶体管300在第1氧化物半导体层10与源电极16之间具备第2氧化物半导体层20,在第1氧化物半导体层10与漏电极18之间具备第3氧化物半导体层22。第2氧化物半导体层20与第3氧化物半导体层22的透氧性较低。通过具备第2氧化物半导体层20与第3氧化物半导体层22,源电极16及漏电极18的氧化得到抑制。

因此,第1氧化物半导体层10与源电极16之间的接触电阻、及第1氧化物半导体层10与漏电极18之间的接触电阻的增加得到抑制。由此,晶体管300的接通电流的减少得到抑制。

第4实施方式的晶体管300在第1氧化物半导体层10与源电极16之间具备第2氧化物半导体层20,在第1氧化物半导体层10与漏电极18之间具备第3氧化物半导体层22。第2氧化物半导体层20与第3氧化物半导体层22的吸氧能力较高。通过具备第2氧化物半导体层20与第3氧化物半导体层22,第1区域10a及第2区域10b的通道长度方向(第3方向)的延展量增加。因此,栅电极12与第1区域10a之间的间隔距离减少。另外,栅电极12与第2区域10b之间的间隔距离减少。

通过间隔距离变小,晶体管300的寄生电阻减少。因此,第4实施方式的晶体管300的接通电流的减少得到抑制。

以上,根据第4实施方式,与第1实施方式同样地,实现热处理后的接触电阻的增加得到抑制而具备较高耐热性的氧化物半导体晶体管。另外,与第1实施方式同样地,实现具备较低寄生电阻的氧化物半导体晶体管。另外,根据第4实施方式,通过采用SGT,能在每单位面积内以较高的密度配置晶体管。

(第5实施方式)第5实施方式的半导体存储装置具备沿着第1方向延伸的第1配线、沿着与第1方向交叉的第2方向延伸的第2配线、及存储单元,且存储单元具备:第1氧化物半导体层,具有与第1配线电连接的第1区域、第2区域、及第1区域与第2区域之间的第3区域;栅电极,包围第1氧化物半导体层,且与第2配线电连接;栅极绝缘层,设置在第1氧化物半导体层与栅电极之间;电容器,与第2区域电连接;及第2氧化物半导体层,设置在第1区域与第1配线之间、及第2区域与电容器之间中至少一处,包含铟(In)、铝(Al)及锌(Zn),且铝相对于铟、铝及锌的总和的原子比为8%以上23%以下,铟相对于铟、铝及锌的总和的原子比为45%以下。存储单元具备与第4实施方式的半导体装置的第2区域电连接的电容器。以下,对于与第1至第4实施方式重复的内容会省略一部分记述。

第5实施方式的半导体存储装置为半导体存储器400。第5实施方式的半导体存储装置是动态随机存取存储器(Dynamic Random Access Memory,DRAM)。半导体存储器400将第4实施方式的晶体管300用作DRAM的存储单元的开关晶体管。

图11是第5实施方式的半导体存储装置的框图。

如图11所示,半导体存储器400具备存储单元阵列210、字线驱动器电路212、行解码器电路214、感测放大器电路215、列解码器电路217及控制电路221。

图12、图13是第5实施方式的半导体存储装置的存储单元阵列的示意剖视图。图12是包含第1方向与第3方向那一面的剖视图,图13是包含第2方向与第3方向那一面的剖视图。第1方向与第2方向交叉。第1方向与第2方向例如垂直。第3方向是与第1方向及第2方向垂直的方向。第3方向是与例如衬底垂直的方向。

第5实施方式的存储单元阵列210具备存储单元立体配置的三维结构。图12、图13中以虚线包围的区域分别表示1个存储单元。

存储单元阵列210具备硅衬底250。

存储单元阵列210在硅衬底250之上,具备例如多根位线BL与多根字线WL。位线BL沿着第1方向延长。字线WL沿着第2方向延长。

位线BL与字线WL例如垂直交叉。位线BL与字线WL交叉的区域内配置有存储单元。存储单元中包含第1存储单元MC1及第2存储单元MC2。第1存储单元MC1及第2存储单元MC2是存储单元的一个例子。

与第1存储单元MC1及第2存储单元MC2连接的位线BL为位线BLx。位线BLx是第1配线的一个例子。与第1存储单元MC1连接的字线WL为字线WLx。字线WLx是第2配线的一个例子。

与第2存储单元MC2连接的字线WL为字线WLy。字线WLx设置在位线BLx的一侧。字线WLy设置在位线BLx的另一侧。

存储单元阵列210具有多根平板电极线PL。平板电极线PL与各存储单元的平板电极72连接。

存储单元阵列210为了各配线及各电极的电分离而具备层间绝缘层260。

多根字线WL与行解码器电路214电连接。多根位线BL与感测放大器电路215电连接。

行解码器电路214具备根据所输入的行地址信号来选择字线WL的功能。字线驱动器电路212具备对行解码器电路214所选择的字线WL施加指定电压的功能。

列解码器电路217具备根据所输入的列地址信号来选择位线BL的功能。感测放大器电路215具备对列解码器电路217所选择的位线BL施加指定电压的功能。另外,具备检测位线BL的电位并将其放大的功能。

控制电路221具备控制字线驱动器电路212、行解码器电路214、感测放大器电路215、列解码器电路217及未图示的其他电路的功能。

字线驱动器电路212、行解码器电路214、感测放大器电路215、列解码器电路217、控制电路221等电路包含例如未图示的晶体管或配线层。晶体管使用例如硅衬底250而形成。

位线BL及字线WL例如为金属。位线BL及字线WL例如为氮化钛、钨、或氮化钛与钨的积层结构。

图14是第5实施方式的半导体存储装置的第1存储单元的示意剖视图。图15是第5实施方式的半导体存储装置的第2存储单元的示意剖视图。

第1存储单元MC1设置在硅衬底250与位线BLx之间。硅衬底250与第2存储单元MC2之间设置位线BLx。

第1存储单元MC1设置在位线BLx的下侧。第2存储单元MC2设置在位线BLx的上侧。

第1存储单元MC1设置在位线BLx的一侧。第2存储单元MC2设置在位线BLx的另一侧。

第2存储单元MC2具有将第1存储单元MC1上下反转而形成的结构。第1存储单元MC1及第2存储单元MC2分别具备晶体管300及电容器201。

晶体管300具备第1氧化物半导体层10、栅电极12、栅极绝缘层14、源电极16、漏电极18、第2氧化物半导体层20、第3氧化物半导体层22。源电极16是第1电极的一个例子。漏电极18是第2电极的一个例子。晶体管300具备与第4实施方式的晶体管300相同的构成。

第1氧化物半导体层10具有第1区域10a、第2区域10b及第3区域10c。

电容器201具备单元电极71、平板电极72及电容器绝缘膜73。单元电极71及平板电极72例如为氮化钛。另外,电容器绝缘膜73具有例如氧化锆、氧化铝、氧化锆的积层结构。

电容器201与第1存储单元MC1及第2存储单元MC2的第1氧化物半导体层10的一端电连接。电容器201的单元电极71与漏电极18连接。平板电极72与平板电极线PL连接。

源电极16与位线BL连接。栅电极12与字线WL连接。

此外,在图12、图13、图14、图15中,是以位线BL与源电极16、及字线WL与栅电极12以相同的材料同时形成的情况为例进行表示的。位线BL与源电极16、及字线WL与栅电极12也可分别以不同的材料各自形成。

第1存储单元MC1的第1氧化物半导体层10的与连接于电容器201的端部为相反侧的端部(另一端)电连接着位线BLx。第2存储单元MC2的第1氧化物半导体层10的与连接于电容器201的端部为相反侧的端部(另一端)电连接着位线BLx。

第1存储单元MC1的栅电极12与字线WLx电连接。另外,第2存储单元MC2的栅电极12与字线WLy电连接。

为了通过字线WL与位线BL之间的耦合来抑制半导体存储器400的误动作,优选字线WL与位线BL之间的距离(图14中的da)较长。字线WL与位线BL之间的距离da优选30nm以上。

另外,为了通过字线WL与电容器201之间的耦合来抑制半导体存储器400的误动作,优选字线WL与电容器201之间的距离较长。因此,优选字线WL与漏电极18之间的距离(图14中的db)较长。字线WL与漏电极18的距离db优选30nm以上。

晶体管300在第1氧化物半导体层10与源电极16之间具备第2氧化物半导体层20,在第1氧化物半导体层10与漏电极18之间具备第3氧化物半导体层22。通过具备第2氧化物半导体层20与第3氧化物半导体层22,第1区域10a及第2区域10b的通道长度方向(第3方向)的延展量增加。

因此,即使拉长字线WL与位线BL之间的距离da,也能降低晶体管300的寄生电阻。另外,即使拉长字线WL与漏电极18的距离db,也能降低晶体管300的寄生电阻。

在将氧化物半导体晶体管用作DRAM的存储单元的开关晶体管的情况下,形成晶体管后实施高温且长时间的热处理。热处理例如为用来形成电容器的热处理。因此,与形成有通道的氧化物半导体层相接的金属电极的氧化容易推进。如果金属电极的氧化推进而形成金属氧化物层,那么会出现接触电阻增加的问题。

晶体管300在第1氧化物半导体层10与源电极16之间具备第2氧化物半导体层20,在第1氧化物半导体层10与漏电极18之间具备第3氧化物半导体层22。通过具备第2氧化物半导体层20与第3氧化物半导体层22,源电极16及漏电极18的氧化得到抑制。

因此,即使形成晶体管后实施高温且长时间的热处理,第1氧化物半导体层10与源电极16之间的接触电阻、及第1氧化物半导体层10与漏电极18之间的接触电阻的增加也会得到抑制。由此,晶体管300的接通电流的减少得到抑制。

根据第5实施方式,通过将第4实施方式的晶体管300用作DRAM的开关晶体管,而实现存储器特性提高的半导体存储器。

(第6实施方式)第6实施方式的半导体装置具备第1氧化物半导体层、导电层及第2氧化物半导体层,该第2氧化物半导体层设置在第1氧化物半导体层与导电层之间,包含铟(In)、铝(Al)及锌(Zn),且铝相对于铟、铝及锌的总和的原子比为8%以上23%以下,铟相对于铟、铝及锌的总和的原子比为45%以下。第6实施方式的半导体装置在将第2氧化物半导体层设置在第1氧化物半导体层与导电层之间这一点上,与第1实施方式不同。以下,对于与第1实施方式重复的内容会省略一部分记述。

图16是第6实施方式的半导体装置的示意剖视图。

第6实施方式的半导体装置包含接触结构体500。接触结构体500具备第1氧化物半导体层10、第2氧化物半导体层20、配线层40、接触插塞42、层间绝缘层44。接触插塞42是导电层的一个例子。

第1氧化物半导体层10是氧化物半导体。第1氧化物半导体层10是金属氧化物。第1氧化物半导体层10例如为非晶体。

第1氧化物半导体层10包含例如铟(In)、镓(Ga)及锌(Zn)。第1氧化物半导体层10之中包含的金属元素当中,铟、镓及锌的总和的原子比例如为90%以上。另外,第1氧化物半导体层10之中包含的氧以外的元素当中,铟、镓及锌的总和的原子比例如为90%以上。例如,第1氧化物半导体层10之中,氧以外的元素当中不存在哪个元素具有比铟、镓及锌任一者大的原子比。

配线层40例如为金属或金属化合物。

接触插塞42设置在第1氧化物半导体层10与配线层40之间。接触插塞42包含金属。接触插塞42例如为金属或金属化合物。接触插塞42例如为钨(W)。

第2氧化物半导体层20设置在第1氧化物半导体层10与接触插塞42之间。第2氧化物半导体层20是氧化物半导体。第2氧化物半导体层20是金属氧化物。第2氧化物半导体层20例如为非晶体。

第2氧化物半导体层20包含铟(In)、铝(Al)及锌(Zn)。第2氧化物半导体层20是包含铟(In)、铝(Al)及锌(Zn)的氧化物。

第2氧化物半导体层20中,铝相对于铟、铝及锌的总和的原子比为8%以上23%以下。也就是说,第2氧化物半导体层20中,以Al/(In+Al+Zn)表达的原子比为8%以上23%以下。

第2氧化物半导体层20中,铟相对于铟、铝及锌的总和的原子比为45%以下。也就是说,第2氧化物半导体层20中,以In/(In+Al+Zn)表达的原子比为45%以下。

第2氧化物半导体层20中,铟相对于铟、铝及锌的总和的原子比例如为1%以上。也就是说,第2氧化物半导体层20中,以In/(In+Al+Zn)表达的原子比为1%以上。

第2氧化物半导体层20之中包含的金属元素当中,铟、铝及锌的总和的原子比例如为90%以上。另外,第2氧化物半导体层20之中包含的氧以外的元素当中,铟、铝及锌的总和的原子比例如为90%以上。例如,第2氧化物半导体层20之中,氧以外的元素当中不存在哪个元素具有比铟、铝及锌任一者大的原子比。

另外,第2氧化物半导体层20之中包含的金属元素当中,镓(Ga)、锡(Sn)及钛(Ti)各自的原子比都小于例如10%。

层间绝缘层44设置在第1氧化物半导体层10与配线层40之间。层间绝缘层44例如为氧化硅、氮化硅或氮氧化硅。

在接触结构体500不具备第2氧化物半导体层20的情况下,通过形成接触结构体500后所实施的热处理,使接触插塞42氧化。也就是说,形成第1氧化物半导体层10中包含的氧被接触插塞42吸收,使构成接触插塞42的金属氧化的金属氧化物层。

通过在第1氧化物半导体层10与接触插塞42之间形成金属氧化物层,第1氧化物半导体层10与接触插塞42之间的接触电阻增加。

接触结构体500在第1氧化物半导体层10与接触插塞42之间具备第2氧化物半导体层20。通过具备第2氧化物半导体层20,接触插塞42的氧化得到抑制。因此,第1氧化物半导体层10与接触插塞42之间的接触电阻的增加得到抑制。

以上,根据第6实施方式,实现热处理后的接触电阻的增加得到抑制而具备较高耐热性的半导体装置。

在第1至第5实施方式中,以设置有第2氧化物半导体层20及第3氧化物半导体层22两者的晶体管为例进行了说明,但也可设为仅设置第2氧化物半导体层20及第3氧化物半导体层22任一者的晶体管。

在第1至第5实施方式中,以第1氧化物半导体层10是包含铟及镓的金属氧化物的情况为例进行了说明,但也可对第1氧化物半导体层10应用其他金属氧化物。

以上,对本发明的若干个实施方式进行了说明,但这些实施方式只是作为例子提出的,并未意图限定发明的范围。这些新颖的实施方式能以其他各种形态来实施,在不脱离发明主旨的范围内,可进行各种省略、置换、变更。例如,可将一实施方式的构成要素与另一实施方式的构成要素置换。这些实施方式及其变化包含在发明的范围及主旨中,并且包含在权利要求书所记载的发明及其等同的范围内。

- 半导体存储装置管理系统、半导体存储装置、主机装置、程序、半导体存储装置的管理方法

- 半导体存储装置及包括半导体存储装置的半导体系统